Изобретение относится к системам специализированных вычислительных средств для оценки параметров нестационарных случайных сигналов (НСС) и может быть использовано при измерении параметров сигналов в различных радиосистемах.

Известное устройство предназначено для определения характера функции, описывающей изменение среднего значения НСС. Оно состоит из соединенных входами первого интегратора и первого элемента задержки, выходы которых подсоединены к входам первого вычитателя, второго интегратора, второго элемента задержки, первого сумматора, третьего элемента задержки, второго вычитателя, третьего интегратора, четвертого элемента задержки, второго сумматора. Выход первого элемента задержки подсоединен к входу третьего элемента задержки, а выход первого интегратора подсоединен к входу второго элемента задержки, выход которого подсоединен к первому входу первого сумматора. Выход первого вычитателя подсоединен к входу второго интегратора, выход которого подсоединен к второму входу первого сумматора. Выход первого сумматора подсоединен во втором каскаде к четвертому элементу задержки и к первому входу второго вычитателя. К второму входу вычитателя подсоединен выход третьего элемента задержки. Выход второго вычитателя подсоединен к входу третьего интегратора, выход которого подсоединен к входу второго сумматора. Другой вход второго сумматора подсоединен к выходу четвертого элемента задержки. Выход i-го сумматора подсоединен к входу i-го элемента задержки из числа i-1 дополнительных элементов задержки. Выход i-го элемента задержки соединен с первым входом i-го вычитателя из числа введенных. Вторые входы этих вычитателей объединены и подключены к выходу m-го сумматора. Выход i-го вычитателя соединен с входом i-го порогового элемента с памятью. Выход i-го порогового элемента является выходом для определения (2i-1)-й степени полинома, описывающего функцию математического ожидания НСС.

Недостатком этого устройства является то, что с его помощью получают ансамбль несмещенных оценок среднего значения НСС, из которых не производится автоматический выбор наиболее точной оценки.

Целью изобретения является автоматический выбор наиболее точной оценки среднего значения НСС из ансамбля несмещенных оценок.

Цель достигается тем, что в устройство введены m каналов, содержащие последовательно соединенные дифференцирующий блок, квадратор, ключ первой группы, сумматор (соединен первый вход), накопитель, блок вычитания (соединен первый вход), ключ второй группы, амплитудный селектор, триггер, а также m ключей третьей группы, синхронизатор, формирователь, масштабный усилитель, блок выделения минимального значения. При этом выход i-го элемента задержки (i = 1, . . . , n-1) подсоединен к объединенным входу i-го канала и информационному входу i-го ключа третьей группы, управляющий вход которого соединен с выходом триггера i-го канала, выход сумматора m-го каскада подсоединен к объединенным входу m-го канала и информационному входу m-го ключа третьей группы, управляющий вход которого соединен с выходом триггера m-го канала. Первый выход синхронизатора соединен с входом формирователя, выход которого соединен с объединенными управляющими входами ключей первой группы m каналов и входом масштабного усилителя, выход которого соединен с объединенными вторыми входами сумматоров m каналов. Выход каждого накопителя соединен с одноименным входом блока выделения минимального значения, выход которого соединен с объединенными вторыми входами блоков вычитания m каналов. Управляющие входы ключей второй группы подсоединены к второму выходу синхронизатора. Входы сброса триггеров m каналов объединены с входами сброса ячеек памяти пороговых элементов и подсоединены к третьему выходу синхронизатора. Выходы m ключей третьей группы, наряду с выходами ячеек памяти пороговых элементов, являются выходами устройства.

Сравнение отличительных признаков заявляемого технического решения с тождественными признаками известных технических решений показало, что предлагаемое решение соответствует критерию "существенные отличия", так как не было выявлено у известных решений признаков или сочетания признаков, тождественных отличительным признакам заявляемого объекта, сообщающих объекту такие же свойства.

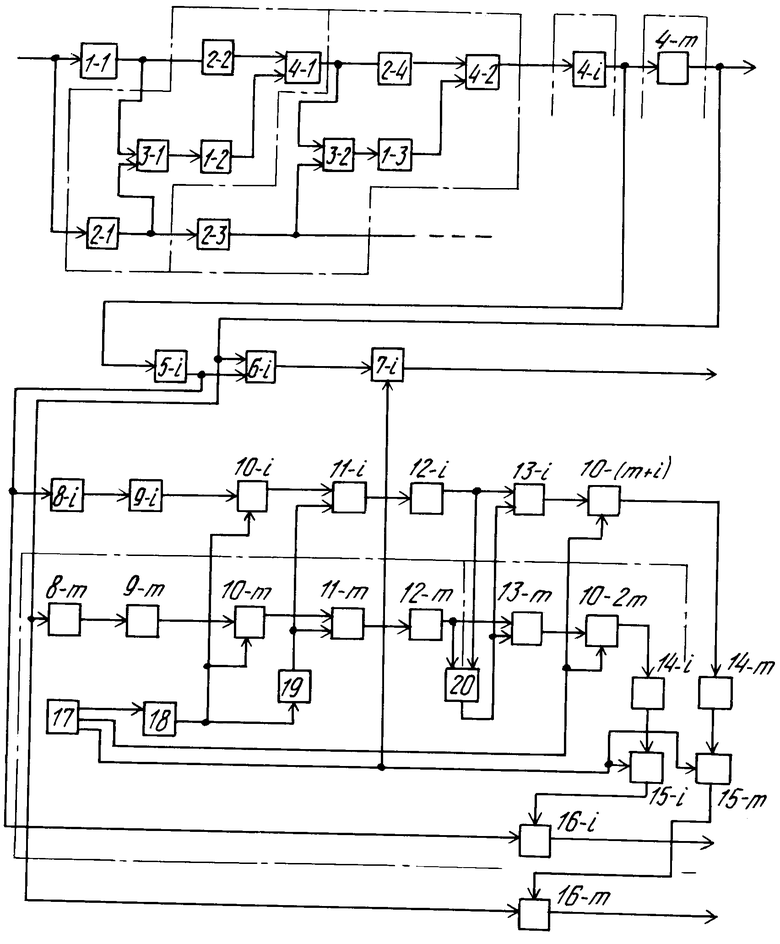

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство включает соединенные входами первый интегратор 1-1 и первый элемент 2-1 задержки, выходы которых подсоединены к входам первого вычитателя 3-1, второй интегратор 1-2, второй элемент 2-2 задержки, первый сумматор 4-1, третий элемент 2-3 задержки, второй вычитатель 3-2, третий интегратор 1-3, четвертый элемент 2-4 задержки, второй сумматор 4-2. Устройство снабжено m подобными каскадами, причем выходом i-го каскада является выход i-го сумматора 4-i, выходом m-го каскада является выход m-го сумматора 4-m.

Выход первого элемента 2-1 задержки подсоединен к входу третьего элемента 2-3 задержки, а выход первого интегратора 1-1 подсоединен к входу второго элемента 2-2 задержки, выход которого подсоединен к первому входу первого сумматора 4-1. Выход первого вычитателя 3-1 подсоединен к входу второго интегратора 1-2, выход которого подсоединен к второму входу первого сумматора 4-1. Выход первого сумматора 4-1 подсоединен во втором каскаде к четвертому элементу 2-4 задержки и к первому входу второго вычитателя 3-2. К второму входу вычитателя 3-2 подсоединен выход третьего элемента 2-3 задержки. Выход вычитателя 3-2 подсоединен к входу третьего интегратора 1-3, выход которого подсоединен к входу второго сумматора 4-2. Другой вход второго сумматора 4-2 соединен с выходом элемента 2-4 задержки. Выход i-го сумматора 4-i подключен к входу i-го элемента 5-i задержки, выход которого соединен с первым входом i-го вычитателя 6-i. Вторые входы вычитателей 6-1, . . . , 6-(m-1) объединены и подключены к выходу m-го сумматора 4-m. Выход вычитателя 6-i соединен с входом i-го порогового элемента 7-i с памятью, выход которого является выходом для определения (2i-1)-й степени полинома, описывающего функцию математического ожидания НСС.

Устройство снабжено также m каналами, содержащими последовательно соединенные дифференцирующий блок 8-i, квадратор 9-i, ключ 10-i первой группы, сумматор 11-i (соединен первый вход), накопитель 12-i, блок 13-i вычитания (соединен первый вход), ключ 10-(m+i) второй группы, амплитудный селектор 14-i, триггер 15-i, устройство содержит также m ключей 16-i третьей группы, синхронизатор 17, формирователь 18, масштабный усилитель 19, блок 20 выделения минимального значения.

Выход i-го элемента 5-i задержки подсоединен к объединенным входу i-го блока 8-i и информационному входу i-го ключа 16-i третьей группы, управляющий вход которого соединен с выходом триггера 15-i. Выход сумматора 4-m m-го каскада подсоединен к объединенным входу m-го блока 8-m и информационному входу ключа 16-m, управляющий вход которого соединен с выходом триггера 15-m. Первый выход синхронизатора 17 соединен с входом формирователя 18, выход которого соединен с объединенными управляющими входами ключей 10-1, . . . , 10-m и входом масштабного усилителя 19. Выход масштабного усилителя соединен с объединенными вторыми входами сумматоров 11-1, . . . , 11-m. Выход каждого накопителя 12-1, . . . , 12-m соединен с одноименным входом блока 20 выделения минимального значения, выход которого соединен с объединенными вторыми входами блоков 13-1, . . . , 13-m вычитания. Входы сброса триггеров 15-1, . . . , 15-m объединены с входами сброса ячеек памяти пороговых элементов 7-1, . . . , 7-(m-1) и подсоединены к второму выходу синхронизатора 17. Выходы ключей 16-1, . . . , 16-m, наряду с выходами пороговых элементов 7-1, . . . , 7-(m-1), являются выходами устройства.

Устройство работает следующим образом.

Случайный сигнал одновременно поступает на первый интегратор 1-1 и элемент 2-1 задержки. Первый сглаженный сигнал с выхода интегратора 1-1 поступает на первый вычитатель 3-1, на второй вход которого поступает задержанный на половину интервала сглаживания НСС. В вычитателе 3-1 осуществляется первое центрирование сигнала, т. е. из случайного сигнала вычитается его сглаженное значение, полученное на выходе интегратора 1-1. Далее первый центрированный сигнал сглаживается во втором интеграторе 1-2 и подается на первый сумматор 4-1. На другой вход сумматора 4-1 подается задержанный элементом 2-2 задержки сигнал с выхода интегратора 1-1. В результате на выходе сумматора 4-1 получают оценку математического ожидания НСС на выходе первого каскада устройства. Эта оценка подается на второй каскад на вычитатель 3-2, на второй вход которого поступает случайный сигнал, задержанный элементом 2-3 задержки на половину интервала сглаживания. В вычитателе 3-2 осуществляется второе центрирование сигнала, т. е. из НСС вычитается его оценка математического ожидания с выхода сумматора 4-1 первого каскада. Затем второй центрированный сигнал сглаживается в третьем интеграторе 1-3 и подается на один из входов второго сумматора 4-2. На другой вход сумматора 4-2 подается задержанный элементом 2-4 задержки сигнал с выхода сумматора 4-1. В результате на выходе сумматора 4-2 второго каскада получают еще одну оценку математического ожидания НСС. Устройство снабжено m подобными каскадами.

На выходе сумматора 4-i i-го каскада получают i-ю оценку математического ожидания НСС, а на выходе сумматора 4-m m-го каскада m-ю оценку математического ожидания НСС. Для определения характера функции, описывающей изменение математического ожидания НСС, из i-й оценки математического ожидания, задержанной в элементе 5-i задержки, в вычитателе 6-i вычитается m-я оценка математического ожидания НСС. Разность оценок с выхода вычитателя 6-i подается на вход i-го порогового элемента 7-i. Если на интервале анализа Та разность оценок не превышает заданного порога, то не происходит срабатывания порогового элемента 7-i. Это означает, что степень полинома, описывающего изменение математического ожидания НСС, меньше величины 2i-1. Если на интервале анализа разность i-й и m-й оценок превышает заданный пороговый уровень, то происходит срабатывание порогового элемента 7-i. Это означает, что степень полинома, описывающего изменение математического ожидания НСС, больше или равна величине 2i-1.

Из вышеприведенного следует, что погрешность смещения оценки математического ожидания НСС равна нулю на выходе i-го каскада устройства, т. е. сумматоре 4-i, если не происходит срабатывания порогового элемента 7-i. При этом степень полинома не превышает 2i-1.

Все оценки поступают на входы m каналов, введенных в устройство. Причем оценки математического ожидания НСС с первой по (m-1)-ю поступают с выходов одноименных элементов 5-1, . . . , 5-(m-1) задержки на входы соответствующих дифференцирующих блоков 8-1, . . . , 8-(m-1). На вход дифференцирующего блока 8-m m-я оценка поступает с выхода сумматора 4-n. Таким образом, осуществляется одновременный анализ всех оценок математического ожидания НСС в каналах устройства.

Как известно, погрешности определения математического ожидания нестационарного случайного сигнала складываются из двух независимых составляющих - погрешности смещения и дисперсии оценки. Суммарная погрешность определяет параметры формы кривой оценки математического ожидания НСС. Так, "длина" кривой оценки зависит от смещения и дисперсии оценки. При этом очевидно, что меньшая "длина" у кривой несмещенной оценки и, кроме того, меньшей "длинной" обладает оценка с меньшей дисперсией. Значит, к указанному классу оценок относятся оценки математического ожидания НСС на выходах, начиная с i-го каскада до m-го каскада, если математическое ожидание НСС описывается полиномом степенью не выше 2i-1. Что же касается того, какая из указанных оценок обладает наименьшей "длинной", а следовательно, наименьшей дисперсией, то вероятнее всего это m-я оценка на выходе сумматора 4-m. Но в силу того, что интервал сглаживания в интеграторах устройства Т ≠∞, а Т - величина конечная, то в некоторой конкретной реализации НСС наименьшей "длинной", а следовательно, наименьшей дисперсией обладает, например, j-я оценка, где j∈ [i, m] . Отсюда следует задача выбора наименее "длинной" оценки математического ожидания НСС для каждой конкретной реализации случайного сигнала. Выбрав такую оценку, тем самым получают наиболее точную оценку среднего значения реализации НСС.

Автоматический выбор наиболее точной оценки среднего значения НСС осуществляется с помощью m каналов, введенных в устройство.

Рассмотрим поступление i-й оценки математического ожидания НСС с выхода элементы 5-i задержки на объединенные вход дифференцирующего блока 8-i i-го канала и информационный вход ключа 16-i.

На выходе дифференцирующего блока 8-i в каждый момент времени получают первую производную от кривой оценки математического ожидания реализации НСС -  (t, T).

(t, T).

При малых интервалах Δt для определения производной функции имеют

. (1)

. (1)

Следовательно, приращение функции  . на интервале Δt равно

. на интервале Δt равно  (t, T) =

(t, T) =  Δt . (2)

Δt . (2)

Квадрат длины отрезка кривой оценки  (t, T) на интервале Δt равен

(t, T) на интервале Δt равен

ΔM2+Δt2 =

t2+Δt2. (3)

t2+Δt2. (3)

Указанные выше операции осуществляют в блоках 9-i, 10-i, 11-i, 17, 18, 19. На выходе квадратора 9-i получают квадрат первой производной, которая поступает на вход ключа 10-i. На выходе ключа 10-i получают отсчеты квадрата первой производной в моменты времени, отстоящие друг от друга на интервал Δt, т. е. в моменты поступления разрешающих импульсов на управляющий вход ключа 10-i c выхода формирователя 18. Отсчеты, пропорциональные второму слагаемому выражения (3), поступают на второй вход сумматора 11-i с выхода масштабного усилителя 19. В результате на выходе сумматора 11-i в дискретные моменты времени, отстоящие на интервал Δt, появляются значения, которые накапливаются в накопителе 12-i. Сигнал с выхода каждого накопителя 12-1, . . , 12-m поступает на первый вход одноименного блока 13-1, . . . , 13-m вычитания и одновременно на одноименный вход блока 20 выделения минимального значения. Выделенный сигнал минимального значения с выхода блока 20 поступает на объединенные вторые входы блоков 13-1, . . . , 13-m вычитания.

Пусть на выходе накопителя 12-j получено минимальное значение длины оценки математического ожидания реализации НСС. Значит, на выходе каждого блока 13-1, . . . , 13-m вычитания в каждый момент времени действует текущая разность между одноименным накопленным значением длины оценки на выходе соответствующего каскада устройства и минимальным значением, накопленным на выходе накопителя 12-j. Отсюда следует, что на выходе блока 13-j вычитания выходной сигнал близок к нулю.

Выходные сигналы блоков 13-1, . . . , 13-m вычитания поступают на входы одноименных ключей 10-(m+1), . . . , 10-2m второй группы. По разрешающему сигналу с второго выхода синхронизатора 17, поступающему на объединенные управляющие входы ключей 10-(m+1), . . . , 10-2m, на одноименные входы амплитудных селекторов 14-1, . . . , 14-m поступают импульсы различной амплитуды, каждый из которых равен разности сигналов на выходе одноименного блока 13-1, . . . , 13-m вычитания. При этом на выходе амплитудного селектора 14-j амплитуда импульса равна или близка к нулю. Следовательно, триггер 15-j не сработает в отличие от остальных триггеров 15-1, . . . , 15-m, которые, сработав, закрывают каждый одноименный ключ 16-1, . . . , 16-m третьей группы. Таким образом, на выходе ключа 16-j автоматически выбирается наиболее точная оценка математического ожидания данной реализа- ции НСС.

В конце интервала анализа происходит сброс триггеров 15-1, . . . , 15-m и элементов памяти в пороговых элементах 7-1, . . . , 7-(m-1).

Получение наиболее точной оценки математического ожидания конкретной реализации НСС путем автоматического выбора этой оценки позволяет адаптировать устройство к анализируемым случайным сигналам, повышая точность оценки при прежнем числе каскадов и времени интегрирования. (56) Авторское свидетельство СССР N 1140134, кл. G 06 G 7/52, 1982.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное усредняющее устройство | 1988 |

|

SU1716544A2 |

| Устройство для определения среднего значения | 1986 |

|

SU1383410A2 |

| Устройство для определения среднего значения | 1982 |

|

SU1140134A2 |

| Устройство усреднения | 1986 |

|

SU1348862A2 |

| Устройство для определения среднего значения | 1986 |

|

SU1319050A2 |

| МНОГОКАНАЛЬНЫЙ СПЕКТРОАНАЛИЗАТОР | 1991 |

|

RU2014621C1 |

| Устройство для оценки неоднородности дисперсии случайных процессов | 1990 |

|

SU1764066A1 |

| Многоканальный адаптивный спектроанализатор | 1991 |

|

SU1830489A1 |

| Многоканальный спектроанализатор | 1987 |

|

SU1439511A2 |

| Устройство для моделирования функций с помощью частных сумм сигналов Уолша | 1990 |

|

SU1741121A2 |

Изобретение относится к системам специализированных вычислительных средств для оценки параметров нестационарных случайных сигналов и может быть использовано при измерении параметров сигналов в различных радиосистемах. Цель изобретения состоит в повышении точности. Устройство содержит элемент задержки, пороговый элемент, блоки обработки информации, состоящие каждый из элементов задержки, вычитателя, интегратора и сумматора, формирователь импульсов, масштабный блок, блок выделения минимального значения и каналы обработки информации, состоящие каждый из дифференциатора, квадратора, ключей, накопителя, сумматора, вычитателя, амплитудного селектора и триггера. 1 ил.

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ, содержащее интегратор, элемент задержки, пороговый элемент и блоки обработки информации, каждый из которых состоит из двух элементов задержки, вычитателя, интегратора и сумматора, причем в каждом блоке обработки информации выход первого элемента задержки соединен с первым входом сумматора, второй вход которого подключен к выходу интегратора, вход которого соединен с выходом вычитателя, вход уменьшаемого которого подключен к выходу второго элемента задержки, вход второго элемента задержки первого блока обработки информации соединен с входом интегратора и является входом устройства, выход интегратора подключен к входу вычитаемого вычитателя и первого элемента задержки первого блока обработки информации, выход сумматора i-го блока обработки информации (где i = 1,2, . . . , m-1) соединен с входом вычитаемого (i + 1)-го блока обработки информации, выход второго элемента задержки i-го блока обработки информации соединен с входом второго элемента задержки (i+1)-го блока обработки информации, выход сумматора j-го (j=  ) блока обработки информации через элемент задержки подключен к входу уменьшаемых вычитателя, вход уменьшаемого которого соединен с выходом сумматора m-го блока обработки информации, выход вычитателя подключен к входу порогового элемента, выход которого является выходом среднего значения устройства, отличающееся тем, что, с целью повышения точности, в него введен формирователь импульсов, масштабный блок, блок выделения минимального значения, синхронизатор и каналы обработки информации, каждый из которых состоит из дифференциатора, квадратора, трех ключей, накопителя, сумматора, вычитателя, амплитудного селектора и триггера, причем в каждом канале обработки информации выход дифференциатора через квадратор соединен с информационным входом первого ключа, выход которого подключен к первому входу сумматора, выход которого через накопитель подключен к входу уменьшаемого вычитателя, выход которого соединен с информационным входом второго ключа, выход которого через амплитудный селектор соединен с единичным входом триггера, прямой выход которого подключен к управляющему входу третьего ключа, первый выход синхронизатора через формирователь импульсов соединен с управляющими входами первых ключей всех каналов обработки информации и с входом масштабного блока, выход которого подключен к вторым входам сумматоров всех каналов обработки информации, выходы накопителей соединены с входами блока выделения минимального значения, выход которого подключен к входам вычитаемого вычитателей всех каналов обработки информации, второй выход синхронизатора соединен с управляющими входами вторых ключей всех каналов обработки информации, третий выход синхронизатора подключен к синхровходу порогового элемента и к нулевым входам триггеров всех каналов обработки информации, выход элемента задержки соединен с информационным входом третьего ключа и с входом дифференциатора первого канала обработки информации, выход сумматора k-го блока обработки информации (где k = j + 1, . . . , m) подключен к входу дифференциатора и информационному входу третьего ключа (m - j)-го канала обработки информации, выходы третьих ключей всех каналов обработки информации являются выходами математического ожидания устройства.

) блока обработки информации через элемент задержки подключен к входу уменьшаемых вычитателя, вход уменьшаемого которого соединен с выходом сумматора m-го блока обработки информации, выход вычитателя подключен к входу порогового элемента, выход которого является выходом среднего значения устройства, отличающееся тем, что, с целью повышения точности, в него введен формирователь импульсов, масштабный блок, блок выделения минимального значения, синхронизатор и каналы обработки информации, каждый из которых состоит из дифференциатора, квадратора, трех ключей, накопителя, сумматора, вычитателя, амплитудного селектора и триггера, причем в каждом канале обработки информации выход дифференциатора через квадратор соединен с информационным входом первого ключа, выход которого подключен к первому входу сумматора, выход которого через накопитель подключен к входу уменьшаемого вычитателя, выход которого соединен с информационным входом второго ключа, выход которого через амплитудный селектор соединен с единичным входом триггера, прямой выход которого подключен к управляющему входу третьего ключа, первый выход синхронизатора через формирователь импульсов соединен с управляющими входами первых ключей всех каналов обработки информации и с входом масштабного блока, выход которого подключен к вторым входам сумматоров всех каналов обработки информации, выходы накопителей соединены с входами блока выделения минимального значения, выход которого подключен к входам вычитаемого вычитателей всех каналов обработки информации, второй выход синхронизатора соединен с управляющими входами вторых ключей всех каналов обработки информации, третий выход синхронизатора подключен к синхровходу порогового элемента и к нулевым входам триггеров всех каналов обработки информации, выход элемента задержки соединен с информационным входом третьего ключа и с входом дифференциатора первого канала обработки информации, выход сумматора k-го блока обработки информации (где k = j + 1, . . . , m) подключен к входу дифференциатора и информационному входу третьего ключа (m - j)-го канала обработки информации, выходы третьих ключей всех каналов обработки информации являются выходами математического ожидания устройства.

Авторы

Даты

1994-01-30—Публикация

1990-06-07—Подача