Изобретение относится к интегральной электронике в применении к цифровым схемам.

Широко известны инверторы на МДП-транзисторах (Кроуфорд Р. Схемные применения МОП-транзисторов. М. : Мир, 1970, с. 127, рис. 5.1). Такие устройства выполняются на двух МДП-транзисторах с индуцированнным каналом, причем один МДП-тразистор является управляемым, а другой - нагрузочным (включается в цепь стока управляемого МДП-транзистора). В одном варианте подложка нагрузочного МДП-транзистора соединяется с его истоком и со стоком управляемого МДП-транзистора, а в другом - с общей шиной.

Известен также интегральный МДП-инвертор (авт. св. СССР N 986241, кл. Н 01 L 27/04, 1982), содержащий полупроводниковую подложку типа проводимости, в которой сформирован пороговый элемент и ключевой элемент, содержащий три диффузионные области второго типа проводимости, между которыми расположены два изолированных затвора, причем одна из крайних областей соединена с ближайшим затвором и источником питания, а другая, крайняя область, соединена с подложкой.

Недостатком аналогов является низкое значение логического перепада выходных напряжений и относительно большое выходное сопротивление.

Наиболее близким техническим решением является интегральный выходной МДП-инвертор (Алексенко А. Г. , Шагурин И. И. Микросхемотехника/М. ; Радио и связь, 1982, с. 92, рис. 2.34), содержащий четыре МДП-транзистора с индуцированным n-каналом, затвор и сток первого из которых подключен к клемме источника питания и стоку второго МДП-транзистора, исток и подложка которого подключены к выходной клемме и стоку четвертого МДП-транзистора, исток и подложка которого подключены к общей шине и к истоку с подложкой третьего МДП-транзистора, затвор которого подключен к затвору четвертого МДП-транзистора и входной клемме, а сток - к истоку с подложкой первого МДП-транзистора и затвору второго МДП-транзистора. Такой инвертор имеет относительно низкое значение логической единицы на выходе устройства Uвых1 и большое выходное сопротивление, что затрудняет его эффективную работу при наличии емкостной нагрузки. Эти факторы и являются основными недостатками прототипа.

Цель изобретения - расширение функциональных возможностей за счет согласования с нагрузкой, особенно емкостной, при этом требуемый технический результат достигается за счет повышения логического перепада выходного напряжения (при постоянном напряжении источника питания Еп) и снижения выходного сопротивления устройства в интегральном выходном МДП-инверторе, содержащем четыре МДП-транзистора с индуцированным n-каналом, затвор и сток первого из которых подключены к клемме источника питания и стоку второго МДП-транзистора, затвор которого подключен к истоку первого МДП-транзистора и стоку третьего МДП-транзистора, затвор которого подключен к входной клемме и затвору четвертого МДП-транзистора, исток которого подключен к общей шине, а сток - к истоку второго МДП-транзистора и выходной клемме устройства, за счет того, что затвор второго МДП-транзистора соединен со своей подложкой, а исток третьего МДП-транзистора подключен к подложке четвертого МДП-транзистора.

За счет поступления управляющих сигналов не только на затворы, но и на подложки второго и четвертого МДП-транзисторов в них реализуется параллельное включение самих МДП-транзисторов и биполярных n-p-n-транзисторов, входящих в их структуры. Малые остаточные напряжения и сопротивления биполярных транзисторов позволяют увеличить логический перепад выходного напряжения и снизить выходное сопротивление устройства, чем и достигается улучшение согласования с нагрузкой.

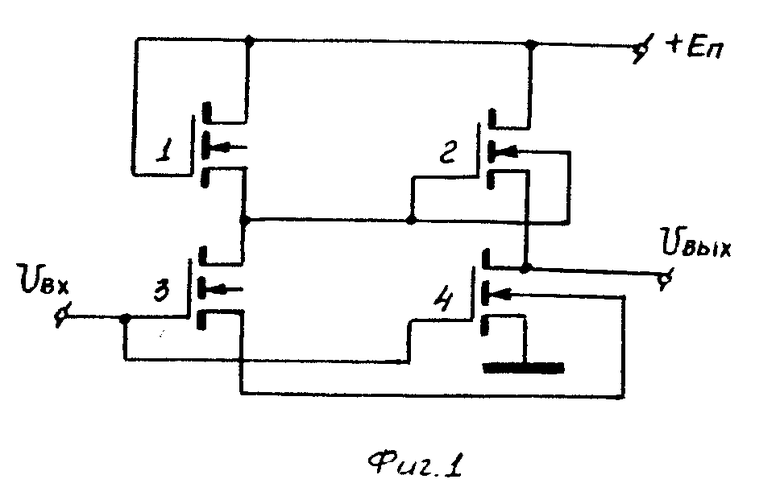

На фиг. 1 приведена принципиальная схема интегрального выходного МДП-инвертора, содержащая четыре МДП-транзистора с индукцированным n-каналом 1, 2, 3 и 4. Затвор и сток МДП-транзистора 1 подключены к стоку МДП-транзистора 2 и клемме источника питания. Входная клемма подключена к затворам МДП-транзисторов 3 и 4. Исток МДП-транзистора 1 подключен к затвору и подложке МДП-транзистора 2 и стоку МДП-транзистора 3, исток которого подключен к подложке МДП-транзистора 4. Исток МДП-транзистора 2 подключен к выходной клемме и стоку МДП-транзистора 4, исток которого подключен к общей шине. Подложки МДП-транзисторов 1 и 3 в зависимости от конкретных технических требований могут быть соединены со своими истоками или подключены к общей шине.

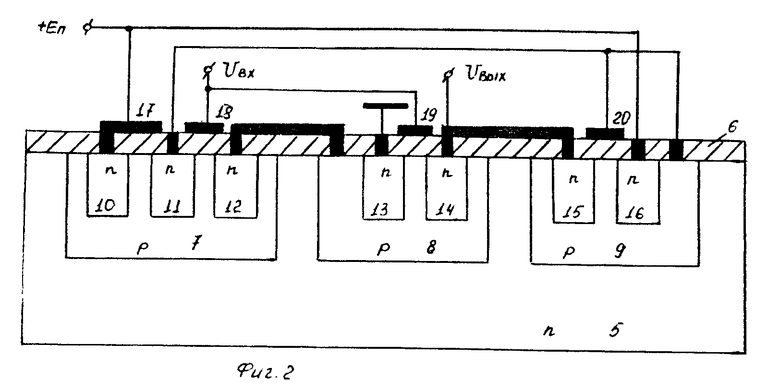

На фиг. 2 приведена конкретная реализация интегрального выходного МДП-инвертора и обозначено: полупроводниковая подложка n-типа 5, диэлектрик 6, диффузионные области p-типа 7, 8 и 9, диффузионные области n-типа 10 - 16, изолированные затворы 17 - 20. Области 10 и 11 с изолированным затвором 17 образуют МДП-транзистор 1, области 11 и 12 с изолированным затвором 18 образуют МДП-транзистор 3, области 13 и 14 с изолированным затвором 19 образуют МДП-транзистор 4, а области 15 и 16 с изолированным затвором 20 образуют МДП-транзистор 2.

Устройство работает следующим образом. При наличии на входной клемме сигнала логического нуля Uвх0 ≈0 МДП-транзисторы 3 и 4 закрыты. При этом на истоке МДП-транзистора 1 будет присутствовать напряжение, равное Еп - U01, где U01 - пороговое напряжение МДП-транзистора 1. Это напряжение поступает не только на затвор, но и на подложку МДП-транзистора 2. В результате МДП-транзистор 2 выполняет также функцию биполярного n-p-n-транзистора, базой которого является его подложка, коллектором - сток, а эмиттером - исток. Таким образом МДП-транзистор 2 совместно с МДП-транзистором 4 образует как истоковый, так и (параллельно включенный) эмиттерный повторители (с динамической нагрузкой). Это обстоятельство и приводит к практическому повторению на выходной клемме напряжения (Еп - U01) и уменьшению (относительно прототипа) выходного сопротивления устройства.

При поступлении на входную клемму положительного напряжения логической единицы Uвх1 МДП-транзисторы 3 и 4 открываются. При этом напряжение на истоке МДП-транзистора 1 резко снижается, что приводит к закрыванию МДП-транзистора 2. Поскольку исток МДП-транзистора 3 подключен к подложке МДП-транзистора 4, то МДП-транзистор 3 совместно с биполярным n-p-n-транзистором, входящим в структуру МДП-транзистора 4, образуют составной транзистор, входным элементом которого является МДП-транзистор 3, а выходным - биполярный транзистор 4. Поскольку сопротивление форсированно открытого биполярного транзистора (входящего в структуру МДП-транзистора 4) мало, то в этом режиме будет иметь место выходное напряжение Uвых0≈0 и малое выходное сопротивление устройства.

Снижение выходного сопротивления устройства позволяет успешно работать при наличии емкостной нагрузки (что обычно имеет место для выходных устройств), поскольку будет осуществляться ее быстрый перезаряд через малое Rвых. Это является основным преимуществом заявляемого устройства, позволяющим существенно повысить его быстродействие. Кроме того, увеличение логического перепада на выходе (за счет повышения Uвых1 и снижения Uвых0) приводит к повышению помехозащищенности.

Экспериментальная проверка выходного МДП-инвертора была проведена на дискретных МДП-транзисторах КР350, КП902 и лабораторных образцах. В отличие от прототипа заявляемое устройство позволило получить больший логический перепад на выходе ΔUвых и меньшее выходное сопротивление. Так, при Еп = 12 В в прототипе ΔUвых≈8 В и Rвых ≈1 кОм, а в заявляемом устройстве ΔUвых≈10 В и Rвых ≈30 Ом.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1992 |

|

RU2009602C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 1992 |

|

RU2009605C1 |

| ОДНОТАКТНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 1992 |

|

RU2009604C1 |

| МДП-инвертор | 1990 |

|

SU1780184A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 1992 |

|

RU2007829C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТРАНЗИСТОРОМ СО СТАТИЧЕСКОЙ ИНДУКЦИЕЙ | 1992 |

|

RU2006151C1 |

| МДП-инвертор | 1991 |

|

SU1803972A1 |

| Источник стабильного напряжения | 1988 |

|

SU1552156A1 |

| ВЫСОКОВОЛЬТНЫЙ ТРАНЗИСТОРНЫЙ КЛЮЧ | 1992 |

|

RU2006181C1 |

| Усилитель | 1990 |

|

SU1727193A1 |

Использование: изобретение относится к интегральной электронике в применении к цифровым схемам. Сущность изобретения: инвертор содержит четыре МДП-транзистора с индуцированным n-каналом. Затвор и сток первого транзистора подключены к клемме источника питания и стоку второго транзистора, затвор которого подключен к истоку первого МДП-транзистора и стоку третьего МДП-транзистора, затвор которого подключен к входной клемме и затвору четвертого транзистора, исток которого подключен к общей шине, а сток - к истоку второго транзистора и выходной клемме устройства. Затвор второго транзистора соединен со своей подложкой, а исток третьего транзистора подключен к подложке четвертого транзистора. 2 ил.

ИНТЕГРАЛЬНЫЙ ВЫХОДНОЙ МДП-ИНВЕРТОР, содержащий четыре МДП-транзистора с индуцированным n-каналом, расположенным в p-подложке, затвор и сток первого из которых подключены к клемме источника питания и стоку второго МДП-транзистора, затвор которого подключен к истоку первого МДП-транзистора и стоку третьего МДП-транзистора, затвор которого подключен к входной клемме и затвору четвертого МДП-транзистора, исток которого подключен к общей шине, а сток - к истоку второго МДП-транзистора и выходной клемме устройства, отличающийся тем, что затвор второго МДП-транзистора соединен со своей подложкой, а исток третьего МДП-транзистора подключен к подложке четвертого МДП-транзистора.

Авторы

Даты

1994-04-30—Публикация

1992-04-23—Подача