Изобретение относится к устройствам аналого-цифрового преобразования и может быть использовано в кардиологии, измерительной и вычислительной технике, телеметрических системах.

Известен следящий аналого-цифровой преобразователь (АЦП), содержащий блок сравнения, дешифратор генератор тактовых импульсов, делитель на два, ключи, источник опорного напряжения, два ЦАП, распределитель импульсов, элементы задержки, триггеры, реверсивный счетчик, элементы И, ИЛИ, регистр [1].

Данное устройство позволяет при определении величины следующего шага квантования учитывать предыдущее состояние АЦП. Это существенно усложняет АЦП, что ограничивает его применение.

Известен АЦП, содержащий входные клеммы, компаратор, ЦАП, источник опорного сигнала, тактовый генератор, реверсивный счетчик, выходную шину, выходы генератора и реверсивного счетчика и D-триггер [2].

Однако данное устройство имеет ограниченную область применения, что обусловлено наличием большой вероятности существенных локальных ошибок при работе в области предельных значений - ноль/максимум, так как в этом случае счетчик переполняется и формирует максимальное/минимальное (инверсное) число на выходе. Данное решение также не обеспечивает оптимальное по критериям Шеннона и Котельникова преобразование входного сигнала. Вероятность получения избыточных данных ограничивает область применения данного АЦП. Кроме того, данный АЦП решает ограниченный круг задач, так как отсутствует возможность обрабатывать сиг налы с составляющей вида U(t) = A , что обусловлено отсутствием выделения момента окончания-начала изменения входного сигнала.

, что обусловлено отсутствием выделения момента окончания-начала изменения входного сигнала.

Цель изобретения - расширение области применения за счет преобразования трапецеидальных сигналов.

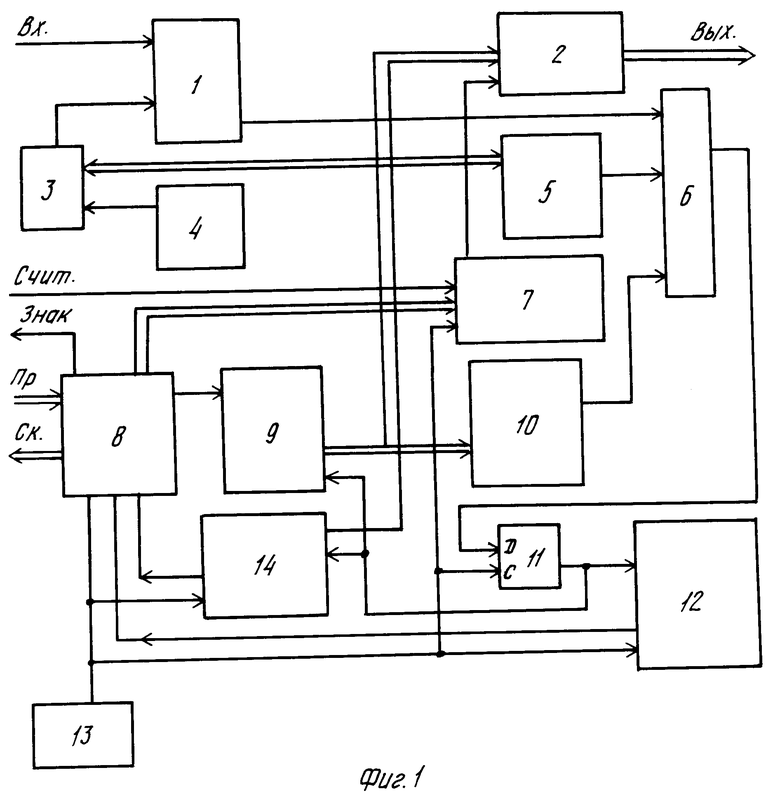

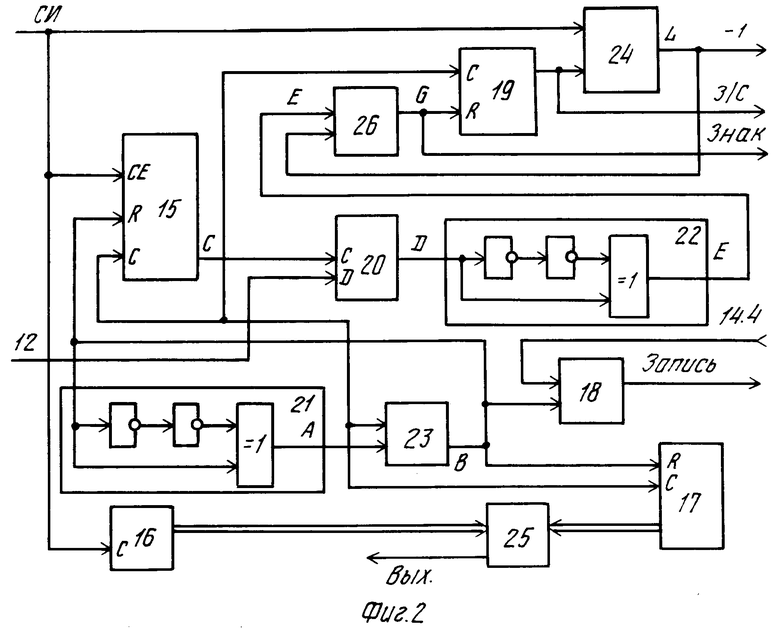

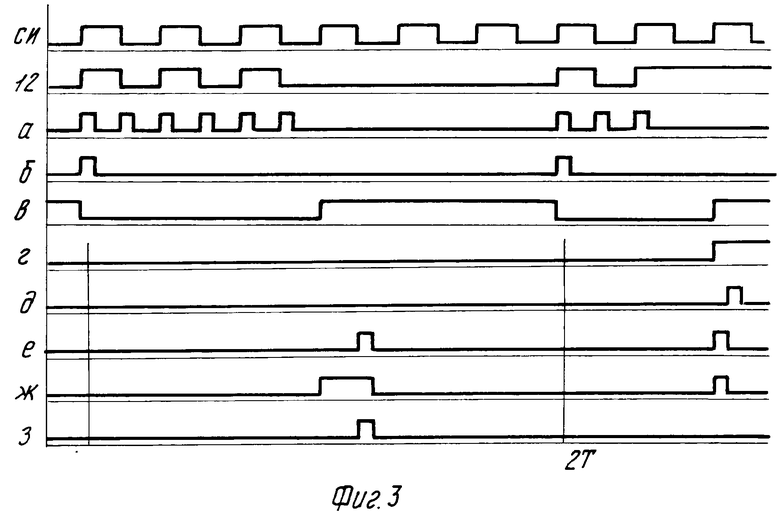

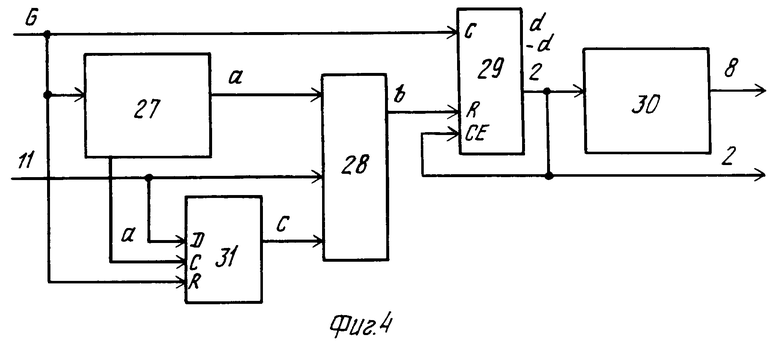

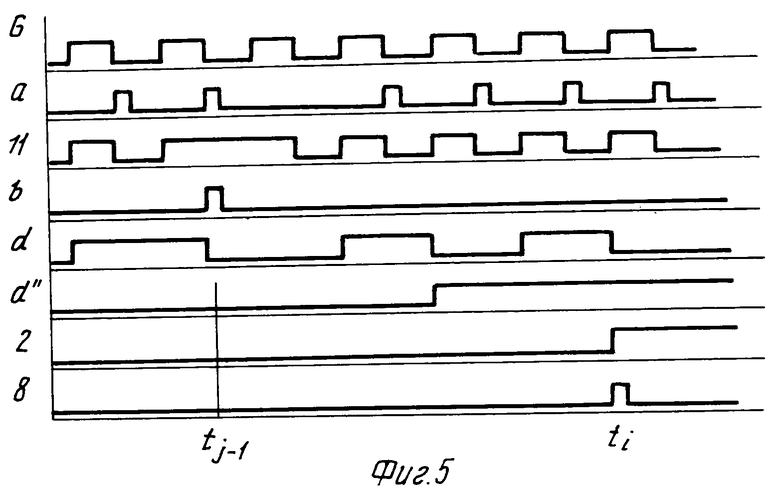

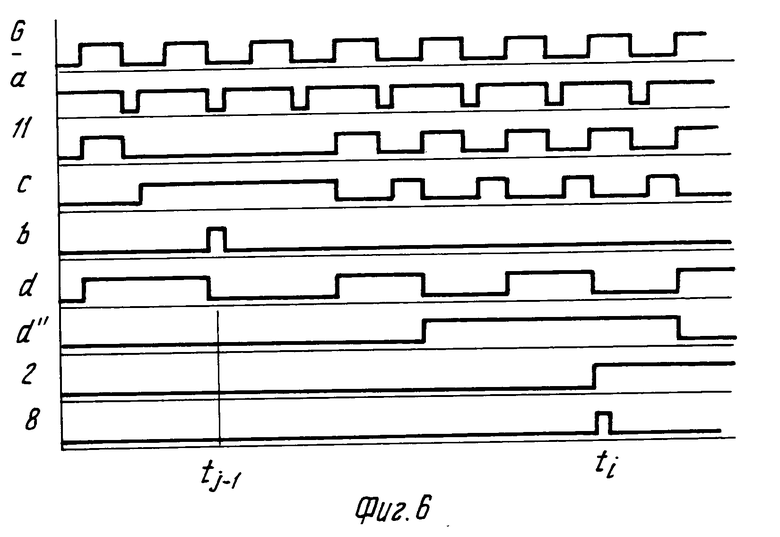

Структурная схема АЦП дана на фиг. 1; структурная схема блока адаптации к скорости изменения входного сигнала - на фиг. 2; временные диаграммы, поясняющие работу блока адаптации к скорости изменения входного сигнала, - на фиг. 3; схема блока выделения момента изменения входного сигнала - на фиг. 4; временные диаграммы, поясняющие его работу, - на фиг. 5 для случая содержания сигналом с триггера продолжительной логической "1" и 6 для случая содержания в составе сигнала с триггера продолжительного логического "0".

Устройство содержит компаратор 1, блок 2 памяти, ЦАП 3, источник 4 опорного сигнала, блок 5 оценки максимума, мажоритарный элемент 6, блок 7 управления памятью, блок 8 адаптации к скорости изменения входного сигнала, реверсивный счетчик 9, блок 10 оценки минимума, триггер 11, блок 12 оценки знака первой производной, генератор 13 тактовой частоты, блок 14 выделения момента изменения входного сигнала.

Блок 8 адаптации к скорости изменения входного сигнала (фиг. 2) содержит счетчики 15-17, элемент ИЛИ 18, триггеры 19 и 20, формирователи 21 и 22 импульсов, элементы И 23 и 24, мультиплексор 25, второй элемент ИЛИ 26.

Блок 14 выделения момента изменения входного сигнала (фиг. 4) содержит формирователь 27 импульсов по спаду входного сигнала, мажоритарный элемент 28, счетчик 29, формирователь 30 импульсов по фронту входного сигнала, D-триггер 31.

АЦП работает следующим образом.

В начальный момент времени до подачи входного сигнала на входной шине Вх нулевое напряжение. На входе ЦАП 3 формируется потенциал, величина которого на один квант превышает уровень нуля. Это определяется в соответствии с начальным числом реверсивного счетчика 9 и блока 10 оценки минимума и обеспечивает на выходе компаратора 1 логический "0". Первый импульс на входе реверсивного счетчика 9, сдвинутый во времени относительно импульса на входе триггера 11, записывается и переключает выход блока 5 оценки минимума в состояние "0". Это переводит реверсивный счетчик 9 в режим вычитания. Следующим импульсом генератора 13 с выхода блока 8 адаптации к скорости в реверсивном счетчике устанавливается начальное число и цикл повторяется. Счетчик 17 блока 8 адаптации к скорости формирует на управляющих входах мультиплексора 25 код для выбора верхней частоты со счетчика 16.

После увеличения уровня входного сигнала, превышающего величину кванта ЦАП 3, на выходе компаратора 1 формируется "1", что переводит реверсивный счетчик 9 в режим сложения. В результате увеличения числа на втором входе компаратора 1 устанавливается потенциал выше уровня входного сигнала и, как следствие, низкий уровень на выходе. Таким образом, цикл последовательного опроса входного сигнала путем сравнения с опорными потенциалами Больше-Меньше на один квант повторяется до момента изменения входного сигнала, т. е. постоянно поддерживается квазиравновесное состояние: уровень входного сигнала находится между двумя известными значениями, выполняя условие N + U < Uвх(Т) ≅ (N + 1) ˙ U, где N + U и (N + 1) ˙ U - смежные уровни ЦАП в моменты времени Т;

Uвх(Т) - уровень входного сигнала.

Если в процессе сравнения входной сигнал превышает уровень опорного кванта, то в реверсивный счетчик 9 дописывается (вычитается) "1" до тех пор, пока уровень опорного кванта (N + 1) не превысит Uвх. Блок 12 оценки знака первой производной выделяет последовательности из двух импульсов в каждом из режимов сложение/вычитание, что идентифицирует соответственно положительный/отрицательный знак первой производной входного сигнала с последующей фильтрацией верхних частот за счет селекции длительности входного импульса. Сигнал с блока 12 оценки знака производной поступает на блок 8 адаптации к скорости изменения входного сигнала - на формирователь 21 импульсов по фронту и спаду и D-вход триггера 20. Выходной сигнал (фиг. 3а) формирователя 21 импульсов через элемент И 23 обнуляет счетчики 15 и 17. Счетчик 17 этот импульс не фиксирует, так как на счетный вход он приходит раньше, чем на обнуляющий. Логический "0" на выходе счетчика 15 блокирует элемент И 23 и снимает блокировку на своем входе, что обеспечивает формирование импульсов. Длительность импульса определяется тактовой частотой генератора 13 по входу СИ (фиг. 2) и емкостью счетчика 15. Импульс с выхода элемента И 23 поступает на блок 7 и записывает в блок 2 памяти данные с выхода реверсивного счетчика 9 и сигнал с выхода блока 12 оценки знака производной.

В случае медленного изменения входного сигнала или наличия флуктуации во входном сигнале при конечной величине петли гестерезиса компаратора 1 замкнутая система следящего алгоритма вызывает формирование несанкционированных сигналов на выходе блока 12 оценки знака производной вида на фиг. 3. Емкость счетчика 15 выбрана такой, чтобы перекрыть несколько таких импульсов, каждый из которых записывается в счетчик 17. Следствием увеличения числа в счетчике 17 является уменьшение частоты на выходе мультиплексора 25, соответственно частоты формирования уровней Больше-Меньше на втором входе компаратора 1. Переполнение счетчика 15, т.е. формирование сигнала на выходе (фиг. 3в), опрашивает D-вход триггера 20 и фиксируется триггером 19, что обеспечивает подготовку блока 7 (фиг. 3ж) для стирания записанных данных в блок 2 памяти по одному предыдущему адресу и блокирует счетчик 15. Если начальный уровень (0/1) сигнала на выходе блока 12 сохраняется, т.е. изменения знака производной в сигнале не произошло, то сохраняется и начальное состояние триггера 20, формирователя 22 импульсов и элемента ИЛИ 26. Поэтому через 1/2 периода импульсов генератора (фиг. 3 СИ) на выходе элемента И формируется импульс ( фиг. 3з - "1") стирания предыдущей записи в момент времени 1Т и обнуления триггера 19. Таким образом выполнена подстройка схемы АЦП по частоте слежения за скоростью изменения входного сигнала без формирования данных с малой информативностью.

При формировании сигнала об изменении знака первой производной в момент времени 2Т блок 8 адаптации работает аналогично до момента опроса счетчиком 15 уровня входного сигнала на D-входе триггера 20. В результате опроса перепад на входе формирователя импульсов обнуляет триггер 19, что исключает формирование сигнала стирания на выходе элемента И 24 (фиг. 3е, д), а также обнуляет счетчик 17. Последнее однозначно исключает вероятность потери информации в случае увеличения скорости изменения входного сигнала до максимально допустимой, так как АЦП отслеживает его начало после изменения знака первой производной с максимальной частотой.

Информация о знаке первой производной входного сигнала формируется с задержкой на выходе триггера 20 (фиг. 3 г) в виде потенциала и выводится на вход АЦП. В совокупности с импульсным выходом он используется для синхронизации с внешними устройствами или для опроса, например, аналогичных АЦП при определении времени распространения процесса в исследуемом объекте или коэффициента корреляции между сигналами. Опрос данного АЦП производится по входу СЧИТ при помощи блока 7, осуществляющего фиксацию данных реверсивного счетчика 9 на выходе блока 2 памяти для последующей обработки.

В случае изменения входного сигнала в пределах одного кванта, что эквивалентно постоянному уровню или формированию трапецеидального сигнала, блоком 14 выделяются моменты для организации сигналов записи данных и идентификации факта начала ti или окончания tj-1d/dt = 0. Блок 14 работает по сигналам с триггера 11 (фиг. 4, 5 и 6), длительность которых проверяется задним фронтом тактовых импульсов при помощи элементов 27 и 28. Результат сравнения (фиг. 5b и 6b) в момент t обнуляет счетчик 29, который может, как показано на фиг. 5.2 и 6.2, идентифицировать факт d/dt=0. Последовательное, т. е. синхронное с тактовыми импульсами, формирование уровней Больше-Меньше на выходе триггера 11 (фиг. 5.11 и 6.11) в интервале tj-1 - ti подсчитывается счетчиком 29 (фиг. 5d и 6.d), который при переполнении заданной величины формирует на выходе (фиг. 5.2 и 6.2) перепад, который блокирует его, и выдается в блок 2. Момент начала (фиг. 5.8 и 6.8) формирования выделяется и используется блоком 8 для записи текущих данных в блок 2 наличия d/dt = 0 или посчитанное меньшее число.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ДИАГНОСТИКИ ПО ЭЛЕКТРОКАРДИОСИГНАЛУ И КОМПЛЕКС ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1999 |

|

RU2174824C2 |

| СИСТЕМА ДИАГНОСТИКИ ПО СТАТИЧЕСКОМУ НИЗКОЧАСТОТНОМУ СИГНАЛУ | 1997 |

|

RU2128843C1 |

| КОМПЛЕКС МНОГОКАНАЛЬНОЙ ЭКСПРЕСС ДИАГНОСТИКИ | 1997 |

|

RU2152073C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛА СЛОЖНОЙ ФОРМЫ | 1991 |

|

RU2022460C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ СИГНАЛА СЛУЧАЙНОГО ПРОЦЕССА | 1993 |

|

RU2072563C1 |

| СПОСОБ И УСТРОЙСТВО ЦИФРОВОЙ ДЕМОДУЛЯЦИИ ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2130695C1 |

| СПОСОБ ДИАГНОСТИКИ ПО СТАТИЧЕСКОМУ НИЗКОЧАСТОТНОМУ СИГНАЛУ | 1997 |

|

RU2129301C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ИНТЕРВАЛОВ ВРЕМЕНИ | 1991 |

|

RU2069888C1 |

| СПОСОБ ИДЕНТИФИКАЦИИ СИГНАЛА СЛУЧАЙНОГО ПРОЦЕССА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2097917C1 |

| УСТРОЙСТВО ВЫДЕЛЕНИЯ ОГИБАЮЩЕЙ СИГНАЛА СЛУЧАЙНОГО ПРОЦЕССА | 1996 |

|

RU2119189C1 |

Изобретение относится к области аналого-цифрового преобразования. Цель изобретения - расширение области применения за счет преобразования сигнала с составляющей вида  . Устройство для преобразования сигнала содержит компаратор, ОЗУ, ЦАП, источник опорного сигнала, блок оценки максимума, мажоритарный элемент, генератор тактовых импульсов, реверсивный счетчик, блок оценки минимума, триггер, блок оценки знака первой производной входного сигнала, входную шину, выход знака производной, выходную шину данных, которая через ОЗУ соединена с группой выходов реверсивного счетчика и соответствующими входами ЦАП, блока оценки максимума и блока оценки минимума, выходы которых через мажоритарный элемент соединены с информационным входом триггера, причем третий вход мажоритарного элемента соединен с входом устройства через компаратор, другой вход которого соединен с источником опорного сигнала через ЦАП, генератор тактовых импульсов соединен с первым входом блока оценки знака производной входного сигнала, а через второй вход триггера с другим его входом, блок запись-считывание, блок адаптации к скорости изменения входного сигнала, первый вход которого соединен с генератором тактовых импульсов, второй вход - с выходом блока оценки знака производной, а его выход соединен с другим входом реверсивного счетчика, группа выходом - с группой выходов устройства, группа управляющих входов соединена с группой входом блока адаптации к скорости входного сигнала, вторая группа выходов которого соединена с группой входов блока запись-считывание, один вход которого соединен с вторым входом триггера и генератором тактовых импульсов, второй - с вторым входом устройства, а группа выходов подключена к ОЗУ, блок выделения момента прекращения изменения начала изменения входного сигнала, первый вход которого соединен с генератором тактовых импульсов, второй вход - с выходом триггера, а первый его выход - с блоком адаптации к скорости изменения входного сигнала, второй выход - с группой информационных входов ОЗУ. 2 з.п.ф-лы, 6 ил.

. Устройство для преобразования сигнала содержит компаратор, ОЗУ, ЦАП, источник опорного сигнала, блок оценки максимума, мажоритарный элемент, генератор тактовых импульсов, реверсивный счетчик, блок оценки минимума, триггер, блок оценки знака первой производной входного сигнала, входную шину, выход знака производной, выходную шину данных, которая через ОЗУ соединена с группой выходов реверсивного счетчика и соответствующими входами ЦАП, блока оценки максимума и блока оценки минимума, выходы которых через мажоритарный элемент соединены с информационным входом триггера, причем третий вход мажоритарного элемента соединен с входом устройства через компаратор, другой вход которого соединен с источником опорного сигнала через ЦАП, генератор тактовых импульсов соединен с первым входом блока оценки знака производной входного сигнала, а через второй вход триггера с другим его входом, блок запись-считывание, блок адаптации к скорости изменения входного сигнала, первый вход которого соединен с генератором тактовых импульсов, второй вход - с выходом блока оценки знака производной, а его выход соединен с другим входом реверсивного счетчика, группа выходом - с группой выходов устройства, группа управляющих входов соединена с группой входом блока адаптации к скорости входного сигнала, вторая группа выходов которого соединена с группой входов блока запись-считывание, один вход которого соединен с вторым входом триггера и генератором тактовых импульсов, второй - с вторым входом устройства, а группа выходов подключена к ОЗУ, блок выделения момента прекращения изменения начала изменения входного сигнала, первый вход которого соединен с генератором тактовых импульсов, второй вход - с выходом триггера, а первый его выход - с блоком адаптации к скорости изменения входного сигнала, второй выход - с группой информационных входов ОЗУ. 2 з.п.ф-лы, 6 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Гнатюк Ю.Г | |||

| Справочник по аналого-цифровым и цифроаналоговым преобразователям | |||

| М.: Радио и связь, 1982, с.411, рис.5.79. | |||

Авторы

Даты

1994-11-30—Публикация

1990-11-26—Подача