Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики железнодорожного транспорта с безопасными отказами.

Известна схема парафазного триггера, содержащая логические элементы И-НЕ, образующие RS-триггеры [1].

Недостатком данного устройства является невозможность его применения для контроля сигналов, для которых допустимо однократное пропадание парафазности.

Наиболее близким техническим решением к изобретению является парафазный преобразователь, содержащий элементы памяти (RS-триггеры, выполненные по известной схеме на логических элементах И-НЕ), два входа контролируемых парафазных сигналов и два выхода, на которых в случае соблюдения парафазности входных сигналов обеспечивается присутствие парафазных сигналов [2].

Недостатком данного устройства является невозможность его применения для контроля сигналов, для которых допустимо однократное пропадание парафазности.

Задачей данного технического решения является обеспечение контроля двух импульсных сигналов, однократное пропадание одного из которых не является признаком отказа.

Поставленная задача реализуется следующим образом. Парафазный преобразователь содержит первый и второй сдвиговые регистры, входы записи которых соединены с первым и вторым входами устройства, входы тактовых импульсов - с выходом генератора импульсов, входы параллельной информации - с выходами соответствующих блоков постоянной взаимно инверсной информации, причем структура кода в этих блоках поразрядно взаимно инверсна, а выходы последних разрядов сдвиговых регистров являются соответственно первым и вторым выходами устройства, причем вход и выход инвертора соединены соответственно с выходом последнего разряда и с информационным входом последовательной записи первого сдвигового регистра, а информационный вход последовательной записи второго сдвигового регистра подключен к источнику постоянного нулевого сигнала. При этом используются сдвиговые регистры, выполненные на базе микросхем 533 ИР 9, инвертор и генератор импульсов, выполненные на базе микросхем 533 ЛН 1.

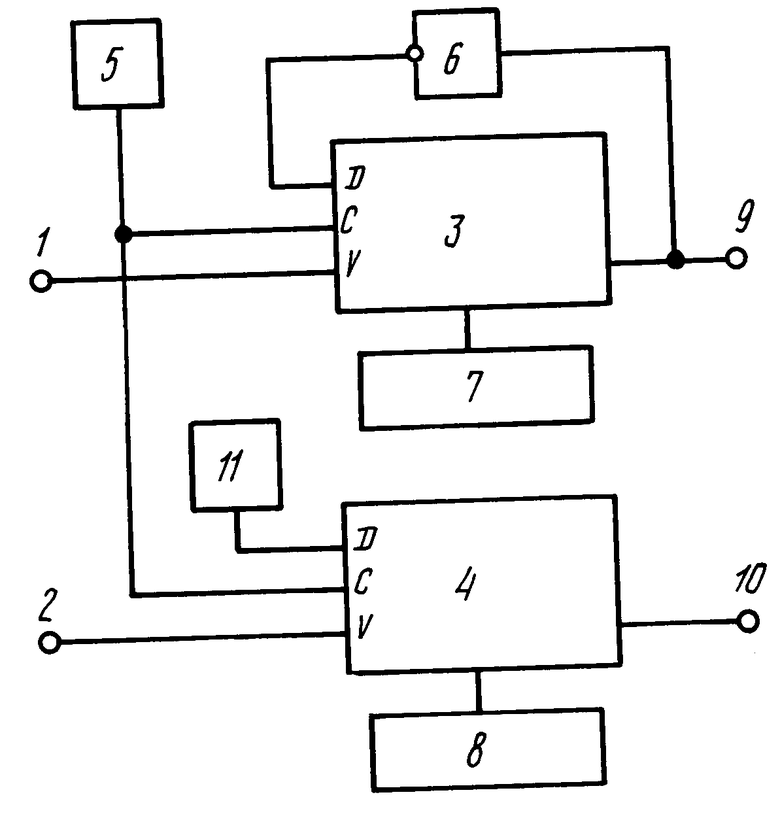

На чертеже представлена функциональная схема устройства.

Устройство содержит первый 1 и второй 2 входы, первый 3 и второй 4 сдвиговые регистры, генератор 5 импульсов, инвертор 6, первый 7 и второй 8 блоки постоянной взаимно инверсной информации, первый 9 и второй 10 выходы и источник 11 постоянной нулевой информации.

Первый 1 и второй 2 входы подключены к входам параллельной записи первого 3 и второго 4 сдвиговых регистров, выходы последних разрядов которых являются первым 9 и вторым 10 выходами устройства, генератор 5 соединен выходом с входами тактовых импульсов сдвиговых регистров 3 и 4, а инвертор 6 соединен входом с выходом последнего разряда регистра 3, а выходом - с информационным входом последовательной записи регистра 3. При этом входы параллельной информации регистров 3 и 4 подключены к соответствующим блокам 7, 8 постоянной информации, причем структура кода в этих блоках взаимно инверсна, а первый информационный вход последовательной записи второго регистра 4 подключен к источнику 11.

В нормальном режиме работы на входы устройства поступают два коротких импульса, которые производят запись в регистры 3 и 4 информации, установленной в блоках 7 и 8. На тактовые входы регистров поступают импульсы от генератора 5, частота которых обратно пропорциональна допускаемому количеству пропадания входных импульсов, а требуемый сдвиг регистра определяется по формуле

S = (1/n + 1) ˙100% где n - число пропаданий. Таким образом в соответствии с изложенным в случае допуска одного пропадания регистр сдвигается на половину своей разрядности (50%), для двух - 32%, для трех - 25% и т.д. За счет того, что информация в блоках 7 и 8 поразрядно взаимно инверсна, на выходах старших разрядов регистров и на выходах 9 и 10 устройства поддерживаются парафазные сигналы.

В случае однократного пропадания одного (одновременного пропадания обоих) из входных импульсов не происходит обновления информации в регистрах 3 и 4, но за счет того, что за время между входными импульсами регистр сдвинул информацию только, например, на половину своей разрядности, на выходах 9 и 10 устройства поддерживаются парафазные сигналы до прихода следующего входного импульса.

Если происходит длительное пропадание входного импульса, происходит нарушение парафазности на выходах 9 и 10 устройства, что обусловлено нарушением взаимно инверсной информации в сдвиговых регистрах 3 и 4 за счет работы инвертора 6 и источника нулевой информации 11.

В случае нарушения логики работы какого-либо блока устройства также происходит нарушение парафазности сигнала на выходах 9 и 10.

Изобретение относится к импульсной технике. Задача технического решения - обеспечение контроля двух импульсных сигналов, однократное пропадание одного из которых не является признаком отказа. Устройство содержит первый 1 и второй 2 выходы, первый 3 и второй 4 сдвиговые регистры, генератор импульсов 5, инвертор 6, первый 7 и второй 8 блоки постоянной информации, первый 9 и второй 10 выходы и источник постоянной нулевой информации 11. Первый 1 и второй 2 входы подключены к входам параллельной записи первого 3 и второго 4 сдвиговых регистров, выходы последних разрядов которых являются первым 9 и вторым 10 выходами устройства, генератор импульсов 5 соединен выходом с входами тактовых импульсов сдвиговых регистров 3 и 4, а инвертор 6 соединен входом с выходом последнего разряда регистра 3, а выходом - с информационным входом последовательной записи регистра 3. При этом входы параллельной информации регистров 3 и 4 подключены к соответствующим 7, 8 блокам постоянной информации, причем структура кода в этих блоках поразрядно взаимно инверсна, а первый информационный вход последовательной записи второго регистра 4 подключен к источнику постоянного нулевого сигнала 11. 1 ил.

ПАРАФАЗНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий первый и второй входы, первый и второй элементы памяти, первый и второй выходы, отличающийся тем, что в него введены инвертор, генератор импульсов, источник постоянного нулевого сигнала, первый и второй блоки постоянной взаимоинверсной информации, а элементы памяти выполнены в виде сдвиговых регистров, при этом входы записи первого и второго сдвиговых регистров являются первым и вторым входами преобразователя, выходы последних разрядов - первым и вторым выходами преобразователя, входы тактовых импульсов соединены с выходом генератора импульсов, входы параллельной информации регистров - с выходами первого и второго блоков постоянной взаимоинверсной информации, вход и выход инвертора соединены соответственно с выходом последнего разряда первого регистра и информационным входом последовательной записи первого регистра, информационный вход последовательной записи второго регистра соединен с источником постоянного нулевого сигнала.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с.99, рис.4-10. | |||

Авторы

Даты

1995-02-27—Публикация

1992-06-05—Подача