Изобретение относится к импульсной технике и может быть использовано в различных системах автоматики, например, на железнодорожном транспорте.

Известен логический элемент, содержащий выходной выпрямитель, диодный мост, первая диагональ которого подключена к первому и второму информационным входам логического элемента, а во вторую диагональ последовательно с входным элементом узла гальванической развязки включен коллекторно-эмиттерный переход транзистора, выходной элемент узла гальванической развязки подключен к входу усилителя [1].

Однако данное устройство имеет недостаточную надежность при дефектах электрической схемы.

Наиболее близким техническим решением к изобретению является логический элемент, содержащий диодный мост, соединенный диагональю переменного тока с первым и вторым информационными входами, первый конденсатор, первый узел гальванической развязки на оптроне, диод, преобразователь полярности, выполненный на основе последовательно соединенных первом и втором диодах, точка соединения которых подключена к первому выводу конденсатора, причем первый конденсатор подсоединен одним концом к аноду диода, задающий генератор, соединенный через первый резистор развязывающей цепи с базой первого транзистора, которая через второй резистор развязывающей цепи соединена со вторым входом развязывающей цепи, второй транзистор, база которого через базовый резистор соединена с его эмиттером и минусовым входом диодного моста, а через выходную цепь второго узла гальванической развязки - с полюсовым выходом диодного моста, цепь запуска, вход которой является входом запуска устройства, а выход соединен с одним выводом второго конденсатора и одним выводом первого резистора [2].

Недостатками данного устройства являются

появление ложного выходного сигнала при возбуждении усилителя;

при появлении утечек в узле гальванической развязки на оптроне на входе усилителя и изменение пороговых свойств последнего;

отсутствие защиты от ложного сигнала на первом и втором информационных входах;

недостаточность порогового стабильного сигнала по первому и второму информационным входам из-за разбросов падения напряжения на цепи коллектор-эмиттер транзистора и входе узла гальванической развязки, в емкости конденсатора в цепи обратной связи логического элемента, что приводит к накоплению дефектов.

Задачей изобретения являются исключение появления ложного выходного сигнала при отказах электрической схемы и генерация сигналов на логических входах.

Поставленная задача реализуется следующим образом. В логический элемент, содержащий первый диодный мост, который диагональю переменного тока соединен с первым и вторым информационными входами, первый конденсатор, первый узел гальванической развязки на оптроне, диод, преобразователь полярности, выполненный на последовательно соединенных первом и втором диодах, точка соединения которых подключена к первому выводу первого конденсатора, задающий генератор, первый транзистор, второй транзистор, база которого через базовый резистор соединена с плюсовым выходом первого диодного моста, а через выходной элемент второго узла гальванической развязки на оптроне - с минусовым выходом первого диодного моста, цепь запуска, вход которой является входом запуска устройства, введены второй диодный мост, третий транзистор с базовым и коллекторным резисторами, точка соединения которых подключена к плюсовому выходу второго диодного моста, коллектор второго транзистора через коллекторный резистор соединен с плюсовым выходом первого диодного моста, коллектор первого диодного моста, а через выходной элемент второго узла гальванической развязки на оптроне - с минусовым выходом первого диодного моста, цепь запуска, вход которой является входом запуска устройства, введены второй диодный мост, третий транзистор с базовым и коллекторным резисторами, точка соединения которых подключена к плюсовому выходу второго диодного моста, коллектор второго транзистора через коллекторный резистор соединен с плюсовым выходом первого диодного моста, коллектор первого транзистора через два последовательно соединенных коллекторных резисторов подключен к первой шине питания, третий узел гальванической развязки на оптроне, выходной элемент которого является выходом устройства, и второй конденсатор, первым выводом соединенным с входом запуска, а вторым с общей шиной первого и второго информационных входов. При этом база второго транзистора через выходной элемент второго узла гальванической развязки на оптроне соединена с его эмиттером, первый вывод первого конденсатора подключен к катоду второго диода преобразователя полярности, а второй вывод - к коллектору второго транзистора, коллектор третьего транзистора соединен с вторым выводом конденсатора преобразователя полярности, входной элемент первого узла гальванической развязки на оптроне первым выводом подключен к эмиттеру четвертого транзистора, а вторым - к общей шине, база третьего транзистора через выходной элемент первого узла гальванической развязки на оптроне подключена к эмиттеру третьего транзистора, катоду диода и минусовым выходам первого и второго диодных мостов. Выход цепи запуска соединен с первыми выводами базового и коллекторного резисторов четвертого транзистора и анодом первого диода преобразователя полярности, задающий генератор соединен через первый резистор с базой первого транзистора, точка соединения коллекторных резисторов первого транзистора подключена через второй резистор к базе и к второму выводу базового резистора четвертого транзистора. Коллектор четвертого транзистора через последовательно соединенные входные элементы второго и третьего узлов гальванической развязки на оптроне соединен с общей шиной, при этом минусовые выходы первого и второго диодных мостов и их диагонали переменного тока объединены, а эмиттер первого транзистора подключен к общей шине. При этом третий и четвертый транзисторы выполнены на базе ПРП, а узлы гальванической развязки - на оптронотранзисторной паре.

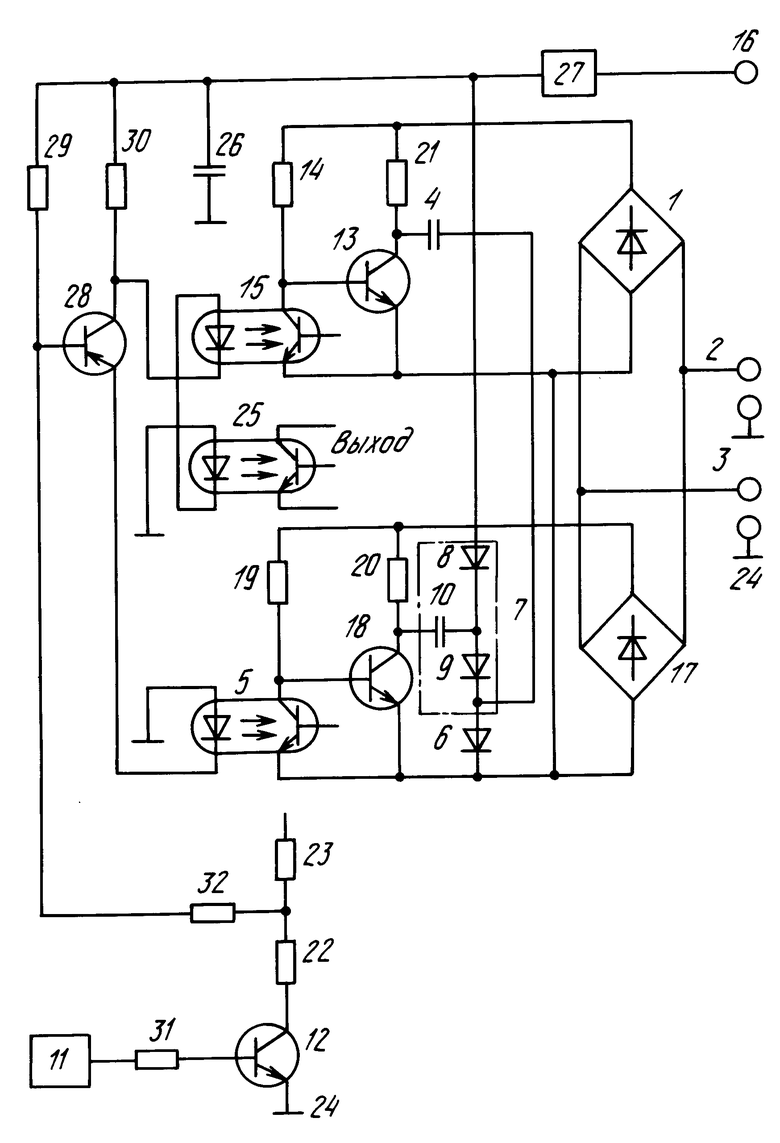

На чертеже представлена принципиальная схема логического элемента.

Логический элемент содержит первый диодный мост 1, соединенный диагональю переменного тока с первым 2 и вторым 3 информационными входами, первый конденсатор 4, первый узел гальванической развязки на оптроне 5, диод 6, преобразователь 7 полярности, выполненный на основе последовательно соединенных первом 8 и втором 9 диодах, точка соединения которых подключена к первому выводу конденсатора 10, причем первый конденсатор 4 подсоединен первым выводом к аноду диода 6 и катоду второго диода 9 преобразователя полярности 7, задающий генератор 11. Кроме того, в состав логического элемента входит первый транзистор 12, второй транзистор 13, база которого через базовый резистор 14 соединена с минусовым выходом первого диодного моста 1, а через выходной элемент второго узла гальванической развязки на оптроне 15 - с минусовым выходом первого диодного моста 1, цепь запуска 16, вход которой является входом запуска устройства. Логический элемент имеет второй диодный мост 17, третий транзистор 18 с базовым 19 и коллекторным 20 резисторами, точка соединения которых подключена к плюсовому выходу второго диодного моста 17, коллектор второго транзистора 13 через коллекторный резистор 21 соединен с плюсовым выходом первого диодного моста 1. Коллектор первого транзистора 12 через два последовательно соединенных коллекторных резистор 22 и 23 подключен к первой шине питания 24, третий узел гальванической развязки на оптроне 25, выходной элемент которого является выходом устройства, и второй конденсатор 26, первым выводом соединенный с входом 27 запуска, а вторым - с общей шиной первого 2 и второго 3 информационных входов. База второго транзистора 13 через выходной элемент второго узла гальванической развязки на оптроне 15 соединена с его эмиттером. Второй вывод первого конденсатора 4 подключен к коллектору второго транзистора 13. Коллектор третьего транзистора 18 соединен с вторым выводом конденсатора 10 преобразователя 7. Входной элемент первого узла гальванической развязки на оптроне 5 первым выводом подключен к эмиттеру четвертого транзистора, а вторым - к общей шине 24. База третьего транзистора 18 через выходной элемент первого узла гальванической развязки на оптроне 5 подключена к эмиттеру третьего транзистора 18, катоду диода 6 и минусовым выходам первого 1 и второго 17 диодных мостов. Выход цепи 27 запуска соединен с первыми выводами базового 29 и коллекторного 30 резисторов четвертого транзистора 28 и анодом первого диода 8 преобразователя полярности 7. Задающий генератор 11 соединен через первый резистор 31 с базой первого транзистора 12. Точка соединения коллекторных резисторов 22 и 23 первого транзистора 12 подключена через второй резистор 32 к базе и второму выводу базового резистора 29 четвертого транзистора 28. Коллектор четвертого транзистора 28 через последовательно соединенные входные элементы второго 15 и третьего 25 узлов гальванической развязки на оптроне соединен с общей шиной 24. Минусовые выходы первого 1 и второго 17 диодных мостов и их диагонали переменного тока объединены, а эмиттер первого транзистора 5 подключен к общей шине 24.

Устройство работает следующим образом.

Входные информационные сигналы поступают синхронно и противофазно на информационные входы 2 и 3 относительно общей шины 22 источника (питание на схеме не показано). При их противофазной работе на диагоналях переменного тока диодных мостов I и II присутствуют сигналы, обеспечивающие на диагоналях постоянного тока этих же мостов постоянное напряжение для обеспечения питания соответствующих каскадов усиления, выполненных на втором 13 и третьем 18 транзисторах с соответствующими коллекторными резисторами 21 и 20. Управление каскадами осуществляется через первый 5 и второй 15 узлы гальванической развязки на оптронах. Второй узел 15 гальванической развязки на оптроне обеспечивает закрытие и выключение второго 13 транзистора (открытие обеспечивает базовый резистор 14), а первый узел 5 гальванической развязки на оптроне обеспечивает закрытие и выключение третьего транзистора 18 (открытие обеспечивает базовый резистор 19).

Рассмотрим работу схемы с момента подачи сигнала через вход запуска 16 устройства на цепь запуска, при этом на ее выходе и соответственно на емкости второго конденсатора 26 появляется отрицательный потенциал, который через коллекторный резистор 30 поступает на коллектор четвертого транзистора 28, а через базовый резистор 29 поступает на базу транзистора 28, который выполнен по схеме с общим эмиттером, как насыщенный ключ, запирание которого обеспечивается динамическим положительным сигналом задающего генератора 11, поступающим через первый резистор 31 на транзистор 12, и с делителя, выполненного на резисторах 22, 23, через резистор 32.

Общая точка цепи 27 запуска конденсатора 26, резисторов 29 и 30 является одновременно цепью питания входных цепей узлов гальванической развязки на оптронах 15 и 25 и четвертого транзистора 28. При этом, если в этой точке уровень отрицательного напряжения обеспечивает протекание через входную цепь узла 5 гальванической развязки, на оптроне рабочего тока третий транзистор 18 закрывается и открывается второй транзистор 13, входная цепь узла гальванической развязки которого зашунтирована открытым четвертым транзистором 28, условием этого является открытие первого транзистора 12. Если последний открывается, то делитель на резисторах 22, 23 обеспечивает в точке их соединения уровень положительного напряжения меньше требуемого порога запирания четвертого транзистора 28 через второй резистор 32, вследствие чего четвертый транзистор 28 открывается через базовый резистор 29. При закрытии первого транзистора 12 сигналом генератора 11 через первый резистор 31 уровень положительного потенциала в точке соединения резисторов 22 и 23 делителя возрастает и через второй резистор 32 запитает четвертый транзистор 28, закрывает входную цепь первого узла 5 гальванической развязки на оптроне и открывает третий транзистор 18, соответственно снимает шунтирование с входных цепей узлов гальванической развязки на оптронах 5, 25 и закрывает второй транзистор 13. Таким образом, переменное положение сигнала от задающего генератора 11 при наличии отрицательного заряда на емкости второго конденсатора 26 обеспечивает периодическое закрытие второго 13 и третьего 18 транзисторов, а также динамический выходной сигнал на выходе третьего узла 25 гальванической развязки на оптроне. Такой режим работы второго 13 и третьего 18 транзисторов обеспечивает их противофазную работу и заряд первого конденсатора 4 через диод 6 и коллекторный резистор 21 второго транзистора 13 до напряжения на выходе диагонали постоянного тока диодного моста 1. Конденсатор 10 преобразователя 7 заряжается через коллекторный резистор 20 третьего транзистора 18 одним полюсом до потенциала постоянного тока на выходе второго диодного моста 17, а через второй диод 9 преобразователя 7 - до отрицательного потенциала, накопленного на первом конденсаторе 4. Таким образом, конденсатор 10 преобразователя 7 при противофазной работе второго 13 и третьего 18 транзисторов обеспечивает умножение напряжения (приблизительно в 1,6 раза), которое через первый диод 8 преобразователя 7 поступает на второй конденсатор 26. В этом случае первоначальная подача через цепь 27 отрицательного потенциала обеспечивает прохождение динамического сигнала от задающего генератора 11 через транзисторные каскады второго 13 и третьего 18 транзисторов и преобразователя 7 для цепи подпитки второго конденсатора 26 после снятия отрицательного запускающего сигнала. Это обеспечивает нормальный режим работы схемы.

В случае если появляется рассогласование сигналов на первом 2 и втором 3 информационных входах, на выходах диодных мостов 1 и 17 на величину этого рассогласования пропадает напряжение питания каскадов второго 13 и третьего 18 транзисторов, которое соответственно не обеспечивает заряд конденсатора 10 преобразователя 7 и первого конденсатора 4 и подзаряд второго конденсатора 26, который через резистор 30, последовательно соединенные входные элементы узлов гальванической развязки на оптронах 15 и 25 и через последовательно соединенные четвертый транзистор 28 и входной элемент первого узла 5 гальванической развязки на оптроне разрежается, тем самым блокируя все устройства в выключенном состоянии до прихода нового сигнала запуска.

Ложная генерация второго 13 и третьего 18 транзисторов или генерация в первом 2 и втором 3 информационных входах не обеспечивает оптимальных режимов заряда конденсатора 10 преобразователя 7 и первого конденсатора 4. Соответственно уровень на втором конденсаторе 26 недостаточен для нормальной работы устройства, т.е. меньше пороговых свойств, задаваемых параллельно подключенными цепями, состоящими из последовательно включенных второго 15 и третьего 25 узлов гальванической развязки на оптронах в одной цепи и последовательно включенных четвертого транзистора 28 и первого узла 5 гальванической развязки в другой цепи, тем самым исключается ложный выходной сигнал при этих дефектах.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1991 |

|

RU2009612C1 |

| СИМИСТОРНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1996 |

|

RU2100895C1 |

| СПОСОБ УПРАВЛЕНИЯ МАГНИТНО-ТРАНЗИСТОРНЫМ КЛЮЧОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1989 |

|

RU2006180C1 |

| Датчик состояния вентилей реверсивного тиристорного преобразователя | 1991 |

|

SU1787303A3 |

| Датчик состояния вентилей реверсивного тиристорного преобразователя | 1991 |

|

SU1767610A2 |

| Способ искробезопасного дистанционного питания и устройство для его осуществления | 1985 |

|

SU1305398A1 |

| Логический элемент | 1984 |

|

SU1236605A1 |

| ПОЕЗДНОЕ УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ С РЕГУЛИРОВАНИЕМ СКОРОСТИ | 1996 |

|

RU2120393C1 |

| ФОРМИРОВАТЕЛЬ ИНФРАНИЗКОЧАСТОТНЫХ ИМПУЛЬСОВ | 1998 |

|

RU2132112C1 |

| Система шахтной телемеханики с временным разделением каналов и дистанционным питанием | 1980 |

|

SU1012447A1 |

Изобретение относится к импульсной технике и предназначено для исключения появления ложного сигнала при отказах электрической схемы и генерации сигналов на логических входах. Устройство содержит два диодных моста, два входа 2, 3, два конденсатора 4, 19, три узла гальванической развязки на оптронах 5, 14 и 32, один диод 6, один преобразователь полярности 7 на двух диодах 8, 9 и одном конденсаторе 10, 1 задающий генератор 11, 4 транзистора 12, 13, 23, 28, 10 резисторов 15, 16, 20, 21, 24, 25, 27, 29, 30, 31, одну цепь запуска 17. 1 ил.

ЛОГИЧЕСКИЙ ЭЛЕМЕНТ, содержащий первый диодный мост, который диагональю переменного тока соединен с первым и вторым информационными входами, первый конденсатор, первый узел гальванической развязки на оптроне, диод, преобразователь полярности, выполненный на последовательно соединенных первом и втором диодах, точка соединения которых подключена к певому выводу конденсатора преобразователя полярности задающий генератор, первый транзистор, второй транзистор, база которого через базовый резистор соединена с плюсовым выходом первого диодного моста, а через выходной элемент второго узла гальванической развязки на оптроне - с минусовым выходом первого диодного моста, цепь запуска, вход которой является входом запуска логического элемента, отличающийся тем, что в него введены второй диодный мост, третий транзистор с базовым и коллекторным резисторами, точка соединения которых подключена к плюсовому выходу второго диодного моста, коллектор второго транзистора через коллекторный резистор соединен с плюсовым выходом первого диодного моста, коллектор первого транзистора через первый и второй последовательно соединенные коллекторные резисторы подключен к первой шине питания, третий узел гальванической развязки на оптроне, выходной элемент которого является выходом логического элемента, и второй конденсатор, первый вывод которого соединен с выходом цепи запуска, а второй вывод - с общей шиной первого и второго информационных входов, база второго транзистора через выходной элемент второго узла гальванической развязки на оптроне соединена с его эмиттером, первый вывод первого конденсатора подключен к катоду второго диода преобразователя полярности, а второй вывод - к коллектору второго транзистора, коллектор третьего транзистора соединен с вторым выводом конденсатора преобразователя полярности, входной элемент первого узла гальванической развязки на оптроне первым выводом подключен к эмиттеру четвертого транзистора, а вторым - к общей шине, база третьего транзистора через выходной элемент первого узла гальванической развязки на оптроне подключена к эмиттеру третьего транзистора, катоду диода и минусовым выходам первого и второго диодных мостов, выход цепи запуска соединен с первыми выводами базового и коллекторного резисторов четвертого транзисторов и анодом первого диода преобразователя полярности, задающий генератор соединен через первый резистор с базой первого транзистора, точка соединения коллекторных резисторов которого подключена через второй резистор к базе и второму выводу базового резистора четвертого транзистора, коллектор которого через последовательно соединенные входные элементы второго и третьего узлов гальванической развязки на оптронах соединен с общей шиной, при этом диагонали переменного тока первого и второго диодных мостов объединены, а эмиттер первого транзистора подключен к общей шине.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Логический элемент | 1984 |

|

SU1236605A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-03-10—Публикация

1992-06-05—Подача