Изобретение относится к радиоэлектронике и может быть использовано в различных вычислительных устройствах при обработке информации в разнообразных радиолокационных, радионавигационных и вычислительных системах.

Наиболее близким к предлагаемому является оптический страничный преобразователь для оптоэлектронного запоминающего устройства, содержащий оптический сумматор и блок формирования частного. Основными недостатками данного устройства являются относительно невысокие быстродействие и надежность, а также его громоздкость.

Техническим результатом является повышение быстродействия, надежности, компактности, а также упрощение конструкции устройства.

Это достигается тем, что в оптический цифровой многоканальный делитель, содержащий оптический сумматор и блок формирования частного, введены блоки формирования единиц и нулей, блоки ввода делителя и делимого, оптические вентили с первого по четвертый, управляемый оптический инвертор, оптический блок анализа сочетания знаков, оптический разветвитель, причем вход блока ввода делителя является для цифрового делителя входом страницы делителей, входом страницы делимых которого является вход блока ввода делимого, выход которого оптически связан с первым входом первого оптического вентиля, второй вход которого оптически связан с выходом управляемого оптического инвертора, первый вход которого оптически связан с общим выходом блока ввода делителя, выход знаковых разрядов которого оптически связан с первым входом оптического блока анализа сочетания знаков, второй вход которого оптически связан с выходом знаковых разрядов оптического сумматора, первый вход которого оптически связан с первым выходом первого оптического вентиля, второй выход которого оптически связан со входом n-го разряда оптического сумматора, первый выход которого оптически связан с третьим входом первого оптического вентиля, третий выход первого оптического вентиля оптически связан со вторым входом оптического сумматора, выход оптического блока анализа сочетания знаков оптически связан со входом оптического разветвителя, первый выход которого оптически связан со вторым входом управляемого оптического инвертора, второй выход оптического разветвителя оптически связан с первым входом второго оптического вентиля, второй вход которого оптически связан с выходом блока формирования единиц, выход второго оптического вентиля оптически связан со входом n-го разряда блока формирования частного, общий вход которого оптически связан с первым выходом третьего оптического вентиля, второй выход которого оптически связан с третьим входом второго оптического вентиля, первый вход третьего оптического вентиля оптически связан с выходом блока формирования нулей, второй вход третьего оптического вентиля оптически связан с первым выходом четвертого оптического вентиля, вход которого оптически связан с выходом блока формирования частного, второй выход четвертого оптического вентиля является оптическим выходом делителя.

Данная совокупность существенных признаков и связей между ними позволяет получить устройство, обладающее более чем в 10 - 100 раз большим быстродействием, надежностью, а также меньшими габаритами по сравнению с прототипом.

Сущность изобретения заключается в том, что организация в делителе параллельного сдвига операндов, а также использование оригинальных схем оптического инвертирования и оптического анализа сочетания знаков операндов позволили построить делитель на основе нетрадиционного оптического алгоритма вычисления частного без восстановления остатка, за счет чего и удалось достигнуть вышеуказанные результаты.

Таким образом, предложенный делитель обладает свойствами, не присущими известным устройствам. Это объясняется новой совокупностью существенных признаков и новыми связями, изложенными выше.

Сравнение предлагаемого блока с известными свидетельствует о соответствии его критерию "новизна", а отсутствие в аналогах отличительных признаков предлагаемого устройства - о соответствии критерию "изобретательский уровень".

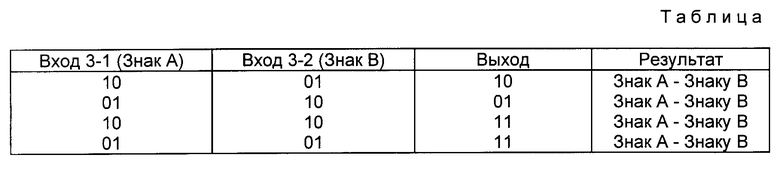

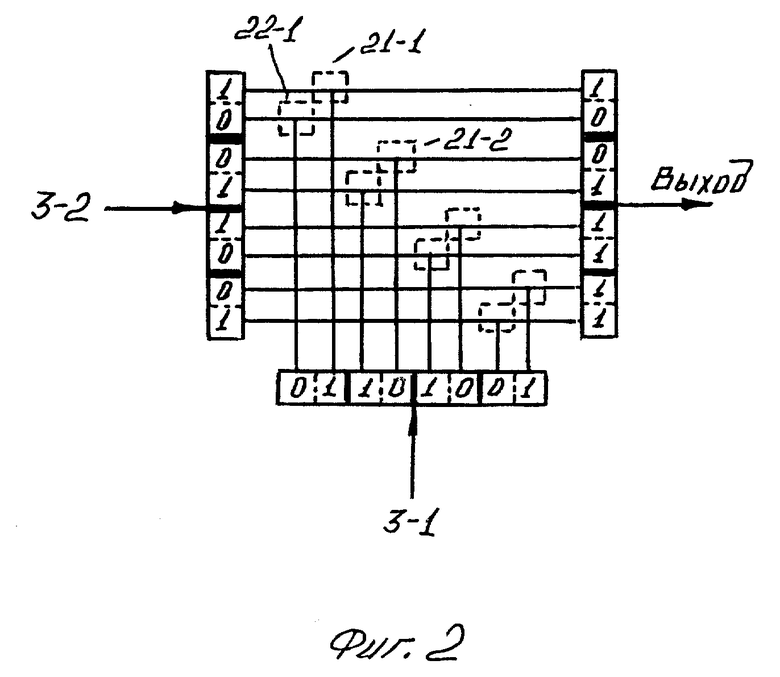

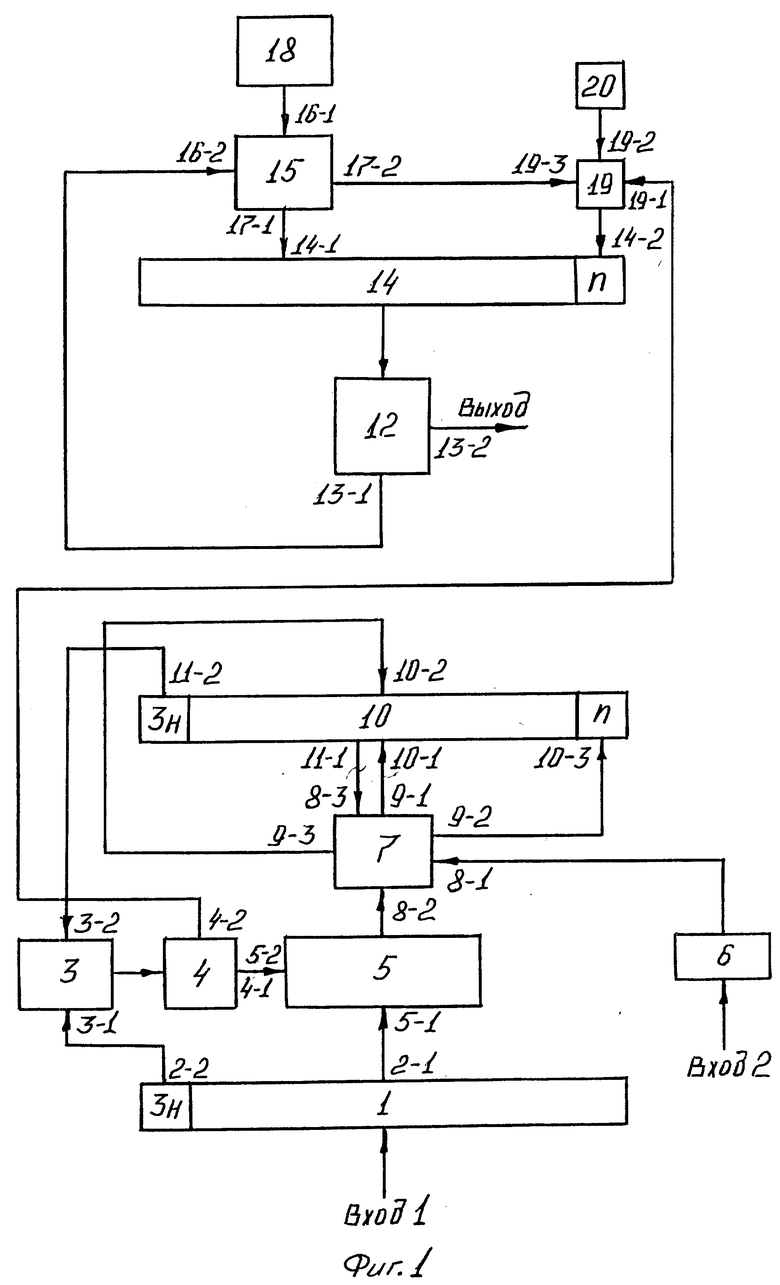

На фиг. 1 приведена схема оптического цифрового многоканального делителя; на фиг. 2 - схема оптического блока анализа сочетания знаков; на фиг. 3 - блок-схема алгоритма деления, реализуемый делителем.

Оптический цифровой многоканальный делитель содержит блок ввода делителя 1, имеющий общий выход 2-1 и выход знаковых разрядов 2-2, оптический блок анализа сочетания знаков 3, имеющий входы 3-1, 3-2, оптический разветвитель 4, имеющий выходы 4-1, 4-2, управляемый оптический инвертор 5, имеющий входы 5-1, 5-2, блок ввода делимого 6, оптический вентиль 7, имеющий входы 8-1... 8-3 и выходы 9-1...9-3, оптический сумматор 10, имеющий первый 10-1 и второй 10-2 входы и вход n-го разряда 10-3, общий выход 11-1 и выход знаковых разрядов 11-2, оптический вентиль 12, имеющий выходы 13-1, 13-2, блок формирования частного 14, имеющий общий вход 14-1 и вход n-го разряда 14-2, оптический вентиль 15, имеющий входы 16-1, 16-2 и выходы 17-1, 17-2, блок формирования нулей 18, оптический вентиль 19, имеющий входы 19-1 ... 19-3, и блок формирования единиц 20.

Блок ввода делителя 1 предназначен для ввода в делитель страницы делителей в виде оптических парафазных сигналов, в том числе с преобразованием их из электрических. При электрическом вводе страницы делителя блок 1 может состоять из связанных между собой электрической памяти, например на регистрах и матрицы лазерных диодов, а при оптическом вводе на входе блока 1 дополнительно устанавливается матрица фотоприемников.

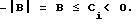

Оптический блок анализа сочетания знаков 3 выполняет функцию анализа знаков делимого (операнд A) и делителя (операнд B) по следующему правилу, представленному в таблице.

Блок 3 может быть выполнен, например, на фиг. 2 в виде групп оптических объединителей 21, 22, каждая из которых содержит два световодных объединителя 21-i и 22-i (где i = 1, 2, 3...), имеющих по два входных порта и по одному выходному, причем входные порты каждого световодного объединителя каждой группы являются входами разноименных полуячеек соответствующих парафазных знаков на одноименных входах блока.

Оптический разветвитель 4 предназначен для размножения оптических сигналов и может быть выполнен, например, в виде матрицы волоконнооптических или интегральнооптических разветвителей.

Управляемый оптический инвертор 5 предназначен для преобразования кода слов в странице делителя в соответствии с управляющими сигналами, поступаемыми с блока 3. Инвертор 5 может, например, состоять из управляемого элемента - растра переключателей поляризации с оптически управляемым входом, на выходе которого расположен поляризационный разветвитель, образующий каналы прямой и инверсной передачи оптических сигналов. В первом из них расположен жгут с регулярной укладкой световодов, во втором - нерегулярной, при которой каждые два световода, передающие один и тот же парафазный знак, на выходе жгута меняются местами.

Блок ввода делимого 6 предназначен для ввода в делитель страницы делимых в виде оптических парафазных сигналов, в том числе с преобразованием их из электрических. При электрическом вводе страницы делимого блок 6 может быть выполнен, например, в виде матрицы лазерных диодов, а при оптическом - в виде матрицы световодных шин.

Оптический вентиль 7 служит для переключения оптических сигналов и может быть выполнен, например, на основе волоконнооптических или интегральнооптических разветвителей и объединителей.

Оптический сумматор 10 предназначен для суммирования страниц операндов и может быть выполнен, например, на основе волоконнооптических и интегральнооптических элементов.

Оптический вентиль 12 предназначен для вывода результата вычисления из устройства и может быть выполнен на основе управляемого оптического переключателя или управляемого волоконнооптического или интегральнооптического разветвителя.

Блок формирования частного 14 служит для формирования результата от деления двух страниц операндов и может быть выполнен, например, в виде связанных между собой матриц лазерных диодов, электронных триггеров и фотоприемников.

Оптический вентиль 15 служит для переключения оптических сигналов и может быть выполнен, например, на основе волоконнооптических или интегральнооптических разветвителей и объединителей.

Блок формирования нулей 18 предназначен для формирования страницы нулей для ввода начальных данных и может состоять, например, из оптически связанных между собой лазерного диода, фокона и маски (например, фототрафарета) страницы парафазных нулей.

Оптический вентиль 19 служит для переключения оптических сигналов при записи информации в n-й разряд блока 14. Вентиль 19 может быть выполнен, например, на основе волоконнооптических или интегральнооптических объединителей.

Блок формирования единиц 20 предназначен для записи парафазных единиц в n-й разряд блока 14 и может состоять, например, из оптически связанных между собой лазерного диода, фокона и маски (например, фототрафарета) парафазных единиц.

Оптический цифровой делитель выполняет операции деления страниц двоичных чисел с фиксированной точкой, причем на знаки делимого и делителя не накладываются никакие ограничения: отрицательные делимое или делитель задаются в дополнительном коде. Делитель реализует описанный ниже алгоритм деления без восстановления остатка.

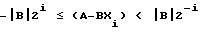

Пусть частное X от деления двух чисел произвольного знака - делимого A и делителя B, удовлетворяющих условию:

равно

X = A/B = x0, x-1x-2 ... x-ix-(i+1)...,

где

x-1, x-2, . .. x-i, x-(i+1) ... равны либо 1, либо  , а

, а  обозначает цифру, равную "-1".

обозначает цифру, равную "-1".

В каждом цикле очередная цифра частного определяется из условия, чтобы приближенное значение частного Xi, составленное из цифры x0 и i старших разрядов после запятой, удовлетворяло неравенству

или введя обозначение

Ci = (A - BXi)2i

получим

Предположим, что перед началом цикла, в котором определяется цифра частного x-(i+1), известно приближенное значение частного X, и, следовательно, величина Ci, удовлетворяющая неравенству (5). Цифра x-(i+1) может иметь два возможных значения:  и 1.

и 1.

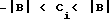

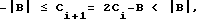

Тогда, если  , то

, то

Xi+1 = Xi-2-(i+1)

Ci+1 = 2Ci + B

И необходимо, чтобы выполнялось условие

которое при положительном делителе  эквивалентно:

эквивалентно:

-B ≤ Ci < 0,

а при отрицательном делителе  эквивалентно условию

эквивалентно условию

0 ≤ Ci < -B

Условия (9) и (10) означают, что знак Ci [sign Ci], но должен совпадать со знаком делителя

signCi ≠ signB

Если же x-(i+1) = 1, то

Xi+1 = Xi + 2-(i+1)

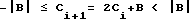

То необходимо, чтобы выполнялось условие ,

,

которое при положительном делителе  эквивалентно условию

эквивалентно условию

0 ≤ Ci < B,

а при отрицательном делителе  эквивалентно условию

эквивалентно условию

Условия (13) и (14) означают, что знак Ci должен совпадать со знаком делителя B

signCi = signB.

Таким образом, в процессе выполнения деления можно ограничиться проверкой неравенства (9) при положительном делителе, считая что при его невыполнении справедливо неравенство (11), или проверкой неравенства (10) при отрицательном делителе, считая что при его невыполнении справедливо неравенство (14).

Следовательно, каждая цифра частного может быть определена за два такта: в первом Ci сдвигается влево, т.е. преобразуется в 2Ci и одновременно знак Ci сопоставляется со знаком делителя, во втором в случае совпадения знаков в частное записывается 1 и для выработки Ci+1 делитель вычитается из 2Ci; в случае несовпадения знаков в частное записывается  и для выработки Ci+1 делитель прибавляется к 2Ci.

и для выработки Ci+1 делитель прибавляется к 2Ci.

Исходными данными для всей операции деления, т.е. для ее первого цикла, должны являться

X0 = signA/B

C0 = A - BsignA/B

X0 можно определить по соотношению знаков делимого и делителя, а C0 - путем добавления к делимому делителя, если их знаки не совпадают, или вычитания из делимого делителя, если их знаки совпадают.

Для определения исходных данных для деления нужно выполнить такие же операции, как и для определения каждой последующей цифры частного.

Из неравенств (9), (10), (14) следует, что погрешность частного, вычисленного описанным выше способом, может с одинаковой вероятностью оказаться и положительной и отрицательной, а предельное ее значение по модулю равно единице младшего разряда, т. е. 2-n. Таким образом, такой вычислительный процесс автоматически обеспечивает округление результата.

Преобразование кода частного, состоящего из цифр 1 и  , в двоичный код, выраженный через 1 и 0, можно осуществить путем замены всех знаков

, в двоичный код, выраженный через 1 и 0, можно осуществить путем замены всех знаков  на 0, сдвига на один разряд влево с пропаданием старшего разряда и записи единицы в n-й разряд кода частного после запятой. Такое преобразование можно совместить с определением цифр 1 и

на 0, сдвига на один разряд влево с пропаданием старшего разряда и записи единицы в n-й разряд кода частного после запятой. Такое преобразование можно совместить с определением цифр 1 и  . Для этого нужно, выполняя вышеописанный алгоритм определения цифр 1 и

. Для этого нужно, выполняя вышеописанный алгоритм определения цифр 1 и  , каждый раз вместо цифры 1 записывать в соседний левый разряд 1, а вместо цифры

, каждый раз вместо цифры 1 записывать в соседний левый разряд 1, а вместо цифры  записывать в соседний левый разряд 0. В первом цикле нужно осуществить только передачу делимого в сумматор прямым или инверсным кодом в зависимости от сочетания знаков делимого и делителя, не записывая перед этим цифру в частное, т.к. она должна была бы попасть в отбрасываемый разряд двоек. После окончания n циклов определения цифр частного, начиная от x0 и кончая xn-1, в последний разряд частного нужно записать xn = 1.

записывать в соседний левый разряд 0. В первом цикле нужно осуществить только передачу делимого в сумматор прямым или инверсным кодом в зависимости от сочетания знаков делимого и делителя, не записывая перед этим цифру в частное, т.к. она должна была бы попасть в отбрасываемый разряд двоек. После окончания n циклов определения цифр частного, начиная от x0 и кончая xn-1, в последний разряд частного нужно записать xn = 1.

Устройство работает в соответствии с приведенным выше алгоритмом деления, который для наглядности представлен в виде блок-схемы на фиг. 3.

Отметим, что ввод в блок формирования частного 14 начального значения частного в первом такте и единицы в младший его разряд в n-ом такте осуществляется с помощью соответственно блока формирования единиц 20.

Сдвиги влево на один разряд в сумматоре 10 и блоке 14 осуществляются за счет такой параллельной передачи их информационного содержания с выходов на входы соответственно с помощью вентиля 7 и вентилей 12, 15, при которой старшие разряды теряются, в младший разряд сумматора со входа 2 вводится нуль ("01"), а младший разряд блока 14 заполняется блоком 3.

Использование изобретения позволит реализовать оптическими цифровыми методами операцию деления в различных вычислительных устройствах, увеличивая в 10 - 100 раз их быстродействие, надежность и компактность. Такие устройства могут широко применяться в разнообразных радиолокационных, радионавигационных и вычислительных системах.

Изобретение относится к вычислительной технике и радиоэлектронике. Техническим результатом является повышение быстродействия, надежности, компактности, а также упрощение конструкции устройства. Такие результаты достигнуты организацией в делителе параллельного сдвига операндов, а также использованием оригинальных схем оптического инвертирования и оптического анализа сочетания знаков операндов, что позволило построить делитель на основе нетрадиционного оптического алгоритма вычисления частного без восстановления остатка. Оптический цифровой многоканальный делитель содержит блок ввода делителя, оптический блок анализа сочетания знаков, оптический разветвитель, управляемый оптический инвертор, блок ввода делимого, оптические вентили, оптический сумматор, блок формирования единиц. Данный делитель может широко применяться в разнообразных радиолокационных, радионавигационных и вычислительных системах увеличивая в 10-100 раз их быстродействие, надежность и компактность. 1 табл., 3 ил.

Оптический цифровой многоканальный делитель, содержащий оптический сумматор и блок формирования частного, отличающийся тем, что введены блоки формирования единиц и нулей, блоки ввода делителя и делимого, оптические вентили с первого по четвертый, управляемый оптический инвертор, оптический блок анализа сочетания знаков, оптический разветвитель, причем вход блока ввода делителя является для цифрового делителя входом страницы делителей, входом страницы делимых которого является вход блока ввода делимого, выход которого оптически связан с первым входом первого оптического вентиля, второй вход которого оптически связан с выходом управляемого оптического инвертора, первый вход которого оптически связан с общим выходом блока ввода делителя, выход знаковых разрядов которого оптически связан с первым входом оптического блока анализа сочетания знаков, второй вход которого оптически связан с выходом знаковых разрядов оптического сумматора, первый вход которого оптически связан с первым выходом первого оптического вентиля, второй выход которого оптически связан с входом n-го разряда оптического сумматора, первый выход которого оптически связан с третьим входом первого оптического вентиля, третий выход первого оптического вентиля оптически связан с вторым входом оптического сумматора, выход оптического блока анализа сочетания знаков оптически связан с входом оптического разветвителя, первый выход которого оптически связан с вторым входом управляемого оптического инвертора, второй выход оптического разветвителя оптически связан с первым входом второго оптического вентиля, второй вход которого оптически связан с выходом блока формирования единиц, выход второго оптического вентиля оптически связан с входом n-го разряда блока формирования частного, общий вход которого оптически связан с первым выходом третьего оптического вентиля, второй выход которого оптически связан с третьим входом второго оптического вентиля, первый вход третьего оптического вентиля оптически связан с выходом блока формирования нулей, второй вход третьего оптического вентиля оптически связан с первым выходом четвертого оптического вентиля, вход которого оптически связан с выходом блока формирования частного, второй выход четвертого оптического вентиля является оптическим выходом цифрового делителя.

| ОПТИЧЕСКИЙ СТРАНИЧНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ОПТОЭЛЕКТРОННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1984 |

|

SU1225397A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1972 |

|

SU424145A1 |

| EP 0330710 А1, 06.09.89. | |||

Авторы

Даты

1998-07-20—Публикация

1997-02-17—Подача