Изобретение относится к технике асинхронной коммутации пакетов информации в сетях передачи данных, в каждом физическом канале которых данные передаются в одном направлении в виде коротких пакетов информации и поступают к включенным в линию связи узлам коммутации (соответственно и к приемным устройствам пользователей сети) последовательно во времени. Изобретение предназначено для использования в сетях связи, обеспечивающих передачу цифровых данных, видео- и речевой информации с помощью одного и того же оборудования, не требующего единого процессора для коммутации пакетов информации, с децентрализованным управлением коммутацией и упрощенным программным обеспечением.

Известно устройство асинхронной коммутации пакетов информации, описанное в монографии (Ларионов А.М., Майоров С.А., Новиков Г.И. - Вычислительные комплексы, системы и сети. - Л. Энергоатомиздат, 1987. стр. 209-210, рис. 6.18). Первый вход известного устройства коммутации ("Передаваемые биты" на рис.6.18) соединен с первым входом селектора, выход которого является выходом устройства коммутации, второй вход селектора соединен с выходом блока задержки, вход которого является вторым входом устройства коммутации. Управляющий вход селектора соединен с выходом блока управления селектором ("Управление селектором").

Указанное известное устройство коммутации предназначено для работы в кольцевых сетях. С помощью селектора в этом устройстве коммутации осуществляется передача (коммутация) на выход устройства коммутации пакетов информации, поступающих либо на первый, либо на второй вход устройства коммутации. При этом управление коммутацией (селектором) осуществляется сигналами от блока управления селектором. Блок управления селектором в данном случае работает по способу так называемого эстафетного доступа с маркером для кольцевых структур (стр. 206 вышеупомянутой монографии Ларионова А.М. и др.), требующего централизованного управления доступом (то есть и коммутацией). При этом требуется наличие в сети одной или нескольких систем формирования маркера, а в каждом устройстве коммутации - блока управления селектором, реализующего функции по распознаванию маркера, изыманию его из кольцевого моноканала сети, отправке в моноканал передаваемого пакета информации, принятии этого вернувшегося по кольцевому моноканалу пакета информации и последующему прекращению передачи.

Недостатком известного устройства асинхронной коммутации является наличие одной или нескольких систем централизованного формирования маркера, при выходе из строя которых сеть теряет работоспособность, ограниченность числа пользователей сети и ограниченная протяженность сети, сложность аппаратуры и программного обеспечения каждого устройства коммутации и сети в целом, составленной из таких устройств коммутации.

Наиболее близким к изобретению по первому варианту является устройство асинхронной коммутации пакетов информации, приведенное в описании к патенту США N 4768190, H 04 J 3/00 (фиг.6, колонка 8 описания). В указанном источнике доступ пользователя 100 (нумерация здесь соответствует описанию прототипа) к кольцевой линии связи 30 осуществляется с помощью схемы доступа 82, включающей устройство асинхронной коммутации пакетов информации, состоящее из управляемого проходного буфера 134, вход которого, соответствующий входу 30 схемы 82, является вторым входом устройства асинхронной коммутации пакетов информации, и управляемый передающий буфер 146, вход которого (from transit buffers) является первым входом указанного устройства. Выходы буферов 134 и 146 объединены и являются выходом устройства. Устройство асинхронной коммутации содержит также блок управления 136, осуществляющий функции определения наличия пакета информации в каждом из упомянутых буферов и управления выдачей пакетов из буферов на выход устройства. Управляющие входы указанных буферов соединены с соответствующими выходами указанного блока управления. Устройство по патенту США содержит также блок 142 выделения тактовых импульсов из поступающего на вход устройства пакета информации. Вход блока 142 соединен с входом 30 схемы 82, то есть практически (через регистр 130) - с вторым входом рассматриваемого устройства асинхронной коммутации пакетов информации. Выход блока 142 соединен с соответствующим входом (CLK) блока управления 136, через который осуществляется синхронизация ввода и вывода пакетов информации из проходного буфера 134 (управляющий, он же тактовый вход-выход PTBC) и синхронизация ввода и вывода пакетов информации из передающего буфера 146 (управляющий и тактовый вход-выход TBC). То есть выход блока 142 выделения тактовых импульсов практически постоянно соединен с тактовыми входами проходного 134 и передающего 146 буферов.

Ввод и вывод пакетов информации из проходного регистра 134 и передающего регистра 146 производятся на одной и той же тактовой частоте, источником которой является блок 142. Пакет информации, поступающий на вход устройства коммутации, помещается в управляемый проходной буфер 134, где задерживается на время, не меньшее длительности пакета информации, и передается на выход устройства во время отсутствия передачи на выход устройства пакета информации из управляемого передающего буфера 146. Пакет информации из управляемого передающего буфера 146 передается на выход устройства в том случае, если управляемый проходной буфер 134 не содержит пакета информации. Так обеспечивается коммутация и бесконфликтная передача на выход устройства коммутации пакетов информации, асинхронно поступающих на его входы.

Недостатком указанного устройства асинхронной коммутации является возможность недопустимого взаимодействия следующих друг за другом пакетов информации в том случае, если последующий пакет информации появляется на входе управляемого проходного буфера, когда из него еще не выведен предыдущий пакет информации, то есть при промежутках времени между принимаемыми пакетами информации, меньшими длительности пакета информации. В общем случае указанные пакеты информации, генерируемые разными пользователями сети, имеют или не совпадающие значения тактовых частот или несинфазность этих частот. При этом происходит сбой при выводе из проходного буфера предыдущего пакета информации и соответствующая потеря информации. Увеличение промежутков времени между передаваемыми по линии связи пакетами информации для устранения указанного недостатка снижает как минимум в два раза эффективность использования линии связи, а уменьшение промежутков времени между передаваемыми по линии связи пакетами информации для повышения эффективности использования линии связи ведет к увеличению вероятности указанных потерь информации.

Задачей изобретения по первому варианту является повышение надежности работы линии связи при одновременном повышении эффективности ее использования.

Для решения указанной задачи в известное устройство асинхронной коммутации пакетов информации, первый вход которого соединен с входом управляемого передающего буфера, выход которого является выходом устройства асинхронной коммутации, содержащее также управляемый проходной буфер, выход которого соединен с выходом устройства асинхронной коммутации, блок выделения тактовых импульсов, вход которого соединен с вторым входом устройства, и блок управления осуществляющий функции определения наличия пакета информации в каждом из упомянутых буферов и управления выдачей пакетов из буферов, причем управляющие входы и выходы состояния указанных буферов соединены с соответствующими выходами и входами указанного блока управления, введены по крайней мере один дополнительный управляемый проходной буфер, узел координации, осуществляющий по командам блока управления функцию подачи каждого поступающего на второй вход устройства коммутации пакета информации на вход одного из управляемых проходных буферов, а также генератор тактовых импульсов и по крайней мере один переключатель тактовых импульсов, при этом блоку управления приданы функции определения наличия пакета информации в каждом из дополнительных управляемых проходных буферов, управления подачей пакетов информации в каждый из проходных буферов и подачи тактовых импульсов на каждый из проходных буферов, причем управляющие входы и выходы состояния каждого из дополнительных проходных буферов соединены с соответствующими выходами и входами блока управления, выход блока выделения тактовых импульсов соединен с первым входом каждого из переключателей тактовых импульсов, выход генератора тактовых импульсов соединен с вторым входом каждого из переключателей тактовых импульсов, выход каждого переключателя тактовых импульсов соединен с тактовым входом одного из управляемых проходных буферов, а управляющий вход каждого из переключателей тактовых импульсов соединен с соответствующим выходом блока управления.

Кроме того, в указанном устройстве асинхронной коммутации пакетов информации узел координации, осуществляющий по командам блока управления функцию подачи каждого поступающего на второй вход узла коммутации пакета информации на вход одного из управляемых проходных буферов, выполнен в виде управляемого селектора, имеющего один вход и количество выходов, равное числу имеющихся в узле асинхронной коммутации управляемых проходных буферов, второй вход узла асинхронной коммутации соединен с входом указанного селектора, каждый из выходов селектора соединен с входом одного из управляемых проходных буферов, а управляющий вход указанного селектора соединен с соответствующим выходом блока управления.

Введение в известное устройство асинхронной коммутации вышеуказанных по крайней мере одного дополнительного управляемого проходного буфера, узла координации, генератора тактовых импульсов и по крайней мере одного переключателя, а также придание блоку управления функции определения наличия пакета информации в каждом из дополнительных управляемых проходных буферов, управления подачей пакетов информации в каждый из проходных буферов и подачи тактовых импульсов на каждый из проходных буферов при указанном соединении (взаимодействии) друг с другом всех элементов устройства обеспечивает подачу каждого поступающего на вход устройства пакета информации в свободный управляемый проходной буфер и вывод пакетов информации из проходных буферов на разных тактовых частотах. Новым техническим результатом изобретения является исключение взаимовлияния следующих друг за другом пакетов информации с промежутками времени между принимаемыми пакетами информации, меньшими длительности пакетов информации, что повышает надежность работы линии связи, а также эффективность ее использования за счет обеспечения возможности сокращения промежутков времени между пакетами информации.

Выполнение узла координации в виде вышеуказанного управляемого селектора при соответствующем его соединении с другими элементами устройства асинхронной коммутации является одним из возможных исполнений изобретения по первому варианту.

Наиболее близким к изобретению по второму варианту является устройство асинхронной коммутации пакетов информации, приведенное также в описании к вышеуказанному патенту США N 4768190, H 04 J 3/00 (фиг.6). Первый вход (from transit buffers) рассматриваемого устройства соединен с входом управляемого передающего буфера 146 (нумерация здесь указана по патенту США), выход которого является выходом устройства асинхронной коммутации, содержащего также приемный 130 и проходной 134 буферы, один из которых (здесь - буфер 134) осуществляет задержку пакета информации на время, не меньшее его передачи, то есть выполнен с числом разрядов, не меньшим количества бит пакета информации. Выход проходного буфера 134 соединен с выходом устройства асинхронной коммутации, а вход - с выходом приемного буфера 130, вход которого соединен с вторым входом 30 устройства. Вход блока 142 выделения тактовых импульсов соединен с вторым входом 30 устройства, а выход - с тактовым входом приемного буфера 130 и блока управления 136. Блок управления 136 осуществляет функцию определения наличия пакета информации в передающем буфере 146 и одном из двух других буферов (здесь - в буфере 134) и функцию управления выдачей пакета информации из передающего буфера 146 и из проходного буфера 134. Управляющий вход передающего буфера 146, а также выходы состояния передающего буфера (ТВС) и одного из двух других буферов (РТВС для проходного буфера 134) соединены с соответствующими выходом и входами указанного блока управления. В описанном устройстве приемный буфер 130 выполнен на регистре сдвига, преобразующем последовательный код в параллельный, а проходной буфер 146 выполнен в виде параллельного регистра.

Недостатком указанного устройства асинхронной коммутации также является возможность недопустимого взаимодействия следующих друг за другом пакетов информации в том случае, если последующий пакет информации появляется на входе управляемого проходного буфера, когда из него еще не выведен предыдущий пакет информации, то есть при промежутках времени между принимаемыми пакетами информации, меньшими длительности пакета информации.

Задачей изобретения по второму варианту является повышение надежности работы линии связи при одновременном повышении эффективности ее использования.

Для решения указанной задачи в известное устройство асинхронной коммутации пакетов информации, первый вход которого соединен с входом управляемого передающего буфера, выход которого является выходом устройства асинхронной коммутации, содержащее также приемный и проходной буферы, последний из которых выполнен с числом разрядов, не меньшим количества бит пакета информации, при этом выход проходного буфера соединен с выходом устройства асинхронной коммутации, в вход - с выходом приемного буфера, вход которого соединен с вторым входом устройства, блок выделения тактовых импульсов, вход которого соединен с вторым входом устройства, а выход - с тактовым входом приемного буфера, и блок управления, осуществляющий функцию определения наличия пакета информации в передающем буфере и функцию управления выдачей пакета информации из передающего буфера, причем управляющий вход передающего буфера, а также выходы состояния передающего буфера и одного из двух других буферов соединены с соответствующими выходами - входами указанного блока управления, введен генератор тактовых импульсов, приемный буфер выполнен с числом разрядов, не меньшим количества бит пакета информации, блоку управления придана функция определения наличия пакета информации в приемном буфере и переноса (записи) указанного пакета в проходной буфер, выход генератора тактовых импульсов соединен с тактовыми входами проходного и передающего буферов, а выход состояния приемного буфера соединен с соответствующим входом блока управления.

Устройство асинхронной коммутации пакетов информации по второму варианту изобретения отличается также тем, что приемный буфер выполнен в виде преобразователя последовательного кода в параллельный, а проходной буфер выполнен в виде преобразователя параллельного кода в последовательный.

Введение в известное устройство асинхронной коммутации генератора тактовых импульсов, выполнение приемного буфера с числом разрядов, не меньшим количества бит пакета информации, и придание блоку управления функции определения наличия пакета информации в приемном буфере при указанном их соединении (взаимодействии) с другими элементами устройства обеспечивает подачу каждого поступающего на вход устройства пакета информации в приемный буфер, освобожденный от принятого ранее пакета информации, и вывод пакетов информации из проходных буферов при несовпадении тактовых частот принимаемого пакета информации и собственного генератора тактовых импульсов и промежутках времени между принимаемыми пакетами информации, меньшими длительности пакета информации. Новым техническим результатом изобретения является исключение взаимовлияния следующих друг за другом пакетов информации, что повышает надежность работы линии связи, а также эффективность ее использования за счет обеспечения возможности сокращения промежутков времени между пакетами информации.

Выполнение приемного буфера в виде преобразователя последовательного кода в параллельный, а проходного буфера - в виде преобразователя параллельного кода в последовательный является одним из возможных исполнений изобретения по второму варианту.

Наиболее близким к изобретению по третьему варианту является устройство асинхронной коммутации пакетов информации, приведенное также в описании к вышеуказанному патенту США N 4768190, H 04 J 3/00 (фиг.6). Первый вход (from transit buffers) рассматриваемого устройства соединен с входом управляемого передающего буфера 146 (нумерация по описанию патента США), выход которого является выходом устройства асинхронной коммутации. Устройство содержит также приемный 130 и проходной 134 буферы, последний из которых осуществляет задержку пакета информации на время, не меньшее его передачи, т.е., выполнен с числом разрядов, не меньшим количества бит пакета информации (с учетом степени параллельности). Выход проходного буфера 134 также соединен с выходом устройства асинхронной коммутации, в вход - с выходом приемного буфера 130, вход которого соединен с вторым входом 30 устройства. Вход блока 142 выделения тактовых импульсов соединен с вторым входом 30 устройства, а выход - с тактовым входом приемного буфера 130 и входом (CLK) блока управления 136. Блок управления 136 осуществляет функцию определения наличия пакета информации в проходном 134 и передающем 146 буферах и функцию управления выдачей пакета информации из проходного и передающего буферов. Управляющие входы проходного (PTBC) и передающего (TBC) буферов, а также выходы состояния проходного и передающего буферов (те же PTBC и TBC) соединены с соответствующими выходом и входами указанного блока управления.

Недостатком этого известного устройства асинхронной коммутации, как и вышеописанных, является возможность недопустимого взаимодействия следующих друг за другом пакетов информации в том случае, если последующий пакет информации появляется на входе управляемого проходного буфера, когда из него еще не выведен предыдущий пакет информации.

Задачей изобретения по третьему варианту является повышение надежности работы линии связи при одновременном повышении эффективности ее использования.

Для решения указанной задачи в известное устройство асинхронной коммутации пакетов информации, первый вход которого соединен с входом управляемого передающего буфера, выход которого является выходом устройства асинхронной коммутации, содержащее также приемный и проходной буферы, последний из которых выполнен с числом разрядов, не меньшим количества бит пакета информации, при этом выход проходного буфера соединен с выходом устройства асинхронной коммутации, в вход - с выходом приемного буфера, вход которого соединен с вторым входом устройства, блок выделения тактовых импульсов, вход которого соединен с вторым входом устройства, а выход - с тактовым входом приемного буфера, и блок управления, осуществляющий функцию определения наличия пакета информации в проходном и передающем буферах и функцию управления выдачей пакета информации из проходного и передающего буферов, причем управляющие входы проходного и передающего буферов, а также выходы состояния проходного и передающего буферов соединены с соответствующими выходом и входами указанного блока управления, введены генератор тактовых импульсов и по крайней мере один дополнительный проходной буфер, выполненный с числом разрядов, не меньшим количества бит пакета информации, блоку управления придана функция определения наличия пакета информации в приемном буфере и в каждом из дополнительных проходных буферов, выход каждого дополнительного проходного буфера соединен с выходом устройства, а вход - с выходом приемного буфера, выход генератора тактовых импульсов соединен с тактовыми входами передающего и всех проходных буферов, а управляющий вход и выход состояния каждого из дополнительных проходных буферов соединены с соответствующими выходом и входом блока управления.

Введение в известное устройство асинхронной коммутации генератора тактовых импульсов и по крайней мере одного дополнительного проходного буфера, выполненного с числом разрядов, не меньшим количества бит пакета информации, а также придание блоку управления функции определения наличия пакета информации в приемном буфере и в каждом из дополнительных проходных буферов, при указанном соединении (взаимодействии) друг с другом всех элементов устройства обеспечивает подачу каждого поступающего на вход устройства пакета информации в свободный управляемый проходной буфер и вывод пакетов информации из проходных буферов на разных тактовых частотах. Новым техническим результатом изобретения является исключение взаимовлияния следующих друг за другом пакетов информации, что повышает надежность работы линии связи, а также эффективность ее использования за счет обеспечения возможности сокращения промежутков времени между пакетами информации.

Вышеописанные три варианта изобретения, связаны между собой единым изобретательским замыслом и соответствуют требованию единства изобретения, так как они относятся к объектам одного вида, одинакового назначения и обеспечивают получение одного и того же технического результата, которым является исключение взаимовлияния следующих друг за другом пакетов информации. Это повышает надежность работы линии связи, а также эффективность ее использования за счет обеспечения возможности сокращения промежутков времени между пакетами информации.

Три варианта изобретения отличаются друг от друга сложностью исполнения по количеству элементов, второй из них является, наиболее простым, а первый - наиболее сложным.

Изобретение поясняется следующими чертежами:

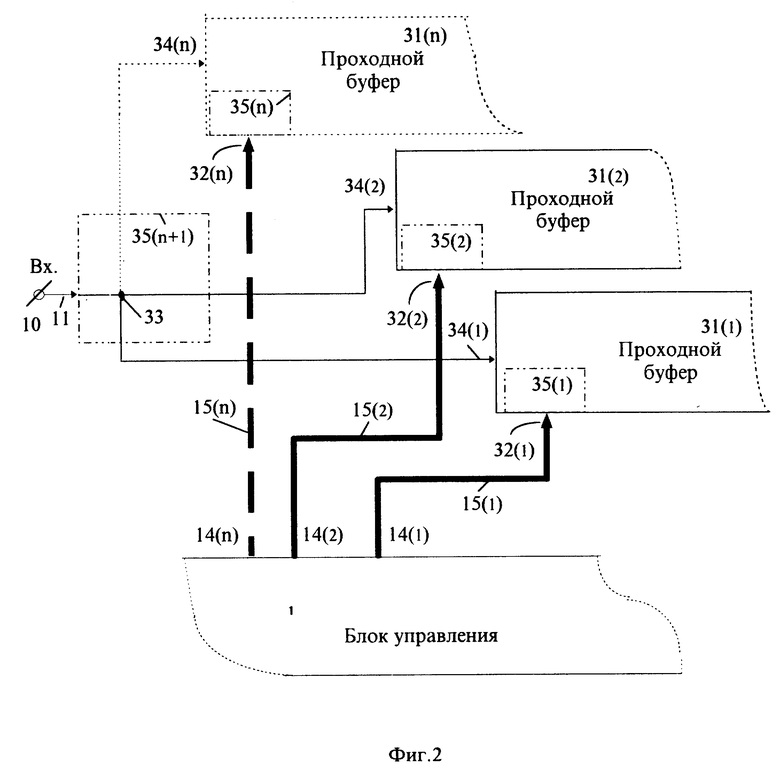

фиг. 1 - блок-схема устройства асинхронной коммутации пакетов информации по первому варианту изобретения;

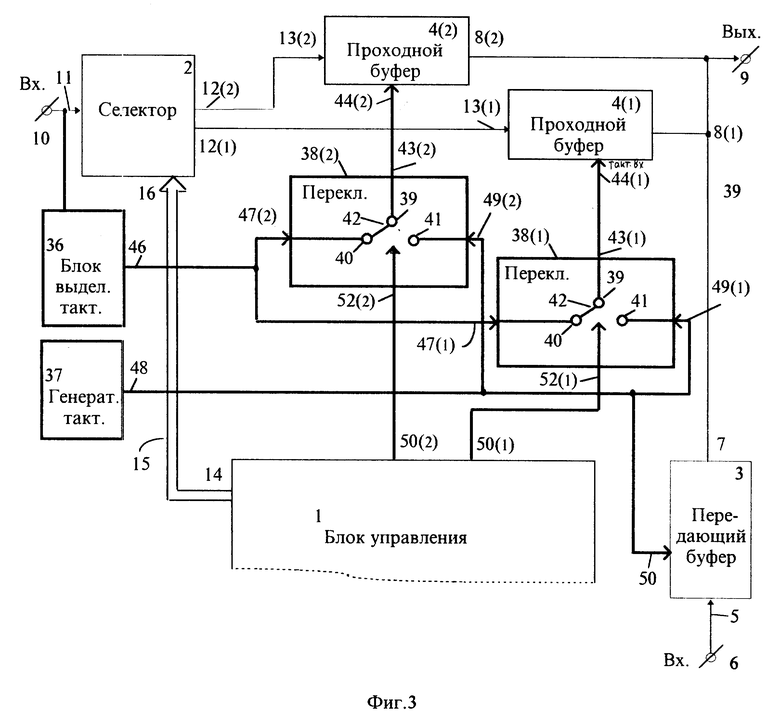

фиг. 2 - вариант выполнения узла координации в устройстве по первому варианту изобретения;

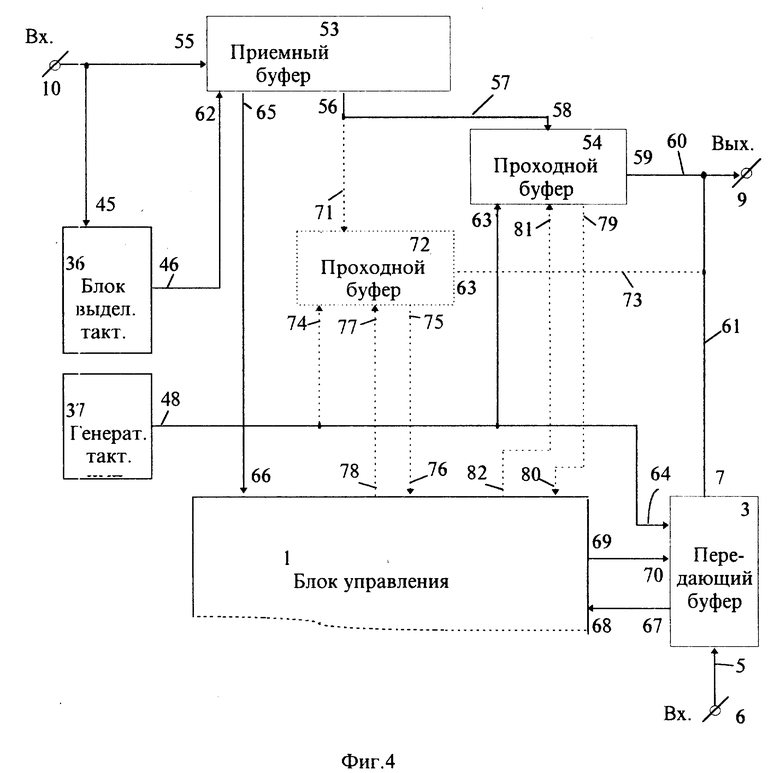

фиг. 3 - блок-схема цепей синхронизации в устройстве асинхронной коммутации пакетов информации по первому варианту изобретения;

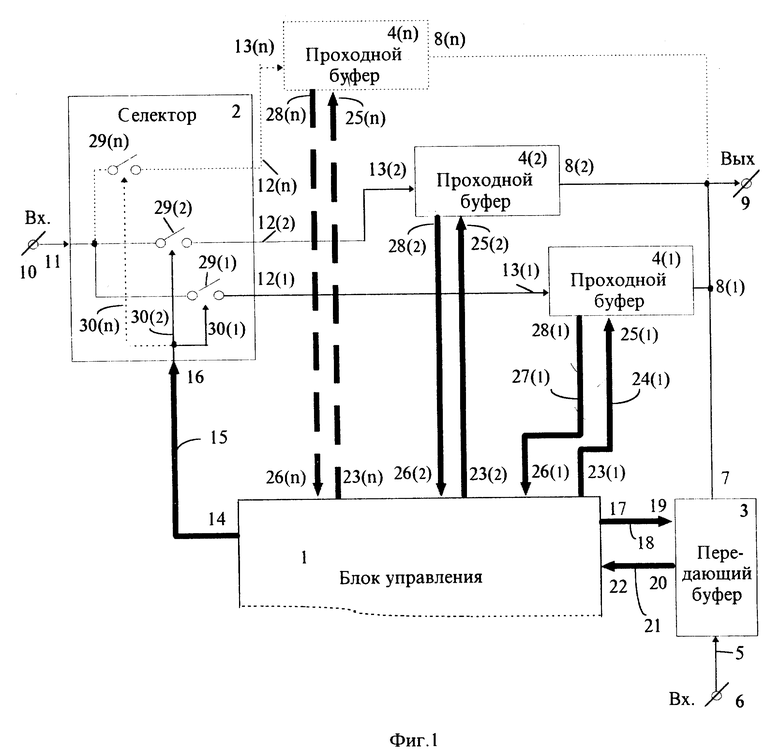

фиг. 4 - блок-схема устройства асинхронной коммутации пакетов информации по второму и третьему вариантам изобретения.

Устройство асинхронной коммутации пакетов информации по первому варианту изобретения (фиг. 1) содержит блок управления 1, управляемый селектор (узел координации) 2, управляемый передающий буфер 3 и управляемые проходные буферы 4(1), 4(2),..., 4(n). Вход 5 управляемого передающего буфера 3 является одновременно первым входом 6 устройства коммутации, выход 7 передающего буфера 3 и выходы 8(1), 8(2),...,8(n) проходных буферов 4(1)-4(n) соединены с выходом 9 устройства коммутации. Второй вход 10 устройства коммутации соединен с входом 11 управляемого селектора 2, каждый из выходов 12(1) - 12(n) которого соединен с соответствующим входом 13(1)-13(n) проходных буферов 4(1) - 4(n). Выход 14 блока управления 1 соединен шиной 15 с управляющим входом 16 селектора 2, а выход 17 блока управления 1 шиной 18 соединен с управляющим входом 19 передающего буфера 3. Выход 20 состояния передающего буфера 3 соединен шиной 21 с входом 22 блока управления 1. Каждый из выходов 23(1) - 23(n) блока управления 1 соединен одной из шин 24(1) - 24(n) с соответствующим управляющим входом 25(1) - 25(n) проходных буферов 4(1) - 4(n). Каждый из выходов 26(1) - 26(n) состояния проходных буферов 4(1) - 4(n) соединен одной из шин 27(1) - 27(n) с соответствующим входом 28(1) - 28(n) блока управления 1.

В качестве каждого из проходных буферов 4(1) - 4(n) может быть использован, например, универсальный регистр сдвига типа КР1533ИР24.

Блок управления 1 выполняется, например, в виде микропроцессора типа 1830ВЕ31.

Узел координации (селектор) 2 содержит n управляемых ключей 29(1) - 29(n), каждый из которых включен в цепь между входом 11 селектора 2 и соответствующим из его выходов 12(1) - 12(n). Управляющий вход каждого из ключей 29(1) - 29(n) соединен с соответствующим из проводников 30(1) - 30(n) с шиной 15. Шина 15 содержит n проводников. В качестве управляемых ключей 29(1) - 29(n) могут быть использованы, например, микросхемы типа КР1533ЛА3.

В варианте исполнения узла координации, приведенном на фиг.2, каждый из проходных буферов 31(1)-31(n) выполнен имеющим свой вход 32(1)-32(n) разрешения загрузки буфера. При этом идущая от выхода 14 блока управления 1 шина 15 состоит из n проводников 15(1)-15(n), каждый из которых соединен с соответствующим входом 32(1)-32(n) разрешения загрузки проходных буферов. Кроме того, в этом варианте вход 10 устройства коммутации соединен в точке 33 с всеми входами 34(1) - 34(n) проходных буферов 31(1) -31(n).

Таким образом, изображенный на фиг.2 узел координации состоит из совокупности показанных на этой фигуре двойным штрих-пунктиром подузлов 35(1)-35(n) и 35(n+1). Подузел 35(n+1) - это соединение входа 10 устройства с входами 34(1) - 34(n) буферов 31(1) - 31(n), а каждый из подузлов 35(1) - 35(n) является составной частью соответствующего буфера, которая управляет возможностью загрузки в буфер действующего на его входе пакета информации.

В качестве каждого из проходных буферов 31(1) - 31(n) используется, например, универсальный регистр сдвига типа КР1533ИР24.

Для простоты изображения узла координации на фиг.1 и 2 предполагается, что проходные буферы 4(1) - 4(n), 31(1) - 31(n) выполнены в виде регистров с последовательным вводом информации. Однако каждый из указанных буферов может быть выполнен в виде регистра с параллельным вводом информации. При этом в селекторе 2 на фиг.1 число ключей для каждого из буферов должно равняться числу параллельных входов буфера, а на фиг.2 в этом случае вход 10 устройства соединен с входами 34(1) - 34(n) проходных буферов 31(1) - 31(n) с помощью шин, имеющих число проводников, также равное числу параллельных входов буфера (на чертежах не показано).

Управляемый передающий буфер 3 может быть выполнен в виде регистра с последовательным или параллельным вводом информации.

Выполнение всех показанных на чертежах буферов относительно вывода информации из них может быть любым, но одинаковым для всех.

Передающий буфер 3 и каждый из проходных буферов 4(1) - 4(n), 31(1) - 31(n) могут быть выполнены, в частности, аналогично одному из блоков 220, показанному на фиг.21А в описании к вышеупомянутому патенту США N 4768190. В этом случае выход 20 состояния буфера 3 и каждый из выходов 28(1) - 28(n) состояния буферов 4(1) - 4(n) аналогичен двум выходам - "buf full (буфер полон)" и "buf empty (буфер пуст)" блока 220 патента США, а каждая из показанных на фиг.1 шин 21 и 24(1) - 24(n) содержит по два проводника.

Схема выполнения цепей синхронизации устройства по первому варианту изобретения, показанного на фиг.1 и 2, приведена на фиг.3, где для упрощения изображены только два проходных буфера 4(1) и 4(2). Схема синхронизации содержит блок 36 выделения тактовых импульсов приема пакетов информации, генератор 37 тактовых импульсов передачи пакетов информации и переключатели 38(1), 38(2). Каждый из переключателей 38 содержит неподвижные контакты 39, 40 и 41. Подвижная перемычка 42 предназначена для замыкания контакта 39 либо с контактом 40, либо с контактом 42. На фиг.3 перемычка 42 изображена в положении, когда она замыкает между собой контакты 39 и 40. Контакт 39 каждого переключателя (38(1), 38(2)) соединен с его выходом (43(1), 43(2)), который, в свою очередь, соединен с входом синхронизации (44(1), 44(2)) соответствующего проходного буфера 4(1) или 4(2). Вход 10 устройства асинхронной коммутации пакетов информации соединен с входом 45 блока 36 выделения тактовых импульсов, выход 46 которого соединен с первыми входами 47(1) или 47(2) переключателей 38(1), 38(2). Выход 48 генератора 37 тактовых импульсов передачи соединен с вторыми входами 49(1), 49(2) указанных переключателей и с входом 50 синхронизации передающего буфера 3. Каждый из управляющих выходов 51(1) и 51(2) блока управления 1 соединен с соответствующим управляющим входом 52(1) или 52(2) переключателей 38(1), 38(2). Остальные соединения на фиг.3 соответствуют соединениям, показанным на фиг.1.

Переключатели 38 могут быть выполнены на микросхемах типа КР1533ЛА3. В качестве генератора тактовых импульсов 37 может быть использован генератор, встроенный в микропроцессор типа 1830ВЕ31 или внешний генератор с кварцевой стабилизацией, выполненный, например, на микросхеме КР1533ЛА3.

Раздельный показ на фиг.1 и 3 выполнения разных по назначению цепей предложенного устройства по первому варианту изобретения осуществлен только с целью упрощения чертежей. Практическая схема устройства содержит все блоки и соединения, показанные на фиг.1 и 3 (или на фиг.2 и 3).

Показанное на фиг.4 устройство асинхронной коммутации пакетов информации по второму варианту изобретения изображено сплошными линиями и включает уже известные блок управления 1, блок 36 выделения тактовых импульсов, генератор 37 тактовых импульсов, передающий буфер 3, первый вход 6, второй вход 10 и выход 9, а также приемный буфер 53 и проходной буфер 54. Второй вход 10 устройства соединен с входом 45 блока 36 и входом 55 приемного буфера 53, выход 56 которого соединен шиной 57 с входом 58 проходного буфера. 54. Выход 59 буфера 54 соединен с выходом 9 устройства шиной 60, а выход 7 передающего буфера 3 соединен с тем же выходом 9 устройства шиной 61. Выход 46 блока 36 выделения тактовых импульсов соединен с тактовым входом 62 приемного буфера 53. Выход 48 генератора тактовых импульсов соединен с входом 63 проходного буфера 54 и входом 64 передающего буфера 3. Выход 65 состояния приемного буфера 53 соединен с входом 66 блока управления 1. Выход 67 состояния передающего буфера 3 соединен с входом 68 блока управления 1, а выход 69 блока управления 1 соединен с управляющим входом 70 этого же буфера 3.

Приемный буфер 53 выполнен в виде регистра сдвига с последовательным входом и параллельным выходом, а проходной буфер 54 - в виде регистра сдвига с параллельным входом и последовательным выходом. Каждый из буферов 53, 54 выполнен с числом разрядов, не меньшим числа бит пакета информации. Передающий буфер 3 при этом может быть выполнен с произвольным вводом, но с последовательным выводом информации.

Приемный буфер 53 может иметь как побитный (т.е. одноразрядный) так и побайтный (восьмиразрядный) вход или иную степень параллельности входа, а проходной буфер 54 соответственно может иметь как побитный (то есть одноразрядный) так и побайтный (восьмиразрядный) выход или иную степень параллельности выхода.

На фиг.4 пунктиром показаны блоки и связи, вместе с которыми все изображенное на данной фигуре представляет собой блок-схему изобретения по третьему варианту. Вход 71 дополнительно введенного проходного буфера 72 соединен с выходом 56 проходного буфера 53, а выход буфера 72 шиной 73 соединен с выходом 9 устройства. Тактовый вход 74 буфера 72 соединен с выходом 48 генератора тактовых импульсов, выход 75 состояния буфера 72 соединен с входом 76 блока управления 1, в управляющий вход 77 буфера 72 соединен с выходом 78 блока управления 1. Кроме того, проходной буфер 54 выполнен с выходом состояния 79, соединенным с входом 80 блока управления 1, и снабжен управляющим входом 81, соединенным с выходом 82 блока 1 управления.

Устройство асинхронной коммутации пакетов информации по третьему варианту изобретения может содержать несколько дополнительных проходных буферов, аналогичных дополнительному проходному буферу 72, включенных в схему устройства аналогично включению буфера 72 (на чертеже не показано).

Блоки устройств асинхронной коммутации по второму и третьему вариантам изобретения могут быть выполнены на микросхемах, указанных выше для устройства по первому варианту изобретения.

Устройство асинхронной коммутации пакетов информации по первому варианту изобретения (фиг.1 и 3) работает следующим образом.

Блок 1 управления контролирует состояние каждого из буферов 3 и 4, т.е. наличие или отсутствие в буфере пакета информации. Считаем в начальный момент времени все буферы 3, 4 пустыми. При этом по команде блока управления 1, переданной в селектор 2 по шине 15, ключ 29(1) замкнут (фиг.1), остальные ключи 29(2) - 29(n) разомкнуты. Подвижные контакты 42 (фиг.3) всех переключателей 38(1-2) находятся в положении, показанном на фиг. 3, т.е. контакты 39 и 49 замкнуты между собой так, что тактовые входы 44 проходных буферов 4 соединены с выходом 46 блока 36 выделения тактовых импульсов.

При поступлении пакета информации на второй вход 10 устройства асинхронной коммутации из этого пакета информации с помощью блока 36 выделяются тактовые импульсы, поступающие на тактовые входы 44 проходных буферов 4. Поступивший на вход 10 устройства пакет информации через замкнутый ключ 29(1) передается на вход 13(1) проходного буфера 4(1) и заполняет этот проходной буфер. С момента появления в первом же разряде проходного буфера 4(1) первого бита пакета информации на выходе 28(1) состояния этого буфера появляется сигнал, при наличии которого блок 1 управления фиксирует занятость проходного буфера 4(1). Занятость буфера фиксируется до тех пор, пока из буфера не будет впоследствии выведен последний бит пакета информации. Поступивший в проходной буфер 4(1) пакет информации задерживается в нем на время, не меньшее длительности пакета, причем указанная задержка осуществляется непосредственно в процессе приема в указанный буфер пакета информации, после чего по команде блока 1 управления, поступающей на управляющий вход 25(1) буфера 4(1) по шине 24(1), передается на выход 9 устройства асинхронной коммутации. Для обеспечения вывода пакета информации из буфера 4(1) по команде блока управления 1, переданной по шине 52(1), подвижный контакт 42 переключателя 38(1) перекидывается вправо по фиг.3, т.е. замыкает между собой контакты 39 и 41. На тактовый вход 44(1) проходного буфера 4(1) подаются тактовые импульсы с выхода 48 генератора 37 тактовых импульсов.

Как только пакет, поступивший на вход 10 устройства, будет полностью принят в проходной буфер 4(1), по команде блока 1 управления в селекторе 2 устанавливается состояние замкнутости того из ключей 29(2)-29(n), который соединяет вход 10 устройства с одним из пустых буферов 4, например замыкается ключ 29(2), если буфер 4(2) пуст. Остальные ключи 29 размыкаются. При этом следующий поступивший на вход 10 устройства пакет информации поступает в проходной буфер 4(2) и задерживается в нем на время, равное длительности пакета, причем указанная задержка осуществляется непосредственно в процессе приема в указанный буфер пакета информации, после чего пакет информации выводится на выход 9 устройства по команде блока 1 управления аналогично вышеописанному.

При поступлении на второй вход 10 устройства пакетов информации одинаковой длины с одинаковым временным интервалом между ними эти пакеты с такой же частотой появляются на выходе 9 устройства, но с задержкой каждого пакета на одинаковое время, равное стандартной длине пакета информации. В этом случае в работе устройства практически достаточно использовать только любые два из проходных буферов 4, например 4(1) и 4(2). При необходимости задержки одного из пакетов информации на время, большее длительности других пакетов, например при поступлении пакета информации увеличенной длины или при поступлении пакета с данными, для которого допустима задержка, так называемой дейтаграммы, последний задерживается в проходном буфере 4(3) до тех пор, пока не возникает возможность его передачи вследствие перерыва в поступлении на вход устройства других пакетов информации. Число таких нестандартных пакетов информации может быть равно n-2. При поступлении пакета информации с первого входа 6 устройства в передающий буфер 3 блок управления получает информацию о занятости буфера 3 с его выхода 20 и разрешает выдачу этого пакета информации на выход 9 устройства только при отсутствии пакетов информации во всех проходных буферах 4. В таком случае на управляющий вход 19 передающего буфера 3 поступает сигнал с выхода 17 блока 1 управления, разрешающий передачу пакета информации. Тактовая частота ввода и вывода пакета информации постоянно поступает на тактовый вход 50 (фиг.3) буфера 3 с выхода 48 генератора 37 тактовых импульсов. При занятости хотя бы одного из проходных буферов 4 пакет информации, поступивший в передающий буфер 3, задерживается в нем до освобождения всех проходных буферов 4. Осуществляющие задержку пакетов информации проходные буферы 4 имеют приоритет перед передающим буфером 3, что является принципом передачи информации в асинхронной сети, составленной из таких устройств коммутации, позволяющих обеспечивать коммутацию в каждом из устройств коммутации без центрального процессора.

Возможно использование иного алгоритма коммутации, когда при поступлении на вход 10 устройства нестандартного пакета информации, для которого допустима задержка, на выход 9 устройства передается пакет информации из передающего буфера 3, а нестандартный пакет находится в это время в том проходном буфере, в который он был принят.

При выполнении первого варианта изобретения с схемой узла координации, показанной на фиг.2, работа устройства происходит аналогично вышеописанному, если учесть, что сигналы блока 1 управления, разрешающие и запрещающие проходным буферам 4 прием пакетов информации с входа 10 устройства, подаются по шине 15 (проводники 15(1)-15(n)) непосредственно на входы 32(1)-32(n) разрешения записи проходных буферов 31(1)-31 (п). В остальном управление проходными буферами 31(1)-31(n) производится с использованием не показанных на фиг. 2 связей этих буферов с блоком 1 управления, блоком 36 и генератором 37 тактовых импульсов, которые (связи) аналогичны связям буферов 4, указанным на фиг.1 и 3.

Устройство синхронной коммутации пакетов информации по второму варианту изобретения (фиг. 4, изображено сплошными линиями) работает следующим образом.

Приходящий на вход 10 устройства пакет информации поступает на вход 55 приемного буфера 53 и задерживается в нем на время, равное длительности пакета. Прием пакета информации всегда осуществляется с использованием тактовых импульсов, поступающих с выхода 46 блока 36 выделения тактовых импульсов из принимаемого пакета информации. Задержка пакета информации в приемном буфере 53 обеспечивается непосредственно в процессе приема в указанный буфер пакета информации, а выдача его из буфера 53 в буфер 54 производится автоматически путем параллельной записи за 1 такт частоты загрузки с параллельного выхода буфера 53 через параллельный вход в буфер 54. По окончании параллельной записи пакета информации в проходной буфер 54 указанный пакет из проходного буфера 54 выдается последовательно (с учетом степени параллельности) на выход 9 устройства, с использованием тактовых импульсов с выхода 48 генератора 37 тактовых импульсов.

Контроль за занятостью приемного буфера 53 пакетом информации осуществляется блоком 1 управления с использованием выхода 65 состояния этого буфера, а контроль за занятостью передающего буфера 3 - с использованием выхода 67 состояния буфера 3. Управление выдачей пакета информации из буфера 3 осуществляется блоком управления путем выдачи соответствующего сигнала на управляющий вход 70 буфера 3. Поступивший в передающий буфер 3 пакет информации выдается на выход 9 устройства коммутации только при отсутствии пакета информации в приемном буфере 53.

Возможно использование иного алгоритма коммутации, когда при поступлении на вход 10 устройства нестандартного пакета информации, для которого допустима задержка, на выход 9 устройства передается пакет информации из передающего буфера 3, а нестандартный пакет находится в это время в том проходном буфере, в который он был принят.

Устройство синхронной коммутации пакетов информации по третьему варианту изобретения (фиг.4, сплошные и пунктирные линии) работает при приеме пакетов информации с входа 10 устройства в приемный буфер 53 аналогично устройству по второму варианту изобретения. Далее работа осуществляется следующим образом. Блок 1 управления определяет занятость всех проходных буферов (например, буферов 54 и 72 и других буферов, включенных в схему, как буфер 72, не показанных на фиг.4), а также управляет загрузкой пакета информации в тот или другой проходной буфер, как и в устройстве по первому варианту (фиг. 2). Пакет информации из приемного буфера 53 передается в один из свободных проходных буферов. Передача пакетов информации из проходных буферов (54, 72) на выход 9 устройства производится также аналогично вышеописанному для первого варианта изобретения. Передача пакета информации из передающего буфера 3 на выход 9 устройства производится только при отсутствии пакетов информации во всех имеющихся в схеме проходных буферах.

Возможно использование иного алгоритма коммутации, когда при поступлении на вход 10 устройства нестандартного пакета информации, для которого допустима задержка, на выход 9 устройства передается пакет информации из передающего буфера 3, а нестандартный пакет находится в это время в том проходном буфере, в который он был принят.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2027315C1 |

| МНОГОКАНАЛЬНЫЙ ЭЛЕКТРОСТИМУЛЯТОР | 1992 |

|

RU2017508C1 |

| СПОСОБ ОБНАРУЖЕНИЯ ДВИЖУЩИХСЯ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2042150C1 |

| СПОСОБ ЛАЗЕРНОЙ ЛОКАЦИИ И ЛАЗЕРНОЕ ЛОКАЦИОННОЕ УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2183841C1 |

| ОПТИЧЕСКАЯ СИСТЕМА СВЯЗИ | 1999 |

|

RU2174287C2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ СТРЕЛОЧНЫМ ПЕРЕВОДОМ | 1998 |

|

RU2147008C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПАЧЕК ИМПУЛЬСОВ | 1995 |

|

RU2098918C1 |

| ОПТИЧЕСКАЯ СИСТЕМА СВЯЗИ | 1995 |

|

RU2121229C1 |

| УСТРОЙСТВО ДЛЯ КОМПЛЕКСНОЙ ОКСИГЕНО- И ГИПОКСИТЕРАПИИ (ВАРИАНТЫ) | 1994 |

|

RU2121854C1 |

Изобретение предназначено для использования в сетях связи, обеспечивающих передачу цифровых данных, видео- и речевой информации в реальном масштабе времени с помощью одного и того же оборудования, не требующего единого процессора для коммутации пакетов информации, с децентрализованным управлением коммутацией и упрощенным программным обеспечением. Изобретение реализовано в трех вариантах. Три варианта изобретения связаны между собой изобретательским замыслом и соответствуют требованию единства изобретения, так как они относятся к объектам одного вида, одинакового назначения и обеспечивают получение одного и того же технического результата, которым является исключением взаимовлияния следующих друг за другом пакетов информации. Это повышает надежность работы линии связи, а также эффективность ее использования за счет обеспечения возможности сокращения промежутков времени между пакетами информации. Три варианта изобретения отличаются друг от друга сложностью исполнения по количеству элементов, второй из них является наиболее простым, а первый - наиболее сложным. 3 с. и 2 з.п. ф-лы, 4 ил.

| Ларионов А.М., Майоров С.А., Новиков Г.И | |||

| Вычислительные комплексы, системы и сети | |||

| - Л.: Энергоатомиздат, 1987, с | |||

| Парный рычажный домкрат | 1919 |

|

SU209A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU 4768190 A, 30.08.88 | |||

| US 4750167 A, 07.06.88 | |||

| US 4782482 A, 01.11.88 | |||

| US 3668328 A, 06.06.72 | |||

| US 4586175 A, 29.04.86 | |||

| DE 3937738 A1, 16.05.91 | |||

| ТРЕХКАНАЛЬНАЯ АСИНХРОННАЯ СИСТЕМА | 1991 |

|

RU2029365C1 |

Авторы

Даты

1998-09-20—Публикация

1997-07-11—Подача