Данное изобретение относится к способу и устройству для предварительной обработки коэффициентов преобразования, способу и устройству для выполнения обратного ортогонального преобразования, способу и устройству для расширения уплотненного информационного сигнала и носителю записи. В частности, изобретение относится к способу и устройству для предварительной обработки коэффициентов преобразования, способу и устройству для выполнения обратного ортогонального преобразования, способу и устройству для уплотнения информационного сигнала, способу и устройству для расширения уплотненного информационного сигнала и носителю записи для сигнала движущегося изображения.

Ортогональные преобразования используются в разнообразных системах обработки цифровых сигналов для различных применений. Ортогональные преобразования позволяют выполнять обработку сигнала в частотной области. Широко известными видами ортогонального преобразования являются быстрое преобразование Фурье (FFT) и дискретное (косинусное преобразование DCT) и т.п. Ортогональное преобразование анализирует, например, фрагмент сигнала во временной области по частотным составляющим (в зависимости от используемой функции ортогонального преобразования), показывая спектр (то есть, распределение энергии по частоте) первоначального фрагмента сигнала во временной области. Путем обработки различными способами частотных составляющих (обычно называемых коэффициентами преобразования), являющихся результатом ортогонального преобразования фрагмента сигнала, может быть уменьшена избыточность в первоначальном фрагменте сигнала. Другими словами, посредством ортогонального преобразования первоначального фрагмента сигнала и обработки результирующих коэффициентов преобразования, первоначальный фрагмент сигнала может быть представлен с использованием меньшего числа бит, чем их было использовано при представлении первоначального фрагмента сигнала. Кроме того, посредством обратного ортогонального преобразования коэффициентов преобразования может быть восстановлен первоначальный фрагмент сигнала во временной области.

Устройства для улучшения сигнала движущегося изображения и для расширения уплотненного сигнала движущегося изображения являются известными примерами систем обработки цифровых сигналов, использующих ортогональное преобразование.

Известно, что мощность сигналов, имеющих высокую корреляцию, концентрируется в низкочастотном диапазоне частотной области. Если концентрация мощности сигнала по конкретной координатной оси (например, частотной оси) возрастает, избыточность сигнала может быть существенно уменьшена, и сигнал может быть уплотнен более эффективно.

Поскольку сигнал движущегося изображения обычно сильно коррелирован как в пространстве, так и во времени, для концентрации мощности сигнала по конкретной координатной оси может быть применено ортогональное преобразование, и сигнал движущегося изображения может быть уплотнен с высокой эффективностью.

До настоящего времени большое количество информации требовалось для представления движущегося изображения, использующего, например, видеосигнал стандарта NTSC (Национальный Комитет по Телевизионным системам США). Благодаря этому, для записи сигнала движущегося изображения требовался носитель записи с очень большой информационной емкостью, если носитель должен был обеспечивать время записи приемлемой длительности. Кроме того, частота информации, при которой с такого носителя записывается и воспроизводится сигнал движущегося изображения, была очень велика. Следовательно большие магнитные ленты и оптические диски требовались для хранения сигналов движущегося изображения.

Если желательно записать сигнал движущегося изображения на более компактный носитель записи с временем воспроизведения приемлемой длительности, к сигналу движущегося изображения должна быть применена операция уплотнения сигнала, чтобы уменьшить количество информации, подлежащей хранению. Кроме того, устройство должно быть способно распаковать уплотненный сигнал движущегося изображения, воспроизводимый с компактного носителя записи.

Для удовлетворения только что описанных требований были предложены различные системы уплотнения сигнала движущегося изображения, которые используют корреляцию между и внутри фрагментов сигнала движущегося изображения, представляющего кадры, составляющие сигнал движущегося изображения. Например, широко известна система уплотнения сигнала движущегося изображения, предложенная Экспертным Советом по Движущимся Изображениям (MPEG). Поскольку система MPEG подробно описана в различных печатных публикациях, детальное описание системы MPEG здесь не приводится.

В последующем описании будет часто употребляться термин "изображение". Поскольку описанный здесь способ сигнальной обработки относится к обработке сигнала движущегося изображения, представляющего движущееся изображение, должно быть понятно, что слово "изображение", обычно используемое здесь, относится к части сигнала движущегося изображения. Кроме того, сигнал движущегося изображения может представлять кадр движущегося изображения в виде фрейма (кадра) или поля. Если не установлено что-либо другое, "изображение" означает поле или кадр.

Сначала система MPEG определяет отличия между кадрами, образующими сигнал движущегося изображения, чтобы уменьшить избыточность сигнала движущегося изображения во временной области. Затем система MPEG уменьшает избыточность сигнала движущегося изображения в пространственной области путем применения ортогонального преобразования к блокам межкадровых отличий в пространственной области. Система MPEG использует дискретное косинусное преобразование (DCT) как ортогональное преобразование. Посредством уменьшения избыточности как во временной, так и в пространственной областях, движущееся изображение уплотняется весьма эффективно. Уплотненный сигнал движущегося изображения, являющийся результатом только что описанного процесса уплотнения, может быть затем записан на носитель записи или передан через подходящий канал передачи.

Когда уплотненный сигнал движущегося изображения воспроизводится с носителя записи или принимается из канала передачи, из уплотненного сигнала движущегося изображения выделяются блоки коэффициентов преобразования, являющиеся результатом DCT-преобразования. Коэффициенты преобразования обрабатываются путем использования обратного ортогонального преобразования (обратное дискретное косинусное преобразование (IDCT) в системе MPEG) для восстановления блоков межкадровых отличий в процессе реконструкции кадров первоначального сигнала движущегося изображения.

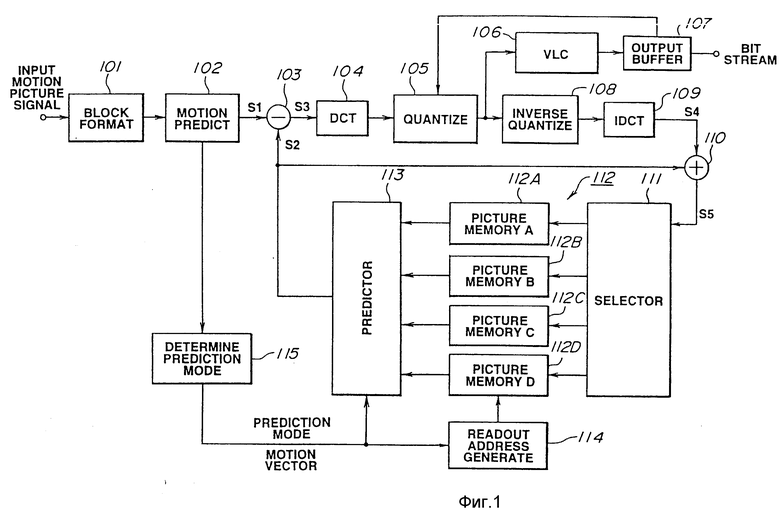

Пример структуры устройства уплотнения сигнала движущегося изображения, основанного на системе MPEG, показан на фиг. 1. В устройстве уплотнения, показанном на фиг. 1, цифровой сигнал движущегося изображения подается в схему форматирования блока 101, где он преобразуется из стандартного видеоформата, например, из стандартного формата видеосигнала NTSC, в блочный формат для получения разделенного на блоки сигнала движущегося изображения. Таким образом, каждый кадр сигнала движущегося изображения разделяется в пространственной области, то есть, по горизонтали и вертикали, на макроблоки, например, 16 х 16 элементов. Макроблоки разбиваются также на блоки 8 х 8 элементов.

Устройство, показанное на фиг. 1, сжимает каждый кадр сигнала движущегося изображения блок за блоком, пока не будут обработаны все блоки, образующие кадр. Затем устройство обрабатывает другой кадр сигнала движущегося изображения, который может быть, а может и не быть следующим кадром в последовательности кадров, образующих движущееся изображение. В последующем описании устройства, показанного на фиг. 1, будет раскрыт процесс сжатия одного блока элементов в одном кадре. Блок элементов, подлежащих уплотнению, - это текучий кадровый блок, являющийся блоком текущего кадра. Разбитый на блоки сигнал движущегося изображения подается на предсказатель движения 102. Предсказатель движения подает текущий кадр, включая блок текущего кадра S1, блок за блоком к схеме расчета блока отличий 103.

Когда схема расчета блока отличий 103 получает текущий кадровый блок от предсказателя движения 102, она также получает блок сопоставления S2, относящийся к текущему кадровому блоку из предсказателя движения 102. Блок сопоставления образуется предсказателем 113 из восстановленных кадров, хранящихся в блоке памяти кадров 112. Схема расчета блока отличий 103 определяет элемент за элементом отличие между текущим кадровым блоком S1 и соответствующим ему блоком сопоставления S2. Результирующий блок отличий, блок отличий S3, подается в схему ортогонального преобразования 104.

Схема ортогонального преобразования 104, которая обычно является схемой дискретного косинусного преобразования (DCT), осуществляет ортогональное преобразование блока отличий S3 и подает результирующий блок коэффициентов преобразования в квантователь 105. Квантователь 105 дискретизирует блок коэффициентов преобразования для получения блока дискретизированных коэффициентов преобразования. Кодер с переменной длиной слова 106 обрабатывает блок дискретизированных коэффициентов преобразования от квантователя 105, используя кодирование с переменной длиной слова, такое как кодирование Хаффмана или неравномерное кодирование и т. п. Результирующий блок закодированных коэффициентов преобразования подается затем, например, в канал цифровой передачи через выходной буфер 107. Сигнал управления, указывающий количество бит, хранящихся в выходном буфере 107, подается обратно к квантователю 105. Квантователь регулирует шаг дискретизации с учетом сигнала управления, предотвращая переполнение или потерю значимости в выходном буфере. Увеличение или уменьшение шага дискретизации соответственно уменьшает или увеличивает количество бит, подаваемых в выходной буфер.

Блок дискретизированных коэффициентов преобразования подается также от квантователя 105 к инверсному квантователю 108, который является частью локального декодера, используемого в устройстве уплотнения для формирования из дискретизированных коэффициентов преобразования реконструированных кадров, используемых в процессе кодирования с предсказанием. Инверсный квантователь 108 осуществляет инверсную дискретизацию блока дискретизированных коэффициентов преобразования путем выполнения обработки, являющейся дополнением к процессу дискретизации, выполненному квантователем 105. Результирующий блок коэффициентов преобразования подается в схему обратного ортогонального преобразователя 109, где он подвергается обратному ортогональному преобразованию, как дополнению к ортогональному преобразованию, выполненному схемой ортогонального преобразователя 104. Результирующий восстановленный блок отличий S4 подается на сумматор 110.

Сумматор 110 получает также блок сопоставления S2 для текущего кадрового блока S1 от одного из устройств памяти кадров в памяти изображения 112, выбираемых предсказателем 113. Сумматор 110 выполняет элемент за элементом суммирование восстановленного блока отличий S4 из схемы обратного ортогонального преобразования 109 и блока сопоставления S2 из памяти изображения 112 для получения реконструированного блока изображения S5. Реконструированный блок изображения доставляется к одному из устройств памяти изображения с 112A по 112D, выбираемых селектором III оттуда, где он хранится.

Реконструируемый блок изображения записывается в выбранное устройство памяти изображения, где он образует один блок (соответствующий текущему блоку) кадра, восстанавливаемого блок за блоком из блоков реконструируемого изображения в выбранном устройстве памяти изображения. По завершении процесса реконструированное изображение будет использоваться с целью получения блоков сопоставления для выполнения кодирования с предсказанием для уплотнения других кадров сигнала движущегося изображения.

Предсказатель движения 102 определяет для каждого макроблока текущего кадра вектор движения между макроблоком текущих кадров и хранящимися в нем макроблоками отличий других кадров сигнала движущегося изображения. Предсказатель движения формирует также сумму абсолютных значений отличий ("сумма абсолютных значений отличий") между элементами в каждом макроблоке текущего кадра и другими макроблоками других кадров. Каждая сумма абсолютных значений отличий показывает степень совпадения между каждым макроблоком текущего кадра и макроблоками других кадров. Предсказатель движения подает каждый вектор движения и соответствующую сумму абсолютных значений отличий и схему определения режима предсказания 115.

Схема определения режима предсказания 115 использует данные, полученные от предсказателя движения 102, для определения режима предсказания, который будет использован для кодирования с предсказанием текущего кадра, связанного с одним или несколькими другими восстанавливаемыми кадрами. Текущий кадр может быть закодирован с предсказателем посредством использования любого из следующих режимов предсказания:

(1) Внутрикадровый режим, при котором кадр сжимается сам, без обращения к любым другим кадрам. Кадр, закодированный таким образом, называется I-кадром.

(2) Режим прямого предсказания, при котором предсказание выполняется с обращением к реконструированному кадру, появившемуся ранее в движущемся изображении. Кадр, закодированный таким образом, называется P-кадр.

(3) Режим двунаправленного предсказания, при котором выполняется предсказание блок за блоком с обращением к опорному блоку, полученному из реконструированного кадра, появившегося ранее в движущемся изображении, реконструированного кадра, появившемся позднее в движущемся изображении или путем выполнения линейной операции элемент за элементом (например, расчет среднего значения) между ранее реконструированным кадром и кадром, реконструированным позднее. Кадр, закодированный таким образом, называется B-кадром.

Другими словами, I-кадр является кадром, в котором выполняется внутрикадровое кодирование. P-кадр предсказывается из реконструированного I-кадра или P-кадр, появившегося ранее в движущемся изображении. B-кадр предсказывается блок за блоком путем использования ранее или позднее реконструированного I-кадра или P-кадра или путем использования блока, полученного посредством выполнения линейной операции с использованием реконструированного I-адра или P-кадра, появившегося ранее в движущемся изображении, и реконструированного I-кадра или P-кадра, появившегося позднее в движущемся изображении.

Схема определения режима предсказания 115 доставляет информацию о режиме предсказания и соответствующий вектор движения к предсказателю 113 и генератору адреса считывания 114. Генератор адреса считывания 114 выдает адреса считывания в память изображения 112 согласно вектору движения, который заставляет каждое устройство памяти изображения со 112A по 112D считывать блок реконструированных кадров, хранящихся в ней. Место считываемого блока в реконструированном изображении определяется вектором движения. Предсказатель 113 выбирает один из считываемых блоков из устройств памяти изображения 112A - 112D в ответ на сигнал режима предсказания PM, полученный от схемы определения режима предсказания 115. Выбранный считываемый блок обеспечивает блок сопоставления S2 для текущего блока S1. Если текущий блок является частью B-кадра, предсказатель выполняет также линейные операции над блоками, считываемыми из устройств памяти изображения 112A - 112D, для получения требуемого блока сопоставления. Предсказатель подает блок сопоставления S2 в схему блока отличий 103 и сумматор 110.

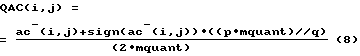

Пример структуры устройства расширения уплотненного сигнала движущегося изображения на базе системы MPEG показан на фигуре 2. В нем уплотненный сигнал движущегося изображения, полученный непосредственно от устройства уплотнения либо путем его воспроизведения с носителя записи, подается в виде потока бит во входной буфер 121, где он временно хранится. Уплотненный цифровой сигнал включает блоки закодированных коэффициентов преобразования (в том числе, блок закодированных коэффициентов преобразования, представляющих текущий блок) и информацию о режиме предсказания, шаге дискретизации и вектор движения для каждого блока.

Уплотненный сигнал движущегося изображения покадрово считывается из входного буфера 121 и направляется в инверсный кодер с переменной длиной слова (IVLC). Инверсный кодер с переменной длиной слова 122 осуществляет обратное кодирование с переменной длиной слова уплотненного сигнала движущегося изображения и разделяет уплотненный сигнал движущегося изображения на составляющие, включающие блоки дискретизированных коэффициентов преобразования, и информацию о режиме предсказания, размере шага и вектор движения для каждого блока.

Каждый блок закодированных коэффициентов преобразования подается в инверсный квантователь 123, который использует информацию о размере шага для блока, чтобы осуществить обратную дискретизацию блока дискретизированных коэффициентов преобразования для получения блока коэффициентов преобразования. Схема обратного ортогонального преобразования 124 осуществляет инверсное ортогональное преобразование, обычно IDCT-обработку блока коэффициентов преобразования для получения восстановленного блока отличий. Инверсный квантователь 123 и схема обратного ортогонального преобразования 124 соответственно осуществляют обработку, являющуюся дополнением к операциям, выполненными квантователем 105 и схемой ортогонального преобразования 104 в устройстве уплотнения, показанном на фигуре 1.

Генератор считываемого адреса 130 подает считываемый адрес в устройства памяти изображения 128A - 128D согласно вектору движения для текущего блока, полученного от инверсного кодера с переменной длиной слова 122. В ответ на считываемый адрес каждое из устройств памяти изображения 128A - 128D считывает хранящийся в нем блок реконструируемого кадра. Предсказатель 129 выбирает один из считываемых блоков из устройства памяти изображения 128A - 128D в ответ на сигнал режима предсказания PM, также получаемый от инверсного кодера с переменной длиной слова 122. Выбранный считываемый блок обеспечивает блок сопоставления для реконструкции текущего блока. Если текущий блок является частью кадра, закодированного как B-кадр, предсказатель выполняет такие линейные операции над считываемыми блоками из устройства памяти изображения 128A - 128D для обеспечения блока сопоставления. Предсказатель 129 доставляет блок сопоставления в сумматор 125.

Сумматор 125 выполняет элемент за элементом сложение восстанавливаемого блока отличий из схемы обратного преобразования 124 и блока сопоставления от предсказателя 129, чтобы реконструировать текущий кадровый блок текущего кадра. Селектор 126 подает реконструированный текущий блок кадра для хранения в одно из устройств памяти изображения 128A - 128D, в котором текущий кадр реконструируется. Реконструированный текущий кадровый блок записывается в выбранном устройстве памяти изображения на месте текущего кадрового блока в реконструируемом текущем кадре. Когда все реконструируемые текущие кадровые блоки будут записаны в выбранное устройство памяти изображения 128A - 128D, реконструируемый текущий кадр будет готов для считывания, а также для использования в качестве опорного кадра для реконструкции других кадров, появляющихся раньше или позже в движущемся изображении.

Реконструируемые кадры, хранящиеся в устройствах памяти изображения 128A - 128D, считываются в виде выходного сигнала движущегося изображения посредством селектора 126 в ответ на адреса считывания, формируемые генератором адреса дисплея 127. Сканирующий преобразователь (не показан) преобразует выходной сигнал движущегося изображения, считываемый из устройств памяти изображения 128A - 128D в растровый формат желаемого формата видеосигнала, например, NTSC. Результирующий выходной сигнал движущегося изображения может быть затем отображен на подходящем дисплее, например, электронно-лучевой трубке (CRT) и т.п. В этом примере генератор синхросигнала 131 синхронизируется от внешнего источника синхросигнала и периодически генерирует кадровый синхросигнал для доставки его к генератору адреса дисплея 127. Генератор адреса дисплея 127 генерирует считываемые адреса синхронно с кадровым синхросигналом.

Схемы ортогонального преобразования, например, схемы DCT и IDCT, используемые в вышеописанных устройствах управления и расширения, выполняют соответствующие арифметические операции над значениями элементов и коэффициентами преобразования, представляемыми целыми числами с конечным числом бит. Таким образом, операции ортогонального преобразования, выполняемые схемами ортогонального преобразования, выдают результат с округленным числом бит. По этой причине различие в точности операции ортогонального преобразования, использующего действительные числа или различие в устройстве схемы, используемой для выполнения операции ортогонального преобразования, может изменить результат операции ортогонального преобразования. Это может привести к несоответствию в работе устройства уплотнения и расширения и несоответствиям между устройствами расширения, осуществляющими расширение общего уплотненного сигнала.

Например, в устройстве уплотнения блок отличий, получающийся из сигнала движущегося изображения, подвергается ортогональному преобразованию, и используется заданная обработка для дискретизации результирующих коэффициентов преобразования в ходе генерирования уплотненного сигнала движущегося изображения. Тогда в устройстве расширения, если операционная точность представления действительных чисел или устройство схемы обратного ортогонального преобразования не соответствует аналогичным характеристикам устройства уплотнения, появляется вероятность того, что выходной сигнал устройства расширения будет отличаться от входного сигнала в устройство уплотнения. Поэтому выходной сигнал устройства расширения может зависеть от точности и конструкции устройства, используемого для расширения.

Операционная точность или структура обратного ортогонального преобразования может варьироваться в зависимости от устройства, используемого для выполнения обратного ортогонального преобразования. Например, обратное преобразование блока коэффициентов преобразования, использующее две различные конструкции одного и того же типа схемы обратного ортогонального преобразования, может дать различные результаты, Такое различие в результатах называется ошибкой несоответствия обратного ортогонального преобразования ("ошибка несоответствия").

Система MPEG определяет операционную точность, при которой должны выполняться DCT и IDCT, но не определяет способ выполнения операций и конфигурацию. Это имеет место из-за того, что схемы и способы для выполнения DCT и IDCT были разработаны до установления стандартов MPEG.

Как было описано выше, в системе MPEG устройство управления реализует, например, межкадровое кодирование с предсказанием и компенсацией движения сигнала движущегося изображения. В этой системе сигнал движущегося изображения разделяется на блоки, блок отличий строится из текущего кадрового блока и блока сопоставления, получаемого посредством применения компенсации движения к реконструируемому кадру; блок отличий подвергается ортогональному преобразованию с использованием DCT-обработки; результирующие коэффициенты преобразования дискретизируется; дискретизированные коэффициенты преобразования подвергаются кодированию с переменной длиной слова и закодированные коэффициенты преобразования собираются вместе с информацией о режиме предсказания, размером шага дискретизации и векторами движения для получения уплотнительного сигнала движущегося изображения.

Устройство расширения применяет инверсное кодирование с переменной длиной слова к закодированным коэффициентам преобразования, инверсную дискретизацию к дискретизированным коэффициентам преобразования, которые являются результатом инверсного кодирования с переменной длиной слова, и IDCT-обработку к коэффициентам преобразования, являющимся результатом инверсной дискретизации. Результирующий восстановленный блок отличий добавляется к блоку сопоставления, полученному посредством применения компенсации движения к реконструируемому кадру согласно вектору движения, Результирующий реконструированный кадровый блок записывается в виде блока реконструированного кадра, который обеспечивает кадр выходного сигнала движущегося изображения и также пригоден для использования в качестве опорного кадра.

Устройство уплотнения включает локальный декодер, который воспроизводит из дискретизированных коэффициентов преобразования реконструируемые кадры для использования их при выполнении кодирования с предсказанием. Локальный декодер включает инверсный квантователь и схему обратного ортогонального преобразования.

Если конфигурация схемы IDCT в локальном декодере устройства уплотнения отличается от схемы IDCT в устройстве расширения, будут иметь место случаи, когда реконструированные кадры, формируемые локальным декодером в устройстве уплотнения, будут отличаться от реконструированных кадров, формируемых устройством расширения. Зависимость IDCT-обработки от ее конкретного исполнения может вызвать проблемы, если уплотненный сигнал движущегося изображения, генерируемый устройством уплотнения в соответствии со стандартом MPEG, записывается на носитель записи, такой как оптический диск и т.п., для массового распространения. Если уплотненный сигнал движущегося изображения, воспроизводимый с оптического диска, расширяется устройствами расширения, изготовляемыми и продаваемыми различными производителями, воспроизводимое изображение может отличаться от оригинала. Кроме того, различия могут зависеть от используемого устройства расширения. Подобная несовместимость между различными устройствами расширения может также возникнуть, когда уплотненный сигнал движущегося изображения распространяется такими распределительными системами, как наземное или спутниковое вещество, телефонные системы, цифровые системы связи с комплексными услугами (ISDM), кабельные или оптические распределительные системы и т.п.

Ошибки несоответствия представляют конкретную проблему, если выполняется межкадровое кодирование с предсказанием. Межкадровое кодирование с предсказанием может быть межполевым кодированием или межкадровым кодированием. Межкадровое кодирование с предсказанием может вызвать накопление ошибок несоответствия в непрерывной области памяти, которые приведут к неисправимым дефектам в реконструируемых кадрах.

При уплотнении сигнала движущегося изображения по системе MPEG каждая видеопоследовательность разделяется на группы изображения (GOP), например, из восьми или двенадцати кадров. Каждый кадр классифицируется как I-кадр, P-кадр и B-кадр, как было описано выше. При выполнении предсказания движения B-кадр не используется в качестве опорного кадра. Поэтому, ошибка несоответствия, появляющаяся в B-кадре, не приводит к ошибкам в других кадрах.

Если ошибка несоответствия появляется в P-кадре, кадр с ошибкой несоответствия записывается в память изображения для использования при выполнении кодирования с предсказанием. Соответственно, если выполняется межкадровое кодирование с предсказанием, ошибка в P-кадре, хранящемся в памяти изображения, частично распространяется в P-кадры и B-кадры, получаемые из него путем кодирования с предсказанием. Ошибка накапливается пока кадр не будет заменен I-кадром или P-кадром, не имеющим такой ошибки.

Подобным же образом, когда ошибка несоответствия появляется в I-кадре, реконструируемый кадр с ошибкой несоответствия записывается в память изображения для использования при выполнении кодирования с предсказанием. Соответственно, если выполняется межкадровое кодирование с предсказанием, ошибка в I-кадре, записанном в память изображения, распространяется в P-кадры и B-кадры, образованные из него путем кодирования с предсказанием. Ошибка накапливается, пока кадр не будет заменен новым I-кадром, не имеющим такой ошибки.

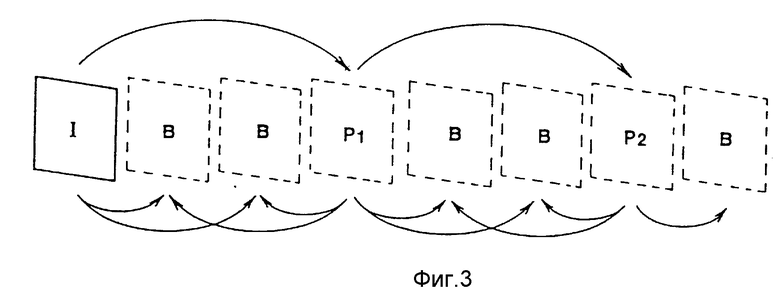

Накопление ошибки показано на фиг. 3. На фиг. 3, если ошибка несоответствия при декодировании I-кадра равна E1, а ошибка несоответствия при декодировании P-кадра P1 равна ЕР1, значение в реконструированном Р-кадре Р1 будет равно E1 + EP1. Кроме того, если ошибка несоответствия при декодировании P-кадра P2 равна EP2, значение ошибки в реконструированном P-кадре P2 будет E1 + EP1 + EP2. Даже если отдельные ошибки несоответствия малы, постепенное накопление этих ошибок может привести к большой ошибке.

Ошибки несоответствия, полученные при IDCT-обработке, используемой в декодерах MPEG как в устройстве уплотнения, так и в устройстве расширения, можно классифицировать по двум отдельным типам:

Тип (1): Ошибки, являющиеся результатом недостаточной операционной точности.

Тип (2): Ошибки, являющиеся результатом систематических различий при округлении.

Стандарт MPEG устанавливает требование к операционной точности, Однако, это требование не строгое, что не дает гарантии отсутствия ошибки несоответствия, Следовательно, ошибка несоответствия Типа (1) может появиться между устройствами IDCT, чья операционная точность удовлетворяет требованию MPEG.

Выходы IDCT-обработки являются целыми числами. Следовательно, после того, как было выполнена IDCT-обработка с использованием действительных чисел, результаты обработки должны быть округлены. В общем случае результаты обработки округляются до ближайшего целого. Однако, появляется проблема, если результат обработки представляет собой *. 5, где * - любое целое число. Стандарт MPEG не определяет, каким образом следует округлять результат *.5. Некоторые устройства IDCT округляют *.5. сверху, а другие устройства IDCT округляют *.5. снизу. Кроме того, появляются случаи, когда округление сверху или округление снизу зависят от знака результата обработки. Ошибки несоответствия, возникающие из-за только что описанных систематических ошибок округления, являются ошибками несоответствия Типа (2).

Ошибки несоответствия Типа (1) отличаются от ошибок несоответствия Типа (2), тем что ошибки Типа (1) появляются случайно в то время, как ошибки Типа (2) систематически. Поскольку ошибки Типа (1) являются случайными, положительные ошибки и отрицательные ошибки появляются с примерно равной вероятностью. Поэтому, при длительном выполнении кодирования с предсказанием можно ожидать, что ошибки несоответствия Типа (1) будут сведены на нет.

С другой стороны, поскольку ошибки несоответствия Типа (2) являются систематическими и присущи самой IDCT-обработке, такие ошибки постоянно имеют один и тот же знак. Соответственно, при длительном выполнении кодирования с предсказанием ошибка несоответствия будет накапливаться в одном направлении. Хотя каждая ошибка несоответствия Типа (2) составляет только +1 или -1, если накапливается много ошибок в одном направлении, накопления ошибка несоответствия будет большой.

Так как ошибки несоответствия Типа (1), хотя они и образуются, через некоторое время исчезают, ошибка Типа (1) не представляют большой проблемы. С другой стороны, поскольку ошибки несоответствия Типа (2) накапливаются в одном направлении, эти ошибки представляют проблему. В этой связи желательно предотвращать появление накапливающихся ошибок несоответствия Типа (2).

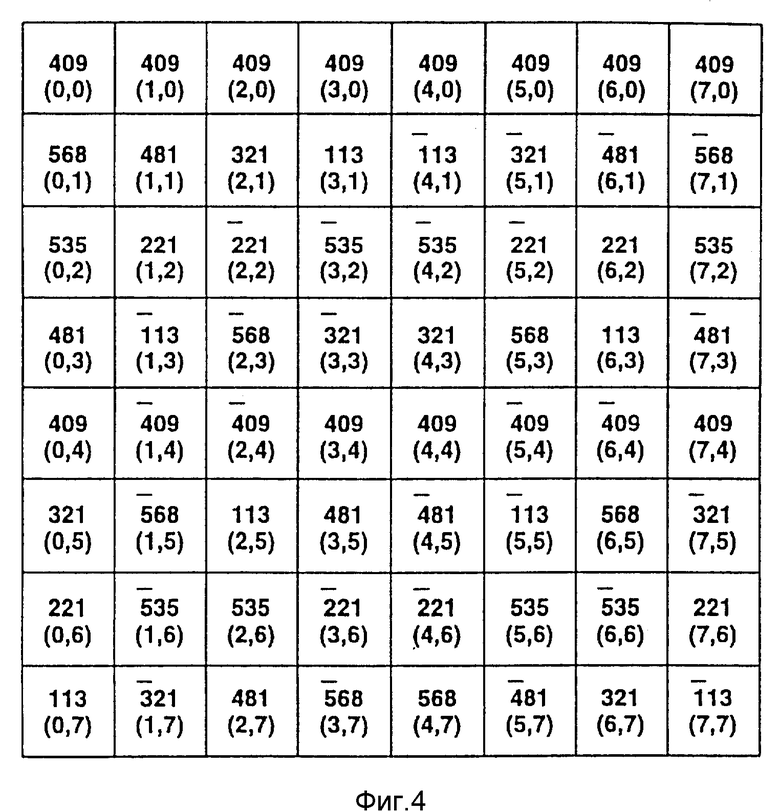

В системе MPEG1 было предложено выполнять обработку перед IDCT-обработкой, чтобы предотвратить появление ошибок несоответствия Типа (2). Обработка присваивает коэффициентам преобразования всех составляющих нечетные значения, кроме коэффициента преобразования составляющей (0.0) макроблока, с внутрикадровым кодированием кадра ("интра-макроблок"). В интра-макроблоке составляющая (0.0) является DC-составляющей. Как показано на фигуре 4, например, коэффициенты преобразования составляющих (0.1), (7.1), (2.3), (5.3), (1.5), (6.5), (3.7) и (4.7) изначально все равны 568. Поскольку это четное число, предварительная обработка устанавливает для этих коэффициентов нечетное значение, например, 567. Если IDCT-обработка применяется к предварительно обработанным коэффициентам преобразования, дробные результаты никогда не появятся.

Поскольку DC-составляющая интра-макроблока очень важна для появления кадра, получаемого из уплотненного сигнала движущегося изображения, точность ее представления ограничивается только 8 бит. Она не подвергается преобразованию к нечетному значению, поскольку это ухудшает точность этой важной составляющей. С другой стороны все коэффициенты преобразования, являющиеся результатом преобразования макроблока кадра, закодированного с использованием межкадрового кодирования ("неинтра-макроблок"), подвергаются обработке, подобной обработке коэффициентов преобразования составляющих, отличных от DC-составляющей интра-макроблока, чтобы ограничить значения коэффициентов преобразования только нечетными числами.

Обработка, при которой значения коэффициентов преобразования, подвергающиеся IDCT-преобразованию, приводятся все к нечетным значениям, называется обработкой на нечетность.

Посредством выполнения обработки на нечетность IDCT-обработка, как в устройстве уплотнения, так и в устройстве расширения, будет выполняться с округлением в соответствии с общим правилом. Это даст возможность поддерживать качество совмещаемых кадров между различными устройствами расширения.

Однако, несмотря на вышеописанную обработку на нечетность, вышеуказанные накапливающиеся ошибки несоответствия Типа (2) будут появляться в процессорах MPEG из-за того, что IDCT-обраотка может выдавать результаты типа *.5, где * - означает целое число. Условия, которые приводят к результату *.5, будут описаны далее на примере двумерного 8 x 8 IDCT, используемого в системе MPEG.

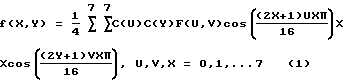

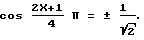

Двумерное 8 x 8 IDCT описывается следующим уравнением:

В вышеприведенном уравнении F(U, V) указывает DCT-коэффициенты, соответствующие двумерному IDCT. В уравнении (1) каждое значение выхода IDCT является действительным числом, то есть, рациональным числом или иррациональным числом. Поскольку *.5 рациональное число, сделав выходное значение IDCT иррациональным числом, можно предотвратить появление накапливающейся ошибки несоответствии. С другой стороны, если выходное значение является рациональным числом, существует вероятность того, что выходное значение будет *.5.

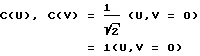

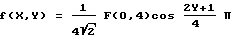

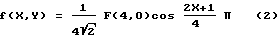

DCT-коэффициенты F(0,0), F(0,4), F(4,0), F(4,4) являются особыми DCT-коэффициентами. Если любой из этих DCT-коэффициентов имеет ненулевое значение, выходное значение IDCT является рациональным числом. Выходное значение IDCT в этом случае определяется следующим уравнением (2):

(X,Y) = 1/4F(0,0)

где

Таким образом, если только один из особых DCT-коэффициентов F(0,0), F (0,4), F(4,0), F(4,4) имеет ненулевое значение, кратное 4, но не кратное 8, выходное значение будет равно *.5.

Если четыре особых DCT-коэффициента являются единственными коэффициентами с ненулевым значением, выходное значение IDCT определяется уравнением (3):

Изменяя комбинации из X и Y, f(X,Y) в уравнении (3), можно иметь следующие значения:

1/8 [F(0,0) + F(0,4) + F (4,0) + F (4,4)]

1/8 [F(0,0) - F(0,4) + F (4,0) - F (4,4)]

1/8 [F(0,0) - F(0,4) + F(4,0) - F(4,4)]

1/8 [F(0,0) - F(0,4) - F(4,0) + F(4,4)] (4)

Таким образом, когда значения четырех особых коэффициентов таковы, что любое из выражений, представленных в уравнении (4), кратно 4, но не кратно 8, будет появляться результат *.5.

Таким образом, если четыре особых коэффициента имеют ненулевые значения, велика вероятность того, что выходное значение IDCT, будет равно *.5.

Также различные симметричные пары DCT-коэффициентов с ненулевыми значениями, отличные от только что рассмотренных четырех особых коэффициентов, могут дать выходное значение *.5.

(1) если пара коэффициентов X(2n+1, 2m+1), X(2m+1, 2n+1) имеет одно и то же ненулевое значение и это значение кратно 4, но не кратно 8; или

(2) если пара коэффициентов X(2n+1, 2n+1), X(8-2n-1, 8-2n-1) имеет одно и то же ненулевое значение и это значение кратно 4, но не кратно 8.

В вышеприведенных уравнениях X(i,j) является коэффициентов преобразования одной составляющей из двумерного 8 х 8 DCT.

Если текущий сигнал движущегося изображения уплотняется устройством уплотнения согласно системе MPEG, то часто образуются ненулевые DCT-коэффициенты в только что упомянутых комбинациях, которые могут дать выходное значение IDCT, равное *.5. Кроме того, значения четырех особых коэффициентов являются ненулевыми большую часть времени.

Поскольку самой общей причиной появления результата *.5 является комбинация DCT-коэффициентов, в которой значения четырех особых коэффициентов являются ненулевыми, предотвращение появления ошибки несоответствия из-за четырех особых коэффициентов существенно уменьшит вероятность появления ошибки несоответствия.

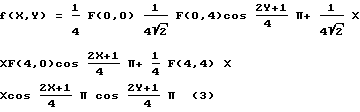

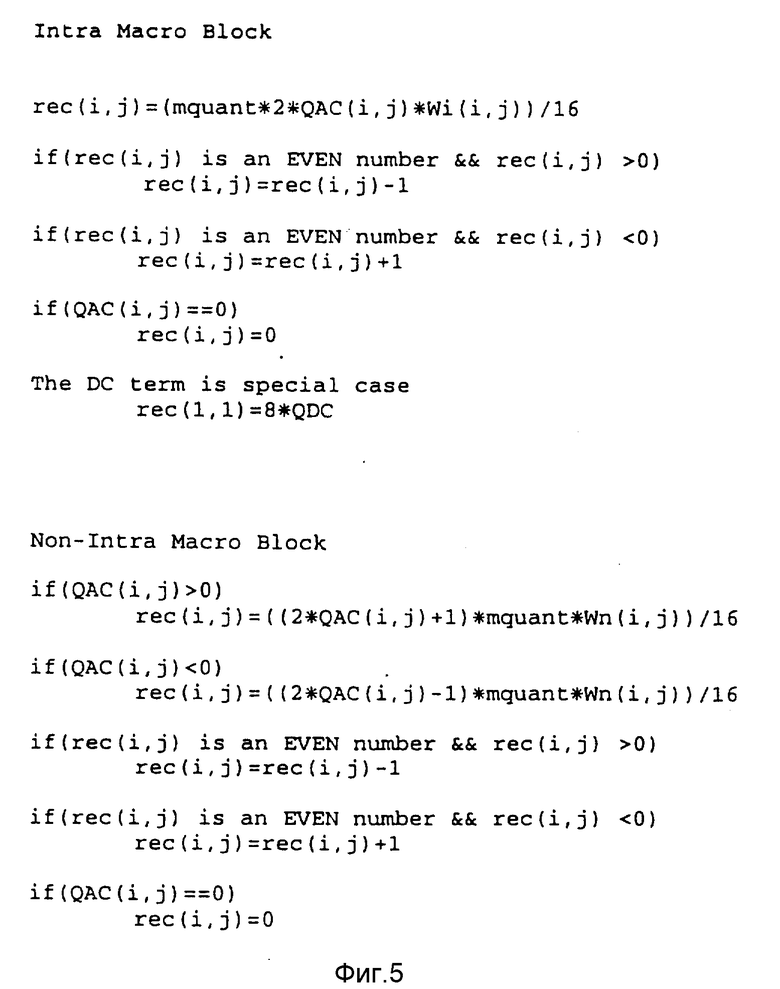

Способ обработки, с помощью которого интра-макроблок и неинтра-макроблок подвергаются инверсной дискретизации в MPEG1, показан на фиг. 5. На фиг. 5 QAC(i, j) является (i,j)-м DCT-коэффициентом, Wi(i,j) является (i,j)-м элементом матрицы весов, mquant является коэффициентом дискретизации и rec (i, j) является (i, j)-м инверсно дискретизированным DCT-коэффициентом. Способ обработки записан в синтаксисе C-языка программирования. Синтаксис этого языка изложен в Herbert Schildt, Using Turbo C. Osborne McGraw Hill (1988), в частности, на страницах 83 - 87.

Дискретизированные DCT-коэффициенты подвергаются обратной дискретизации и результирующие DCT-коэффициенты, затем подвергаются IDCT-обработке. Однако, в MPEG1 к DCT-коэффициентам, имеющим четное значение, добавляется +1 или -1, чтобы быть уверенным, что все DCT-коэффициенты, подвергшиеся IDCT-обработке, будут иметь нечетные значения. В результате этой операции, когда, например, только один из четырех особых коэффициентов F(0,0) имеет ненулевое значение, поскольку появляется ошибка несоответствия, когда F(0,0) кратно 4, но не кратно 8, если DCT-коэффициенты обрабатываются так, что все они имеют нечетное значение, результат, если DCT-коэффициент подвергся IDCT-обработке, не может быть равен *.5. Подобным же образом, если только один из других четырех особых коэффициентов F(0,4), F(4,0), F(4,4) имеет ненулевое значение, ошибка несоответствия не появится. Однако, если несколько из четырех особых коэффициентов имеют ненулевое значение, как можно видеть из фигуры 4, или если появились пары симметрично построенных коэффициентов, как в случаях (1) и (2), упомянутых выше, присвоение всем DCT-коэфифицентам нечетных значений не предотвратит появления ошибки несоответствия.

Следовательно, обработка на нечетность MPEG1 не предотвратит появления накапливающейся ошибки несоответствия, когда два или более DCT-коэффициентов имеют ненулевое значение. Кроме того, обработка не нечетность MPEG1 вдвое уменьшает разрешающую способность дискретизированных коэффициентов преобразования, поскольку коэффициенты преобразования с четными значениями не разрешены. Это ухудшает качество изображения. Если требуется высокое качество изображения, это представляет проблему. Очевидно желательно иметь лучший способ предотвращения накапливающихся ошибок несоответствия, чем тот, который предложен в MPEG1.

С учетом рассмотренных выше проблем, возникающих в предшествующих разработках, целью этого изобретения является получение способа и устройства, которые эффективно предотвращают появление накапливающихся ошибок несоответствия, когда коэффициенты преобразования подвергаются обратному ортогональному преобразованию и в котором разрешающая способность коэффициентов преобразования не ухудшается.

В частности, целью настоящего изобретения является создание способа и устройства для обратного ортогонального преобразования коэффициентов преобразования, которые эффективно решают проблему ошибок несоответствия.

В частности, целью настоящего изобретения является создание способа и устройства для обработки блока коэффициентов преобразования до выполнения обратного ортогонального преобразования блока коэффициентов преобразования, так чтобы предотвратить ошибки округления, когда блок коэффициентов преобразования подвергается обратному преобразованию.

Кроме того, целью этого изобретения является создание устройства уплотнения сигнала движущегося изображения, устройства расширения уплотненного сигнала движущегося изображения и носителя записи для уплотненного сигнала движущегося изображения, в которых исключаются ошибки несоответствия, и обеспечение мер, предотвращающих влияние ошибок несоответствия, чтобы они как можно меньше ухудшали бы качество изображения.

Цель этого изобретения предполагает эффективное и несложное предотвращение ошибок несоответствия, которые не могут быть предотвращены известными способами.

Соответственно изобретение обеспечивает способ обработки набора коэффициентов преобразования для получения невосприимчивого к ошибкам набора коэффициентов преобразования для обработки посредством обратного ортогонального преобразования. Невосприимчивый к ошибкам набор коэффициентов преобразования свободен от ошибок округления, если он подвергается обратному ортогональному преобразованию. При этом способе коэффициенты преобразования суммируются. Четность суммы (то есть, является ли сумма нечетной или четной) оценивается. Если устанавливается, что сумма четная, инвертируется четность одного из коэффициентов преобразования с инвертированной четностью. Коэффициент преобразования с инвертированной четностью делает контрольную сумму нечетной. В конце концов, набор коэффициентов преобразования, включающий коэффициент преобразования с инвертированной четностью, обеспечивает невосприимчивый к ошибкам набор.

Изобретение также обеспечивает устройство для предварительной обработки набора коэффициентов преобразования для получения невосприимчивого к ошибкам набора коэффициентов преобразования для обработки посредством обратного ортогонального преобразования. Невосприимчивый к ошибкам набор коэффициентов преобразования свободен от ошибок округления, если он подвергается обратному ортогональному преобразованию. Устройство содержит накопитель. Накопитель получает каждый из коэффициентов преобразования в наборе и суммирует их. Схема оценки четности получает эту сумму от накопителя и оценивает четность суммы. Схема инвертирования четности работает тогда, когда схема оценки четности устанавливает, что контрольная сумма четная, и инвертирует четность одного из коэффициентов преобразования для получения коэффициента преобразования с инвертированной четностью. Коэффициент преобразования с инвертированной четностью делает контрольную сумму нечетной. В конце концов схема создает набор коэффициентов преобразования, включающий коэффициент преобразования с инвертированной четностью, в виде невосприимчивого к ошибкам набора.

Кроме того, изобретение обеспечивает способ обратного ортогонального преобразования набора коэффициентов преобразования без появления ошибок округления. Каждый из коэффициентов преобразования представляется двоичным числом. В этом способе оценивается младший бит каждого из коэффициентов преобразования в наборе. В наборе подсчитываются коэффициенты преобразования, имеющие единичный младший бит. Результат счета оценивается, чтобы определить, является ли он четным числом. Если результат счета оценивается как четное число, один из коэффициентов преобразования изменяется, чтобы получить видоизмененный коэффициент преобразования. Видоизмененный коэффициент преобразования делает результат счета нечетным числом. В конце концов, набор коэффициентов преобразования, включающий видоизмененный коэффициент преобразования, подвергается ортогональному преобразованию.

Изобретение также обеспечивает устройство для обратного ортогонального преобразования набора коэффициентов преобразования без появления ошибок округления. Устройство включает схему суммирования коэффициентов преобразования для получения суммы и схему оценки четности, которая оценивает четность суммы. Схема приведения значения суммы к нечетному работает тогда, когда схема оценки четности устанавливает, что контрольная сумма четная, и преобразует четность одного из коэффициентов преобразования для получения коэффициента преобразования с инвертированной четностью. Коэффициент преобразования с инвертированной четностью делает сумму нечетной. В конце концов, схема обратного ортогонального преобразования получает набор коэффициентов преобразования, включающий коэффициент преобразования с инвертированной четностью, от устройства приведения значения суммы к нечетному.

Изобретение также обеспечивает устройство для обратного ортогонального преобразования набора коэффициентов преобразования без появления ошибок округления. Устройство содержит схему оценки младшего бита для оценки значения младшего бита каждого коэффициента преобразования. Счетная схема выполняет подсчет тех коэффициентов преобразования, для которых схема оценки младшего бита установила, что они имеют значение младшего бита, равное единице. Схема оценки результата счета оценивает, является ли результат счета из счетной схемы четным числом. Таким образом, устройство приведения результата счета к нечетному значению работает тогда, когда схема оценки результата счета устанавливает, что результат счета является четным числом, чтобы изменить один из коэффициентов преобразования для получения видоизмененного коэффициента преобразования. Видоизмененный коэффициент преобразования делает результат счета нечетным числом. В конце концов, схема обратного ортогонального преобразования получает набор коэффициентов преобразования, включая видоизмененный коэффициент преобразования, из схемы приведения результата счета к нечетному значению.

Изобретение также обеспечивает устройство для уплотнения сигнала движущегося изображения. Сигнал движущегося изображения включает кадры, а каждый кадр делится на блоки. Устройство содержит предиктивный кодер, который кодирует с предсказанием блоки сигнала движущегося изображения путем использования блоков сопоставления опорного кадра для формирования блоков отличий. Кодер блока отличия уплотняет блоки отличий, поступающие от предиктивного кодера, чтобы сформировать уплотненный сигнал движущегося изображения. Кодер блока отличий включает схему ортогонального преобразования, которая осуществляет ортогональное преобразование блока отличий, поступающего от предиктивного кодера, для получения блоков коэффициентов преобразования, и квантователь, который дискретизирует блоки коэффициентов преобразования, поступающие от схемы ортогонального преобразования, для получения уплотненных сигнальных блоков. Уплотненный сигнал движущегося изображения формируется из уплотненных сигнальных блоков.

Устройство также включает локальный декодер, который расширяет уплотненные сигнальные блоки, поступающие от кодера блока отличий, для получения восстановленных блоков отличий без появления ошибок округления, когда уплотненные сигнальные блоки подвергаются обратному ортогональному преобразованию. Локальный декодер включает инверсный квантователь, который осуществляет обратную дискретизацию уплотненных сигнальных блоков, поступающих от кодера блоков отличий, для получения блоков восстановленных коэффициентов преобразования. Накопитель суммирует восстановленные коэффициенты преобразования в каждом блоке коэффициентов преобразования, поступающие от инверсного квантователя, для получения суммы, четность которой оценивается схемой оценки четности. Устройство приведения суммы к нечетному значению работает, когда схема оценки четности устанавливает, что контрольная сумма четная, чтобы инвертировать четность одного из восстанавливаемых коэффициентов преобразования в блоке для получения коэффициента преобразования с инвертированной четностью, что делает сумму нечетной. В конце концов, схема обратного ортогонального преобразования получает блок восстановленных коэффициентов преобразования, включая коэффициент преобразования с инвертированной четностью, от устройства приведения значения суммы к нечетному. Схема обратного ортогонального преобразования обеспечивает восстановленные блоки отличий.

Устройство также включает предиктивный декодер, который декодирует с предсказанием восстанавливаемые блоки отличий, поступающие от локального декодера, чтобы реконструировать кадровые блоки, соответствующие блокам сигнала движущегося изображения. И наконец, устройство включает память изображения, которая хранит реконструированные блоки кадров, поступающие от предиктивного декодера, в виде блоков реконструированного кадра для использования как опорного кадра для предиктивного кодирования других кадров сигнала движущегося изображения.

В только что описанном устройстве накопитель, схема оценки четности и устройство приведения суммы к нечетному значению в локальном декодере могут быть заменены: схемой оценки младшего бита, которая оценивает младший бит каждого из восстанавливаемых коэффициентов преобразования; счетчиком, который обеспечивает подсчет восстанавливаемых коэффициентов преобразования в каждом блоке, которые имеют единичные значения младших бит; схемой оценки результата счета, которая оценивает, является ли результат работы счетчика четным числом; и схемой приведения результата счета к нечетному значению, которая работает тогда, когда схема оценки результата счета устанавливает, что результат счета четное число, чтобы изменить один из восстанавливаемых коэффициентов преобразования в блоке для получения видоизмененного коэффициента преобразования, который делает результат счета нечетным числом.

Изобретение также обеспечивает устройство для расширения уплотненного сигнала движущегося изображения, чтобы получить выходной сигнал движущегося изображения. Уплотнительный сигнал движущегося изображения включает фрагменты сигнала, каждый из которых представляет кадр выходного сигнала движущегося изображения. Фрагменты сигнала включают закодированные (с переменной длиной слова) уплотненные сигнальные блоки. Устройство содержит инверсный кодер с переменной длиной слова, который применяет обратное кодирование с переменной длиной слова к закодированным (с переменной длиной слова) уплотненным сигнальным блокам для обеспечения уплотненных сигнальных блоков.

Декодер расширяет уплотненные сигнальные блоки от инверсного с переменной длиной слова для получения восстановленных блоков отличий без появления ошибок округления, когда уплотненные сигнальные блоки подвергаются ортогональному преобразованию. Декодер включает инверсный квантователь, который осуществляет инверсную дискретизацию каждого уплотненного сигнального блока из кодера блока отличий, чтобы получить блок восстановленных коэффициентов преобразования. Накопитель суммирует восстановленные коэффициенты преобразования в блоке коэффициентов преобразования, поступающие от инверсного квантователя, для получения суммы, четность которой оценивается схемой оценки четности. Устройство приведения суммы к нечетному значению работает, когда схема оценки четности устанавливает, что контрольная сумма четная, чтобы проинвертировать четность одного из восстанавливаемых коэффициентов преобразования в блоке, чтобы получить коэффициент преобразования с инвертированной четностью, который сделает контрольную сумму нечетной. Схема обратного ортогонального преобразования получает блок восстанавливаемых коэффициентов преобразования, включая коэффициент преобразования с инвертированной четностью, от устройства приведения суммы к нечетному значению и обеспечивает восстановленные блоки отличий.

Устройство также включает предиктивный декодер, который декодирует с предсказанием восстанавливаемые блоки отличий, поступающие от декодера, для реконструкции блоков изображения, а память изображения, которая хранит реконструируемые кадровые блоки, поступающие от предиктивного декодера, в виде блоков реконструированного кадра. Реконструированный кадр используется как опорный кадр для предиктивного декодирования других кадров сигнала движущегося изображения. И наконец, устройство включает схему, которая считывает выходной сигнал движущегося изображения из памяти изображения.

В только что описанном устройстве расширения накопитель, схема оценки четности и устройство приведения суммы к нечетному значению в декодере могут быть заменены схемой оценки младшего бита, которая оценивает значение младшего бита каждого из восстановленных коэффициентов преобразования; счетчиком, который обеспечивает подсчет устанавливаемых коэффициентов преобразования в каждом блоке, имеющих единичные значения младших бит; схемой оценки результата счета, которая устанавливает, является ли результат счета четным числом; и схемой приведения результата счета к нечетному значению, которая работает, когда схема оценки результата счета устанавливает, что результат счета - четное число, чтобы изменить один из устанавливаемых коэффициентов преобразования в блоке для получения видоизмененного коэффициента преобразования, который делает результат счета нечетным числом

Изобретение, кроме того, обеспечивает способ уплотнения сигнала движущегося изображения для получения уплотненного сигнала движущегося изображения. В этом способе к блокам сигнала движущегося изображения применяется предиктивное кодирование и ортогональное преобразование, чтобы получить блоки коэффициентов преобразования, из которых формируется уплотненный сигнал движущегося изображения. Суммы блоков коэффициентов преобразования приводятся к нечетному значению, до применения обратного ортогонального преобразования и предиктивного декодирования, чтобы получить блоки реконструированного кадра для использования в качестве опорного кадра при предиктивном кодировании других кадров сигнала движущегося изображения.

Изображение также обеспечивает способ уплотнения сигнала движущегося изображения, обеспечивающий уплотненный сигнал движущегося изображения. В этом способе выявляется движение между блоками кадра сигнала движущегося изображения и блоками реконструированного сигнала изображения, служащего опорным сигналом, и к опорному кадру применяется компенсация движения в ответ на обнаружение движения, чтобы образовать блоки сопоставления опорного кадра. Блоки сопоставления опорного кадра используются при предиктивном кодировании блоков сигналов движущегося изображения, чтобы получить блок отличий. Блоки отличий подвергаются ортогональному преобразованию для получения коэффициентов преобразования. Уплотненный сигнал формируется из блоков коэффициентов преобразования посредством применения дискретизации и кодирования с переменной длиной слова. Прежде чем применить обратное ортогональное преобразование к блокам коэффициентов преобразования для получения блоков восстановленных отличий, сумма каждого блока коэффициентов преобразования приводится к нечетному значению, чтобы предотвратить появление ошибок округления в процессе обратного ортогонального преобразования. И наконец, к блокам восстановленных отличий применяется предиктивное декодирование, чтобы получить блоки реконструированного кадра для использования в качестве опорного кадра при применении предиктивного кодирования к другим кадрам сигнала движущегося изображения.

И наконец, изобретение обеспечивает носитель записи, на который записывается уплотненный сигнал движущегося изображения, представляющий движущееся изображение. Уплотненный сигнал движущегося изображения формируется из сигнала движущегося изображения посредством применения предиктивного кодирования и ортогонального преобразования к блокам сигнал движущегося изображения для получения блоков коэффициентов преобразования, из которых формируется уплотненный сигнал движущегося изображения. Суммы блоков коэффициентов преобразования приводятся к нечетному значению до применения обратного ортогонального преобразования и предиктивного декодирования к блокам коэффициентов преобразования, чтобы получить блоки реконструированного кадра для использования в качестве опорного кадра при предиктивном кодировании других кадров сигнала движущегося изображения.

Теперь согласно изобретению будет описан путь, предотвращающий появление накапливающихся ошибок несоответствия.

Анализ уравнения (4) показывает, что несоответствие появляется, когда выражения в уравнении порождают результат (2n+1)/2, где n - любое целое число.

Уравнение (4) может быть записано как

f(X,Y)= 1/8 ACC,

где

ACC есть сумма всех коэффициентов.

Наиболее часто встречающийся вид несоответствий:

f(X,Y) = 1/8 ACC = (2n+1)/2 = 1/8 (4*(2n+1))

Из этого видно, что, если ACC сделать нечетным числом, ошибка несоответствия никогда не появится.

Исходя из этого, в данном изобретении используется схема, предусматривающая обратную дискретизацию DCT коэффициентов и затем, до IDCT обработки, расчет суммы DCT коэффициентов. Если сумма DCT коэффициентов является четным числом (то есть, контрольная сумма - четная), изменяется четность одного из коэффициентов, чтобы сделать нечетной сумму DCT коэффициентов (то есть, сделать контрольную сумму нечетной). Достаточно изменить четность только одного из DCT коэффициентов, чтобы сделать нечетной сумму DCT коэффициентов. Кроме того, может быть изменена четность коэффициента, который оказывает наименьшее влияние на выходное значение IDCT. Другими словами, это изобретение, путем проверки четности суммы DCT коэффициентов до IDCT обработки и, если контрольная сумма четная, путем изменения четности одного из DCT коэффициентов для приведения суммы DCT коэффициентов к нечетному значению, эффективно предотвращает появление ошибок несоответствия.

Следует подчеркнуть, что согласно изобретению достаточно изменить четность только одного DCT коэффициента, чтобы сделать нечетной суммы DCT коэффициентов. MPEG1 делает нечетными все DCT коэффициенты, что вдвое уменьшает разрешающую способность DCT коэффициентов, подвергающихся IDCT обработке. С другой стороны, процедура предотвращения ошибок несоответствия согласно настоящему изобретению делает сумму DCT нечетной таким образом, чтобы существенно не уменьшить точность предоставления входных и выходных значений IDCT. При применении способа согласно настоящему изобретению в устройстве уплотнения сигнала движущегося изображения, в устройстве расширения уплотненного сигнала движущегося изображения или в устройстве для передачи уплотненного сигнала движущегося изображения, ухудшение качества изображения будет минимальным.

Кроме того, если способ согласно настоящему изобретению применяется в системе MPEG, минимальный шаг дискретизации может быть равен 1, в отличие от известного способа, в котором минимальный шаг дискретизации был равен 2.

Краткое описание сопроводительных чертежей

На фиг.1 представлена блок-схема, показывающая структуру известного устройства уплотнения сигнала движущегося изображения согласно системе MPEG.

На фиг.1 представлена блок-схема, показывающая структуру известного устройства расширения сигнала движущегося изображения согласно системе MPEG.

На фиг.3 показана последовательность уплотнения сигнала движущегося изображения в системе MPEG.

На фиг.4 показаны рабочие примеры значений коэффициентов DCT.

На фиг.5 показывает шаги обработки, используемой для обратной дискретизации интра-макроблоков и неинтра-макроблоков в известной системе MPEG1.

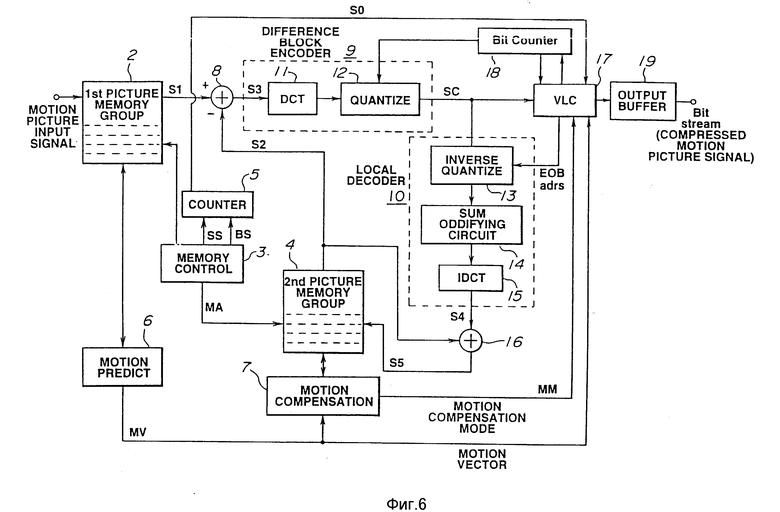

На фиг.6 представлена блок-схема, раскрывающая структуру первого варианта устройства уплотнения сигнала движущегося изображения согласно изобретению.

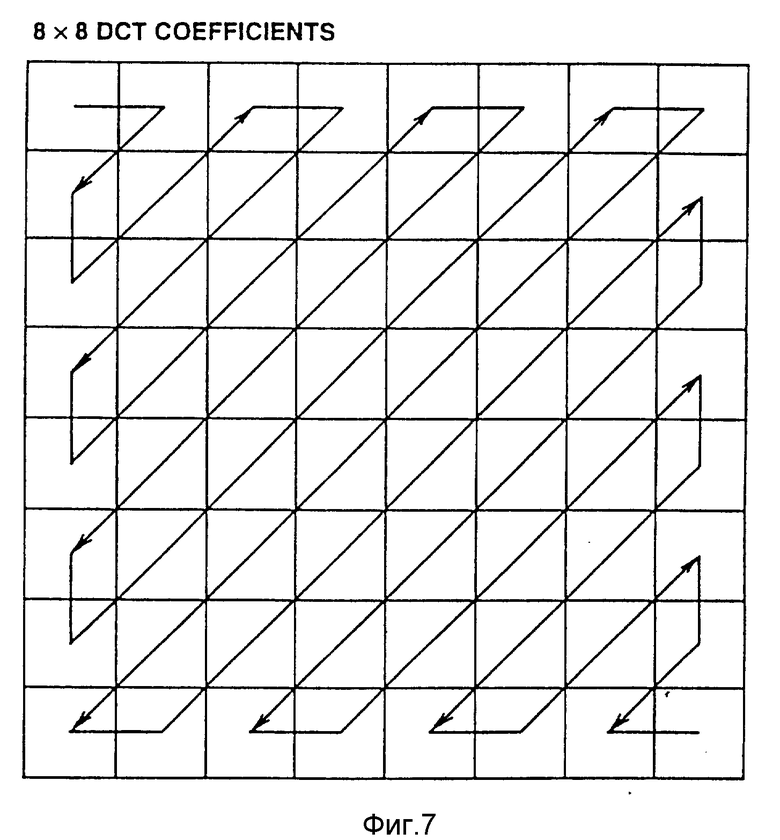

Фиг. 7 показывает, как считывается блок коэффициентов DCT с использованием сканирования зигзагом.

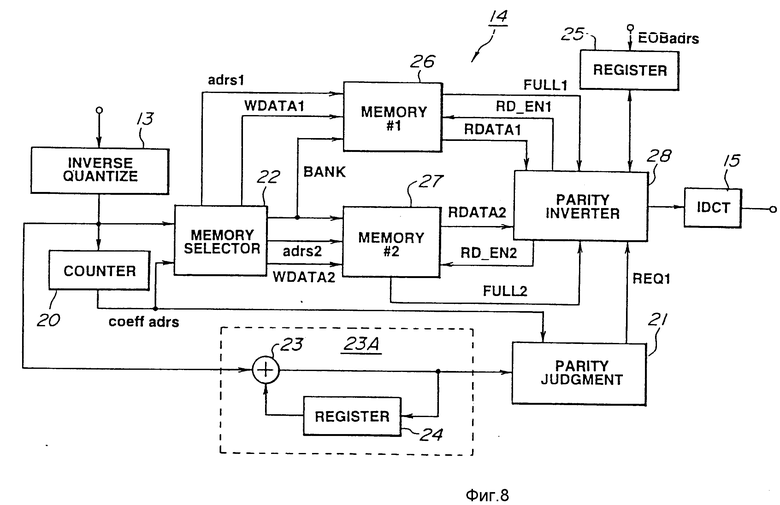

Фиг. 8 представляет блок-схему первого практического варианта схемы приведения к нечетной сумме 14, показанной на фиг.6.

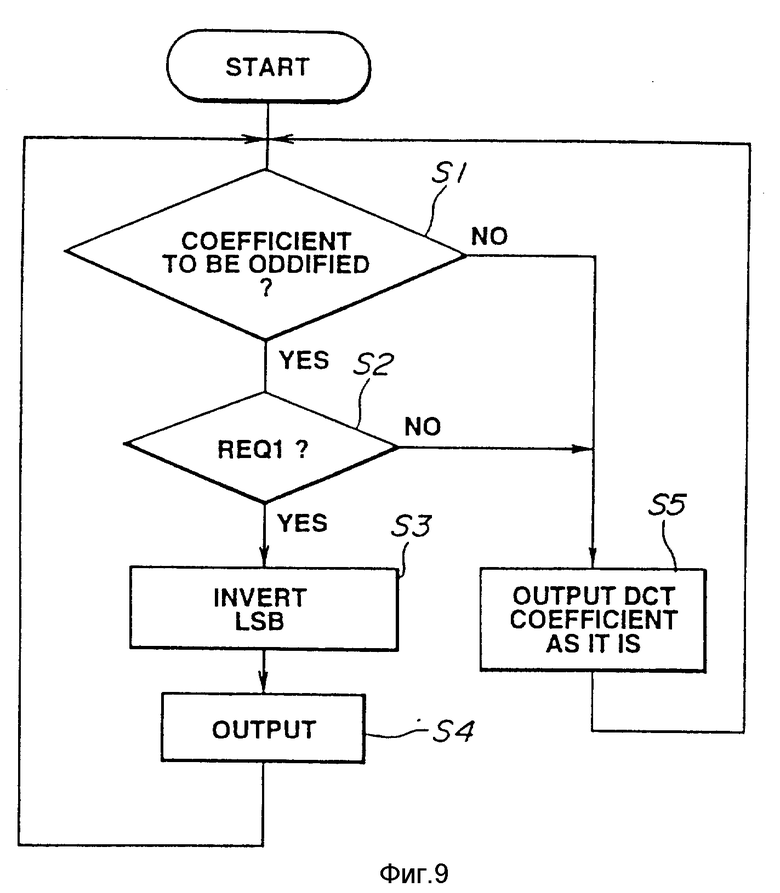

Фиг. 9 представляет блок-схему функционирования схемы приведения к нечетной сумме, показанной на фиг.8.

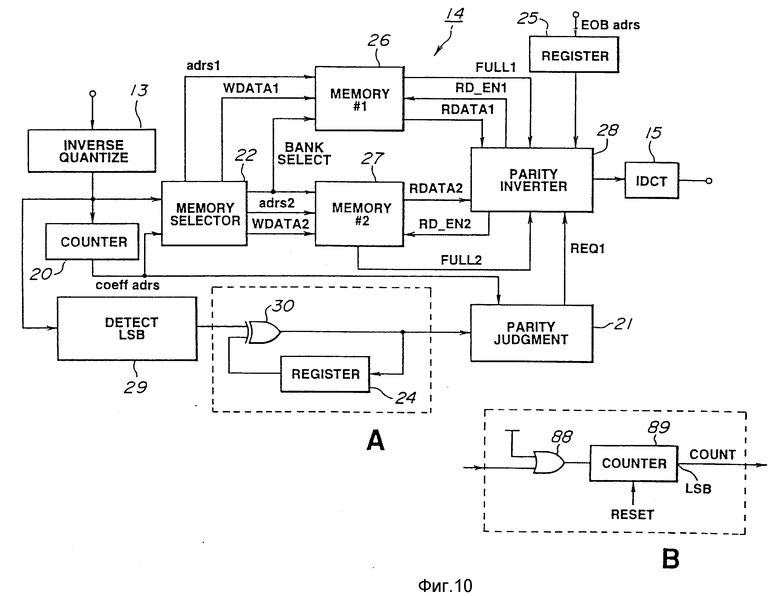

На фиг. 10A представлена блок-схема второго варианта схемы приведения к нечетной сумме, показанной на фиг.6.

Фиг. 10B показывает изменение во втором варианте схемы приведения к нечетной сумме, показанной на фиг.6.

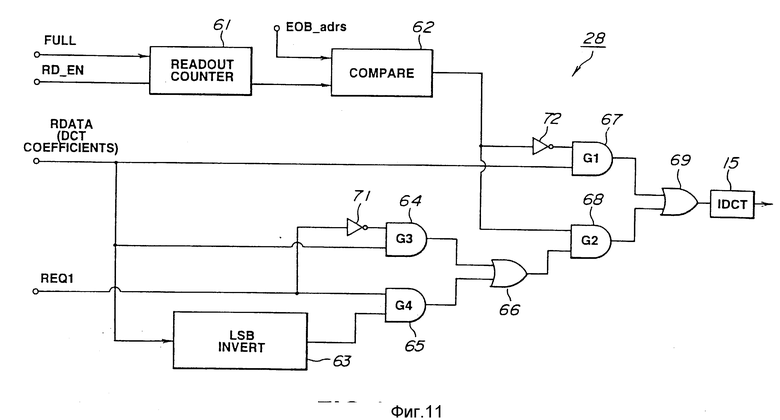

На фиг. 11 показана блок-схема первого варианта инвертора контроля четности, показанного на фиг.8.

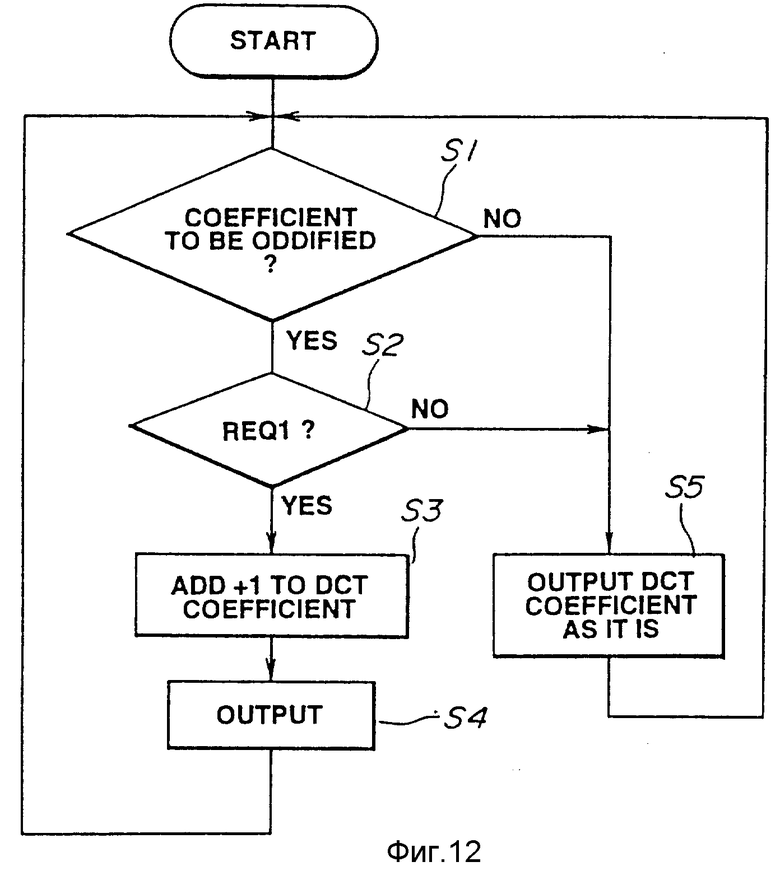

На фиг. 12 представлена блок-схема, поясняющая работу второго варианта вышеупомянутого инвертора контроля четности.

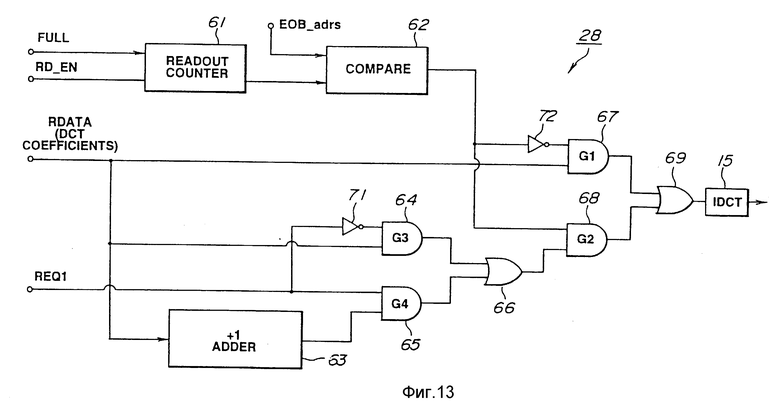

На фиг.13 показана блок-схема второго варианта вышеупомянутого инвертора контроля четности.

На фиг.14 представлена блок-схема, объясняющая работу третьего варианта вышеупомянутого инвертора контроля четности.

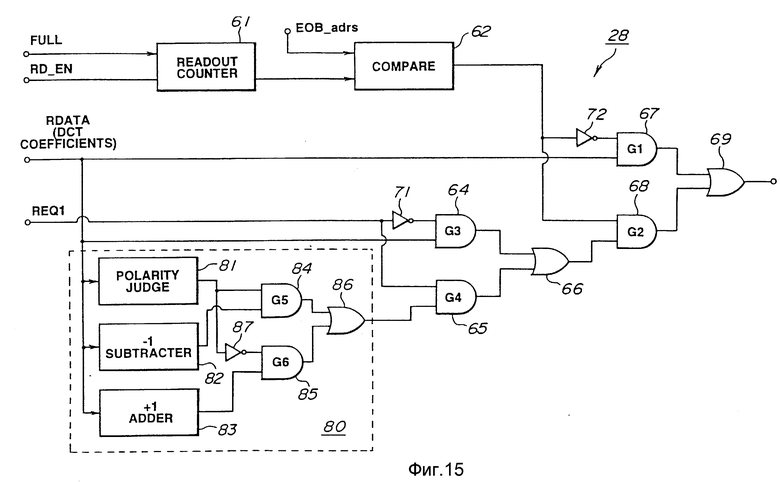

На фиг. 15 представляет блок-схему третьего варианта вышеупомянутого инвертора контроля четности.

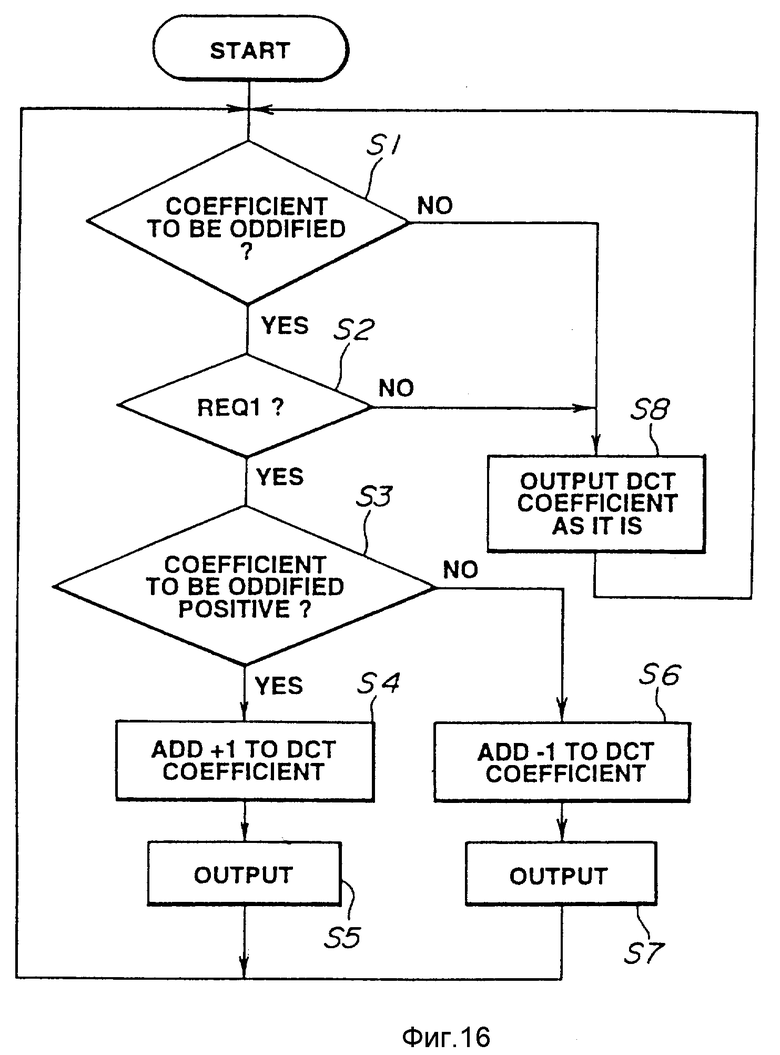

На фиг. 16 показана блок-схема, объясняющая работу четвертого варианта вышеупомянутого инвертора контроля четности.

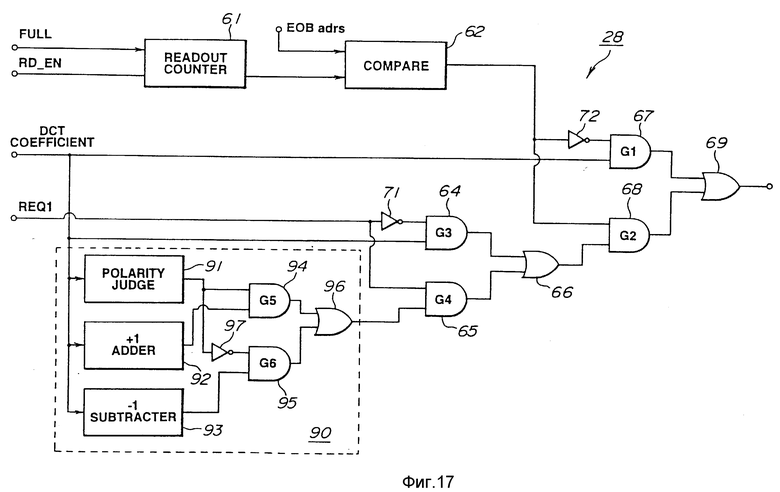

На фиг. 17 показана блок-схема четвертого варианта вышеупомянутого инвертора контроля четности.

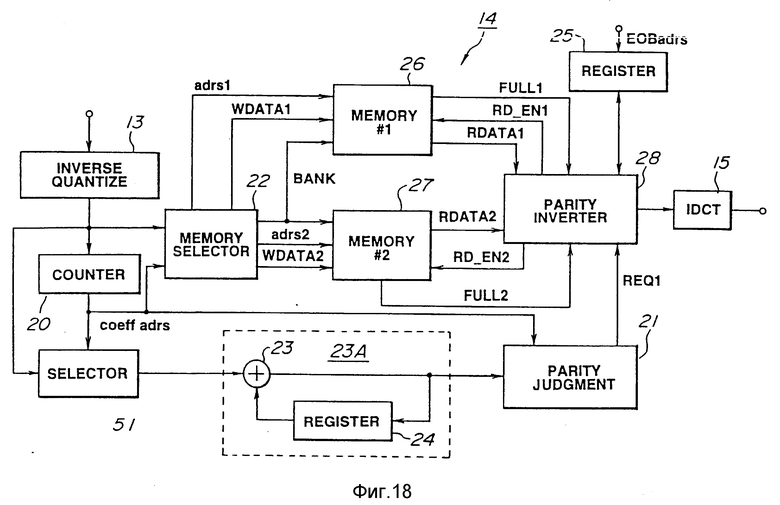

На фиг. 18 представлена блок-схема третьего варианта схемы приведения к нечетной сумме, показанной на фиг.6.

На фиг.19 показана блок-схема структуры первого варианта устройства расширения уплотненного сигнала движущегося изображения согласно изобретению.

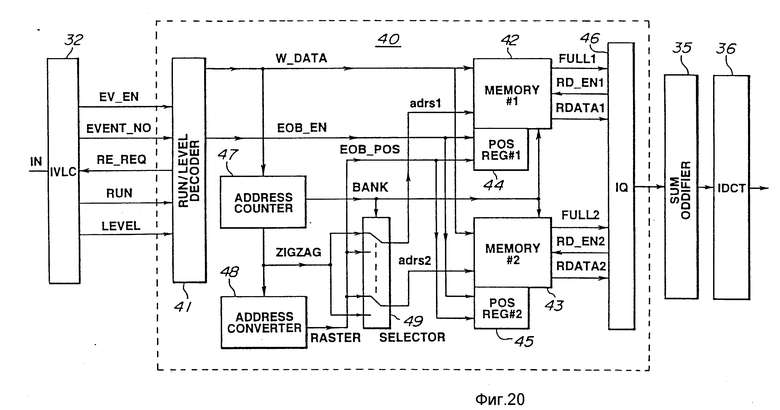

Фиг.20 представляет блок-схему инверсного квантователя и устройства приведения к нечетной сумме в устройстве расширения уплотненного сигнала движущегося изображения, показанного на фиг.19.

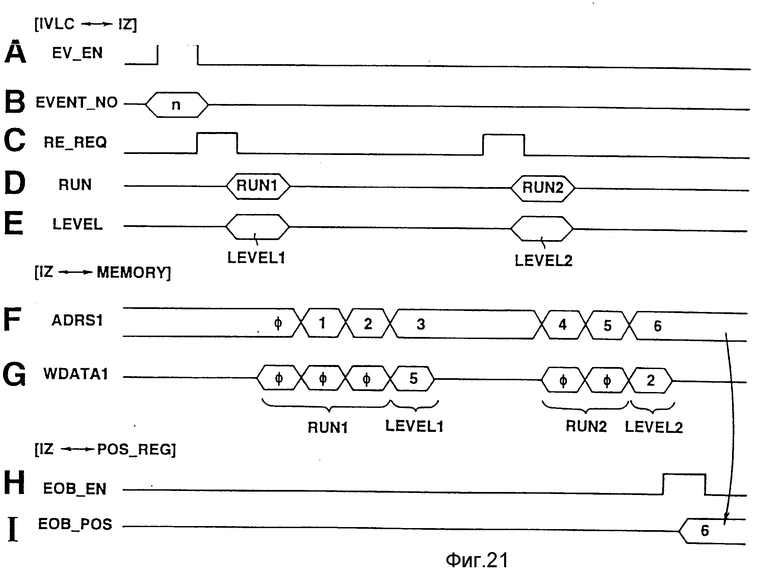

На фиг. 21 представлена временная диаграмма, поясняющая работу вышеупомянутых инверсного квантователя и устройства приведения к нечетной сумме.

На фиг.22 представляет блок-схему структуры второго варианта устройства уплотнения сигнала движущегося изображения согласно изобретению.

На фиг.23 показана блок-схема первого варианта схемы приведения к нечетной сумме во втором варианте устройства уплотнения сигнала движущегося изображения, показанного на фиг.22.

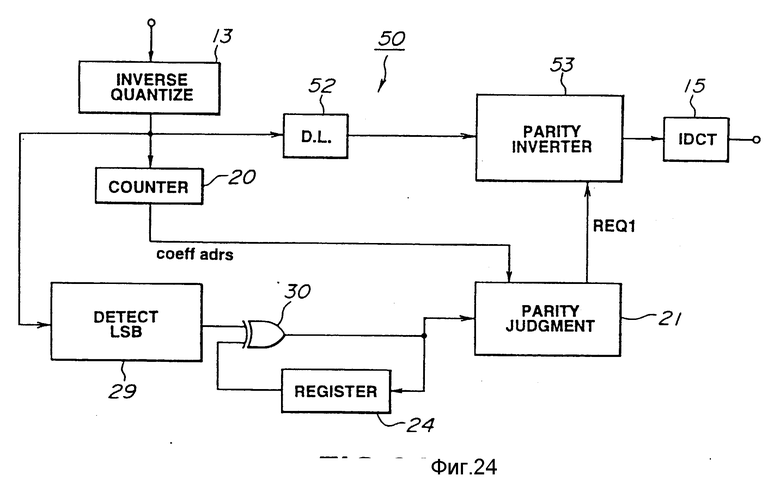

На фиг.24 показана блок-схема второго варианта схемы приведения к нечетной сумме во втором варианте устройства уплотнения сигнала движущегося изображения, показанном на фиг.22.

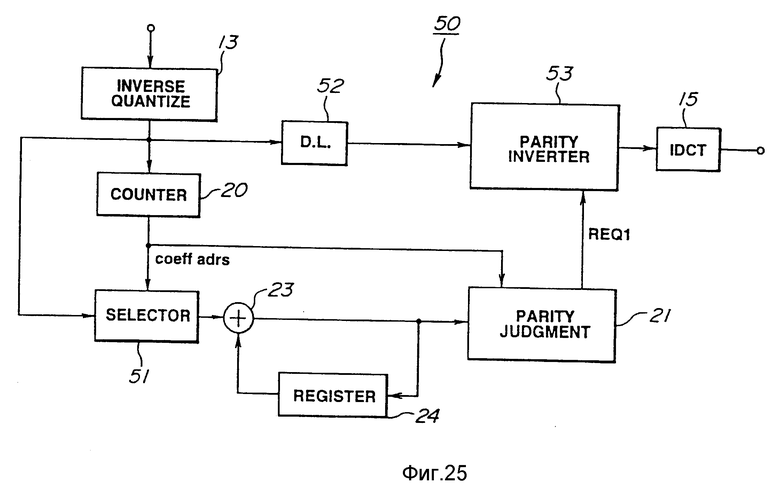

На фиг. 25 показана блок-схема третьего варианта схемы приведения к нечетной сумме во втором варианте устройства уплотнения сигнала движущегося изображения, показанном на фиг.22.

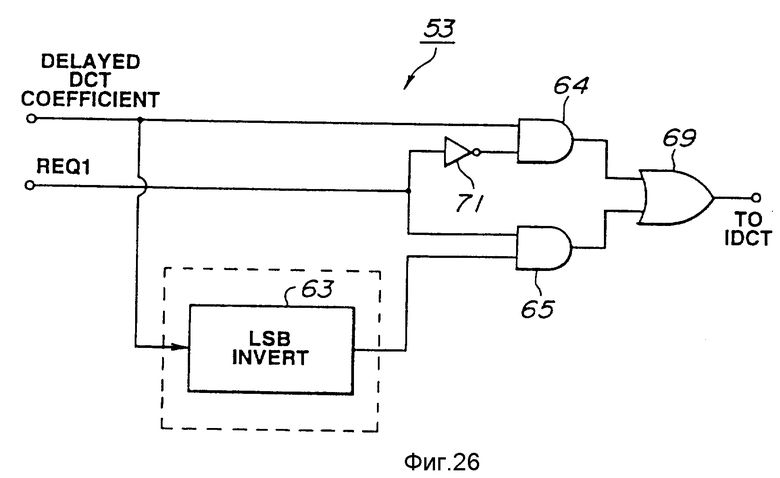

Фиг. 26 представляет блок-схему варианта инвертора контроля четности в схемах приведения к нечетной сумме, показанных на фиг.23-25.

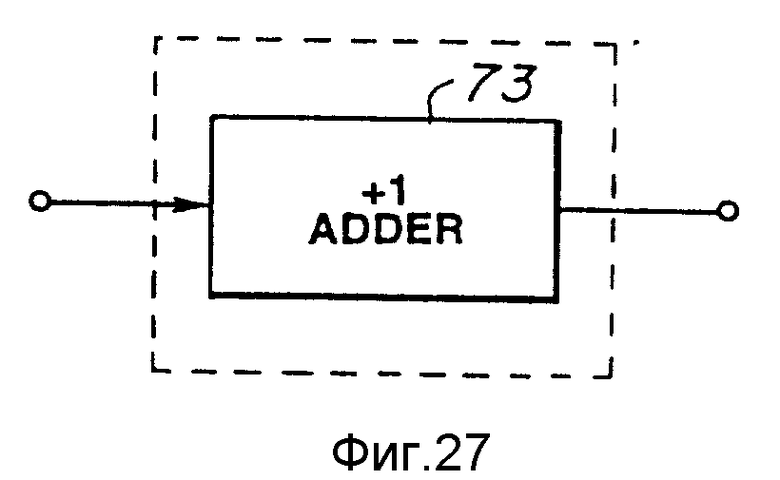

На фиг. 27 показано первое изменение в инверторе контроля четности, показанном на фиг.26.

На фиг. 28 показано второе изменение в инверторе контроля четности, показанном на фиг.26.

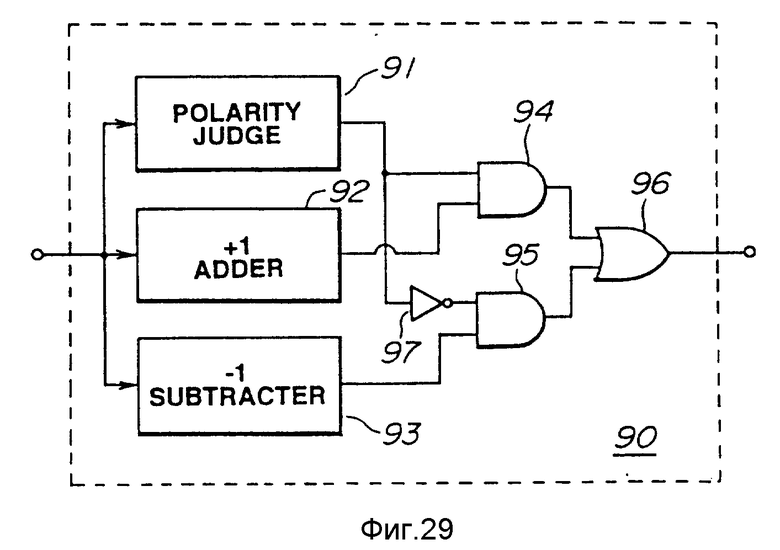

На фиг. 29 показано третье изменение в инверторе контроля четности, показанном на фиг.26.

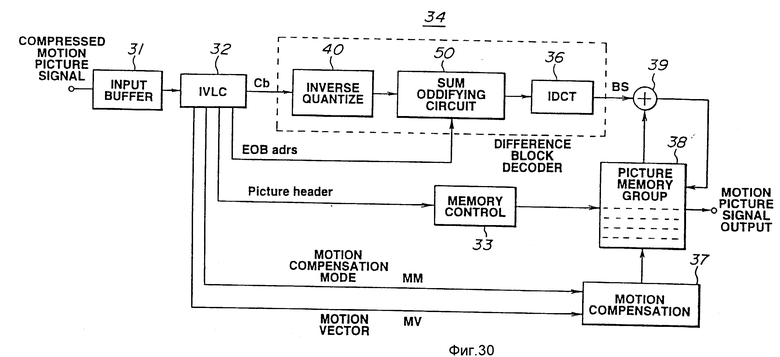

На фиг.30 показана блок-схема структуры второго варианта устройства расширения уплотненного сигнала движущегося изображения согласно изобретению.

Наилучший вариант воплощения изобретения

Теперь со ссылками на рисунке будут описаны предпочтительные варианты реализации способа обратного дискретного косинусного преобразования, устройство обратного косинусного преобразования, устройство уплотнения сигнала движущегося изображения, устройство расширения уплотненного сигнала движущегося изображения, носитель записи и устройство передачи.

Изобретение используется применительно к системе гибридного кодирования, в которой скомбинированы предиктивное кодирование с компенсацией движения и дискретное косинусное преобразование (DCT). Такая гибридная система кодирования описана в H.261 of ISO-IEC/JTC1/SC2/WG11 (обычно называемом MPEG) CCITT (Международного Консультативного Комитета по Телеграфии и Телефонии), который является Международным Комитетом для издания, в том числе, и стандартов для уплотнения сигналов движущегося изображения и уплотнения движущегося изображений для хранения на носителе записи. Базовая конфигурация гибридной системы кодирования MPEG хорошо известна. Раздел WG11 включает полезный глоссарий используемых в нем терминов.

Предиктивное кодирование с компенсацией движения является способом уменьшения избыточности сигнала движущегося изображения путем использования корреляции сигнала движущегося изображения во временной области. Предсказание компенсации движения текущего кадра (то есть, кадра, который сейчас кодируется ) выполняется с использованием другого, уже декодированного кадра движущегося изображения в качестве опорного кадра. Ошибки, являющиеся результатом предсказания с компенсацией движения, включаются в уплотненный сигнал вместе с вектором движения, режимом предсказания и т.д. Это значительно уменьшает количество информации в уплотненном сигнале движущегося изображения, необходимое для представления текущего кадра.

Сигнал ошибки предсказания с компенсацией движения уплотняется путем использования устройства уплотнения сигнала, который использует пространственную корреляцию каждого кадра, образующего движущееся изображение. Устройство уплотнения сигнала отличий обычно включает схему ортогонального преобразования, такую как DCT-схему и квантователь. DCT является видом ортогонального преобразования, которое концентрирует мощность сигнала в отдельных частотных составляющих как результат внутрикадровой (кадровой или полевой) двумерной корреляции изображения. Таким образом, только сконцентрированные и распределенные коэффициенты включаются в уплотненный сигнал либо непосредственно, либо после дополнительного уплотнения. Это еще уменьшает количество информации в уплотненном сигнале движущегося изображения, необходимое для представления текущего кадра.

Межкадровое предиктивное кодирование с компенсацией движения можно выполнять между кадрами сигнала движущегося изображения. Как вариант, если сигнал движущегося изображения является уплотненным (черезстрочным) сигналом, предиктивное кодирование с компенсацией движения можно выполнять между полями. Вдобавок межкадровое предиктивное кодирование с компенсацией движения может быть адаптивно включено между межкадровым кодированием и межполевым кодированием в зависимости от характеристик сигнала движущегося изображения.

I. Первый вариант воплощения изобретения

Рабочий вариант конфигурации устройства уплотнения сигнала движущегося изображения, в котором применяется изобретение, показан на фигуре 6. В устройстве, показанном на фиг.6, сигнал движущегося изображения делится на кадры и уплотняется кадр за кадром. Каждый кадр делится на кадровые блоки, и кадр уплотняется блок за блоком. Уплотняемый кадровый блок будем называть текущим кадровым блоком. Текущий кадровый блок управляется блоком кадра, который называется текущим кадром.

Сигнал движущегося изображения, обычно видеосигнал, доставляется в первое устройство памяти кадров 2, где временно хранятся многочисленные кадры сигнала движущегося изображения. Контроллер памяти 3 управляет считыванием кадров из первого устройства памяти кадров 2 и второго устройства памяти кадров 4. Контроллер памяти 3 также доставляет сигнал начала слоя SS и сигнал начала макроблока BS к счетчику слоя/макроблока 5. Контроллер памяти доставляет эти сигналы синхронно-соответственно с каждым слоем и каждым макроблоком каждого кадра (например, текущего кадра), считанного из первого устройства памяти кадра 2 для уплотнения. Слой является горизонтальной строкой блоков, показывающей всю ширину кадра.

Устройство предсказания движения 6 выполняет предсказание движения путем поблочного сопоставления блока текущего кадра с множеством блоков предыдущих и последующих кадров, хранящихся в первом устройстве памяти кадров 2. Сопоставление блоков выполняется с использованием блоков, например, 16 х 16 элементов. Сигнал индикации опорного кадра предсказания движения, формируемый контроллером памяти 3, выбирает блоки предыдущих или последующих кадров, хранящихся в первом устройстве памяти кадров 2, для поблочного сопоставления с текущим блоком. Устройство предсказания движения 6 доставляет затем к компенсатору движения 7, в виде вектора движения MV, место блока в одном из предыдущих или последующих кадрах, хранящихся в первом устройстве памяти кадров, для которого отличия между блоком и текущим кадровым блоком, то есть, ошибка предсказания движения, будут минимальными.

В ответ на вектор движения MV компенсатор движения 7 заставляет блок каждого из реконструируемых кадров, хранящихся во втором устройстве памяти кадров 4, считываться как потенциальный блок сопоставления. Место в реконструируемых кадрах, из которого считываются потенциальные блоки сопоставления, определяется вектором движения MV. Сигнал индикации опорного кадра компенсации движения от контроллера памяти 3 выбирает затем один из потенциальных блоков сопоставления, считываемых из второго устройства памяти кадра 4 как блок сопоставления для текущего блока. Реконструируемые кадры, хранящиеся во втором устройстве памяти кадров 4, являются кадрами, которые были реконструированы посредством локального декодирования дискретизированных DCT - коэффициентов, формируемых кодером блока отличий 9, который будет описан ниже.

Реконструированный кадр, из которого выбирается блок сопоставления с помощью сигнала индикации опорного кадра компенсации движения, зависит от режима предсказания текущего кадра. При прямом режиме предсказания блок сопоставления выбирается из предшествующего реконструированного кадра. В двунаправленном режиме предсказания блок сопоставления выбирается из предшествующего реконструированного кадра, последующего реконструированного кадра или может быть сформирован путем выполнения линейной операции (например, расчет среднего значения) над блоками предшествующего реконструированного кадра или последующего реконструированного кадра. Окончательно, если текущий кадр кодируется в внутрикадровом режиме кодирования, то есть, кадр кодируется без предсказания, как блок сопоставления используется нулевой блок, в котором значения всех элементов установлены на ноль. Блоки сопоставления, считываемые из второго устройства памяти кадров 4, адаптивно видоизменяются таким образом, чтобы для каждого блока сигнала движущегося изображения выбирался оптимальный блок сопоставления.

Компенсатор движения 7 выбирает режим предсказания для каждого кадра посредством первого расчета суммы абсолютных значений отличий элемент за элементом между блоком текущего кадра и потенциальными блоками сопоставления, формируемыми в различных режимах предсказания. Затем компенсатор движения выбирает режим предсказания, для которого эта сумма является минимальной. Компенсатор движения подает сигнал режима предсказания MM, который указывает на выбранный режим предсказания, к кодеру с переменной длиной слова 17, который будет описан ниже. Компенсатор движения 7 заставляет также второе устройство памяти кадров 4 выдать блок сопоставления S2 для выбранного режима предсказания в схему формирования отличий 8.

Схема формирования отличий 8 получает также блок текущего кадра S1 сигнала движущего изображения, считываемый из первого устройства памяти кадров 2, и рассчитывает элемент за элементом отличие между блоком текущего кадра S1 и блоком сопоставления S2. Схема формирования отличий выдает результирующий блок отличий S2 в кодер блока отличий 9. Кодер блока отличий 9 уплотняет блок отличий S3, чтобы сформировать блок дискретизированных коэффициентов преобразования SC. Блок дискретизированных коэффициентов преобразования SC подается в локальный декодер 10, где он расширяется для получения восстановленного блока отличий S4. Локальный декодер 10 в устройстве уплотнения сигнала движущегося изображения имеет структуру, подобную устройству расширения уплотненного сигнала движущегося изображения, которая будет описана ниже, но которая отличается в некоторых деталях.

Теперь будут описаны кодер отличий 9 и локальный декодер 10.

Кодер блока отличий 9 включает схему DCT 11 и квантователь 12, как показано на фигуре 6. Схема DCT 11 применяет DCT-обработку, чтобы осуществить ортогональное преобразование блока отличий S3 их схемы формирования блока отличий 8. Схема DCT 11 подается результирующий блок DCT-коэффициентов в квантователь 12. Квантователь 12 дискретизирует блок DCT-коэфифициентов для получения блока дискретизированных DCT-коэффициентов SC.

Локальный декодер 10 состоит из инверсного квантователя 13, схемы приведения к нечетной сумме 14 и схемы IDCT 15, как показано на фигуре 6. Инверсный квантователь 13 использует таблицу квантования для инверсной дискретизации блока дискретизированных DCT-коэфифициентов SC из квантователя 12. Схема приведения к нечетной сумме выполняет операцию инвертирования четности над результирующим блоком DCT-коэффициентов, если сумма DCT-коэффициентов не является нечетным числом. Это предотвращает появление ошибки несоответствия, когда блок DCT-коэффициентов с приведенной нечетной суммой подвергается обратному ортогональному преобразованию. Схема IDCT 15 выполняет обратное дискретное косинусное преобразование (IDCT) над блоком DCT-коэффициентов с приведенной нечетной суммой, поступающим от схемы приведения к нечетной сумме 14, для получения восстановленного блока отличий.

Теперь будет описан процесс дискретизации, выполняемый квантователем 12. Каждый блок 8 х 8 DCT-коэффициентов дискретизируется. Каждый блок кадра, уплотненного в режиме внутрикадрового кодирования (I-кадр), называется в режиме внутрикадрового кодирования (I-кадр), называется интра-макроблоком. Каждый блок, уплотненный в режиме межкадрового кодирования, называется неинтра-макроблоком. Когда интра-макроблок подвергается ортогональному преобразованию, DCT-коэффициент составляющей (0,0) является DC-коэффициентом. DC-коэффициент дискретизируется путем деления с округлением DC-коэффициента на 8, если дискретизация осуществляется с 8-битовой точностью; делится на 4, если дискретизация осуществляется с 9-битовой точностью; делится на 2, если дискретизация осуществляется с 10-битовой точностью; и делится на 1, если дискретизация осуществляется с 11-битовой точностью. DC-составляющая интра-макроблока дискретизируется согласно следующим уравнениям, которые записаны в синтаксисе C языка программирования:

QDC = dc//8 (8 бит)

QDC = dc//4 (9 бит)

QDC = dc//2 (10 бит)

QDC = dc//1 (11 бит), (5)

где dc - есть DC-коэффициент, а QDC-дискретизированный DC-коэффициент.

DCT-коэффициенты, отличающиеся от DC-коэффициента, являющегося результатом ортогонального преобразования интра-макроблока ("AC-составляющие") дискретизируются путем определения коэффициентов дискретизации ac-(i,j) посредством взвешивания DCT-коэффициентов ac(i,j) с помощью матрицы взвешивания Wi согласно следующему уравнению:

ac-(i,j) = (16•ac(i,j))//Wi(i,j) (6)

Коэффициенты матрицы взвешивания Wi выглядят следующим образом:

Wi =

8 16 19 22 26 27 29 34

16 16 22 24 27 29 34 37

19 22 26 27 29 34 34 38

22 22 26 27 29 34 37 40

22 26 27 29 32 35 40 48

26 27 29 32 35 40 48 58

26 27 29 34 38 46 56 69 (7)

Затем путем использования следующего уравнения коэффициенты дискретизации ac-(i, j) дискретизируются, чтобы определить уровни дискретизации QAC(i,j) соответствующих AC-коэффициентов.

В вышеприведенном уравнении p и q являются произвольными целыми константами, например p = 3 и q = 4, а mquant-дискретизированный коэффициент.

DCT коэффициенты, являющиеся результатом ортогонального преобразования макроблока межкадрового кодирования (неинтра-макроблок), дискретизируются посредством определения коэффициентов дискретизации ac-(i,j) путем взвешивания всех DCT коэффициентов, полученных посредством преобразования "неинтра-макроблока" с помощью матрицы взвешивания Wn согласно следующему уравнению:

ac-(i,j) = (16•ac(i,j)//Wn(i,j) (9)

Коэффициенты матрицы взвешивания Wn выглядят следующим образом:

Wn =

16 17 18 19 20 21 22 23

17 18 19 20 21 22 23 24

18 19 20 21 22 23 24 25

19 20 21 22 23 24 26 27

20 21 22 23 25 26 27 28

21 22 23 24 26 27 28 30

22 23 24 26 27 28 30 31

23 24 25 27 28 30 31 33 (10)

Затем, используя следующие уравнение, дискретизируются коэффициенты дискретизации ac-(i, j), чтобы определить уровни дискретизации QAC(i,j) коэффициентов AC.

QCT(i,j)

= ac-(i,j)/(2•mquant), если (mquant=нечетное);

= ac-(i,j)+1/(2•mquant), если (mquant=четное и ac-< 0);

= ac-(i,j)-1/(2•mquant), если (mquant=четное и ac->0) (11)

Результирующие уровни дискретизации QCT(i,j) подаются к кодеру с переменной длиной слова 17 и локальному декодеру 10 в виде вышеописанного блока дискретизированных DCT коэффициентов SC.

Кодер с переменной длиной слова 17 применяет кодирование с переменной длиной слова к блоку дискретизированных DCT коэффициентов, полученных посредством дискретизации блока DCT коэффициентов. Кодер с переменной длиной слова 17 определяет отличия между дискретизированными коэффициентами преобразования в четырех блоках яркости, образующих каждый макроблок, и DC коэффициентом соответствующего интра-макроблока. Затем кодер с переменной длиной слова использует таблицу кодирования с переменной длиной слова для применения кодирования с переменной длиной слова к результирующим значениям отличий. Этот способ использует высокую корреляцию между четырьмя соседними блоками яркости, что означает, что DC коэффициенты имеют, по существу, одно и то же значение. Кодер с переменной длиной слова 17 также определяет отличия между дискретизированными коэффициентами двух блоков отличий цвета и использует таблицу кодирования с переменной длиной слова для выполнения кодирования с переменной длиной слова результирующих значений отличий. Таблица кодирования с переменной длиной слова для коэффициентов яркости и таблица для отличий по цвету отличаются друг от друга.

Кодер с переменной длиной слова 17 применяет кодирование с переменной длиной слова к блоку дискретизированных DCT коэффициентов посредством считывания блока дискретизированных DCT коэффициентов в зигзагообразном порядке сканирования, начиная с DCT-коэффициента составляющей (0,0), как показано на фигуре 7. Блок дискретизированных DCT-коэффициентов считывается в зигзагообразном порядке сканирования, потому что ненулевые DCT-коэффициенты, являющиеся результатом DCT-обработки, обычно концентрируются с окрестности составляющей (0,0). Таким образом, считывание DCT-коэффициентов в зигзагообразном порядке повышает эффективность кодирования с переменной длиной слова посредством увеличения ряда следующих друг за другом нулевых DCT-коэффициентов, считываемых между каждыми ненулевыми DCT-коэффициентами.

Кодер с переменной длиной слова 17 считывает DCT-коэффициенты в зигзагообразном порядке сканирования и определяет значение (другими словами, уровень) каждого ненулевого DCT-коэффициента и количество (другими словами, ряд) предшествующих нулевых DCT-коэффициентов. Это выполняется посредством двумерного кодирования с переменной длиной слова блока DCT-коэффициентов. После кодирования коэффициенты в блоке выражаются через значение ряда и пар уровней. Кодер с переменной длиной слова добавляют также 2-битовый код, ЕОВ, который указывает ненулевой DCT-коэффициент, который является последним ненулевым DCT-коэффициентом. Кодер с переменной длиной слова 17 доставляет адрес последнего ненулевого коэффициента в зигзагообразном порядке сканирования к преобразователю адреса (не показан). Преобразователь адреса преобразует адрес в зигзагообразном порядке сканирования в адрес, EOB- adrs в растровом порядке сканирования. Кодер с переменной длиной слова подает адрес EOB-adrs в схему приведения к нечетной сумме 14.

Схема приведения к нечетной сумме 14 хранит адрес EOB-adrs в раствором порядке сканирования в регистре 25, показанном, для примера на фиг. 8, который будет описан ниже.