Изобретение относится к автоматике, вычислительной технике, в частности к электроизмерительной технике.

Известны интеграторы напряжения на основе операционного усилителя (ОУ) с резистором на входе и конденсатором в цепи обратной связи (т.е. интегрирующего ОУ) (см. Гутников В.С. Интегральная электроника в электроизмерительных устройствах. - Л.: Энергоатомиздат, 1988. - С. 94). Недостатком таких устройств является накопление погрешности в режиме длительного интегрирования из-за наличия входного тока и напряжения смещения используемого ОУ.

Известны также интеграторы, в которых используются цепи отрицательной обратной связи по постоянному напряжению, с помощью которых устраняется эффект накопления погрешностей от интегрирования входного тока и напряжения смещения ОУ (см. Зыкин Ф.А., Казаков М.К. Интеграторы периодических сигналов / Изв. ВУЗов. Энергетика - 1988. - N 7). Недостатками таких устройств являются появление погрешностей интегрирования и увеличение инерционности из-за введения дополнительных обратных связей.

Наиболее близким устройством того же назначения к заявляемому изобретению по совокупности признаков является интегратор периодических напряжений, содержащий интегрирующий ОУ, вход которого является входом интегратора, и ключ, подключенный параллельно конденсатору интегрирующего ОУ (см. Хоровиц П. , Хилл У. Искусство схемотехники. - М.: Мир, 1983. - Т. 1. - С. 208), которое принято за прототип.

В таком устройстве погрешность от интегрирования входных токов и напряжения смещения снижается периодическим разрядом конденсатора интегрирующего ОУ с помощью замыкания ключа. Но это приводит к возникновению погрешностей интегрирования в режиме длительного интегрирования, поскольку в интервалы времени замкнутого состояния ключа происходит потеря информации об интегрируемом напряжении. Кроме этого, погрешности увеличиваются из-за влияния переходного процесса при замыкании и размыкании ключа.

Сущность изобретения состоит в стремлении получить технический результат, заключающийся в снижении погрешностей интегрирования периодических напряжений в режиме длительного интегрирования.

Указанный технический результат при осуществлении изобретения достигается тем, что в известном интеграторе периодических напряжений, содержащем первый интегрирующий операционный усилитель, вход которого является входом интегратора, и первый ключ, подключенный параллельно конденсатору первого интегрирующего операционного усилителя, особенность заключается в том, что в него введены второй интегрирующий операционный усилитель, второй, третий, четвертый ключи, сумматор напряжения, устройство управления, причем вход второго интегрирующего операционного усилителя соединен со входом первого интегрирующего операционного усилителя, второй ключ подключен параллельно конденсатору второго интегрирующего усилителя, третий ключ подключен между выходом первого интегрирующего операционного усилителя и первым входом сумматора напряжения, выход которого является выходом интегратора, четвертый ключ подключен между выходом второго интегрирующего усилителя и вторым входом сумматора напряжения, вход устройства управления соединен со входом интегратора, а первый, второй, третий и четвертый выходы устройства управления соединены со входами управления соответственно первого, второго, третьего и четвертого ключей, причем устройство управления содержит триггер Шмитта, вход которого является входом устройства управления, а выход подключен к последовательно соединенным первому и второму делителям частоты, выходы первого и второго делителей частоты подключены к входам первого логического элемента "И", выход которого является вторым выходом устройства управления, выход второго делителя частоты, являющийся третьим выходом устройства управления, через логический инвертор, выход которого является четвертым выходом устройства управления, соединен со входом второго логического элемента "И", другой вход которого подключен к выходу первого делителя частоты, а выход второго логического элемента "И" является первым выходом устройства управления.

Проведенный анализ уровня техники позволил установить, что заявителем не обнаружено аналога, характеризующегося признаками, тождественными всем признакам заявленного изобретения, а определение из перечня аналогов прототипа позволило выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном устройстве, изложенных в формуле изобретения. Следовательно, заявляемое изобретение соответствует условию "новизна".

Для проверки соответствия заявленного изобретения условию "изобретательский уровень" заявитель провел дополнительный поиск известных решений, чтобы выявить признаки, совпадающие с отличительными от прототипа признаками заявленного устройства. Результаты поиска показали, что заявленное изобретение не вытекает для специалиста явным образом из известного уровня техники, поскольку из уровня техники, определенного заявителем, не выявлено влияние предусматриваемых существенными признаками заявленного изобретения преобразований на достижение технического результата. Следовательно, заявленное изобретение соответствует условию "изобретательский уровень".

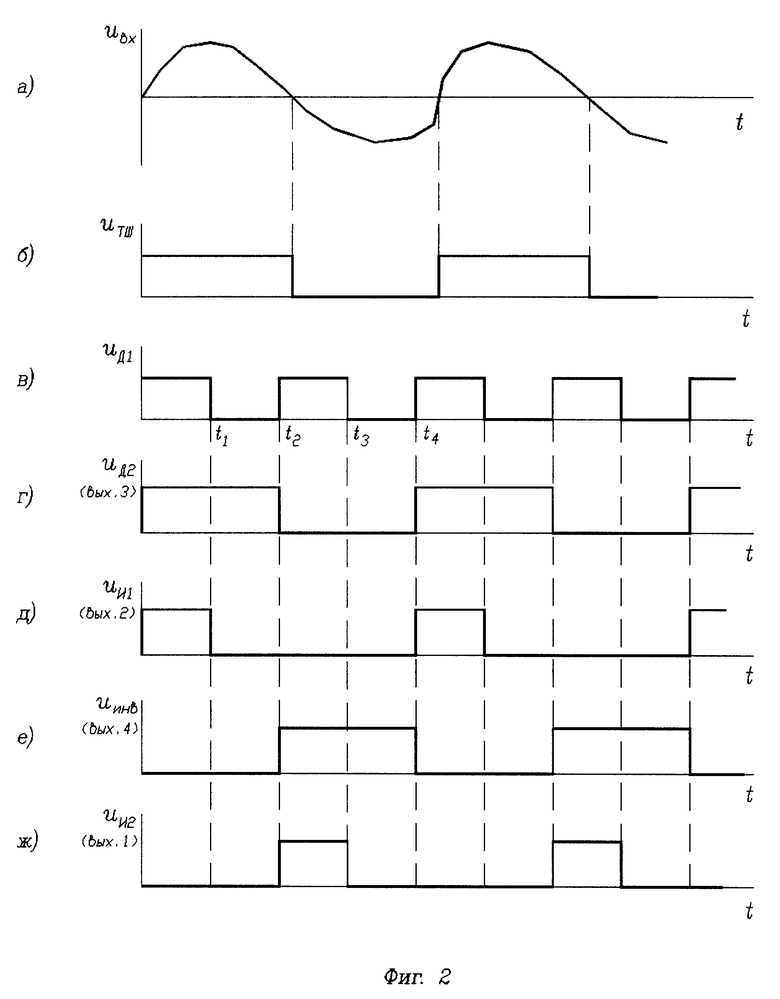

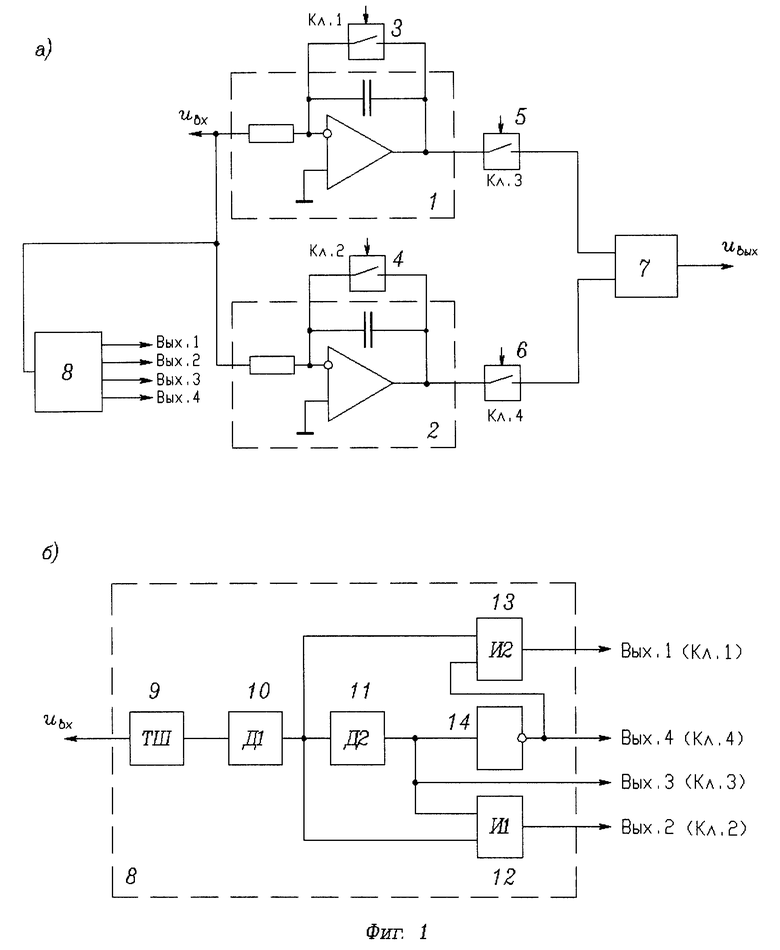

На чертежах представлено: на фиг. 1 изображена схема интегратора периодических напряжений; на фиг. 2 приведены графики напряжений, поясняющие работу устройства.

Интегратор содержит (фиг. 1,а): первый 1 и второй 2 интегрирующие ОУ, параллельно конденсаторам которых включены соответственно первый 3 и второй 4 ключи; третий 5 и четвертый 6 ключи, причем третий ключ 5 включен между выходом первого интегрирующего ОУ 1 и входом сумматора напряжений 7, а четвертый ключ 6 включен между выходом второго интегрирующего ОУ 2 и другим входом сумматора 7; устройство управления (УУ) 8. Устройство управления 8 содержит (фиг. 1, б): триггер Шмитта 9; последовательно соединенные первый 10, второй 11 делители частоты (счетчики импульсов); первый 12 и второй 13 логические элементы "И"; логический инвертор 14.

Работа устройства осуществляется следующим образом.

Входное периодическое напряжение Uвх (фиг. 2,а) подается на оба (1 и 2) интегрирующих ОУ и на УУ 8, причем предполагается, что параметры элементов обоих интегрирующих ОУ предложенного интегратора выбраны одинаковыми. Триггер Шмитта 9 преобразует это напряжение в прямоугольные импульсы (фиг. 2,б). Первый делитель частоты 10 уменьшает частоту напряжения (напряжение Uд1 на фиг. 2, в), что снижает частоту переключения интегрирующих ОУ 1 и 2 (см. ниже) с целью устранения погрешности от влияния переходных процессов.

Таким образом, масштабы по оси t графиков на фиг. 2,б и на фиг. 2,в различные: в действительности период напряжения Uд1 (фиг. 2,в) больше периода напряжения Uтш (фиг. 2,б).

Второй делитель частоты 11 является делителем частоты на два. Его выходное напряжение Uд2 показано на фиг. 2,г. Напряжение Uд1 с первого 10 и напряжение Uд2 со второго 11 делителей подаются на первый логический элемент "И" 12, выходное напряжение Uи1 которого показано на фиг. 2,д. Логический инвертор 14 инвертирует сигнал, поступающий со второго делителя частоты 11, и его выходное напряжение Uинв показано на фиг. 2,е. Напряжения с выхода первого делителя 10 и с выхода инвертора 14 подаются на вход второго логического элемента "И" 13, выходное напряжение Uи2 которого показано на фиг. 2,ж.

Выход второго логического элемента "И" 13 является первым выходом УУ 8, который соединяется со входом управления первого ключа 3. Выход первого логического элемента "И" 12 является вторым выходом УУ 8, который соединяется со входом управления второго ключа 4. Выход второго делителя частоты 11 является третьим выходом УУ 8, который соединяется со входом управления третьего ключа 5. Выход логического инвертора 14 является четвертым выходом УУ 8, который соединяется со входом управления четвертого ключа 6.

Соответствующие напряжения на указанных выходах УУ 8 управляют работой ключей 1-4: при наличии логической "1" ключ замыкается, а при наличии логического "0" - размыкается. Например, в интервале времени 0...t2 третий ключ 5 замкнут (фиг. 2,г), а четвертый ключ 6 разомкнут (фиг. 2,е), и ко входу сумматора 7 подводится напряжение с выхода интегрирующего ОУ 1, который осуществляет интегрирование входного напряжения Uвх. При этом в интервале времени 0...t1 второй ключ 4 замкнут (фиг. 2,д), чем осуществляется фиксация нулевого уровня второго интегрирующего ОУ 2, в частности снятие напряжения от интегрирования входных токов и напряжения смещения ОУ (устранение паразитного смещения нулевого уровня). В момент времени t1 второй ключ 4 размыкается (фиг. 2,д) и второй интегрирующий ОУ 2 начинает интегрировать входное напряжение, но четвертый ключ 6 до момента времени t2 разомкнут (фиг. 2,е) и напряжение с выхода этого ОУ на вход сумматора 7 не поступает. В интервале времени t1...t2 заканчивается переходный процесс во втором интегрирующем ОУ 2 и к моменту времени t2 напряжения на выходах обоих интегрирующих ОУ будут одинаковыми. В этот момент времени третий ключ 5 размыкается, а четвертый ключ 6 замыкается, чем обеспечивается подведение ко входу сумматора напряжения уже с выхода второго интегрирующего ОУ 2, но поскольку оба интегрирующие ОУ к моменту t2 выдают одинаковые напряжения, то выходное напряжение сумматора (т.е. выходное напряжение интегратора) не изменится.

Затем в интервале времени t2...t4 интегрирование входного напряжения осуществляет второй интегрирующий ОУ 2, причем в интервале времени t2...t3 производится фиксация нулевого уровня интегрирующего ОУ 1, в частности устранение погрешности от интегрирования входных токов и напряжения смещения ОУ. Далее рабочие циклы устройства повторяются.

Таким образом, производится распределение рабочих циклов между обоими интегрирующими ОУ и потери информации об интегрируемом напряжении в моменты фиксации нулевого уровня не происходит (интегрирование не прерывается), что повышает точность обработки периодических напряжений в режиме длительного интегрирования. Причем во время интегрирования структура "рабочей" части интегратора включает только минимально необходимое количество элементов (интегрирующий ОУ и разомкнутый ключ в цепи обратной связи), что позволяет выполнять операцию интегрирования с высокой точностью. Более того, современные ключи на полевых транзисторах имеют весьма высокое сопротивление в разомкнутом состоянии (109 Ом и более), поэтому отношение этого сопротивления к сопротивлению резистора на входе интегрирующего ОУ может превышать значение коэффициента усиления ОУ без обратной связи, что говорит о том, что ключ не будет оказывать влияния на работу интегратора.

Выбор значения коэффициента деления частоты первого делителя частоты 10, определяющего увеличение периода напряжения Uд1 по отношению к периоду напряжения Uтш, выбирается из следующих соображений. Во-первых, необходимо, чтобы погрешность от паразитного смещения нулевого уровня не превышала допустимую величину за время Δt работы интегрирующего ОУ (например, Δt = t4 - t1, фиг. 2,д). Во-вторых, за время Δt' между началом работы интегрирующего ОУ и подключением этого ОУ ко входу сумматора 7 (например, Δt' = t2 - t1, фиг. 2, д,е) переходный процесс в интегрирующем ОУ должен закончиться. Поэтому погрешность интегрирования от влияния переходного процесса при замыкании и размыкании ключей устраняется.

Таким образом, вышеизложенные сведения свидетельствуют о том, что средство, воплощающее заявленное изобретение при его осуществлении, способно обеспечить достижение усматриваемого заявителем технического результата. Следовательно, заявленное изобретение соответствует условию "промышленная применимость".

| название | год | авторы | номер документа |

|---|---|---|---|

| ФИЛЬТР ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ | 2001 |

|

RU2204883C1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО ТОКА | 1996 |

|

RU2127887C1 |

| ФИЛЬТР ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ | 2000 |

|

RU2182400C1 |

| ПЕРЕНОСНОЙ ЦИФРОВОЙ ИЗМЕРИТЕЛЬ БОЛЬШИХ ПОСТОЯННЫХ ТОКОВ | 1996 |

|

RU2131128C1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 2000 |

|

RU2188452C2 |

| УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2001 |

|

RU2182361C1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2004 |

|

RU2256184C1 |

| УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДЛИТЕЛЬНОСТЕЙ ДВУХ РАЗНОВРЕМЕННЫХ ИМПУЛЬСОВ | 2002 |

|

RU2231920C2 |

| ЦИФРОВОЙ ПИРОМЕТР СПЕКТРАЛЬНОГО ОТНОШЕНИЯ | 1996 |

|

RU2108554C1 |

| АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2178207C1 |

Изобретение относится к автоматике и вычислительной технике, в частности к электроизмерительной технике. Техническим результатом является повышение точности обработки периодических напряжений в режиме длительного интегрирования. Устройство содержит два интегрирующих операционных усилителя, четыре ключа, сумматор напряжения и устройство управления, причем устройство управления содержит триггер Шмитта, два делителя частоты, два элемента И и логический инвертор. 2 ил.

Интегратор периодических напряжений, содержащий первый интегрирующий операционный усилитель, вход которого является входом интегратора, и первый ключ, подключенный параллельно конденсатору первого интегрирующего операционного усилителя, отличающийся тем, что в него введены второй интегрирующий операционный усилитель, второй, третий, четвертый ключи, сумматор напряжения, устройство управления, причем, вход второго интегрирующего операционного усилителя соединен со входом первого интегрирующего операционного усилителя, второй ключ подключен параллельно конденсатору второго интегрирующего усилителя, третий ключ подключен между выходом первого интегрирующего операционного усилителя и первым входом сумматора напряжения, выход которого является выходом интегратора, четвертый ключ подключен между выходом второго интегрирующего усилителя и вторым входом сумматора напряжения, вход устройства управления соединен со входом интегратора, а первый, второй, третий и четвертый выходы устройства управления соединены со входами управления соответственно первого, второго, третьего и четвертого ключей, причем устройство управления содержит триггер Шмитта, вход которого является входом устройства управления, а выход подключен к последовательно соединенным первому и второму делителям частоты, выходы первого и второго делителей частоты подключены к входам первого логического элемента И, выход которого является вторым выходом устройства управления, выход второго делителя частоты, являющийся третьим выходом устройства управления, через логический инвертор, выход которого является четвертым выходом устройства управления, соединен со входом второго логического элемента И, другой вход которого подключен к выходу первого делителя частоты, а выход второго логического элемента И является первым выходом устройства управления.

| ХОРОВИЦ П | |||

| И др | |||

| Искусство схемотехники | |||

| - М.: Мир, т.1, с.207, 208 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для защиты забойного пространства от падающих кусков | 1988 |

|

SU1603020A1 |

| Интегратор с запоминанием | 1978 |

|

SU698009A1 |

| ИНТЕГРАТОР С БОЛЬШИМ ВРЕМЕНЕМ ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2034331C1 |

| ГУТНИКОВ В.С | |||

| Интегральная электроника в электроизмерительных устройствах | |||

| - Л.: Энергоатомиздат, 1988, с.94. | |||

Авторы

Даты

2000-05-20—Публикация

1999-04-13—Подача