Изобретение относится к радиотехнике и связи и может быть использовано в системах передачи дискретной информации, в частности в телефонии для приема сигналов многочастотного кода "2 из 6".

Известен цифровой приемник многочастотной сигнализации, содержащий N цепей, каждая из которых состоит из двух блоков возведения в квадрат, трех сумматоров, порогового элемента и двухканального коррелятора.

В основу данного изобретения положено использование оптимальной (в смысле максимального правдоподобия) процедуры приема гармонического сигнала известной частоты. К сожалению, оптимальность данного приемника проявляется только в смысле выделения (обнаружения) гармонического сигнала из адитивной смеси с белым шумом. На практике же основной проблемой приема сигнала с кодом "2 из 6" является не выделение его на фоне значительного канального шума, а устранение последствий перекоса сигнальных частот, отклонения частотных и временных параметров формируемых сигналов от регламентируемых значений, наличия паразитных речевых сигналов и сигналов служебной сигнализации. Однако данное устройство не может обеспечить удовлетворительное выделение двухчастотных посылок в таких условиях.

В качестве прототипа данному устройству выбран цифровой приемник многочастотного кода, содержащий блок синхронизации, М согласованных фильтров, постоянно запоминающий блок, М логических элементов ИЛИ-НЕ, М пороговых блоков, блок фиксации количества срабатываний, формирователь импульсов и триггер.

Недостатком этого устройства также является невысокая достоверность приема многочастотного сигнала, особенно в случае наличия перекоса в уровнях сигнальных частот, а также при появлении даже слабого паразитного речевого сигнала. В указанных случаях возможно ложное срабатывание цифрового приемника. Кроме того, данный приемник чувствителен к искажениям временных параметров информационного сигнала, которые обусловлены невысоким качеством станционных формирователей двухчастотных посылок и выражаются в уменьшении длительности двухчастотных посылок.

Целью изобретения является повышение достоверности приема двухчастотных сигналов.

Для достижения поставленной цели в устройство для декодирования двухчастотных сигналов, содержащее блок согласованных фильтров, первый, второй, третий и четвертый пороговые элементы, согласно изобретению, дополнительно введены фильтр низких частот, аналого-цифровой преобразователь, режекторный фильтр, линейный детектор, интегрирующее звено, блок линейных детекторов, блок интегрирующих звеньев, блок управляемых ключей, управляющий таймер, арифметический блок, первый и второй сумматоры, первый, второй и третий блоки вычисления отношения, логический элемент И и блок отображения, причем выход блока согласования с каналом связи через последовательно включенный фильтр низких частот соединен со входом аналого-цифрового преобразователя, выход которого через последовательно включенный режекторный фильтр связан с входом линейного детектора и входами блока согласованных фильтров, при этом выход линейного детектора через последовательно включенные интегрирующее звено и первый пороговый элемент соединен с первым входом логического элемента И, а выходы блока согласованных фильтров подключены к соответствующим входам блока линейных детекторов, в свою очередь выходы блока линейных детекторов связаны с соответствующими входами блока интегрирующих звеньев, выходы которых соединены с соответствующими входами блока управляемых ключей, причем управляющий вход блока управляемых ключей связан с управляющим таймером, а выходы всех управляемых ключей соединены с входами арифметического блока, первый выход которого подключен к первому входу первого сумматора и первому входу второго блока вычисления отношения, второй выход - к второму входу первого сумматора, второму входу второго блока вычисления отношения и первому входу третьего блока вычисления отношения, третий выход арифметического блока подключен к второму входу третьего блока вычисления отношения и первому входу второго сумматора, а четвертый, пятый и шестой выходы арифметического блока соединены соответственно со вторым, третьим и четвертым входами второго сумматора, при этом выход первого сумматора связан с первым входом первого блока вычисления отношения, выход второго сумматора со вторым входом первого блока вычисления отношения, а выход последнего через второй пороговый элемент соединен со вторым входом логического элемента И, тогда как выход второго блока вычисления отношения через третий пороговый элемент связан с третьим входом логического элемента И, выход же третьего блока вычисления отношения через четвертый пороговый элемент подключен к четвертому входу логического элемента И, выход которого соединен с управляющим входом арифметического устройства, в то время как информационный выход арифметического устройства связан с блоком отображения.

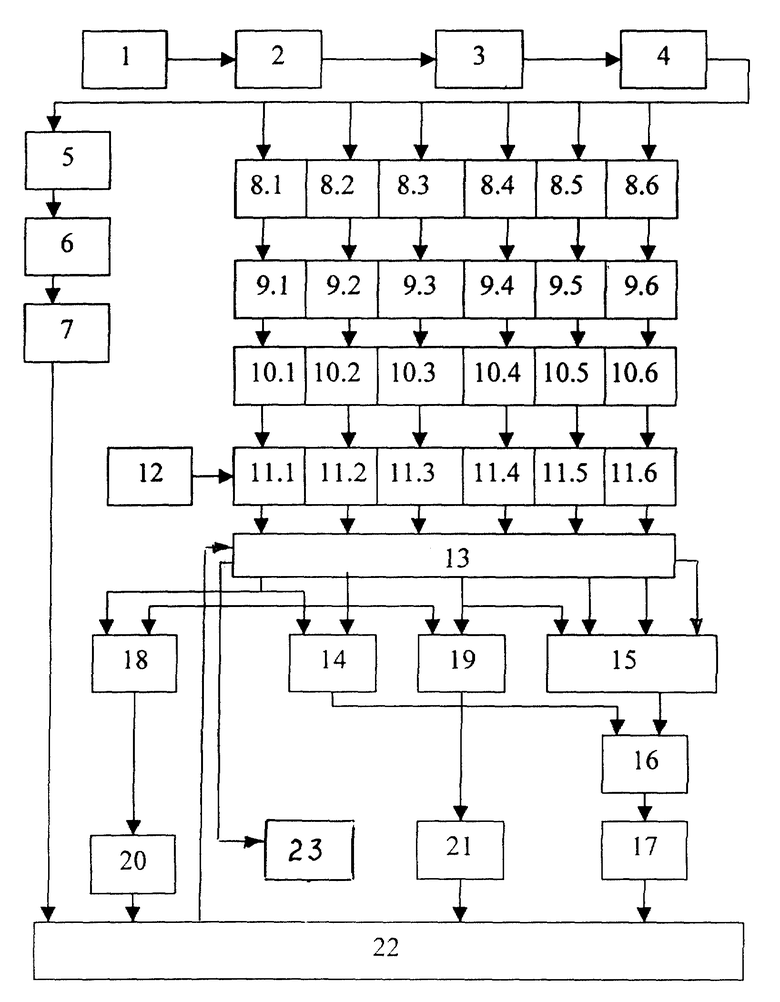

Устройство для приема многочастотных сигналов (см. чертеж) содержит блок 1 согласования с каналом связи, фильтр низких частот 2, аналого-цифровой преобразователь 3, режекторный фильтр 4, линейный детектор 5, интегрирующее звено 6, первый пороговый элемент 7, блок согласованных фильтров 8.1-8.6, блок линейных детекторов 9.1-9.6, блок интегрирующих звеньев 10.1-10.6, блок управляемых ключей 11.- 11.6, управляющий таймер 12, арифметический блок 13, первый сумматор 14, второй сумматор 15, первый блок вычисления отношения 16, второй пороговый элемент 17, второй блок вычисления отношения 18, третий блок вычисления отношения 19, третий пороговый элемент 20, четвертый пороговый элемент 21, логический элемент И 22, блок отображения 23.

Сущность изобретения состоит в использовании нескольких оцениваемых информационных статистик, с помощью которых осуществляется обнаружение и прием многочастотного сигнала в условиях возможной его маскировки паразитным сигналом и искажения ряда параметров.

Данное устройство обеспечивает устойчивое выделение полезного сигнала из смеси канальных шумов и паразитных речевых сигналов с помощью частотной селекции входного сигнала, выделения двух частотных составляющих с максимальным уровнем, вычисления отношения уровня двух этих составляющих к суммарному уровню других составляющих, оценивания мощности сигнала в информационной полосе частот, оценивания отношения первого и второго, а также второго и третьего максимумов частотных составляющих.

Устройство декодирования двухчастотных сигналов работает следующим образом.

Анализируемый сигнал с выхода канала связи, пройдя через блок 1 согласования с каналом связи и через низкочастотный фильтр 2, поступает в аналого-цифровой преобразователь 3, на выходе которого принимает форму последовательности цифровых отсчетов. Данная цифровая последовательность подвергается фильтрации в режекторном фильтре 4 для устранения проникания в приемник сигнала запроса и подается затем на вход линейного детектора 5.

При этом в блоках 5 - 7 формируется оценка мощности приходящего сигнала в информационной полосе частот, для чего в линейном детекторе 5 вычисляется абсолютное значение исходного сигнала, а затем в интегрирующем звене 6 оценивается его средневыпрямленное значение.

Оценка мощности входного сигнала, ограниченного информационной полосой частот, используется в заявляемом устройстве в качестве первой информационной статистики при принятии решения о наличии в данный момент в канале связи полезного сигнала. Для этого получаемая на выходе интегрирующего звена оценка мощности сравнивается с пороговой величиной в пороговом элементе 7. В случае присутствия в канале связи сигнала достаточного уровня на выходе порогового элемента устанавливается значение, соответствующее логической единице.

Одновременно последовательность цифровых отсчетов входного сигнала с выхода режекторного фильтра 4 подается на вход блока согласованных фильтров 8.1-8.6. Последний блок представляет собой совокупность из шести резонансных фильтров, настроенных на номинальные частоты полезного информационного сигнала. Здесь осуществляется расфильтровка частотных составляющих входного сигнала. При этом выход каждого из резонансных фильтров через соответствующие линейные детекторы 9.1-9.6 соединен с соответствующим интегрирующим звеном из блока интегрирующих звеньев 10.1-10.6. Таким образом, посредством блоков 8.1-8.6, 9.1-9.6 и 10.1-10.6 обеспечивается оценивание частотных составляющих спектра входного сигнала в информационной полосе частот.

Принятие решения о наличии информационного сигнала в канале связи и процедура его декодирования осуществляется через равные промежутки времени по команде из управляющего таймера 12, открывающего на считывание управляемые ключи 11.1-11.6. Значения, накопленные в блоке интегрирующих звеньев 10.1-10.6, считываются в арифметический блок 13. В нем определяются первый, второй и третий максимумы спектральных составляющих и фиксируются номера секций блока интегрирующих звеньев 10.1-10.6, в которых были достигнуты абсолютные максимумы огибающих.

Таким образом, можно говорить, что арифметический блок 13 по своей сути осуществляет перестановку в порядке убывания шести оценок мощности, получаемых в интегрирующих звеньях 10.1-10.6 и подаваемых на соответствующие входы арифметического блока 13, и распределяет их по соответствующим выходам. Так, например, наибольшее значение будет подано на первый выход арифметического блока 13, второе по величине значение - на второй выход и т.д. В принципе, для правильной работы заявляемого устройства имеет значение распределение в порядке убывания только первых трех величин, а последние три значения могут распределяться по четвертому, пятому и шестому выходам произвольным образом.

Далее в блоках 14-17 оценивается отношение мощности двух наиболее мощных спектральных составляющих к сумме остальных четырех частотных составляющих. Для этого значения с первого и второго выходов арифметического блока 13 считываются в первый сумматор 14. Значение с выхода первого сумматора 14 подается на первый вход первого блока вычисления отношения 16, на второй вход которого поступает оценка суммы остальных спектральных составляющих из второго сумматора 15. Если полученная величина больше некоторого порогового значения, задаваемого во втором пороговом элементе 17, то по данному информационному признаку считается, что входной сигнал является полезным и на выходе второго порогового элемента 17 устанавливается значение, соответствующее логической единице.

Введение в состав заявляемого устройства блоков, которые обеспечивают оценку отношения мощностей двух наиболее мощных спектральных составляющих и суммы остальных спектральных составляющих, позволяет приемнику работать как с сигналами номинального уровня, так и со слабыми сигналами. При этом перекос в уровнях двух сигнальных частот в достаточно больших пределах (до 12 дБ) не мешает правильности приема двухчастотной комбинации.

Для предотвращения ложных срабатываний приемника на паразитном речевом сигнале в устройство введены блоки 18-22, с помощью которых оцениваются отношения первого и второго (второй блок 18 вычисления отношения), а также второго и третьего (третий блок 19 вычисления отношения) спектральных максимумов. Соответствующим выбором порогов в третьем и четвертом пороговых элементах 20, 21 обеспечивается различение полезного сигнала (беспаузной последовательности двухчастотных посылок) от паразитных сигналов. Здесь используется априорная информация о полезном сигнале, состоящая в том, что возможное различие в уровнях двух первых спектральных максимумов не может превышать некоторую фиксированную величину. Требованиями к функционированию приемника накладываются также ограничения на минимальное различие уровней второго и третьего максимумов. Иначе сигнал считается помехой. В случае, когда указанные выше условия выполняются, на выходе соответствующих пороговых элементов выставляются логические единицы.

Окончательное решение о наличии или отсутствии многочастотного сигнала в канале связи принимается в логическом элементе И 22, если все четыре информационных признака оказываются положительными. Тогда на арифметический блок 13 поступает управляющее воздействие, после чего из информационного выхода последнего на блок отображения 23 передаются данные о принятой двухчастотной комбинации. Затем в блоке отображения осуществляется преобразование этой двухчастотной комбинации в соответствующую цифру.

Реализацию данного устройства наиболее целесообразно осуществлять с помощью современной системы электронных компонентов, предпочтительно с использованием сигнальных микропроцессоров либо заказных микросхем. Кроме того возможна программная реализация данного объекта с использованием персонального компьютера или иных вычислительных средств.

Источники информации

1. Авторское свидетельство СССР N 1467795, кл. H 04 Q 1/45, 1986 г.

2. Авторское свидетельство СССР N 1741292. кл. H 04 Q 1/44, 1989 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2000 |

|

RU2169436C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1997 |

|

RU2128400C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1997 |

|

RU2128401C1 |

| УСТРОЙСТВО ДЛЯ ПРИЁМА МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2001 |

|

RU2210193C2 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ТОНАЛЬНЫХ СИГНАЛОВ В КАНАЛАХ СВЯЗИ | 2001 |

|

RU2214051C2 |

| УСТРОЙСТВО ДЛЯ ИДЕНТИФИКАЦИИ ФАКСИМИЛЬНЫХ СИГНАЛОВ | 2000 |

|

RU2192667C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ ТОНАЛЬНОГО НАБОРА | 2000 |

|

RU2178950C2 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ АКУСТИЧЕСКИХ СИГНАЛОВ В КАНАЛАХ СВЯЗИ | 1996 |

|

RU2118067C1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ АКУСТИЧЕСКИХ СИГНАЛОВ В КАНАЛАХ СВЯЗИ | 2000 |

|

RU2171549C1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ СИГНАЛОВ ОБМЕНА СРЕДСТВ ДОКУМЕНТАЛЬНОЙ СВЯЗИ | 2001 |

|

RU2210188C2 |

Изобретение относится к радиотехнике и связи и может быть использовано в системах передачи дискретной информации, в частности в телефонии для приема сигналов многочастотного кода "2 из 6". Достигаемый технический результат - повышение достоверности приема двухчастотных сигналов. Устройство для декодирования двухчастотных сигналов содержит блок согласования с каналом связи, фильтр низких частот, аналого-цифровой преобразователь, режекторный фильтр, линейный детектор, интегрирующее звено, блок согласованных фильтров, четыре пороговых элемента, блок линейных детекторов, блок интегрирующих звеньев, блок управляемых ключей, управляющий таймер, арифметический блок, два сумматора, три блока вычисления отношения, логический элемент И и блок отображения. 1 ил.

Устройство для декодирования двухчастотных сигналов, содержащее блок согласованных фильтров, первый, второй, третий и четвертый пороговые элементы, отличающееся тем, что в устройство дополнительно введены фильтр низких частот, аналого-цифровой преобразователь, режекторный фильтр, линейный детектор, интегрирующее звено, блок линейных детекторов, блок интегрирующих звеньев, блок управляемых ключей, управляющий таймер, арифметический блок, первый и второй сумматоры, первый, второй и третий блоки вычисления отношения, логический элемент И и блок отображения, причем выход блока согласования с каналом связи через последовательно включенный фильтр нижних частот соединен с входом аналого-цифрового преобразователя, выход которого через последовательно включенный режекторный фильтр связан с входом линейного детектора и входами блока согласованных фильтров, при этом выход линейного детектора через последовательно включенные интегрирующее звено и первый пороговый элемент соединен с первым входом логического элемента И, а выходы блока согласованных фильтров подключены к соответствующим входам блока линейных детекторов, в свою очередь, выходы блока линейных детекторов связаны с соответствующими входами блока интегрирующих звеньев, выходы которых соединены с соответствующими входами блока управляемых ключей, причем управляющий вход блока управляемых ключей связан с управляющим таймером, а выходы всех управляемых ключей соединены с входами арифметического блока, первый выход которого подключен к первому входу первого сумматора и первому входу второго блока вычисления отношения, второй выход - к второму входу первого сумматора, второму входу второго блока вычисления отношения и первому входу третьего блока вычисления отношения, третий выход арифметического блока подключен к второму входу третьего блока вычисления отношения и первому входу второго сумматора, а четвертый, пятый и шестой выходы арифметического блока соединены соответственно со вторым, третьим и четвертым входами второго сумматора, при этом выход первого сумматора связан с первым входом первого блока вычисления отношения, выход второго сумматора - со вторым входом первого блока вычисления отношения, а выход последнего через второй пороговый элемент соединен со вторым входом логического элемента И, тогда как выход второго блока вычисления отношения через третий пороговый элемент связан с третьим входом логического элемента И, выход же третьего блока вычисления отношения через четвертый пороговый элемент подключен к четвертому входу логического элемента И, выход которого соединен с управляющим входом арифметического блока, в то время как информационный выход арифметического блока связан с блоком отображения.

| УСТРОЙСТВО ДЛЯ ПРИЕМА МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1997 |

|

RU2128400C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1997 |

|

RU2128401C1 |

| Цифровой приемник многочастотной сигнализации | 1986 |

|

SU1467795A2 |

| US 5428680 A, 27.06.1995 | |||

| US 4395595 A, 26.06.1983 | |||

| US 5818929, 06.10.1998. | |||

Авторы

Даты

2001-10-10—Публикация

2000-01-20—Подача