Изобретение относится к области оптоэлектроники, в частности к вычислительным устройствам, реализуемым на основе оптоэлектронной схемотехники и предназначенным для использования в схемах оптоэлектронной обработки информации. Предлагаемый оптоэлектронный процессор позволяет реализовать сложные логические операции многозначной и нечеткой логики на основе хорошо известной элементной базы, обычно используемой для выполнения процедур умножения вектора, записанного в двоичном коде, на матрицу, также записанную в виде двоичного кода.

Для реализации быстродействующих оптоэлектронных схем параллельной нечеткой и многозначной обработки информации [1, 2] прежде всего необходимы устройства, реализующие логические операции MAXIMUM, MINIMUM. Операции MAXIMUM, MINIMUM выделяют наибольший и, соответственно, наименьший из сигналов, поданных на входы логического вентиля, а затем выводят его в качестве выходного сигнала. Ранее были предложены оптоэлектронные логические устройства [1, 3], которые выполняют такие операции MAXIMUM, MINIMUM. Описанная в [1] схема позволяет, например, построить логические вентили с большим числом входов, что дает возможность существенно повысить степень параллелизма схем обработки. В [3] предложена схема логических вентилей, основанных на миниатюрных интегрально-оптических волноводных схемах. Вместе с тем, в [1, 3] речь идет о достаточно сложных устройствах, включающих в себя дорогостоящие компоненты, в то время как для широкого практического применения, например в контроллерах и в схемах обработки сигналов, поступающих с датчиков, требуются более простые и дешевые схемы, удобные для тиражирования однотипных узлов.

Заявляемый оптоэлектронный процессор также может быть непосредственно использован в качестве логических вентилей MAXIMUM и MINIMUM, то есть основных функциональных узлов логических вычислительных схем, использующих принципы многозначной и нечеткой логики.

Аналогом заявляемого устройства является логическое устройство [3], реализующее операции MAXIMUM и MINIMUM как в схемах, основанных на многозначной, так и на нечеткой логике. В указанном устройстве, предназначенном для работы с оптическими входными и выходными сигналами, имеется световодная коммутационная схема, выполняемая с помощью Х- и Y-образных ответвителей. Величины входных оптических сигналов в световодной коммутационной схеме измеряются фотоприемниками и сравниваются с помощью микроэлектронного компаратора, переключающего одновременно два Х-образных ответвителя, что позволяет вывести на выход устройства, соответственно, максимальный или минимальный из двух входных оптических сигналов. При этом выбор выполняемой логической операции MAXIMUM или MINIMUM определяется лишь выбором соответствующей пары входов из имеющихся четырех входов. Однако такое устройство одновременно сравнивает лишь два входных сигнала, что сильно ограничивает степень параллелизма обработки, выполняемой с помощью таких логических устройств. Кроме того, в указанном устройстве используются сложные в изготовлении и дорогостоящие световодные ответвители. Другим аналогом заявляемого устройства является оптоэлектронный логический вентиль MAXIMUM, MINIMUM [1], использующий принцип кодирования дискретных логических уровней различными частотами оптического сигнала. Такая схема позволяет реализовать схемы обработки в рамках математического аппарата многозначной логики, или с помощью той же многозначной логики приближенно выполнить вычисления, необходимые для устройств нечеткой обработки информации. В этих целях необходимо предварительно закодировать величины входных электрических или оптических сигналов одной из р возможных частот оптического излучения, после чего оптическая схема разворачивает произвольное число входных сигналов в оптический спектр, состоящий не более чем из р различных частот. Далее электронный узел выделяет в полученном оптическом спектре либо наибольшую, либо наименьшую длины волн, подавая на выход соответствующий сигнал. При этом выбор выполняемой логической операции MAXIMUM, MINIMUM определяется выбором одного из двух возможных способов коммутации блока фотоприемников. Такая схема принципиально позволяет реализовать многовходовые устройства, выполняющие логические операции MAXIMUM, MINIMUM, однако она является сравнительно громоздкой и дорогостоящей, что ограничивает ее применимость для многих практических приложений.

Прототипом заявляемого устройства является оптоэлектронный процессор [4, 5] , вычисляющий вектор-матричное произведение и решающий целый ряд других задач. Оптоэлектронный процессор используется как основной функциональный блок в цифровой оптической обработке информации и предполагает двоичную (бинарную) кодировку входных и выходных сигналов. В общем случае данное устройство состоит из линейки светоизлучающих элементов, первой оптической системы, пространственного модулятора света, второй оптической системы, линейки фотоприемных элементов. Линейка светоизлучающих элементов задает значения компонент входного вектора Xi, первая оптическая система проецирует каждый из элементов линейки светоизлучающих элементов на зону пространственного модулятора света, описываемую одной строкой матрицы весовых коэффициентов Wij. Пространственный модулятор света, который может быть управляемым или неуправляемым, представляет собой матрицу пикселов, имеющих определенные значения коэффициента пропускания света, задающего весовые коэффициенты Wij. Каждая строка (или столбец) матрицы пикселов задает двоичный вектор для сигналов, вводимых извне или вычисленных на более ранних этапах оптических вычислений. В целом матрица пикселов может быть описана как набор из нескольких таких векторов, содержащих промежуточные значения. При прохождении пространственного модулятора света компоненты входного вектора Xi арифметически умножаются на значения весовых коэффициентов Wij: Xi • Wij. Вторая оптическая система собирает свет на скрещенную с линейкой светоизлучателей линейку фотоприемных элементов, суммируя компоненты света на выходе столбцов матрицы пикселов пространственного модулятора света. В результате, выходной вектор описывается выражением вида  . Первая и вторая оптические системы обычно выполняются с помощью элементов анаморфотной оптики. Указанный оптоэлектронный процессор традиционно рассматривается как один из базовых узлов для реализации схем оптоэлектронной обработки, основанных на традиционной булевой (двоичной) логике. Однако он не позволяет выполнить специальные логические операторы, необходимые для построения схем обработки, основанных на более сложных математических аппаратах многозначной и нечеткой логики. Способ применения, определяемый схемой прототипа, предполагает, что матрично-векторный умножитель (также называемый в литературе матрично-векторный перемножитель) применяется на тех этапах двоичных вычислений, где имеется один внешний входный сигнал, представленный в виде двоичного вектора, и набор постоянных или изменяющихся во времени промежуточных сигналов, представленных в виде двоичных векторов и вводимых в матрично-векторный умножитель в виде столбцов или строк матричного транспаранта.

. Первая и вторая оптические системы обычно выполняются с помощью элементов анаморфотной оптики. Указанный оптоэлектронный процессор традиционно рассматривается как один из базовых узлов для реализации схем оптоэлектронной обработки, основанных на традиционной булевой (двоичной) логике. Однако он не позволяет выполнить специальные логические операторы, необходимые для построения схем обработки, основанных на более сложных математических аппаратах многозначной и нечеткой логики. Способ применения, определяемый схемой прототипа, предполагает, что матрично-векторный умножитель (также называемый в литературе матрично-векторный перемножитель) применяется на тех этапах двоичных вычислений, где имеется один внешний входный сигнал, представленный в виде двоичного вектора, и набор постоянных или изменяющихся во времени промежуточных сигналов, представленных в виде двоичных векторов и вводимых в матрично-векторный умножитель в виде столбцов или строк матричного транспаранта.

Задачей предлагаемого изобретения является создание оптоэлектронного процессора, позволяющего выполнять вычисления, основанные на логических операциях MAXIMUM и MINIMUM, наиболее часто используемых в многозначной и нечеткой логиках. Заявляемое устройство принципиально отличается от прототипа тем, что реализует логические операции Y=MINIMUM(X1,X2,...,Xn) и Y=MAXIMUM(X1,X2,...,Xn) вместо алгебраической функции вида  , вычисляемой оптоэлектронным процессором, выполняющим вектор-матричное произведение.

, вычисляемой оптоэлектронным процессором, выполняющим вектор-матричное произведение.

Важной особенностью заявляемого устройства является принципиальная возможность выполнять логические операции MAXIMUM, MINIMUM параллельно для большого числа входных переменных, поскольку в нем использован простой принцип наращивания числа входов. Оптоэлектронный способ реализации логических операций позволяет преодолеть известные проблемы по увеличению числа входов в традиционных микроэлектронных логических вентилях, ограничивающие возможности реализации параллельных вычислительных схем. Поэтому предлагаемое устройство предназначено прежде всего для использования в архитектурах параллельной обработки информации и схемах многопараметрической обработки.

Поскольку заявляемое устройство основано на принципах многозначной логики, а не двоичной, как прототип, то благодаря этому можно легко реализовать методики приближенной обработки информации, основанные на весьма популярном в настоящее время математическом аппарате нечеткой логики, которая по сути является расширением многозначной логики.

Реализация заявляемого устройства является простой и дешевой, поскольку в нем применяются уже известные оптоэлектронные компоненты, используемые в оптоэлектронном процессоре, выполняющем процедуры вектор-матричного умножения.

В наиболее наглядном и кратком виде идея заявляемого устройства заключается в том, что все используемые сигналы, включая внешний информационный сигнал и промежуточные сигналы, "объединены" в единый набор сигналов, непосредственно задаваемый с помощью матрицы светоизлучающих элементов, а кодирование всех аналоговых или многозначных сигналов осуществляется с помощью специального многозначного кода, записывающего сигнал с помощью последовательности 0 и 1. В этом случае от схемы матрично-векторного умножителя "достаточно" использовать лишь ее "вторую половину", в которой фотоприемники собирают свет по столбцам матрицы светоизлучающих элементов. При этом заявляемое устройство позволяет выполнять качественно новые виды вычислений и в рамках многозначной, и нечеткой логики. Кроме того, в заявляемом устройстве оказывается возможным исключить и первую и вторую оптические системы, что дополнительно упрощает устройство.

Поставленная цель достигается за счет того, что в заявляемом оптоэлектронном процессоре содержится набор линеек светоизлучающих элементов, количество которых равно числу используемых входных сигналов. Линейки светоизлучающих элементов объединены в матрицу светоизлучающих элементов, где каждому входному сигналу, задаваемому отдельной линейкой светоизлучающих элементов, соответствует отдельная строка матрицы. В заявляемом устройстве каждая из линеек светоизлучающих элементов может составлена из светодиодов или полупроводниковых лазеров. Как и прототип, заявляемое устройство содержит линейку фотоприемников с достаточно большим размером фоточувствительной площадки каждого фотоприемника. Светоизлучающие элементы в линейках светоизлучающих элементов (по строкам матрицы светоизлучающих элементов) и фотоприемные элементы в линейке фотоприемников расположены вдоль одной оси координат, обеспечивая необходимую схему организации оптической связи между светоизлучающими элементами и фотоприемными элементами.

По сравнению с прототипом в предлагаемом устройстве, благодаря использованию специального многозначного кодирования входных сигналов и упорядоченному расположению светоизлучающих элементов, задающих одинаковые логические уровни сигналов (в интервале от 0 до р-1), удается совместить функции линейки светоизлучающих элементов и матричного транспаранта, кодирующего матрицу весовых коэффициентов, заменив их набором линеек светоизлучающих элементов. Для предлагаемой схемы при необходимости из числа входных сигналов можно произвольно выделить некоторое число внешних информационных сигналов, например, поступающих с датчиков или являющихся промежуточными результатами, вводимыми из других частей вычислительной схемы, подобно тому, как в прототипе задаются строки или столбцы матрицы транспаранта.

В линейках светоизлучающих элементов (строках матрицы светоизлучающих элементов) количество элементов р выбирается равным числу логических уровней, которое необходимо использовать в рамках многозначного логического аппарата, адекватно описывающего конкретную проблему.

Последовательно за матрицей светоизлучающих элементов расположена линейка фотоприемных элементов, включающая в себя р параллельно расположенных фотоприемников. Каждый из р фотоприемников оптически связан лишь с теми светоизлучающими элементами в матрице светоизлучающих элементов, которые имеют тот же номер столбца (от 1 до р), что и фотоприемник, при одном и том же направлении отсчета. Для реализации операции MAXIMUM одновременно выходы всех фотоприемников электрически связаны со входами стандартных буферных неинвертирующих микросхем, выходы которых являются выходами оптического процессора, кодирующими выходной сигнал Y. Для реализации операции MINIMUM выход каждого фотоприемника электрически связан с входом стандартной микроэлектронной инвертирующей микросхемы НЕ, а выходами оптического процессора, кодирующими выходной сигнал Y, являются выходы микросхем НЕ.

Первое существенное отличие предлагаемой схемы устройства от схемы оптоэлектронного процессора, выполняющего вектор-матричное произведение, связано с заменой линейки светоизлучающих элементов и матрицы пространственного модулятора света (то есть матрицы пропускающих и не пропускающих свет элементов) на матрицу светоизлучающих элементов, используемую для ввода всех используемых сигналов. При этом k-й столбец матрицы светоизлучающих элементов задает k-й логический уровень, объединяя в себе все светоизлучающие элементы с одинаковыми логическими уровнями, расположенными в различных строках матрицы светоизлучающих элементов, то есть линейках светоизлучающих элементов, относящихся к различным входным переменным.

Вторым отличием предлагаемой схемы от прототипа является то, что каждый из фотоприемников с номером от 1 до р регистрирует не суммарную интенсивность света на выходе столбцов (или строк) матрицы, как в прототипе, а в пороговом режиме обнаруживает наличие света хотя бы от одного из светоизлучающих элементов, расположенных в столбце матрицы светоизлучающих элементов с таким же номером (от 1 до р), как у самого фотоприемника.

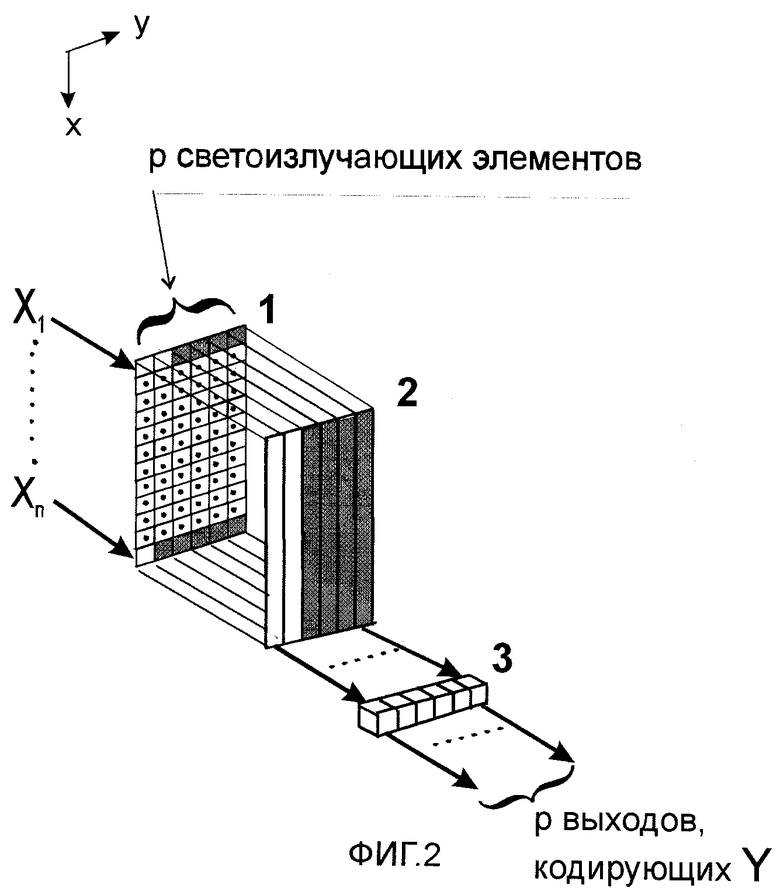

Третьим существенным отличием предлагаемой схемы как от прототипа [4], так и от аналогов [1, 3], является использование особого принципа кодирования входного сигнала, где одно из р возможных значений величины входного сигнала осуществляется в виде набора из р последовательно расположенных светящихся элементов светоизлучающих линеек, а при этом все остальные элементы не испускают свет. Принцип многозначного кодирования показан на фиг.1 в сравнении с двоичным кодированием сигналов. Темные квадратики изображают неизлучающие свет элементы, а светлые соответствуют испускающим свет элементам. При выполнении операции MAXIMUM входные сигналы вводятся в виде неинвертированного кода. Нулевой величине входного сигнала и, соответственно, "нулевому" логическому уровню в рамках математического аппарата р-значной логики или р-значного приближения нечеткой логики соответствует один светящийся элемент, "первому" логическому уровню соответствуют два рядом расположенных светящихся элемента, "второму" логическому уровню соответствуют три рядом расположенных испускающих свет элемента, аналогично "р-1"-му логическому уровню соответствуют р рядом расположенных светящихся элементов. При выполнении операции MINIMUM на вход оптического процессора требуется подавать сигналы в виде инвертированного кода. Чтобы согласно фиг.1 представить сигнал в инвертированном коде, конкретное логическое значение сигнала k следует задать в неинвертированном виде, а затем все испускающие свет элементы в линейке светоизлучающих элементов следует заменить на несветящиеся, и, соответственно, наоборот.

Заявляемое устройство может быть использовано не только для реализации оптоэлектронных схем, основанных на принципах многозначной логики, но и достаточно удобно для приближенной обработки сигналов на принципах нечеткой логики, поскольку на основе предлагаемой схемы можно использовать большое число градаций входного сигнала по величине, а также большое число входных переменных.

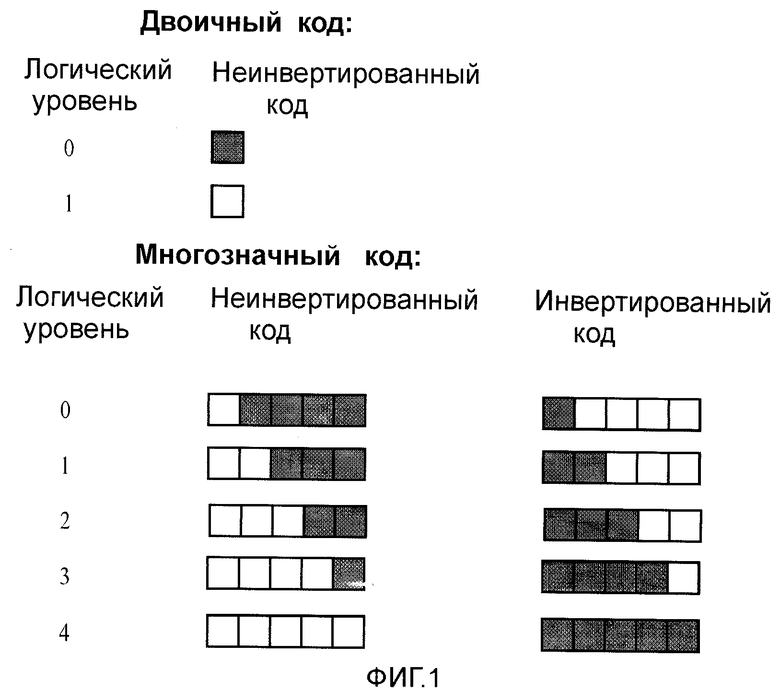

Схема заявляемого устройства показана на фиг.2. Используется n входных сигналов Xi, соответственно i= 1,...,n. Для ввода каждой из входных переменных Xi, имеющих р градаций по величине, используется отдельная линейка светоизлучающих элементов. Все n одинаковых линеек светоизлучающих элементов расположены параллельно друг другу, формируя отдельные строки матрицы светоизлучающих элементов 1. Номер строки n при этом определяется номером входного сигнала. Каждая из строк матрицы 1, то есть линеек светоизлучающих элементов содержит р управляемых внешними устройствами светоизлучающих элементов. Размерность матрицы светоизлучающих элементов 1 составляет n х р.

Последовательно за матрицей светоизлучающих элементов 1 расположена линейка фотоприемных элементов 2, которая содержит р одинаковых фотоприемников, расположенных параллельно строкам матрицы 1, и, соответственно, каждой из входящих в нее линеек светоизлучающих элементов. Направление нумерации фотоприемников в линейке фотоприемников 2 и светоизлучающих элементов в строках матрицы светоизлучающих элементов 1 совпадает. На фиг.2 этому направлению соответствует ось у. Каждый светоизлучающий элемент с номером k в каждой из строк матрицы 1 (то есть в каждой из линеек светоизлучающих элементов) оптически связан с входным торцом фотоприемника с номером k в линейке фотоприемников 2. Соответственно, каждый фотоприемник в линейке фотоприемников 2 оптически связан одновременно со всеми светоизлучающими элементами в столбце матрицы светоизлучающих элементов 1, имеющем тот же порядковый номер, что и фотоприемник в линейке фотоприемников 2, при условии отсчета номеров в одном направлении (оси у на фиг.2).

Заявляемый оптоэлектронный процессор изготовляется в двух исполнениях, различающихся типом электронных микросхем 3 на фиг.2. В первом исполнении, используемом для выполнения операций MAXIMUM, входной сигнал вводится в оптоэлектронный процессор в виде неинвертированного кода, а каждый из выходов фотоприемников в линейке фотоприемников 2 находится в электрической связи с входом одной из электронных микросхем, входящих в набор буферных неинвертирующих микросхем 3. При этом выходы набора буферных неинвертирующих микросхем 3 являются выходами устройства, задающими дискретное логическое значение выходного сигнала Y в виде неинвертированного кода. Во втором исполнении, используемом для выполнения операции MINIMUM, входные сигналы вводятся в инвертированном виде, а каждый из выходов фотоприемников в линейке фотоприемников 2 находится в электрической связи с входом одной из электронных микросхем, входящих в набор инвертирующих микросхем НЕ 3. Выходы всего набора микросхем НЕ 3 являются выходами для второго исполнения оптоэлектронного процессора и задают дискретное логическое значение выходного сигнала Y в виде неинвертированного кода, приведенного на фиг.1. Направление и порядок нумерации буферных неинвертирующих и инвертирующих микросхем НЕ совпадает с направлением и порядком нумерации фотоприемников в линейке фотоприемников 2.

Число градаций р величины входных переменных X1, X2, ..., Xn является одинаковым для всех переменных, выбирается заранее и определяет число светоизлучающих элементов в строках матрицы светоизлучающих элементов 1.

Используемый принцип работы заявляемого оптоэлектронного процессора позволяет работать с р-дискретными градациями величин входных сигналов как в рамках аппарата многозначной логики, так и применительно к р-значному приближению нечеткой логики.

Способ выполнения кодирования входных сигналов согласно фиг.1 и способ взаимного преобразования инвертированных и неинвертированных сигналов друг в друга в заявляемом устройстве не оговаривается и позволяет использовать произвольные микроэлектронные и оптоэлектронные узлы, комбинируя их любым удобным способом с оптоэлектронными процессорами, выполняющими логические операции MAXIMUM, MINIMUM.

Заявляемое устройство работает следующим образом. Информационные сигналы X1, X2, ..., Xn, величины которых могут принимать р-дискретных градаций по величине, вводятся в кодированном виде в линейки, составленные из р светоизлучающих элементов и составляющие строки матрицы светоизлучающих элементов 1 (см фиг.2). В первом исполнении оптоэлектронного процессора на входы подается неинвертированный кодированный сигнал (см фиг.1), а во втором исполнении - инвертированный кодированный сигнал. В каждой из строк матрицы светоизлучающих элементов 1 каждый светоизлучающий элемент, предназначенный для ввода определенного логического уровня k, имеет номер q=k+1, отсчитываемый в одном и том же направлении для всех строк матрицы светоизлучающих элементов 1. Направление отсчета номеров q, которому на фиг.2 соответствует ось у, совпадает с направлением отсчета номеров фотоприемников в линейке фотоприемников 2. При этом пропорционально величине входного сигнала высвечивается разное число рядом расположенных светоизлучающих элементов. При уровне входного сигнала, описываемом нулевым логическим уровнем k=0, свет испускает только один элемент имеющий наименьшее значение номера q=1, то есть крайний левый элемент. При уровне входного сигнала, описываемом 1-м логическим уровнем, свет испускает крайний левый элемент и следующий, расположенный справа от него (этот случай показан на фиг.2 для сигнала X1). При максимально возможном логическом уровне входного сигнала k=p-1 свет испускают все р элементов линейки светоизлучающих элементов в соответствующей строке матрицы светоизлучающих элементов 1. Вследствие наличия оптической связи между элементами матрицы светоизлучающих элементов 1 и линейкой фотоприемников 2 световые сигналы, кодирующие входные сигналы X1, X2, ..., Xn будут подаваться на фотоприемники в линейке фотоприемников 2, работающие в пороговом режиме. На фиг.2 показано направление отсчета номеров слева направо, начиная от крайних левых элементов, вдоль оси Y, однако выбор направления отсчетов номеров элементов вдоль оси Y условен, если бы было выбрано направление отсчета номеров справа налево, то и направление отсчета фотоприемников и выходов инвертирующих микросхем НЕ следовало бы взять противоположным.

В линейке фотоприемников 2 каждый фотоприемник предназначен для идентификации строго определенного логического уровня k, где k=0,..., р-1, а отсчет логических уровней фотоприемников в линейке фотоприемников 2 производится в том же направлении, что и для светоизлучающих элементов в матрице светоизлучающих элементов 2. На фиг.2 этому направлению соответствует ось Y. Для срабатывания фотоприемника, обнаруживающего наличие логического сигнала k-уровня и находящегося одновременно в оптической связи со всеми светоизлучающими элементами, которые могут вводить сигнал k-го логического уровня отдельно по каждой из входных переменных X1, X2, ..., Xn, достаточно поступления сигнала хотя бы от одной из строк матрицы светоизлучающих элементов 1. На фиг.2 сработавшие в пороговом режиме фотоприемники в линейке фотоприемников 2, выдающие на выход электрический сигнал "1", показаны белым цветом. Фотоприемники, на которые свет не поступает, выдают выходной электрический сигнал "0" и заштрихованы на фиг.2. Выбор направления считывания выходных сигналов с линейки фотоприемников 2 является одинаковым для обоих исполнений оптоэлектронного процессора и определяется изначальным выбором отсчета первого элемента в линейках светоизлучающих элементов. Ввод входного сигнала "0" для какой-либо входной переменной приведет к засвечиванию фотоприемника, регистрирующего "0"-й логический уровень. Последующий ввод логического сигнала "1" для какой-либо входной переменной приведет к засвечиванию двух фотоприемников, и т. д. Для вычисления выражения Y=MAXIMUM(X1,X2,...,Xn) следует использовать вариант исполнения оптоэлектронного процессора, в котором каждый из сигналов с фотоприемников в линейке фотоприемников 2 подается на вход одной из микросхем, входящей в набор неинвертирующих буферных электронных микросхем 3. Набор выходных сигналов неинвертирующих буферных электронных микросхем 3 формирует неинвертированный выходной сигнал оптоэлектронного процессора. Для вычисления выражения Y=MINIMUM(X1,X2,...,Xn) следует использовать второй вариант исполнения оптоэлектронного процессора, в котором сигналы с фотоприемников в линейке фотоприемников 2 дополнительно инвертируются. Для этого каждый из этих сигналов подается на вход одной из микросхем, входящей в набор электронных инвертирующих микросхем НЕ 3. На выходах набора электронных инвертирующих микросхем НЕ 3 будет получен результат выполнения операции MINIMUM, при этом выходной сигнал будет представлен в неинвертированном виде согласно фиг.1.

Для реализации заявляемого устройства могут быть использованы известные типы оптоэлектронных изделий линейки светодиодов или полупроводниковых лазеров, любые разновидности полупроводниковых фотоприемников, например на основе Si, необходимыми требованиями к которым являются достаточная чувствительность и площадь фоточувствительной площадки, а также быстродействие.

Заявляемое устройство может быть использовано в качестве многовходовых логических вентилей многозначной и нечеткой логики в оптоэлектронных устройствах обработки информации. Такие многовходовые вентили предназначены для повышения производительности вычислений в задачах обработки сигналов и приближенных вычислений.

Литература

1. Арестова М. Л. , Быковский А.Ю. Методика реализации оптоэлектронных схем многопараметрической обработки сигналов на основе принципов многозначной логики. "Квантовая электроника", т.22, 10, 1995, с.980.

2. Прикладные нечеткие системы. Под ред. Т. Тэрано, К. Асаи, М. Сугэно. Пер. c яп. - М.: Мир, 1993.

3. Арестова М. Л. , Быковский А.Ю. Патент РФ 2044338 "Логическое устройство, реализующее операции MAXIMUM&MINIMUM", приоритет от 18.06.92.

4. J. W. Goodman, A.R. Dias, L.M. Wody. Fully parallel high speed incoherent optical method for performing the discrete fourier transform. Opt.lett, v.2, 1, pp.1-3, 1978.

5. Евтихиев Н.Н., Есепкина Н.А., Долгий В.А., Лавров А.П., Хотянов Б.М., Чернокожин В.В., Шестак С.А. Оптоэлектронный процессор в виде гибридной микросхемы. Квантовая электроника, т.22, 10, 1995, с.985.2

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПТОЭЛЕКТРОННОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2128356C1 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО, РЕАЛИЗУЮЩЕЕ ОПЕРАЦИИ MAXIMUM & MINIMUM | 1992 |

|

RU2044338C1 |

| СПОСОБ РЕГИСТРАЦИИ ОТОАКУСТИЧЕСКОЙ ЭМИССИИ | 1999 |

|

RU2194444C2 |

| СПОСОБ ДИАГНОСТИКИ АНОМАЛИЙ ЗРЕНИЯ И АНАЛИЗАТОР ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2000 |

|

RU2195854C2 |

| ПОЛУПРОВОДНИКОВЫЙ ЛАЗЕР С НАКАЧКОЙ ЭЛЕКТРОННЫМ ПУЧКОМ | 2000 |

|

RU2191453C2 |

| АЛМАЗНЫЙ ДЕТЕКТОР | 2001 |

|

RU2204813C1 |

| СПОСОБ ЛАЗЕРНОЙ ОБРАБОТКИ ДИСПЕРСНЫХ МАТЕРИАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2196023C2 |

| УСТРОЙСТВО ДЛЯ ИСПАРЕНИЯ ЙОДА | 2001 |

|

RU2204188C2 |

| СПОСОБ ПОВЫШЕНИЯ РАБОТОСПОСОБНОСТИ ОРГАНИЗМА | 2001 |

|

RU2204998C2 |

| ОПТОЭЛЕКТРОННЫЙ НЕЧЕТКИЙ ПРОЦЕССОР | 2011 |

|

RU2446436C1 |

Изобретение относится к области оптоэлектроники, в частности к оптоэлектронным вычислительным устройствам, и предназначено для использования в схемах параллельной оптоэлектронной обработки информации для реализации логических операций MAXIMUM, MINIMUM многозначной и нечеткой логики. Техническим результатом является создание оптоэлектронного процессора, позволяющего выполнять вычисления, основанные на логических операциях MAXIMUM, MINIMUM. Для этого оптоэлектронный процессор содержит матрицу светоизлучающих элементов, в оптической связи с которыми находится линейка фотоприемников, связанная с буферными электронными микросхемами. Число линеек светоизлучающих элементов, составляющих строки матрицы светоизлучающих элементов, определяется числом входных переменных, при этом все они содержат одинаковое число р светоизлучающих элементов. Линейки светоизлучающих элементов предназначены для ввода текущих значений входных переменных. 2 з.п.ф-лы, 2 ил.

| ЛОГИЧЕСКОЕ УСТРОЙСТВО, РЕАЛИЗУЮЩЕЕ ОПЕРАЦИИ MAXIMUM & MINIMUM | 1992 |

|

RU2044338C1 |

| АКАЕВ А.А | |||

| и др | |||

| Оптические методы обработки информации | |||

| - М.: Высшая школа, 1988, с.216-219 | |||

| ПОТЕМКИН И.С | |||

| Функциональные узлы цифровой автоматики | |||

| - М.: Энергоатомиздат, 1988, с.12 и 13 | |||

| ОПТОЭЛЕКТРОННОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2128356C1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ МНОГОФУНКЦИОНАЛЬНЫЙ КОРРЕЛЯТОР | 1994 |

|

RU2079874C1 |

| US 5121248 A, 09.06.1992. | |||

Авторы

Даты

2003-09-10—Публикация

2001-03-01—Подача