Изобретение относится к схемам, в частности, для работающих по DECT-стандарту устройств беспроводной связи, для регенерации входного сигнала, содержащего характеристические цифровые последовательности данных.

В современных системах обработки данных, устройствах и системах связи передача, хранение и обработка данных или информации все в большей мере осуществляется при помощи цифровой техники. При этом данные или информация представляются в виде последовательностей дискретных значений. Это цифровое кодирование в большинстве случаев основывается на двоичном представлении, при котором разрешенный алфавит символов ограничен двумя различными дискретными значениями, которые, как правило, обозначаются как "ВЫСОКОЕ" или " 1" и "НИЗКОЕ" или "0". Отдельные элементы или разряды, представляющие в закодированной таким образом последовательности данных соответственно одно из допустимых значений, при двоичном кодировании обозначают термином "Бит" (от англ. binary digit). Тем не менее, наряду с этим используются также цифровые представления, алфавит символов которых включает три или более различных дискретных значения.

Если последовательность цифровых значений представляют, например, в виде электрического сигнала, то получается сигнал, состоящий из последовательности сигнальных импульсов, которые представляют собой соответственно разряды лежащей в основе цифровой последовательности. При этом в идеальном случае все импульсы, представляющие одинаковые цифровые значения, идентичны между собой и явно отличаются, например, по форме или высоте уровня от импульсов, которые представляют другие цифровые значения. Таким образом, каждому цифровому значению взаимно однозначно соответствует специальный вид импульса.

Очень часто в цифровой технике для кодирования используют равные по длине друг другу так называемые "прямоугольные импульсы", причем каждый импульс характеризуется высотой фиксированного в пределах некоторой области допустимых погрешностей уровня сигнала. Для уровня сигнала при этом разрешены только дискретные значения, количество которых равно количеству N различных значений лежащего в основе алфавита символов, причем каждое цифровое значение взаимно однозначно соответствует одному из уровней сигнала.

При передаче, хранении или обработке осуществляемых преимущественно при помощи электрических или оптических сигналов закодированных цифровым кодом данных или информации в реальных условиях постоянно возникают помехи, которые приводят к отклонению характеристик сигнала от идеальных. Если эти отклонения, например из-за многократной передачи сигнала, становятся слишком большими, лежащая в основе цифровая последовательность не может больше однозначно восстанавливаться из сигнала и это приводит к ошибочному функционированию. Эта проблема возникает, как правило, когда соответствующие сигналы восстанавливают, например, после прохождения через линии передачи или при считывании их с использованием соответствующих устройств из памяти, при этом изначальная форма сигнала восстанавливается с существенными искажениями.

Из ЕР 0133067 А1 известно, например, такое устройство для регенерации сигнала, считываемого с оптической запоминающей дискеты, которое для коррекции считываемого тактового сигнала имеет обрабатывающую схему, дополнительно подключенную к считывающему процессору.

Регенерация цифровых сигналов используется также в беспроводных телекоммуникационных аппаратах, которые функционируют, например, в соответствии с цифровым DECT-стандартом, для того чтобы освободить передающийся по радио между базовой станцией и мобильной частью (или соответственно мобильной частью и базовой станцией) сигнал от возникающих при этом помех.

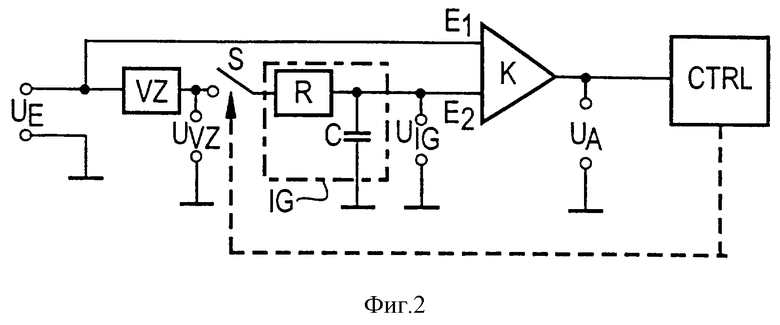

Соответствующая схема для DECT-систем, фигура 1, опубликована в DE 4236774 С2. При этом предназначенный для регенерации закодированный двоичным кодом сигнал в дальнейшем обозначается как входной сигнал UE, подается на аналоговый компаратор К, который сравнивает его с опорным уровнем UIG и на своем выходе в виде последовательности прямоугольных импульсов равной длины выдает регенерированный с идентичной двоичной структурой сигнал UA. Опорный уровень UIG получается посредством пошагового суммирования входного сигнала UE при помощи интегрирующего элемента IG.

При этом используется тот факт, что согласно DECT-стандарту в каждом канале передачи охватывающая первые 16 бит состоящего из 420 бит передающегося блока синхронизирующая пусковая кодовая группа, которая вместе с охватывающей последующие 16 бит синхронизирующей подтверждающей группой служит для синхронизации, представляет собой характеристическую последовательность данных. Она состоит из периодически чередующейся последовательности бит с ВЫСОКИМ и НИЗКИМ значением, которая для направления передачи "мобильная станция - базовая станция" начинается с "1010...", а для обратного направления передачи "базовая станция - мобильная станция" с "0101...". Суммирование входного сигнала UE, фигура 3а, распространяется соответственно только на эту характеристическую последовательность бит и прекращается при помощи управляемого устройством контроля CTRL переключателя S1, когда после синхронизирующей пусковой кодовой группы первый раз следуют друг за другом два одинаковых двоичных значения. Благодаря этому в течение регенерации последующей формы сигнала получается, фигура 3б, стабильное опорное напряжение UIG, по высоте приближенно равное среднему значению UDC ВЫСОКОГО и НИЗКОГО уровней входного сигнала UE. Однако недостатком опубликованного решения является то, что первое двоичное значение, идентичное непосредственно предшествующему, распознается лишь после того, как соответствующий ему сигнальный импульс был уже интегрирован, вследствие чего опорное напряжение UIG получается сдвинутым относительно своего предшествующего значения UDC. В таком случае это нежелательное смещение UOFF опорного уровня впоследствии должно исправляться подключенным при помощи переключателя S2 каскадом ОК компенсации смещения. Величина подлежащего коррекции смещения зависит при этом от уровня входного сигнала.

Если этот входной сигнал UE также, как и в случае беспроводных DECT-передач, образуется путем демодуляции радиосигнала, то величина подлежащего компенсации смещения UOFF зависит от уровня демодулированного сигнала UE и вместе с тем от вида модуляции, например от девиации амплитуды или частоты передатчика. При этом модуляционная девиация передатчика может иметь широкий диапазон изменений.

По меньшей мере при использовании беспроводных телекоммуникационных DECT-устройств добавляется еще один недостаток, так как полярность требуемой компенсации для направлений передачи "мобильная станция - основная станция" и "основная станция - мобильная станция" из-за инвертированных друг по отношению к другу синхронизирующих пусковых кодовых групп должна быть взаимно противоположной.

Из WO 94/10783 известно беспроводное телекоммуникационное устройство, в котором используется компенсирующая схема для устранения ошибочных значений при определении опорного уровня. Данное техническое решение является наиболее близким заявленному.

Задачей настоящего изобретения является указать улучшенную по сравнению с рассмотренной выше схему для регенерации входного сигнала, содержащего характеристические цифровые последовательности данных, при использовании которой устраняются названные недостатки.

Эта задача решается благодаря схеме, которой свойственны указанные в пункте 1 формулы изобретения признаки.

Соответствующая изобретению схема для регенерации цифрового сигнала, содержащего характеристические цифровые последовательности данных с N>1 различными разрешенными дискретными значениями в цифровом разряде, включает в свой состав:

- средства преобразования, которые на основе сравнения входного сигнала с как минимум N-1 опорными уровнями вырабатывают регенерированный цифровой выходной сигнал,

- по меньшей мере один интегрирующий элемент для получения как минимум N-1 опорных уровней путем интеграции состоящих из характеристических последовательностей данных участков входного сигнала,

- управляемое коммутационное устройство для включения и соответственно выключения интеграции входного сигнала, устройство контроля, которое посредством управления коммутационным устройством с началом характеристической последовательности данных в структуре сигнала включает процесс интеграции и, когда распознается конец последовательности данных, вновь выключает его, для того чтобы избежать смещения по меньшей мере N-1 опорного уровня, а также

- по крайней мере один элемент задержки, посредством которого осуществляется задержка подачи входного сигнала на как минимум один интегрирующий элемент по сравнению с подачей входного сигнала на средства преобразования, благодаря чему предотвращается приводящая к ошибочному уровню интеграция за пределами конца характеристической последовательности данных.

Таким образом, устраняются все связанные с компенсацией сдвига недостатки. Кроме того, по сравнению с использованием компенсационного каскада изобретение обуславливает явно более низкий расход материала и более низкую стоимость.

Следующие предпочтительные формы реализации изобретения являются предметом зависимых пунктов формулы изобретения.

Согласно первой форме реализации соответствующей изобретению схемы по крайней мере один элемент задержки реализован в виде RC-звена.

Кроме того, согласно второй форме реализации изобретения элемент задержки может быть реализован также в виде нескольких последовательно соединенных RC-звеньев, благодаря чему при помощи благоприятных также в отношении своей цены обычных стандартных радиодеталей могут устанавливаться практически любые времена задержки.

Согласно следующей форме реализации изобретения средства преобразования реализованы в виде по крайней мере одного компаратора. При этом, в частности, в двоичных цифровых системах могут использоваться благоприятные в смысле стоимости стандартные детали.

Предпочтительная модификация соответствующей изобретению схемы предполагает, что в случае N>2 по меньшей мере один из как минимум N-1 опорного уровня генерируется не непосредственно собственным интегрирующим элементом, а путем отвода от одного из других, выработанного по меньшей мере одним интегрирующим элементом опорного уровня. Это может осуществляться, например, при помощи одного или нескольких потенциометров. Благодаря этому получается, во-первых, экономия материала и места, а во-вторых, может снижаться нагрузка входного сигнала, обусловленная распределением тока между интегрирующими элементами.

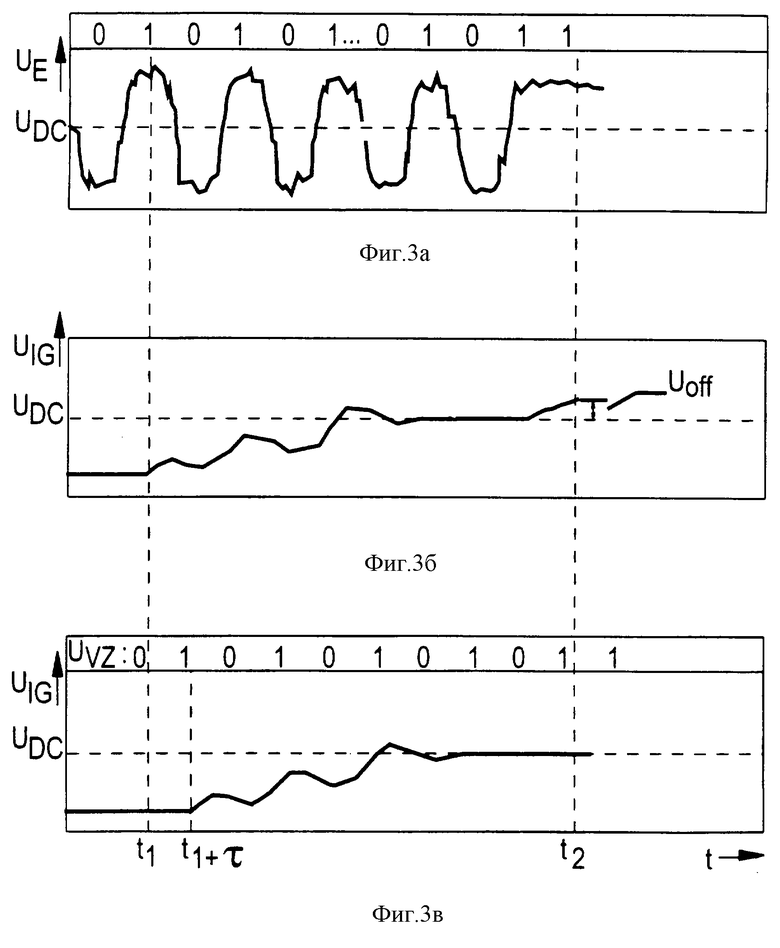

Далее изобретение более подробно поясняется при помощи соответствующего коммуникационной DECT-аппаратуре примера формы реализации со ссылками на фигуры 2 и 3.

Показывает:

Фигура 2 - соответствующую изобретению, в частности для DECT-систем, схему для регенерации сигнала, содержащего закодированные двоичным кодом данные;

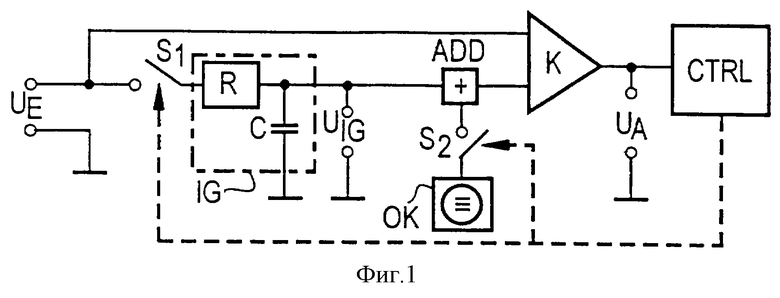

Фигура 3

а) временную развертку предназначенного для регенерации входного сигнала UE на примере соответствующей DECT-стандарту синхронизирующей пусковой кодовой группы;

б) выработанный из нее опорный уровень при использовании соответствующей уровню техники схемы по фигуре 1;

в) соответствующий опорный уровень при использовании соответствующей изобретению схемы по фигуре 2.

На фигуре 2 представлен пример предпочтительной формы реализации соответствующей изобретению схемы для случая закодированных двоичным кодом (N=2) данных, например, в DECT-системе. Предназначенный для регенерации входной сигнал UE подается, во-первых, непосредственно на неинвертированный вход E1 аналогового компаратора К, а во-вторых, через элемент задержки VZ как задержанный сигнал UVZ на реализованный в виде RC-звена интегрирующий элемент IG. Вырабатываемый интегратором опорный уровень UIG подается на второй вход E2 компаратора. Компаратор К сравнивает входной сигнал UE с опорным уровнем UIG и выдает на своем выходе представленный в виде последовательности прямоугольных импульсов одинаковой длины с идентичной двоичной структурой регенерированный сигнал UA. Подключенное последовательно устройство CTRL контроля распознает в структуре этого регенерированного сигнала UA соответственно предназначенные для интеграции характеристические двоичные последовательности, в DECT-системах cоответственно синхронизирующие пусковые кодовые группы. Интегрирование входного сигнала UE для формирования опорного уровня UIG ограничивается участками сигнала, содержащими такие характеристические двоичные последовательности, в то время как устройство контроля CTRL путем управления коммутирующим устройством S соответственно включает и выключает процесс интеграции, когда распознает начало или соответственно конец одной из этих двоичных последовательностей.

На фигуре 3 для обеих схем по фигурам 1 и 2 на примере соответствующей DECT-стандарту синхронизирующей пусковой кодовой группы представлены структура подлежащего регенерации входного сигнал UE и соответственно выработанного в процессе интеграции опорного уровня UIG. При этом двоичная последовательность на фигуре 3 относится к направлению передачи "Основная станция - мобильная станция" DECT-системы, и соответствующая схема используется в принимающих мобильных станциях. К моменту времени t1 от начала синхронизирующей пусковой кодовой группы входного сигнала UE переключатель S (соответственно S1 на фиг.1) замыкается. В соответствующей изобретению схеме по фигуре 2 по другому, нежели в схеме по фиг.1, в которой входной сигнал UE интегрируется непосредственно и уже с момента времени t1, осуществляется интеграция задержанного элементом задержки VZ на временной интервал τ по отношению к UE сигнала UVZ. В ходе соответствующего процесса интеграции в обеих случаях опорный уровень UIG строится, таким образом, до значения насыщения UDC, по величине примерно равного среднему значению ВЫСОКОГО и НИЗКОГО уровней входного сигнала UE. Конец синхронизирующей пусковой кодовой группы распознается устройством CTRL контроля, когда оно к моменту времени t2 первый раз принимает бит, который имеет такое же значение как и непосредственно ему предшествующий. При использовании схемы по фигуре 1 этот бит участвует к тому же и в процессе интеграции, что приводит, таким образом, к нежелательному смещению UOFF опорного уровня UIG, прежде чем в момент времени t2 интеграция прекращается. В противоположность этому при использовании соответствующей изобретению схемы по фигуре 2 в момент времени t2 названный бит еще не подается на интегрирующий элемент IG, когда устройство CTRL контроля путем соответствующего управления переключателем S прекращает интеграцию. Требуемая высота уровня UDC опорного напряжения поэтому сохраняется, и коррекция смещения является излишней.

Изобретение относится к системам обработки данных устройств беспроводной связи. Схема, в частности в DECT-системах, для регенерации входного сигнала (ВС) (UE), содержащего характеристические цифровые последовательности данных (ХЦПД) с N>1 различными разрешенными дискретными значениями в цифровом разрезе, содержит средство преобразования, вырабатывающее регенерированный выходной цифровой сигнал и которое сравнивает ВС (UE) c опорными уровнями, образованными путем коммутации (S) и интеграции с задержкой (VZ) участков ВС (Ue) на интеграторе (IG). При этом управление коммутационным устройством (S) к началу ХЦПА или к ее концу осуществляется устройством контроля (СТRL). Технический результат заключается в предотвращении интеграции после окончания ХЦПД, приводящей к искажению уровня. 4 з.п. ф-лы, 3 ил.

| Экономайзер | 0 |

|

SU94A1 |

| US 4672596, 09.06.1987 | |||

| US 5274273 A, 28.12.1993 | |||

| НАРЫШКИН А.К | |||

| Импульсные устройства ЭВМ, приборов и систем | |||

| - М.: Энергоатомиздат, 1991, с.56, 58, 64. | |||

Авторы

Даты

2003-09-27—Публикация

1997-03-27—Подача