Изобретение относится к электротехнике и может быть использовано в качестве реле времени.

Известно устройство, содержащее траверсу, якорь, упругий амортизатор, при этом в траверсе с двух сторон выполнены канавки, на которых выполнены скосы, на выступающей нижней части траверсы выполнены полозья, в средней части траверсы выполнен паз для установки в него упругого амортизатора, а в центре якоря установлена ось с возможностью вхождения и фиксации упомянутой оси якоря в канавках [1].

Недостатком устройства являются относительно узкие функциональные возможности, не позволяющие использовать его в качестве реле времени.

Наиболее близким по технической сущности к заявляемому является устройство, содержащее последовательно соединенные генератор тактовых импульсов, двоичный счетчик, дешифратор, формирователь импульсов и исполнительный блок [2].

Недостатком наиболее близкого технического решения являются относительно узкие функциональные возможности, поскольку оно не обеспечивает возможность оперативной перестройки временных характеристик и не позволяет выработать несколько регулируемых по времени состояния своих выходных параметров при управлении технологическими процессами.

Техническим результатом изобретения является расширение функциональных возможностей.

Этот технический результат достигается тем, что в устройство, содержащее первый исполнительный блок, генератор тактовых импульсов, двоичный счетчик и дешифратор, при этом выход двоичного счетчика соединен с входом дешифратора, первый и второй выходы которого соединены, соответственно, с первым счетным и вторым счетным входами первого исполнительного блока, введены блок питания, входные клеммы которого являются входными клеммами реле времени, с первой, второй и третьей выходными клеммами и с общей клеммой, блок запуска с первой и второй входными клеммами, с первой и второй выходными клеммами и с общей клеммой, второй исполнительный блок с первой и второй клеммами питания, с первой и второй входными клеммами, с общей клеммой и с выходной клеммой и управляемый делитель частоты с клеммой питания, с общей клеммой, с входом установки нуля, со счетным входом и выходом, при этом первая выходная клемма блока питания соединена с первой входной клеммой блока запуска, с первой клеммой питания второго исполнительного блока и со второй клеммой питания первого исполнительного блока, вторая выходная клемма соединена со второй клеммой питания второго исполнительного блока, третья выходная клемма соединена с клеммами питания генератора тактовых импульсов и управляемого делителя частоты, со второй входной клеммой блока запуска, с клеммой питания двоичного счетчика, с клеммой питания дешифратора и со второй клеммой питания первого исполнительного блока, а общая клемма соединена с общими клеммами генератора тактовых импульсов, управляемого делителя частоты, блока запуска, второго исполнительного блока, двоичного счетчика, дешифратора и первого исполнительного блока, первая выходная клемма блока запуска соединена с первой входной клеммой второго исполнительного блока, с входом установки нуля управляемого делителя частоты, с входом установки нуля двоичного счетчика и с входом установки в начальное состояние первого исполнительного блока, а вторая выходная клемма блока запуска соединена с третьим входом первого исполнительного блока, четвертый вход которого соединен с выходной клеммой второго исполнительного блока, выход генератора тактовых импульсов соединен со счетным входом управляемого делителя частоты, выход которого соединен со счетным входом двоичного счетчика, а вторая входная клемма второго исполнительного блока соединена с выходом первого исполнительного блока.

Кроме того, блок запуска содержит элементы НЕ с первого по четвертый, резисторы с первого по пятый, первый и второй конденсаторы, диод, при этом первые клеммы первого и третьего резисторов являются, соответственно, первой и второй входными клеммами блока запуска, вторая клемма первого резистора соединена с первой клеммой четвертого резистора, с входами первого элемента НE и с первой клеммой второго резистора, вторая клемма которого соединена с первыми клеммами первого конденсатора, пятого резистора, с первыми клеммами питания первого, второго, третьего и четвертого элементов НЕ и является общей клеммой блока запуска, вторая клемма третьего резистора соединена с входами второго элемента НЕ, со второй клеммой первого конденсатора и с анодом диода, катод которого соединен с выходом первого элемента НЕ, вторая клемма четвертого резистора соединена с выходом второго элемента НЕ, с первой клеммой второго конденсатора и является первой выходной клеммой блока запуска, выход четвертого элемента НЕ, вход которого соединен с выходом третьего элемента НЕ, является второй выходной клеммой блока запуска, вторая клемма второго конденсатора соединена с входом третьего элемента НЕ и со второй клеммой пятого резистора, а вторая входная клемма блока запуска соединена со вторыми клеммами питания первого, второго, третьего и четвертого элементов НЕ.

Кроме того, второй исполнительный блок содержит резисторы с первого по четвертый, соответственно, диоды с первого по третий, первый и второй транзисторы, обмотку реле, при этом первая клемма третьего резистора соединена с первой клеммой четвертого резистора и является первой клеммой питания упомянутого блока, катод второго диода соединен с первой клеммой обмотки и является второй клеммой питания упомянутого блока, эмиттер первого транзистора соединен с катодом третьего диода и является общей клеммой упомянутого блока, первой входной клеммой которого является первая клемма первого резистора, вторая клемма которого соединена с базой первого транзистора, коллектор которого соединен с первой клеммой второго резистора и с катодом первого диода, анод которого соединен со второй клеммой третьего резистора и с базой второго транзистора, эмиттер которого соединен с анодом третьего диода, а коллектор соединен со второй клеммой четвертого резистора и является исходной клеммой упомянутого блока, вторая клемма второго резистора соединена со второй клеммой обмотки реле, с анодом второго диода и является второй входной клеммой упомянутого блока.

Кроме того, генератор тактовых импульсов содержит резисторы с первого по четвертый, первый и второй элементы НЕ, первый и второй конденсаторы, при этом первая и вторая клеммы питания первого и второго элементов НЕ являются, соответственно, клеммой питания и общей клеммой генератора, первая клемма первого резистора соединена с входами первого элемента НЕ, выход которого соединен с первой крайней и со средней клеммами третьего резистора и со входами второго элемента НЕ, выход которого соединен с первой клеммой первого конденсатора и с первой клеммой четвертого резистора, вторая клемма которого является выходом генератора и соединена с первой клеммой второго конденсатора, вторая клемма которого соединена с общей клеммой генератора, а вторая клемма первого конденсатора соединена со второй клеммой первого резистора и с первой клеммой второго резистора, вторая клемма которого соединена со второй крайней клеммой третьего резистора.

Кроме того, управляемый делитель частоты содержит счетчик, первый диод, конденсатор, первый и второй элементы НЕ, первый резистор, переключатель, второй резистор, первый, второй и третий транзисторы, второй, третий и четвертый диоды, при этом клемма питания счетчика соединена с первой клеммой первого резистора, с клеммами питания первого и второго элементов НЕ и является клеммой питания упомянутого делителя, общая клемма счетчика соединена с первой клеммой конденсатора, с общими клеммами первого и второго элементов НЕ и является общей клеммой упомянутого делителя, анод первого диода является входом установки нуля упомянутого делителя, а катод соединен со второй клеммой конденсатора, с первой клеммой второго резистора, вторая клемма которого соединена с выходом второго элемента НЕ и с R-входом счетчика, С-вход которого является счетным входом упомянутого делителя, вторая клемма первого резистора соединена с первой выходной клеммой переключателя, вторая, третья и четвертая выходные клеммы которого соединены со входами первого элемента НЕ, выход которого соединен со входами второго элемента НЕ и является выходом упомянутого делителя, первый, второй, третий, четвертый и пятый выходы счетчика соединены, соответственно, с базой первого транзистора, с базой второго транзистора и с катодом второго диода, с катодом третьего диода, с базой третьего транзистора и с катодом четвертого диода, эмиттер первого транзистора соединен с первой входной клеммой переключателя, коллектор соединен с эмиттером второго транзистора и со второй входной клеммой переключателя, коллектор второго транзистора соединен с третьей входной клеммой переключателя и с эмиттером третьего транзистора, коллектор которого соединен с анодами второго, третьего и четвертого диодов и с четвертой входной клеммой переключателя.

Кроме того, двоичный счетчик содержит счетчик, группа выходов которого является выходом двоичного счетчика, клемма питания и общая клемма которого являются, соответственно, клеммой питания и общей клеммой двоичного счетчика, a R- и С-входы являются, соответственно, входом установки нуля и счетным входом двоичного счетчика.

Кроме того, дешифратор содержит группу из семи транзисторов, базы которых являются входом группы и входом дешифратора, первый и второй переключатели, первый и второй резисторы, первые клеммы которых являются клеммой 7-3 питания дешифратора, первый и второй конденсаторы, первые клеммы которых являются, соответственно, первым и вторым выходами дешифратора и соединены с первой и со второй клеммой второго резистора, соответственно, при этом эмиттеры транзисторов группы соединены с соответствующими клеммами первого переключателя, выходная клемма которого соединена со второй клеммой первого резистора, а коллекторы транзисторов группы соединены с соответствующими клеммами второго переключателя, выходная клемма которого соединена со второй клеммой второго резистора, а вторые клеммы первого и второго конденсаторов являются общей клеммой дешифратора.

Кроме того, первый исполнительный блок содержит первый и второй триггеры, клеммы питания и общие клеммы которых являются, соответственно, второй клеммой питания и общей клеммой упомянутого блока, первый и второй ключи, резисторы с первого по пятый, соответственно, первая обмотка реле, диоды с первого по седьмой, первый и второй конденсаторы, вторая обмотка реле, третий ключ и транзистор, коллектор которого соединен с анодом шестого диода и является первой клеммой питания упомянутого блока, выход первого триггера соединен с управляющим входом первого ключа и с первой клеммой первого резистора, вторая клемма которого соединена с первой силовой клеммой первого ключа, с первой клеммой первого конденсатора, с первой силовой клеммой третьего ключа, с первой клеммой третьего резистора, с первой силовой клеммой второго ключа, с первой клеммой второго конденсатора, с первой клеммой второго резистора, с S-входами первого и второго триггеров и с общей клеммой упомянутого блока, первая клемма пятого резистора соединена с четвертым входом упомянутого блока, вторая клемма соединена с базой транзистора, эмиттер которого соединен с анодом второго диода, катод которого соединен с первой клеммой четвертого резистора, вторая клемма которого соединена со второй клеммой первого конденсатора, с катодом первого диода и с первой клеммой первой обмотки реле, вторая клемма которого соединена с анодом первого диода и со второй силовой клеммой первого ключа, анод третьего диода соединен с выходом упомянутого блока, а катод соединен со второй силовой клеммой третьего ключа и с катодом четвертого диода, анод которого соединен с первой клеммой второй обмотки реле и с анодом седьмого диода, катод которого соединен со второй и с третьей клеммами второй обмотки реле, с катодом шестого диода, со второй клеммой второго конденсатора и с катодом пятого диода, анод которого соединен с четвертой клеммой второй обмотки реле и со второй силовой клеммой второго ключа, управляющая клемма которого соединена со второй клеммой третьего резистора и с выходом второго триггера, а вторая клемма второго резистора соединена с управляющим входом третьего ключа и является третьим входом упомянутого блока, при этом R-входы первого и второго триггеров являются входом установки в начальное состояние упомянутого блока, вторая клемма питания соединена с D-входами первого и второго триггеров, С-вход первого триггера является первым счетным входом, а С-вход второго триггера - вторым счетным входом упомянутого блока.

Кроме того, блок питания содержит трансформатор, входные клеммы которого являются входными клеммами блока питания, выпрямительный блок, первая и вторая входные клеммы которого соединены, соответственно, с первой и второй клеммами выходной обмотки трансформатора, диод, анод которого соединен с первой выходной клеммой выпрямительного блока и является первой выходной клеммой блока питания, первый и второй конденсаторы, первый, второй и третий транзисторы, резистор, первая клемма которого является второй выходной клеммой блока питания и соединена с коллекторами первого и второго транзисторов и с первой клеммой первого конденсатора, вторая клемма которого является общей клеммой блока питания и соединена с базой и коллектором третьего транзистора, со второй выходной клеммой выпрямительного блока и с первой клеммой второго конденсатора, вторая клемма которого соединена с третьей выходной клеммой блока питания и с эмиттером первого транзистора, база которого соединена с эмиттером второго транзистора, база которого соединена со второй клеммой резистора и с эмиттером третьего транзистора.

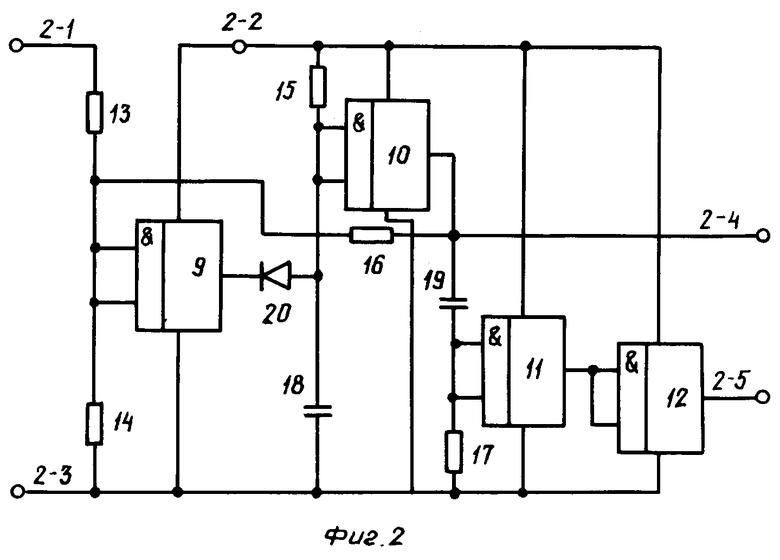

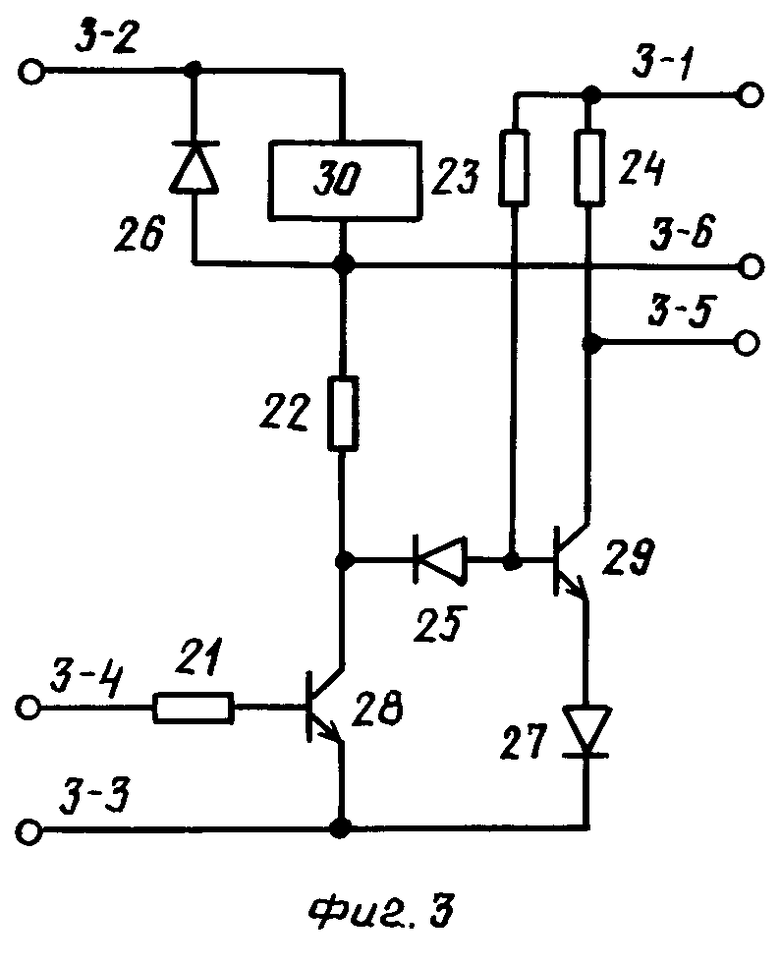

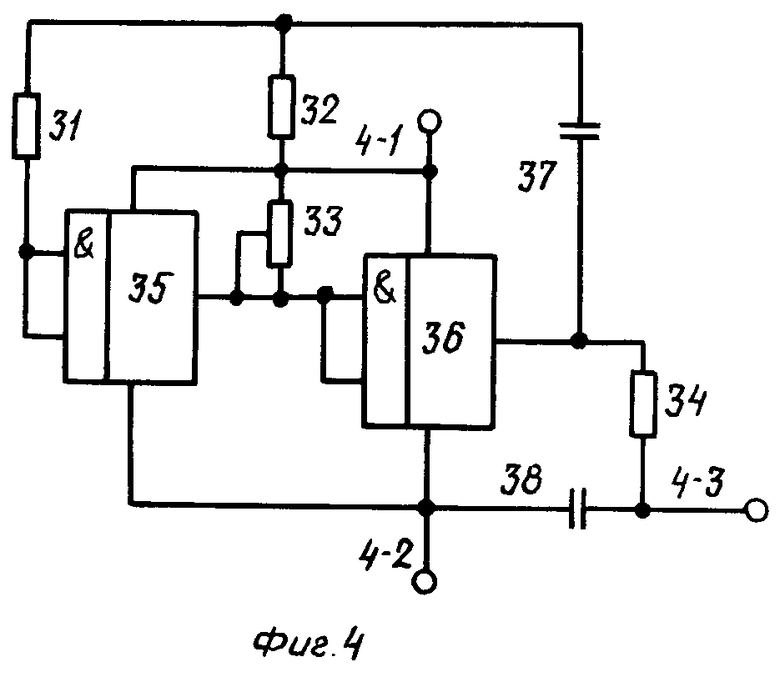

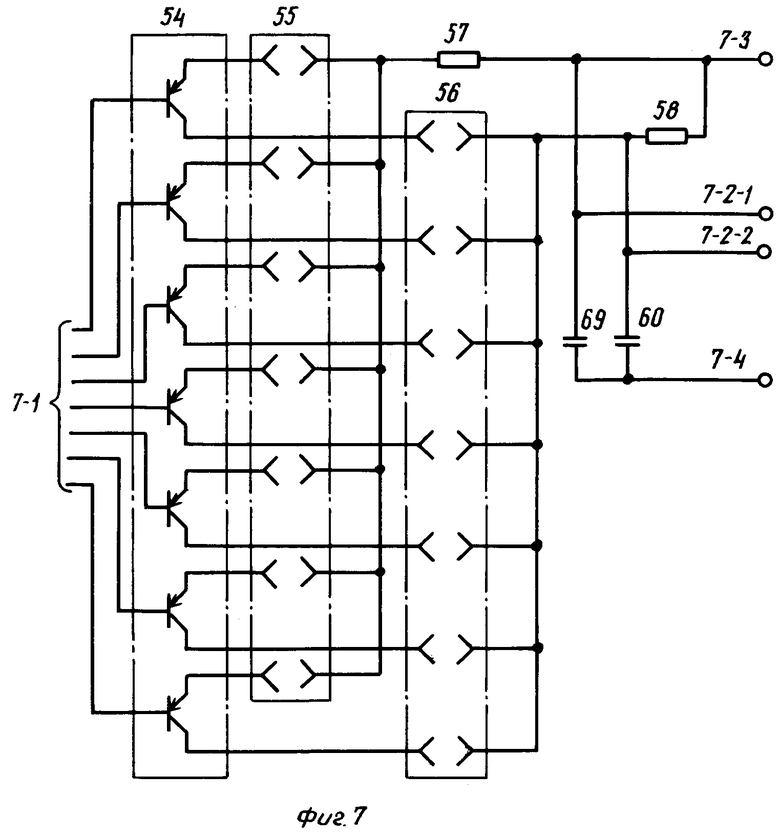

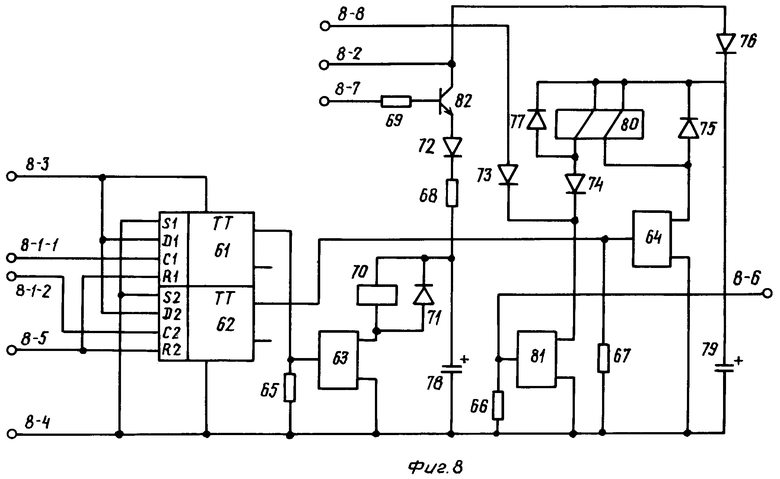

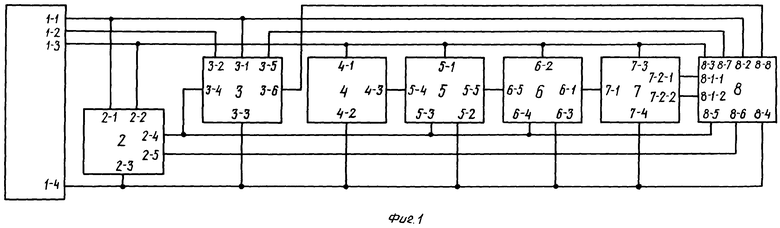

На фиг. 1 представлена электрическая структурная схема реле времени, на фиг. 2 - пример выполнения блока запуска, на фиг.3 - второго исполнительного блока, на фиг.4 - генератора тактовых импульсов, на фиг.5 - управляемого делителя частоты, на фиг.6 - двоичного счетчика, на фиг.7 - дешифратора, на фиг.8 - первого исполнительного блока, на фиг.9 - блока питания.

Реле времени (фиг.1) содержит блок 1 питания с первой 1-1, второй 1-2, третьей 1-3 выходными клеммами и с общей клеммой 1-4, блок 2 запуска с первой 2-1 и второй 2-2 входными клеммами, с общей 2-3 клеммой с первой 2-4 и второй 2-5 выходными клеммами, второй исполнительный блок 3 с первой 3-1 и второй 3-2 клеммами питания, с общей клеммой 3-3, с первой 3-4 входной клеммой, с выходной клеммой 3-5 и со второй входной клеммой 3-6, генератор 4 тактовых импульсов с клеммой питания 4-1, с общей клеммой 4-2 и с выходом 4-3, управляемый делитель 5 частоты с клеммой питания 5-1, с общей клеммой 5-2, с входом 5-3 установки нуля, со счетным входом 5-4 и с выходом 5-5, двоичный счетчик 6 с выходом 6-1, с клеммой 6-2 питания, с общей клеммой 6-3, с входом 6-4 установки нуля и со счетным входом 6-5, дешифратор 7 с входом 7-1, с первым 7-2-1 и вторым 7-2-2 выходами, с клеммой 7-3 питания и с общей клеммой 7-4, первый исполнительный блок 8 с первым 8-1-1 и вторым 8-1-2 счетными входами, с первой 8-2 и второй 8-3 клеммами питания, с общей клеммой 8-4, с входом 8-5 установки в начальное состояние, с третьим выходом 8-6, с четвертым входом 8-7 и с выходом 8-8, при этом выход 6-1 двоичного счетчика соединен с входом 7-1 дешифратора, первый 7-2-1 и второй 7-2-2 выходы которого соединены, соответственно, с первым счетным 8-1-1 и вторым 8-1-2 счетным входами первого исполнительного блока, первая выходная клемма 1-1 блока 1 питания соединена с первой входной клеммой 2-1 блока 2 запуска, с первой клеммой 3-1 питания второго исполнительного блока 3 и со второй клеммой 8-3 питания первого исполнительного блока 8, вторая выходная клемма 1-2 соединена со второй клеммой 3-2 питания второго исполнительного блока, третья выходная клемма 1-3 соединена с клеммой 4-1 питания генератора тактовых импульсов и с клеммой 5-1 питания управляемого делителя частоты, со второй входной клеммой 2-2 блока запуска, с клеммой 6-2 питания двоичного счетчика 6, с клеммой 7-3 питания дешифратора 7 и со второй клеммой 8-3 питания первого исполнительного блока 8, а общая клемма 1-4 соединена с общей клеммой 4-2 генератора 4 тактовых импульсов, с общей клеммой 5-2 управляемого делителя 5 частоты, с общей клеммой 2-3 блока 2 запуска, с общей клеммой 3-3 второго исполнительного блока 3, с общей клеммой 6-3 двоичного счетчика 6, с общей клеммой 7-4 дешифратора 7 и с общей клеммой 8-4 первого исполнительного блока 8, первая выходная клемма 2-4 блока 2 запуска соединена с первой входной клеммой 3-4 второго исполнительного блока 4, с входом 5-3 установки нуля управляемого делителя 5 частоты, с входом 6-4 установки нуля двоичного счетчика 6 и с входом 8-5 установки в начальное состояние первого исполнительного блока 8, а вторая выходная клемма 2-5 блока 2 запуска соединена с третьим входом 8-6 первого исполнительного блока 8, четвертый вход 8-7 которого соединен с выходной клеммой 3-5 второго исполнительного блока 3, выход 4-3 генератора 4 тактовых импульсов соединен со счетным входом 5-4 управляемого делителя 5 частоты, выход которого соединен со счетным входом 6-5 двоичного счетчика 6, а вторая входная клемма 3-6 второго исполнительного блока 6 соединена с выходом 8-6 первого исполнительного блока 6.

Блок 2 запуска (фиг.2) содержит элементы НЕ 9-12 с первого по четвертый, соответственно, резисторы 13-17 с первого по пятый, первый 18 и второй 19 конденсаторы, диод 20, при этом первые клеммы первого 13 и третьего 15 резисторов являются, соответственно, первой 2-1 и второй 2-2 входными клеммами блока запуска, вторая клемма первого резистора 13 соединена с первой клеммой четвертого резистора 16, с входами первого элемента HE 9 и с первой клеммой второго резистора 14, вторая клемма которого соединена с первыми клеммами первого конденсатора 18, пятого резистора 17, с первыми клеммами питания первого 9, второго 10, третьего 11 и четвертого 12 элементов НЕ и является общей клеммой 2-3 блока запуска, вторая клемма третьего резистора 15 соединена с входами второго элемента НЕ 10, со второй клеммой первого конденсатора 18 и с анодом диода 20, катод которого соединен с выходом первого элемента НЕ 9, вторая клемма четвертого резистора 16 соединена с выходом второго элемента НЕ 10, с первой клеммой второго конденсатора 19 и является первой выходной клеммой 2-4 блока запуска, выход четвертого элемента НЕ 12, вход которого соединен с выходом третьего элемента НЕ 11, является второй выходной клеммой 2-5 блока запуска, вторая клемма второго конденсатора соединена с входом третьего элемента НЕ 11 и со второй клеммой пятого резистора 17, а вторая входная клемма 2-2 блока запуска соединена со вторыми клеммами питания первого, второго 10, третьего 11 и четвертого 12 элементов НЕ.

Второй исполнительный блок 3 (фиг.3) содержит резисторы 21-24 с первого по четвертый, соответственно, диоды 25-27 с первого по третий, соответственно, первый 28 и второй 29 транзисторы, обмотку 30 реле, при этом первая клемма третьего резистора 23 соединена с первой клеммой четвертого резистора 24 и является первой клеммой 3-1 питания упомянутого блока, катод второго диода 26 соединен с первой клеммой обмотки 30 и является второй клеммой питания упомянутого блока, эмиттер первого транзистора 28 соединен с катодом третьего диода 27 и является общей клеммой упомянутого блока, первой входной клеммой которого является первая клемма первого резистора 21, вторая клемма которого соединена с базой первого транзистора 28, коллектор которого соединен с первой клеммой второго резистора 22 и с катодом первого диода 25, анод которого соединен со второй клеммой третьего резистора 23 и с базой второго транзистора 29, эмиттер которого соединен с анодом третьего диода 27, а коллектор соединен со второй клеммой четвертого резистора 24 и является выходной клеммой 3-5 упомянутого блока, вторая клемма второго резистора 22 соединена со второй клеммой обмотки 30 реле, с анодом второго диода 26 и является второй входной клеммой 3-6 упомянутого блока.

Генератор 3 тактовых импульсов (фиг.4) содержит резисторы 31-34 с первого по четвертый, соответственно, первый 35 и второй 36 элементы HЕ, первый 37 и второй 38 конденсаторы, при этом первая и вторая клеммы питания первого 35 и второго 36 элементов НЕ являются, соответственно, клеммой 4-1 питания и общей клеммой 4-1 генератора, первая клемма первого резистора 31 соединена с входами первого элемента НЕ 35, выход которого соединен с первой крайней и со средней клеммами третьего резистора 33 и со входами второго элемента НЕ 36, выход которого соединен с первой клеммой первого конденсатора 37 и с первой клеммой четвертого резистора 34, вторая клемма которого является выходом 3-4 генератора и соединена со второй клеммой второго конденсатора 38, вторая клемма которого соединена с общей клеммой 4-2 генератора, а вторая клемма первого конденсатора 37 соединена со второй клеммой первого резистора 31 и с первой клеммой второго резистора 32, вторая клемма которого соединена со второй крайней клеммой третьего резистора 33.

Управляемый делитель частоты (фиг.5) содержит счетчик 39, первый диод 40, конденсатор 41, первый 42 и второй 43 элементы НЕ, первый резистор 44, переключатель 45, второй резистор 46, первый 47, второй 48 и третий 49 транзисторы, второй 50, третий 51 и четвертый 52 диоды, при этом клемма питания счетчика 39 соединена с первой клеммой первого резистора 44, с клеммами питания первого 42 и второго 43 элементов НЕ и является клеммой 5-1 питания упомянутого делителя, общая клемма счетчика 39 соединена с первой клеммой конденсатора 41, с общими клеммами первого 42 и второго 43 элементов НЕ и является общей клеммой 5-2 упомянутого делителя, анод первого диода является входом 5-3 установки нуля упомянутого делителя, а катод соединен со второй клеммой конденсатора 41, с первой клеммой второго резистора 46, вторая клемма которого соединена с выходом второго элемента НЕ 43 и с R-входом счетчика 39, С-вход которого является счетным входом упомянутого делителя, вторая клемма первого резистора 44 соединена с первой выходной клеммой переключателя 45, вторая, третья и четвертая выходные клеммы которого соединены со входами первого элемента НЕ 42, выход которого соединен со входами второго элемента НЕ 43 и является выходом упомянутого делителя, первый, второй, третий, четвертый и пятый выходы счетчика 39 соединены, соответственно, с базой первого транзистора 47, с базой второго транзистора 48 и с катодом второго диода 50, с катодом третьего диода 51, с базой третьего транзистора 49 и с катодом четвертого диода 52, эмиттер первого транзистора соединен с первой входной клеммой переключателя 45, коллектор соединен с эмиттером второго транзистора 48 и со второй входной клеммой переключателя 45, коллектор второго транзистора 48 соединен с третьей входной клеммой переключателя 45 и с эмиттером третьего транзистора 49, коллектор которого соединен с анодами второго 50, третьего 51 и четвертого 52 диодов и с четвертой входной клеммой переключателя 45.

Двоичный счетчик 6 (фиг.6) содержит счетчик 53, группа выходов которого является выходом 6-1 двоичного счетчика, клемма питания и общая клемма которого являются, соответственно, клеммой питания 6-2 и общей клеммой 6-3 двоичного счетчика, a R- и С-входы являются, соответственно, входом 6-4 установки нуля и счетным входом 6-5 двоичного счетчика.

Дешифратор 7 (фиг.7) содержит группу 54 из семи транзисторов, базы которых являются входом группы 54 и входом 7-1 дешифратора, первый 55 и второй 56 переключатели, первый 57 и второй 58 резисторы, первые клеммы которых являются клеммой 7-3 питания дешифратора, первый 59 и второй 60 конденсаторы, первые клеммы которых являются, соответственно, первым 7-2-1 и вторым 7-2-2 выходами дешифратора и соединены с первой и со второй клеммой второго резистора 58, соответственно, при этом эмиттеры транзисторов группы 54 соединены с соответствующими клеммами первого переключателя 55, выходная клемма которого соединена со второй клеммой первого резистора 57, коллекторы транзисторов группы 54 соединены с соответствующими клеммами второго переключателя 56, выходная клемма которого соединена со второй клеммой второго резистора 58, а вторые клеммы первого 59 и второго 60 конденсаторов являются общей клеммой 7-4 дешифратора 7.

Первый исполнительный блок 8 (фиг.8) содержит первый 61 и второй 62 триггеры, клеммы питания и общие клеммы которых являются, соответственно, второй клеммой 8-3 питания и общей клеммой 8-4 упомянутого блока, первый 63 и второй 64 ключи, резисторы 65-69 с первого по пятый, соответственно, первая обмотка 70 реле, диоды 71-77 с первого по седьмой, соответственно, первый 78 и второй 79 конденсаторы, вторая обмотка 80 реле, третий ключ 81 и транзистор 82, коллектор которого соединен с анодом шестого диода 76 и является первой клеммой 8-2 питания упомянутого блока, выход первого триггера соединен с управляющим входом первого ключа 63 и с первой клеммой первого резистора 65, вторая клемма которого соединена с первой силовой клеммой первого ключа 63, с первой клеммой первого конденсатора 78, с первой силовой клеммой третьего ключа 81, с первой клеммой третьего резистора 67, с первой силовой клеммой второго ключа 64, с первой клеммой второго конденсатора 79, с первой клеммой второго резистора 66, с S-входами первого 61 и второго 62 триггеров и с общей клеммой 8-4 упомянутого блока, первая клемма пятого резистора 69 соединена с четвертым входом 8-7 упомянутого блока, вторая клемма соединена с базой транзистора 82, эмиттер которого соединен с анодом второго диода 72, катод которого соединен с первой клеммой четвертого резистора 68, вторая клемма которого соединена со второй клеммой первого конденсатора 78, с катодом первого диода 71 и с первой клеммой первой обмотки 70 реле, вторая клемма которого соединена с анодом первого диода 71 и со второй силовой клеммой первого ключа 63, анод третьего диода 73 соединен с выходом 8-8 упомянутого блока, а катод соединен со второй силовой клеммой третьего ключа 81 и с катодом четвертого диода 74, анод которого соединен с первой клеммой второй обмотки 80 реле и с анодом седьмого диода 77, катод которого соединен со второй и с третьей клеммами второй обмотки 80 реле, с катодом шестого диода 76, со второй клеммой второго конденсатора 79 и с катодом пятого диода 75, анод которого соединен с четвертой клеммой второй обмотки 80 реле и со второй силовой клеммой второго ключа 64, управляющая клемма которого соединена со второй клеммой третьего резистора 67 и с выходом второго триггера 62, а вторая клемма второго резистора 66 соединена с управляющим входом третьего ключа 81 и является третьим входом 8-6 упомянутого блока, при этом R-входы первого 61 и второго 62 триггеров являются входом 8-5 установки в начальное состояние упомянутого блока, вторая клемма 8-3 питания соединена D-входами первого 61 и второго 62 триггеров, С-вход первого триггера 61 является первым счетным входом 8-1-1, а С-вход второго триггера 62 - вторым счетным входом 8-1-2 упомянутого блока.

Блок 1 питания (фиг.9) содержит трансформатор 83, входные клеммы которого являются входными клеммами реле времени, выпрямительный блок 84, первая и вторая входные клеммы которого соединены, соответственно, с первой и второй клеммами выходной обмотки трансформатора 83, диод 85, анод которого соединен с первой выходной клеммой выпрямительного блока 84 и является первой выходной клеммой 1-1 блока питания, первый 86 и второй 87 конденсаторы, первый 88, второй 89 и третий 90 транзисторы и резистор 91, первая клемма которого является второй выходной клеммой 1-2 блока питания и соединена с коллекторами первого 88 и второго 89 транзисторов и с первой клеммой первого конденсатора 86, вторая клемма которого является общей клеммой блока питания и соединена с базой и коллектором третьего транзистора 90, со второй выходной клеммой выпрямительного блока 84 и с первой клеммой второго конденсатора 87, вторая клемма которого соединена с третьей выходной клеммой 1-3 блока питания и с эмиттером первого транзистора 88, база которого соединена с эмиттером второго транзистора 89, база которого соединена со второй клеммой резистора 91 и с эмиттером третьего транзистора 90.

В качестве элементов НЕ в блоках реле времени используются элементы И-НЕ с объединенными входами.

Работает реле времени следующим образом.

Блок 1 питания формирует на своих выходных и общей клеммах напряжения питания для других блоков устройства. Порог срабатывания блока 2 запуска задан соотношением величин первого 13 и второго 14 резисторов. При подаче напряжения на трансформатор 83 и его выпрямлении с помощью выпрямительного блока 84 заряжаются конденсаторы 89, 79, а на вход блока 2 запуска поступает пульсирующее напряжение с выхода выпрямительного блока 84. В результате на выходе элемента НЕ 9 формируются инвертированные импульсы с удвоенной частотой сети. Первый же из этих импульсов разряжает конденсатор 18 и на выходе элемента НЕ 10 появляется уровень логической единицы. Этот сигнал поступает на вход установки в ноль счетчиков 39, 53 и триггеров 61, 62, а через резистор 16 организуется цепь положительной обратной связи, позволяющая получить коэффициент возврата блока 2 запуска меньше единицы. С выхода элемента НЕ 10 через конденсатор 19 сигнал с уровнем логической единицы поступает на вход элемента НЕ 12, в результате чего открывается ключ 81 и по сигналу, проходящему через диод 74, срабатывает обмотка 80 реле, являющаяся обмоткой двустабильного реле, а по сигналу, проходящему через диод 73, срабатывает обмотка 30 реле с мгновенным контактом. По мере заряда конденсатора 19 через резистор 17 на входы элемента НЕ 11 поступает сигнал логического нуля, что приводит к закрытию ключа 81. Но при этом контакты обмотки 80 в исходное состояние не возвращаются, так как сигнал с выхода элемента НЕ 10, проходящий через резистор 21, открывает транзистор 28. Величина тока, проходящего через этот транзистор и резистор 22, достаточна для удержания контактов обмотки 30 в сработанном состоянии. При открытом транзисторе 28 сигнал, проходящий через резисторы 24 и 69, открывает транзистор 82 и по цепи транзистор 82 - диод 72 - резистор 68 заряжается конденсатор 78. При этом генератор 4 формирует импульсы, которые не подсчитываются в счетчиках 39 и 53.

При сбросе входного напряжения на выходе элемента НЕ 9 импульсы не формируются, диод 20 закрывается, конденсатор 18 заряжается через резистор 15 от конденсатора 86 и на выходе элемента НЕ 10 формируется сигнал логического нуля, разрешающий работу счетчиков и триггеров. Сигнал логического нуля на выходе элемента НЕ 10 приводит к возврату обмотки 30 в исходное состояние.

Управляемый делитель 5 частоты в зависимости от положения переключателя 45 делит частоты импульсов генератора на величины, кратные целому числу. Импульсы с выхода управляемого делителя 5 заполняют счетчик 53. При достижении числа импульсов величины, заданной положением переключателя 55 дешифратора 7, триггер 61 переключается и от тока конденсатора 78 кратковременно срабатывает обмотка 70. При достижении числа импульсов величины, заданной положением переключателя 56 дешифратора 7, триггер 62 переключается, открывая ключ 64, и от тока разряда 79 обмотка возвращается в исходное состояние.

Таким образом, предложенное устройство обладает более широкими функциональными возможностями, поскольку позволяет оперативно изменять параметры реле путем перестройки параметров дешифраторов и блока управления генератором, а также делителя частоты и генератора тактовых импульсов.

Источники информации

1. Патент РФ 2172038, 1998, кл. Н 01 Н 50/00, 50/18.

2. Электротехнический справочник, в 4-х томах, т.2. Электротехнические изделия и устройства. Под общей редакцией В.Г.Герасимова и др. - М.: Издательство МЭИ, 1998, с.390, рис.35.10 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЕ ВРЕМЕНИ | 2002 |

|

RU2208259C1 |

| РЕЛЕ ВРЕМЕНИ | 2002 |

|

RU2219615C1 |

| РЕЛЕ ПРОМЕЖУТОЧНОЕ | 2002 |

|

RU2208863C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2003 |

|

RU2237312C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2222086C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2231157C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2225653C1 |

| РЕЛЕ ВРЕМЕНИ | 2002 |

|

RU2219612C1 |

| РЕЛЕ ВРЕМЕНИ | 2002 |

|

RU2219613C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2228559C1 |

Использование: в электротехнике для создания реле времени. Реле времени содержит блок питания, блок запуска, два исполнительных блока, генератор тактовых импульсов, управляемый делитель частоты, двоичный счетчик и дешифратор. Технический результат заключается в достижении более широких функциональных возможностей, поскольку устройство позволяет оперативно изменять параметры реле путем перестройки параметров дешифраторов, а также управляемого делителя частоты. 8 з.п.ф-лы, 9 ил.

| ГЕРАСИМОВ В.Г | |||

| и др | |||

| Электротехнический справочник | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электротехнические изделия и устройства | |||

| - М.: МЭИ, 1998, с.390, рис.35.10 | |||

| RU 2001460 C1, 15.10.1993 | |||

| РЕЛЕ ВРЕМЕНИ | 1989 |

|

RU2012942C1 |

| РЕЛЕ ВРЕМЕНИ | 0 |

|

SU235175A1 |

| US 4480194 A1, 30.10.1984. | |||

Авторы

Даты

2003-10-20—Публикация

2002-04-17—Подача