Изобретение относится к специализированным средствам вычислительной техники и служит для вычисления среднего значения и оценки математического ожидания как детерминированных, так и случайных аналоговых сигналов произвольной формы.

Известно устройство, которое может быть использовано как для измерения среднего, так и математического ожидания и содержащее сумматор, три регистра и два элемента сравнения, причем выход первого регистра соединен с первым входом сумматора и первого элемента сравнения, выход “Меньше” которого соединен с входом синхронизации первого регистра, информационный вход которого соединен с информационным входом второго регистра, с вторым входом первого элемента сравнения и первым входом второго элемента сравнения и является информационным входом устройства, выход второго регистра соединен с вторыми входами сумматора, выход “Больше” которого соединен с входом синхронизации второго регистра, выход сумматора соединен с информационным входом третьего регистра, выход которого является выходом устройства, вход разрешения записи первого регистра соединен с входом разрешения записи второго регистра и является тактовым входом устройства, вход синхронизации третьего регистра является входом останова устройства. [А.с. СССР №1336033. Опубл. в БИ, 1987 г., №33].

Недостатком измерителя являются ограниченные функциональные возможности и низкая точность, так как алгоритм измерений, реализуемый этим устройством, основан на вычислении полусуммы максимального и минимального значений из имеющейся выборки заданного объема.

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому вычислителю является вычислитель оценки математического ожидания, содержащий входной блок, аналого-цифровой преобразователь (АЦП), усреднитель и блок управления, первый, второй и третий управляющие входы которого подключены к управляющим входам соответственно входного блока, АЦП и усреднителя, информационным входом вычислителя является информационный вход входного блока, выход которого соединен с информационным входом АЦП, выход которого соединен с информационным входом усреднителя, выход которого является выходом вычислителя [Мирский Г.Я. Электронные измерения. -М.: Радио и связь, 1986 г., стр. 273, рис.8.2].

Вычислитель-прототип реализует классический дискретный метод, состоящий в оцифровывании аналогового сигнала, алгебраическом суммировании полученных отсчетов и затем делении суммы на количество отсчетов. То есть вычисляется среднее арифметическое, которое при достаточно большом объеме выборки стремится к математическому ожиданию. При этом вычислитель не может быть использован в ряде задач, связанных с обработкой знакопеременных процессов. Известно, что при вычислении математического ожидания многих знакопеременных процессов результат оказывается равным нулю, в то время как процесс оказывает реальное действие, результат которого далеко не нулевой. Типичный пример - белый шум или, например, гармонический сигнал, математическое ожидание которого за период равно нулю. В подобных случаях приходится вычислять либо математическое ожидание модуля процесса, либо, в случае с гармоническими сигналами, математическое ожидание полуволны (полуволн одного знака).

Недостатком прототипа являются ограниченные функциональные возможности.

Технический результат, достигаемый при использовании настоящего изобретения, состоит в расширении функциональных возможностей вычислителя за счет вычисления оценок математического ожидания процесса, математического ожидания модуля процесса, а также математического ожидания одновременно положительной и отрицательной составляющих знакопеременного процесса.

Технический результат достигается тем, что в известный вычислитель оценки математического ожидания, содержащий входной блок, АЦП и блок управления, тактовый выход которого подключен к тактовому входу АЦП, информационный вход которого соединен с выходом входного блока, вход которого является информационным входом вычислителя, согласно изобретению введены два сумматора-накопителя, сумматор и три блока деления, причем выход АЦП подключен одновременно к информационным входам первого и второго сумматоров-накопителей, вход первого блока деления объединен с первым информационным входом сумматора и подключен к выходу первого сумматора-накопителя, вход второго блока деления объединен с вторым информационным входом сумматора и подключен к выходу второго сумматора-накопителя, выходы первого и второго блоков деления являются соответственно первым и вторым информационными выходами вычислителя, третьим информационным выходом которого является выход третьего блока деления, вход которого соединен с выходом сумматора, управляющий и обнуляющий входы блока управления являются соответствующими входами вычислителя.

Сущность изобретения поясняется функциональными схемами.

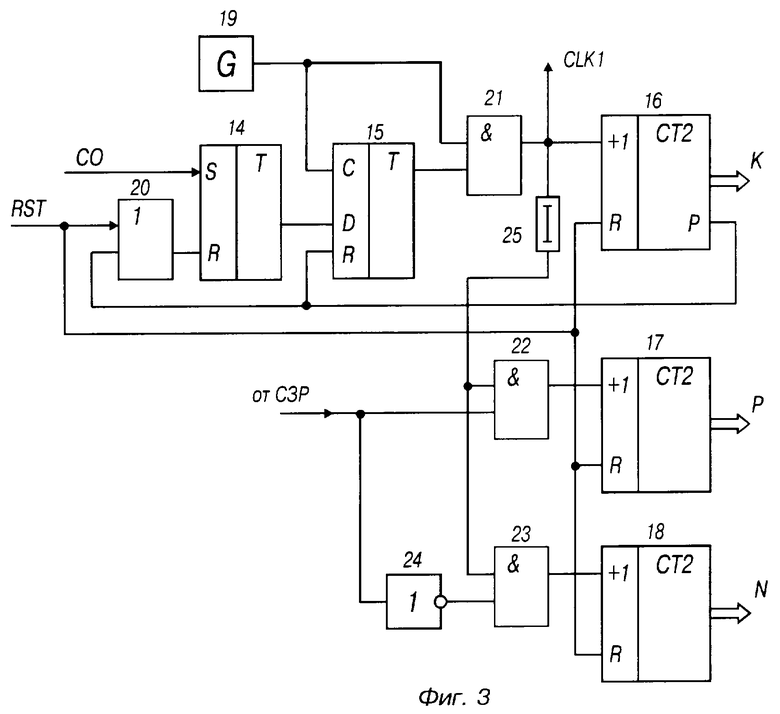

На фиг.1 приведена функциональная схема вычислителя оценки математического ожидания; на фиг.2 - функциональная схема сумматора-накопителя 3 (фиг.2а) и функциональная схема сумматора-накопителя 4 (фиг.2б); на фиг.3 - функциональная схема блока 9 управления.

Функциональная схема вычислителя (фиг.1) содержит входной блок 1, АЦП 2, сумматоры-накопители 3 и 4, сумматор 5, блоки 6, 7, 8 деления и блок 9 управления. Вход входного блока 1 является информационным входом x(f) вычислителя, выход блока 1 соединен с информационным входом АЦП 2, выход которого подключен одновременно к информационным входам сумматоров-накопителей 3 и 4, вход блока 6 деления объединен с первым информационным входом сумматора 5 и подключен к выходу сумматора-накопителя 3, вход блока 7 деления объединен с вторым информационным входом сумматора 5 и подключен к выходу сумматора-накопителя 4, выходы блока 6 деления и блока 7 деления являются соответственно выходами оценки М(х-) положительной составляющей и оценки М(х+) отрицательной составляющей математического ожидания, выход блока 8 деления является выходом оценки математического ожидания М (х), М ( ), вход блока 8 деления соединен с выходом сумматора 5, вход управления SGN (signum) которого является входом выбора режима вычислений, управляющим входом СО вычислителя и входом RST обнуления вычислителя являются соответствующие входы блока 9 управления, тактовый вход CLKI которого подключен к тактовому входу АЦП 2, выходы К, Р и N блока 9 являются соответственно выходами значений делителей К, Р и N (коэффициентов 1/К, 1/Р и 1/N).

), вход блока 8 деления соединен с выходом сумматора 5, вход управления SGN (signum) которого является входом выбора режима вычислений, управляющим входом СО вычислителя и входом RST обнуления вычислителя являются соответствующие входы блока 9 управления, тактовый вход CLKI которого подключен к тактовому входу АЦП 2, выходы К, Р и N блока 9 являются соответственно выходами значений делителей К, Р и N (коэффициентов 1/К, 1/Р и 1/N).

Функциональная схема сумматора-накопителя 3 положительных значений (фиг.2а) содержит сумматор 10, регистр 11 и элемент 2И 12, выход которого соединен с тактовым входом регистра 11, вход параллельной записи информации которого соединен с выходом сумматора 10, первый вход которого является входом сумматора-накопителя 3, а второй вход соединен с выходом регистра 11, выход которого является еще и выходом сумматора-накопителя 3, первый вход элемента 2И является входом старшего значащего разряда (СЗР) сумматора-накопителя 3, тактовым входом CLK2 которого является второй вход элемента 2И 12, этот же вход является входом сигнала готовности данных.

Функциональная схема сумматора-накопителя 4 отрицательных значений (фиг.26) содержит сумматор 10-1, регистр 11-1, элемент 2И 12-1 и инвертор 13, выход которого соединен с первым входом элемента 2И 12-1, выход которого соединен с тактовым входом регистра 11-1, вход параллельной записи информации которого соединен с выходом сумматора 10-1, первый вход которого является входом сумматора-накопителя 4, а второй вход соединен с выходом регистра 11-1, выход которого является еще и выходом сумматора-накопителя 4, тактовым входом CLK2 которого является второй вход элемента 2И 12-1, а входом СЗР сумматора-накопителя 4 является вход инвертора 13.

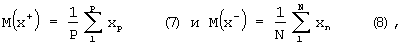

Блок управления по фиг.3 содержит триггеры 14, 15, счетчики 16, 17, 18, генератор 19 тактовых импульсов, элемент 2ИЛИ 20, элементы 2И 21, 22, 23, инвертор 24 и элемент 25 задержки, управляющим входом СО блока 9 является S-вход триггера 14, выход которого соединен с D-входом триггера 15, тактовый вход которого объединен с первым входом элемента 2И 21 и подключен к выходу генератора 19, второй вход элемента 2И 21 соединен с выходом триггера 15, обнуляющий вход которого объединен с первым входом элемента 2ИЛИ 20 и подключен к выходу переполнения счетчика 16, суммирующий вход которого соединен с выходом элемента 2И 21, выход элемента 2ИЛИ 20 соединен с R-входом триггера 14, первые входы элементов 2И 22 и 23 объединены и подключены через элемент 25 к выходу элемента 2И 21, выход элемента 2И 22 подключен к суммирующему входу счетчика 17, а выход элемента 2И 22 к суммирующему входу счетчика 18, обнуляющие входы счетчиков 16, 17, 18 и второй вход элемента 2ИЛИ 20 объединены и представляют собой обнуляющий вход блока 9, тактовым выходом CLK1 которого является выход элемента 2И 21, входом СЗР блока 9 управления являются объединенные вход инвертора 24 и второй вход элемента 2И 22, выход инвертора 24 соединен с вторым входом элемента 2И 23, выходы счетчиков 16, 17 и 18 являются выходами соответственно значений К, Р и N блока 9 управления.

Вычислитель (фиг.1) функционирует следующим образом.

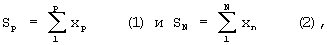

Процесс x(t), который может быть как знакопеременным, так и знакопостоянным, поступает через входной блок 1 на вход АЦП 2. Будем далее считать, что исследуемый процесс x(t) знакопеременный. С выхода АЦП 2 оцифрованные значения x(t) в виде двоичного кода поступают одновременно в два канала: в сумматор-накопитель 3 и сумматор-накопитель 4. При этом сумматор накопитель 3 суммирует только положительные значения отсчетов х(t), а сумматор-накопитель 4 только отрицательные. В результате к концу интервала наблюдения, который задается блоком 9 управления и состоит из К отсчетов, в сумматорах-накопителях 3 и 4 соответственно будут накоплены суммы:

где xр - положительные отсчеты;

xn - отрицательные отсчеты;

Р - общее число положительных отсчетов;

N - общее число отрицательных отсчетов.

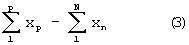

Полученные значения сумм (1) и (2) направляются в сумматор 5, где они могут как складываться, так и вычитаться в зависимости от состояния входа SGN. Допустим, при SGN=1 происходит вычитание. Тогда поступившая на вход блока 8 деления разность

будет представлять собой не что иное, как результат суммирования всех К отсчетов с учетом их знака, причем К=Р+N. Следовательно, после деления в блоке 8 на величину К получим оценку математического ожидания М(х) процесса x(t):

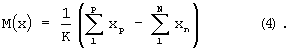

Положим, далее, что при SGN=0 в сумматоре 5 происходит сложение операндов (1) и (2). На его выходе после сложения получим величину

которая представляет собой сумму модулей всех значений процесса x(t) за время наблюдения, так как отрицательная компонента (2) берется с положительным знаком. Несложно понять, что после деления суммы (5) на общее количество отсчетов К будет получена оценка математического ожидания модуля процесса х(t):

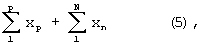

Учитывая, что к окончанию интервала наблюдения на выходах сумматоров-накопителей 3 и 4 фиксируются суммы положительной составляющей Sp процесса и отрицательной составляющей SN процесса x(t), то после деления их в блоках 6 и 7 соответственно на Р и N получим следующие оценки:

где М (x+) представляет собой оценку математического ожидания положительной составляющей процесса x(t), а М (х-) - отрицательной составляющей.

Как видим, описанным выше образом при помощи представленной структуры (фиг.1) можно получить оценки четырех параметров М(х), М( ), М(х+) и М(х-). Последние два параметра позволяют в некоторой степени вскрыть структуру случайного процесса, группируя отсчеты по их знаку. Сравнение полученных таким образом математических ожиданий М(х+) и М(х-), например, путем взятия их отношения, может дать информацию о соотношении весов положительной и отрицательной составляющих исследуемого сигнала, что весьма полезно, например, при решении задач, связанных с контролем прохождения случайных сигналов по нелинейным цепям.

), М(х+) и М(х-). Последние два параметра позволяют в некоторой степени вскрыть структуру случайного процесса, группируя отсчеты по их знаку. Сравнение полученных таким образом математических ожиданий М(х+) и М(х-), например, путем взятия их отношения, может дать информацию о соотношении весов положительной и отрицательной составляющих исследуемого сигнала, что весьма полезно, например, при решении задач, связанных с контролем прохождения случайных сигналов по нелинейным цепям.

Рассмотрим далее аппаратурные особенности выделения знака оцифрованных значений процесса x(t).

При включении АЦП с параллельным выводом данных в биполярном режиме положительные значения отсчетов всегда сопровождаются логическими единицами на СЭР выходной шины, а отрицательные значения - логическим нулем. В сумматорах-накопителях 3 и 4 (фиг.2) информация, снимаемая с СЗР, используется для разрешения их работы. В сумматоре-накопителе положительных значений (фиг.2а) тактирование регистра 11 возможно только при СЗР=1, в сумматоре-накопителе отрицательных значений (фиг.2б), напротив, тактирование регистра 11-1 возможно только при СЗР=0. Таким образом поступающие по единой информационной шине данные в сумматорах-накопителях 3, 4 автоматически дифференцируются по знаку. Тактирование регистров 11 и 11-1 осуществляется тактовыми импульсами CLK2, время появления которых определяется моментами формирования новых кодовых значений на выходе АЦП 2. В зависимости от типа применяемого АЦП возможны два варианта тактирования упомянутых регистров. Если используется АЦП параллельного типа, то в качестве последовательности CLK2 можно использовать сдвинутую во времени на величину, определяемую быстродействием АЦП, последовательность CLK1. Если же в качестве АЦП 2 используется, например, преобразователь последовательных приближений, у которого цикл преобразования происходит за несколько тактов, то управление записью в регистры 11 и 11-1 можно осуществлять импульсами готовности данных, выдаваемых АЦП подобного типа.

Блок 9 управления (фиг.3) служит для отсчета длительности интервала наблюдения и подсчета количества отсчетов в выборках. Работает он следующим образом.

Перед началом работы блок 9 обнуляют подачей на вход RST импульса обнуления, после чего подают запускающий импульс на вход СО. Триггер 15 переходит в связи с указанным и по фронту тактового импульса в состояние логической единицы, разрешая тем самым прохождение тактовых импульсов на выход элемента 2И 21 (на выход CLK1) и через элемент 25 задержки на входы элементов 2И 22 и 23. Таким образом начинается тактирование АЦП 2 и отсчет интервала наблюдения. Длительность интервала наблюдения задается коэффициентом пересчета счетчика 16, по импульсу переполнения которого триггеры 14 и 15 переходят в состояние низкого логического уровня и подача тактовых импульсов CLK1 на тактовый вход АЦП 2 прекращается. В течение всего интервала наблюдения, состоящего из K отсчетов, счетчики 17 и 18 подсчитывают количество положительных Р и отрицательных N отсчетов соответственно. Подсчет ведется по числу единиц и нулей, возникающих на СЭР АЦП 2, а тактирование счетчиков 17 и 18 происходит последовательностью CLK1, задержанной на время, определяемое быстродействием АЦП 2. Так, например, если информация в цифровом коде появляется через время tnp после воздействия фронта тактового импульса, по которому происходит взятие отсчета (выборки), соответствующего этому цифровому коду, то время задержки в элементе 25 должно составлять примерно (1,1-1,3) tnp. Это верно для АЦП параллельного действия. В случае с АЦП последовательного приближения функциональная схема блока 9 несколько изменяется (такой вариант в материалах заявки не представлен), в частности, вместо задержанной последовательности CLK1 следует использовать импульсы готовности данных с выхода АЦП. Кроме этого подсчет общего количества отсчетов К в выборке целесообразно также вести по общему количеству импульсов готовности.

По окончании интервала наблюдения на выходах счетчиков 16, 17 и 18 фиксируются двоичные коды величин К, Р и N соответственно. Полученные значения используются для усреднения результатов наблюдения как делители в блоках 8, 6, 7 деления соответственно. Относительно упомянутых блоков деления отметим, что коэффициент деления блока 8 может быть постоянным, если длительность интервала наблюдения, задаваемая счетчиком 16, предполагается неизменной. Коэффициенты же деления p и n, блоков 6 и 7 должны быть величинами переменными, конкретные значения которых Р=р и N=n, определяются с окончанием интервала наблюдения.

Входной блок 1 в заявляемом вычислителе служит для масштабирования амплитуды процесса путем его ослабления или усиления для того, чтобы он находился в диапазоне входных значений выбранного АЦП. Схемотехнически входной блок может быть выполнен в виде управляемого делителя напряжения, усилителя с регулируемым выходным напряжением или их комбинации.

Изобретение относится к вычислительной технике и служит для вычисления среднего значения и оценки математического ожидания как детерминированных, так и случайных аналоговых сигналов произвольной формы. Техническим результатом является обеспечение возможности вычисления математического ожидания модуля процесса, а также математического ожидания одновременно положительной и отрицательной составляющей знакопеременного процесса. Для этого вычислитель содержит входной блок, аналого-цифровой преобразователь, два сумматора-накопителя, сумматор, три блока деления и блок управления. 4 ил.

Вычислитель оценки математического ожидания, содержащий входной блок, АЦП и блок управления, тактовый выход которого подключен к тактовому входу АЦП, информационный вход которого соединен с выходом входного блока, вход которого является информационным входом вычислителя, отличающийся тем, что введены два сумматора-накопителя, сумматор и три блока деления, при этом блок управления предназначен для отсчета длительности интервала наблюдения и подсчета количества положительных и отрицательных отсчетов, первый сумматор-накопитель предназначен для суммирования значений положительных отсчетов, а второй сумматор-накопитель предназначен для суммирования значений отрицательных отсчетов, выход АЦП подключен одновременно к информационным входам первого и второго сумматоров-накопителей, вход первого блока деления объединен с первым информационным входом сумматора и подключен к выходу первого сумматора-накопителя, вход второго блока деления объединен с вторым информационным входом сумматора и подключен к выходу второго сумматора-накопителя, выходы первого и второго блоков деления являются соответственно первым и вторым информационными выходами вычислителя, третьим информационным выходом которого является выход третьего блока деления, вход которого соединен с выходом сумматора, управляющий и обнуляющий входы блока управления являются соответствующими входами вычислителя, при этом значения количества положительных отсчетов, значения количества отрицательных отсчетов и значения общего количества отсчетов на интервале наблюдения, полученные на выходах блока управления, используются соответственно в качестве делителей в первом, втором и третьем блоках деления, при этом блок управления осуществляет подсчет количества положительных и отрицательных отсчетов по числу единиц и нулей, возникающих на старшем значащем разряде АЦП.

| МИРСКИЙ Г.Я | |||

| Электронные измерения | |||

| - М.: Радио и связь, 1986, с.273, рис.8.2.RU 2133499 С1, 20.07.1999.SU 1336033 А1, 07.08.1987.RU 21065620 С1, 20.08.1996.US 6434511 А, 13.08.2002.JP 2001005803 А, 12.01.2001. |

Авторы

Даты

2004-05-20—Публикация

2002-10-11—Подача