Изобретение относится к электротехнике и может быть использовано в качестве реле синхронизации, обеспечивающего автоматизацию процесса включения синхронного генератора.

Известно устройство, содержащее последовательно соединенные генератор тактовых импульсов, двоичный счетчик, дешифратор, формирователь импульсов и исполнительный элемент, выполненный в виде транзистора [1].

Недостатком устройства является относительно узкие функциональные возможности, не позволяющие использовать его в качестве реле разности частот.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее первый и второй выпрямительные блоки, выполняющие функции измерителя амплитуды напряжения, выполненные в виде диодов, катод и анод которых являются соответственно клеммой напряжения генератора и клеммой напряжения сети, алгебраический сумматор, первый и второй входы которого соединены соответственно с анодом первого и с катодом второго диодов, первый и второй операционные усилители, являющиеся соответственно инвертором и компаратором, входы которых соединены с выходом алгебраического сумматора, третий и четвертый диоды, аноды которых соединены с выходами первого и второго операционных усилителей соответственно, умножитель, входы которых соединены с катодами третьего и четвертого диодов, первый и второй инверторы, входы которых соединены соответственно с катодами третьего и четвертого диодов, и первый и второй исполнительные элементы, входы которых соединены соответственно с выходом первого и второго операционных усилителей [2].

Недостатком наиболее близкого технического решения являются относительно узкие функциональные возможности, поскольку оно вырабатывает сигнал примерного равенства амплитуды напряжений сети и генератора, что указывает на временной интервал возможной подстройки частоты генератора к частоте сети, но не вырабатывает сигналов недопустимого рассогласования частот входного и синхронизируемого сигналов при заданной относительной допустимой величине их рассогласования, а также не формирует сигнала опережения, используемого для точного согласованного по фазе включения генератора в сеть.

Техническим результатом изобретения является расширение функциональных возможностей и повышение точности.

Этот технический результат достигается тем, что в устройство, содержащее выпрямитель входного напряжения, вход которого соединен с входом напряжения сети, выпрямитель синхронизируемого напряжения, вход которого соединен с входом напряжения генератора, первый алгебраический сумматор, первый умножитель на постоянный коэффициент, первый инвертор, первый компаратор и первый и второй исполнительные элементы, введены измеритель частоты входного напряжения, вход которого соединен с входом выпрямителя входного напряжения, а выход соединен с входом сложения первого алгебраического сумматора и с входом первого умножителя на постоянный коэффициент, выход которого через первый инвертор соединен с первым входом первого компаратора, измеритель частоты синхронизируемого напряжения, вход которого соединен с входом выпрямителя синхронизируемого напряжения, а выход соединен с входом вычитания первого алгебраического сумматора, второй компаратор, первый вход которого соединен с выходом первого умножителя на постоянный коэффициент, а второй вход соединен со вторым входом первого компаратора и с выходом первого алгебраического сумматора, первый элемент И, первый вход которого соединен с выходом “больше” первого компаратора, а выход соединен с входом первого исполнительного элемента, второй элемент И, первый вход которого соединен с выходом “меньше” второго компаратора, а выход соединен с входом второго исполнительного элемента, третий элемент И, выход которого соединен со вторыми входами первого и второго элементов И, третий компаратор, выход “больше” которого соединен с первым входом третьего элемента И, четвертый компаратор, выход “меньше” которого соединен со вторым входом третьего элемента И, второй алгебраический сумматор, вход вычитания и вход сложения которого соединен с выходом выпрямителя синхронизируемого напряжения и с выходом выпрямителя входного напряжения соответственно, второй умножитель на постоянный коэффициент, вход которого соединен с выходом выпрямителя входного напряжения, а выход соединен с первым входом четвертого компаратора, второй инвертор, вход которого соединен с выходом второго умножителя, а выход соединен с первым входом третьего компаратора, второй вход которого соединен со вторым входом четвертого компаратора и с выходом второго алгебраического сумматора, последовательно соединенные первый формирователь прямоугольных импульсов, вход которого соединен с входом выпрямителя синхронизируемого напряжения, и формирователь последовательности коротких импульсов, выход которого соединен с первым входом фазового детектора, последовательно соединенные второй формирователь прямоугольных импульсов, вход которого соединен с входом выпрямителя входного напряжения, и интегрирующий усилитель, выход которого соединен со вторым входом фазового детектора, пятый компаратор, фильтр нижних частот, вход которого соединен с выходом фазового детектора, а выход соединен с входом пятого компаратора, выполненного в виде компаратора с нулевым порогом, четвертый элемент И, первый и второй входы которого соединены с выходом “меньше” первого компаратора и с выходом “больше” второго компаратора соответственно, последовательно соединенные генератор тактовых импульсов, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом “больше” пятого компаратора, а третий вход соединен с выходом четвертого элемента И, первый и второй элементы задержки, входы которых соединены с выходом “равно” пятого компаратора, последовательно соединенные первый счетчик импульсов, счетный вход которого соединен с выходом пятого элемента И, а вход установки в ноль - с выходом первого элемента задержки, регистр памяти, управляющий вход которого соединен с выходом “равно” пятого компаратора, и третий умножитель на постоянный коэффициент, а также второй счетчик импульсов, счетный вход которого соединен с выходом пятого элемента И, вход подачи кода начальной установки соединен с выходом третьего умножителя на постоянный коэффициент, управляющий вход второго счетчика импульсов соединен с выходом второго элемента задержки, а вход установки в ноль - с выходом “равно” пятого компаратора, и блок формирования постоянного коэффициента, вход которого соединен с выходом “равно” пятого компаратора, а выход соединен с входом подачи постоянного коэффициента третьего умножителя на постоянный коэффициент, при этом измерители частоты входного и синхронизируемых сигналов преобразуют входной и синхронизируемый сигналы в соответствии с математическими выражениями

U0=A0/f0, U1=A1/f1,

где U0 - сигнал на выходе измерителя частоты входного сети,

U1 - сигнал на выходе измерителя частоты синхронизируемого напряжения,

f0 - частота входного напряжения,

f1 - частота синхронизируемого напряжения,

А0, А1 - масштабные коэффициенты, пропорциональные амплитудам входного и синхронизируемого напряжения соответственно, выпрямители входного напряжения и синхронизируемого напряжения преобразуют напряжения в величины, пропорциональные их амплитудам и равные А0 и А1 соответственно, а выход второго счетчика является выходом реле синхронизации.

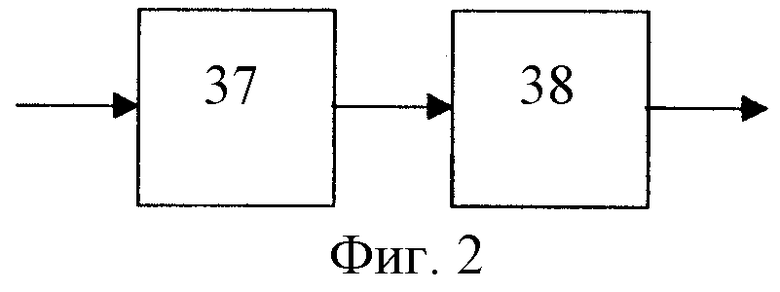

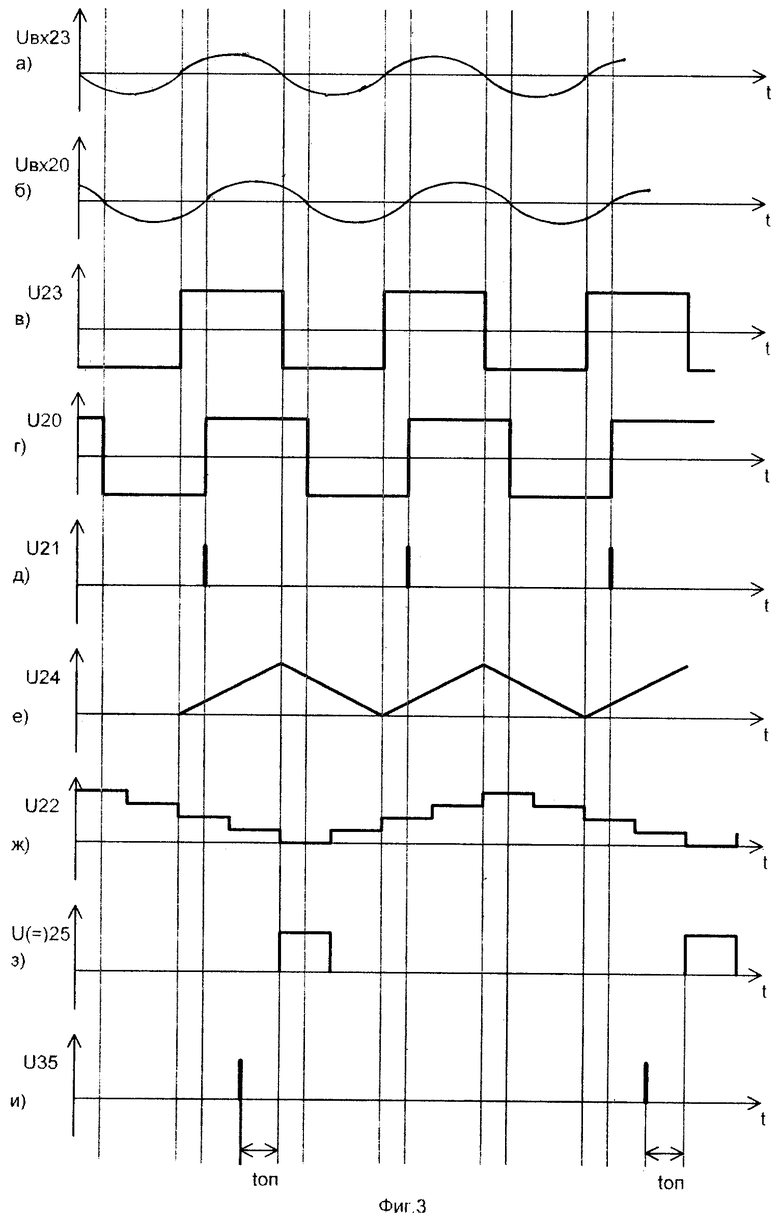

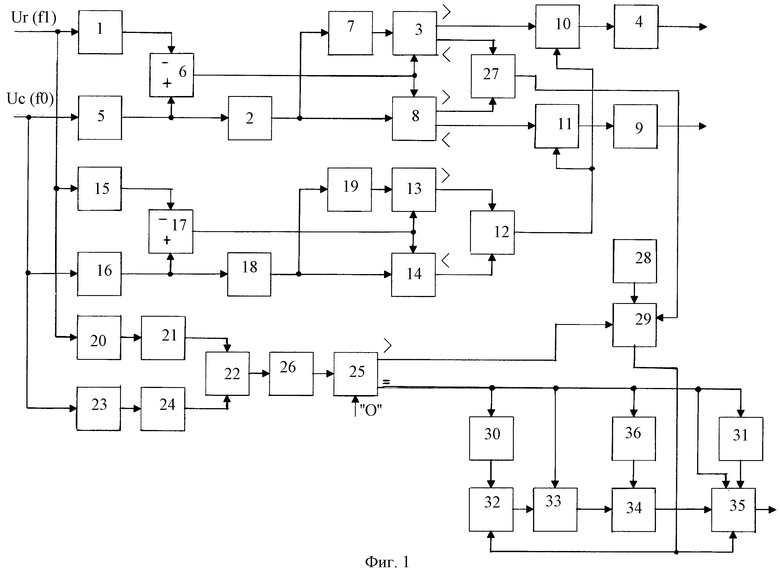

На фиг.1 представлена электрическая структурная схема реле синхронизации; на фиг.2 - то же, измерителей частоты, на фиг.3 - временные диаграммы, поясняющие работу реле синхронизации.

Реле синхронизации содержит измеритель 1 частоты синхронизируемого напряжения, первый умножитель 2 на постоянный коэффициент, первый компаратор 3, первый исполнительный элемент 4, измеритель 5 частоты входного напряжения, выход которого соединен с входом сложения алгебраического сумматора 6, вход вычитания которого соединен с выходом измерителя 1 частоты синхронизируемого напряжения, первый инвертор 7, вход которого соединен с выходом первого умножителя 2 на постоянный коэффициент, а выход соединен с первым входом первого компаратора 3, второй компаратор 8, первый вход которого соединен с выходом первого умножителя, а второй вход соединен с выходом алгебраического сумматора 6 и со вторым входом первого компаратора 3, второй исполнительный элемент 9, первый элемент И 10, первый вход которого соединен с выходом “больше” первого компаратора 3, а выход соединен с входом первого исполнительного элемента 4, второй элемент И 11, первый вход которого соединен с выходом “меньше” второго компаратора 8, а выход соединен с входом второго исполнительного элемента 9. Устройство содержит третий элемент И 12, выход которого соединен со вторыми входами первого 10 и второго 11 элементов И, третий компаратор 13, выход “больше” которого соединен с первым входом третьего элемента И 12, четвертый компаратор 14, выход “меньше” которого соединен со вторым входом третьего элемента И 12, выпрямитель 15 синхронизируемого напряжения, вход которого соединен с входом измерителя частоты синхронизируемого напряжения, выпрямитель 16 входного напряжения, вход которого соединен с входом измерителя частоты входного напряжения, второй алгебраический сумматор 17, вход вычитания и вход сложения которого соединен с выходами выпрямителя 15 синхронизируемого напряжения и с выходом выпрямителя 16 входного напряжения соответственно. В состав реле входят также второй умножитель 18 на постоянный коэффициент, вход которого соединен с выходом выпрямителя 16 входного напряжения, а выход соединен с первым входом четвертого компаратора 14, второй инвертор 19, вход которого соединен с выходом второго умножителя 18 на постоянный коэффициент, а выход соединен с первым входом третьего компаратора 13, второй вход которого соединен со вторым входом четвертого компаратора 14 и с выходом второго алгебраического сумматора 17, последовательно соединенные первый формирователь 20 прямоугольных импульсов, вход которого соединен с входом выпрямителя 15 синхронизируемого напряжения, формирователь 21 последовательности коротких импульсов и фазовый детектор 22, последовательно соединенные второй формирователь 23 прямоугольных импульсов, вход которого соединен с входом выпрямителя 16 входного напряжения, и интегрирующий усилитель 24, выход которого соединен со вторым входом фазового детектора 22. Устройство также содержит пятый компаратор 25, фильтр 26 нижних частот, вход которого соединен с выходом фазового детектора 22, а выход соединен с входом пятого компаратора 25, выполненного в виде компаратора с нулевым порогом, четвертый элемент И 27, первый и второй входы которого соединены с выходом “меньше” первого компаратора 3 и с выходом “больше” второго компаратора 8 соответственно, последовательно соединенные генератор 28 тактовых импульсов и пятый элемент И 29, второй вход которого соединен с выходом “больше” пятого компаратора 25, а третий вход соединен с выходом четвертого элемента И 27, первый 30 и второй 31 элементы задержки, входы которых соединены с выходом “равно” пятого компаратора 25, последовательно соединенные первый счетчик 32 импульсов, счетный вход которого соединен с выходом пятого элемента И 29, а вход установки в ноль - с выходом первого элемента задержки 30, регистр 33 памяти, управляющий вход которого соединен с выходом “равно” пятого компаратора 25, и третий умножитель 34 на постоянный коэффициент, а также второй счетчик 35 импульсов, счетный вход которого соединен с выходом пятого элемента И 29, вход подачи кода начальной установки соединен с выходом третьего умножителя 34 на постоянный коэффициент, управляющий вход соединен с выходом второго элемента задержки 32, вход установки в ноль второго счетчика 35 импульсов соединен с выходом “равно” пятого компаратора 25, а выход является выходом реле синхронизации, и блок 36 формирования постоянного коэффициента, вход которого соединен с управляющим входом регистра 33 памяти, а выход соединен с входом подачи постоянного коэффициента третьего умножителя 34 на постоянный коэффициент, при этом измерители частоты входного 5 и синхронизируемого 1 сигналов преобразуют входной и синхронизируемый сигналы в соответствии с математическими выражениями

U0=A0/f0, U1=A1/f1,

где U0 - сигнал на выходе измерителя частоты входного напряжения;

U1 - сигнал на выходе измерителя частоты синхронизируемого напряжения;

f0 - частота входного напряжения;

f1 - частота синхронизируемого напряжения;

А0, А1 - масштабные коэффициенты, пропорциональные амплитудам входного и синхронизируемого напряжений соответственно, а выпрямитель 16 входного напряжения и выпрямитель 15 синхронизируемого напряжения преобразуют напряжения в величины, пропорциональные их амплитудам и равные А0 и А1 соответственно.

Измерители 1 и 5 частоты (фиг.2) могут быть выполнены в виде усилителя 37, в выходной цепи которого включен резонансный контур 38, настроенный таким образом, чтобы номинальные значения входных частот приходили на середину линейной части ветви (спада) его частотной характеристики. В этом случае выходное напряжение измерителя будет обратно пропорционально частоте его входного сигнала.

На фиг.3 представлены сигнал Uвх23 на входе второго формирователя 23 прямоугольных импульсов (фиг.3, а), сигнал Uвх20 на входе первого формирователя 20 прямоугольных импульсов (фиг.3, б), сигнал U23 на выходе второго формирователя 23 прямоугольных импульсов (фиг.3, в), сигнал U20 на выходе первого формирователя 20 прямоугольных импульсов (фиг.3, г), сигнал U21 на выходе формирователя 21 последовательности коротких импульсов (фиг.3, д), сигнал U24 на выходе интегрирующего усилителя 24 (фиг.3, е), сигнал U22 на выходе фазового детектора 22 (фиг.3, ж), сигнал U25 на выходе “равно” пятого компаратора 25 (фиг.3, з), сигнал U35 на выходе второго счетчика 35 (фиг.3, и).

Работает реле синхронизации следующим образом.

При включении реле на выходе измерителя 5 формируется сигнал U0=A0/f0, величина которого обратно пропорциональна частоте f0 входного напряжения (напряжения сети), а на выходе измерителя 1 - сигнал U1=A1/f1, обратно пропорциональный частоте f1 синхронизируемого напряжения (напряжения генератора). Одновременно с этим выпрямитель 16 вырабатывает сигнал, пропорциональный А0, а выпрямитель 15 формирует сигнал, пропорциональный А1. В этом случае на выходе второго алгебраического сумматора 17 формируется величина разности амплитуд напряжений А0-А1. Кроме того, сигнал с выхода выпрямителя 16 А0 умножается во втором умножителе 18 на малый коэффициент Кu, определяющий допустимое отклонение амплитуды синхронизируемого напряжения от входного. Поэтому в третьем компараторе 13 сравниваются величины А0-А1 и А0Кu, а в четвертом компараторе 14 сравниваются величины А0-А1 и А0Кu. Если выполняется условие А0-А1<A0Ku, A0-А1>-А0Кu, что соответствует нахождению разности амплитуд входного и синхронизируемого напряжений в допустимых пределах, то на выходе третьего элемента И 12 будет сформирован сигнал логической единицы, что откроет первый 10 и второй 11 элементы И и позволит управлять первым 4 и вторым 9 исполнительными элементами. Следовательно, управление частотой синхронизируемого сигнала будет происходить только при рассогласовании амплитуд входного и синхронизируемого напряжений в допустимых пределах, что повышает точность подстройки частоты синхронизируемого сигнала (напряжения генератора).

Кроме того, сигнал с выхода измерителя 5 умножается в первом умножителе 2 на малый коэффициент Kf, определяющий допустимое отклонение частоты синхронизируемого сигнала от входного. Тогда с учетом того, что Al≅A0, в первом компараторе 3 сравниваются величины А0(f1-f0)/f

Первый исполнительный элемент 4 сработает, когда частота напряжения генератора f1 превысит допустимое отклонение от частоты напряжения сети f0 в большую сторону на относительную величину, задаваемую коэффициентом Kf, а второй исполнительный элемент 9 - когда частота напряжения генератора недопустимо отклонится в меньшую сторону.

Сигнал логической единицы на выходе четвертого элемента И 27, соответствующий разрешению формирования команды подключения генератора в сеть, будет наблюдаться при нахождении частоты генератора в допустимых пределах относительно отклонении от частоты напряжения сети.

Сама команда подключения, которая должна вырабатываться с заданным временем опережения tоп, формируется следующим образом. Сигнал логической единицы с выхода четвертого элемента И 27 поступает на вход пятого элемента И 29, на один из других входов которого поступают счетные импульсы для первого счетчика 32 с выхода генератора 28 тактовых импульсов. На выходе фазового детектора 22 формируется сигнал постоянного напряжения, амплитуда которого пропорциональна углу между векторами напряжений генератора и сети (фиг.3, ж). Этот сигнал после фильтрации в фильтре 26 нижних частот сравнивается в пятом компараторе 25 с нулевым уровнем, поэтому на его выходе “равно” будут формироваться импульсы (фиг.3, з) в конце каждого периода изменений сигнала на выходе фазового детектор 22. Между этими импульсами на выходе “больше” пятого компаратора 25 будет наблюдаться уровень логической единицы, по которому импульсы генератора 28 будут поступать на счетный вход первого счетчика 32, в котором будет формироваться сигнал, пропорциональный периоду Т выходного сигнала на выходе фазового детектора 22. Одновременно те же импульсы поступают на счетный вход второго счетчика 35. По сигналу с выхода “равно” пятого компаратора 25 содержимое первого счетчика 32 (величина Т) будет переписываться в регистр 33 памяти, после чего содержимое первого счетчика 32 будет обнуляться. Содержимое регистра 33 умножается в третьем умножителе 34 на число Коп, значение которого определяется в блоке 36, выполненного, например, в виде ПЗУ, на основе заданного заранее времени опережения tоп на включение генератора в сеть. Блок 36 программируется для вычисления Коп на основе следующего уравнения: Коп=(1-tоп/T). При этом по импульсу с выхода “равно” пятого компаратора 25 обнуляется содержимое второго счетчика 35, после чего результат перемножения вводится в этот счетчик в качестве его первоначальной установки. При подсчитанном числе импульсов во втором счетчике 35, равном длительности интервала времени в пределах периода изменений сигнала на выходе фазового детектора 22, на выходе второго счетчика 35 формируется короткий импульс переполнения, который используется в качестве импульса запуска генератора с опережением на величину tоп.

Таким образом, предложенное устройство обладает более широкими функциональными возможностями и более высокой точностью, поскольку оно вырабатывает сигнал на включение генератора только в интервале, соответствующем допустимой величине рассогласования частот напряжений сети и генератора, которая определяется при примерном равенстве их амплитуд.

Источники информации

[1] Электротехнический справочник, в 4-х томах, т.2. Электротехнические изделия и устройства. Под общей ред. В.Г.Герасимова и др. - М.: Издательство МЭИ, 1998 г., с.390, рис. 35.10.

[2] Андреев В.А. Релейная защита и автоматика систем электроснабжения. - М.: Высшая школа, 1991, с. 355, рис. 12.16.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЕ СИНХРОНИЗАЦИИ | 2003 |

|

RU2231849C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2228559C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2231157C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2225653C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2231851C2 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2216812C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2004 |

|

RU2269837C1 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2003 |

|

RU2231852C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2222086C1 |

| РЕЛЕ РАЗНОСТИ ЧАСТОТ | 2002 |

|

RU2208869C1 |

Изобретение относится к электротехнике и может быть использовано в качестве реле синхронизации, обеспечивающего автоматизацию процесса включения синхронного генератора. Технический результат заключается в расширении функциональных возможностей. Для этого устройство содержит выпрямитель входного напряжения, вход которого соединен с входом напряжения сети, выпрямитель синхронизируемого напряжения, вход которого соединен с входом напряжения генератора, первый и второй алгебраические сумматоры, первый, второй и третий умножители на постоянный коэффициент, первый и второй инверторы, с первого по пятый компараторы, при этом пятый компаратор выполнен в виде компаратора с нулевым порогом, и первый и второй исполнительные элементы, измеритель частоты входного напряжения, измеритель частоты синхронизируемого напряжения, с первого по пятый элементы И, первый и второй формирователи прямоугольных импульсов, формирователь последовательности коротких импульсов, фазовый детектор, интегрирующий усилитель, фильтр нижних частот, генератор тактовых импульсов, первый и второй элементы задержки, первый и второй счетчики импульсов, регистр памяти, блок формирования постоянного коэффициента, при этом измерители частоты входного и синхронизируемых сигналов преобразуют входной и синхронизируемый сигналы в соответствии с математическими выражениями:

U0=A0/f0, U1=A1/f1,

где U0 - сигнал на выходе измерителя частоты входного напряжения;

U1 - сигнал на выходе измерителя частоты синхронизируемого напряжения;

f0 - частота входного напряжения;

f1 - частота синхронизируемого напряжения;

А0, А1 - масштабные коэффициенты, пропорциональные амплитудам входного и синхронизируемого напряжения соответственно, выпрямители входного напряжения и синхронизируемого напряжения преобразуют напряжения в величины, пропорциональные их амплитудам и равные А0 и A1 соответственно, а выход второго счетчика импульсов является выходом реле синхронизации. 3 ил.

Реле синхронизации, содержащее выпрямитель входного напряжения, вход которого соединен с входом напряжения сети, выпрямитель синхронизируемого напряжения, вход которого соединен с входом напряжения генератора, первый алгебраический сумматор, первый умножитель на постоянный коэффициент, первый инвертор, первый компаратор и первый и второй исполнительные элементы, отличающееся тем, что введены измеритель частоты входного напряжения, вход которого соединен с входом выпрямителя входного напряжения, а выход соединен с входом сложения первого алгебраического сумматора и с входом первого умножителя на постоянный коэффициент, выход которого через первый инвертор соединен с первым входом первого компаратора, измеритель частоты синхронизируемого напряжения, вход которого соединен с входом выпрямителя синхронизируемого напряжения, а выход соединен с входом вычитания первого алгебраического сумматора, второй компаратор, первый вход которого соединен с выходом первого умножителя на постоянный коэффициент, а второй вход соединен со вторым входом первого компаратора и с выходом первого алгебраического сумматора, первый элемент И, первый вход которого соединен с выходом “больше” первого компаратора, а выход соединен с входом первого исполнительного элемента, второй элемент И, первый вход которого соединен с выходом “меньше” второго компаратора, а выход соединен с входом второго исполнительного элемента, третий элемент И, выход которого соединен со вторыми входами первого и второго элементов И, третий компаратор, выход “больше” которого соединен с первым входом третьего элемента И, четвертый компаратор, выход “меньше” которого соединен со вторым входом третьего элемента И, второй алгебраический сумматор, вход вычитания и вход сложения которого соединен с выходом выпрямителя синхронизируемого напряжения и с выходом выпрямителя входного напряжения, соответственно, второй умножитель на постоянный коэффициент, вход которого соединен с выходом выпрямителя входного напряжения, а выход соединен с первым входом четвертого компаратора, второй инвертор, вход которого соединен с выходом второго умножителя на постоянный коэффициент, а выход соединен с первым входом третьего компаратора, второй вход которого соединен со вторым входом четвертого компаратора и с выходом второго алгебраического сумматора, последовательно соединенные первый формирователь прямоугольных импульсов, вход которого соединен с входом выпрямителя синхронизируемого напряжения, и формирователь последовательности коротких импульсов, выход которого соединен с первым входом фазового детектора, последовательно соединенные второй формирователь прямоугольных импульсов, вход которого соединен с входом выпрямителя входного напряжения, и интегрирующий усилитель, выход которого соединен со вторым входом фазового детектора, пятый компаратор, фильтр нижних частот, вход которого соединен с выходом фазового детектора, а выход соединен с входом пятого компаратора, выполненного в виде компаратора с нулевым порогом, четвертый элемент И, первый и второй входы которого соединены с выходом “меньше” первого компаратора и с выходом “больше” второго компаратора, соответственно, генератор тактовых импульсов, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом “больше” пятого компаратора, а третий вход соединен с выходом четвертого элемента И, первый и второй элементы задержки, входы которых соединены с выходом “равно” пятого компаратора, последовательно соединенные первый счетчик импульсов, счетный вход которого соединен с выходом пятого элемента И, а вход установки в ноль - с выходом первого элемента задержки, регистр памяти, управляющий вход которого соединен с выходом “равно” пятого компаратора, и третий умножитель на постоянный коэффициент, а также второй счетчик импульсов, счетный вход которого соединен с выходом пятого элемента И, вход подачи кода начальной установки соединен с выходом третьего умножителя на постоянный коэффициент, управляющий вход второго счетчика импульсов соединен с выходом второго элемента задержки, а вход установки в ноль - с выходом “равно” пятого компаратора, и блок формирования постоянного коэффициента, вход которого соединен с выходом “равно” пятого компаратора, а выход соединен с входом подачи постоянного коэффициента третьего умножителя на постоянный коэффициент, при этом измерители частоты входного и синхронизируемых сигналов преобразуют входной и синхронизируемый сигналы в соответствии с математическими выражениями:

U0=A0/f0, U1=A1/f1,

где U0 - сигнал на выходе измерителя частоты входного напряжения;

U1 - сигнал на выходе измерителя частоты синхронизируемого напряжения;

f0 - частота входного напряжения;

f1 - частота синхронизируемого напряжения;

А0, А1 - масштабные коэффициенты, пропорциональные амплитудам входного и синхронизируемого напряжения соответственно,

выпрямители входного напряжения и синхронизируемого напряжения преобразуют напряжения в величины, пропорциональные их амплитудам и равные А0 и А1, соответственно, а выход второго счетчика импульсов является выходом реле синхронизации.

| АНДРЕЕВ В.А | |||

| Релейная защита и автоматика систем электроснабжения | |||

| - М.: Высшая школа, 1991, с.355 | |||

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ СИНХРОНИЗАЦИИ СИНХРОННЫХ ГЕНЕРАТОРОВ | 1991 |

|

RU2014707C1 |

| РЕЛЕ ЗАЩИТЫ | 1994 |

|

RU2088010C1 |

| Устройство для релейной защиты | 1979 |

|

SU855778A1 |

| JP 51141341, 06.12.1976. | |||

Авторы

Даты

2004-07-27—Публикация

2003-03-14—Подача