Предпосылки создания изобретения

Область техники, к которой относится изобретение

Данное изобретение касается в общем компьютерной передачи сигналов, более конкретно устройства и способа сопряжения интегральных схем высокоскоростной поблочной передачи сигналов данных, управления и адреса между множеством интегральных схем на шине или между двумя узлами с пониженным потреблением энергии.

Уровень техники

В полупроводниковых интегральных схемах, используемых при цифровых вычислениях и других цифровых применениях, часто используется множество взаимосоединенных схем со сверхвысокой степенью интеграции (СВСИ) для выполнения передачи двоичных данных по единым или многосегментным линиям передачи. Обычные линии передач включают в себя трассировки, которые образованы на соответственной подложке типа печатной платы. Каждую линию передачи можно проектировать, например, используя так называемые микрополосковые трассировки и трассировки полосковой линии, чтобы образовать линию передачи, имеющую волновое сопротивление приблизительно 50-70 Ом. В качестве альтернативы противоположные концы каждой линии передачи могут оканчиваться волновым сопротивлением. Выходная нагрузка на драйвере для такой линии передачи может составлять всего (25-35) Ом.

Для потребления приемлемой энергии высокочастотная передача сигналов требует сигналы небольшой амплитуды. В случае приемного устройства для легкого обнаружения размаха напряжения (например, 0,8-1,2 В) в условиях наличия помех, типа ЛСПГ (логические схемы приемопередатчика Ганнинга), ВСЛСП (высокоскоростная логическая схема приемопередатчика), ЛСПОН (логическая схема последовательной оконечной нагрузки) или ШОП (шины оперативной памяти rambus), ток также должен быть очень большим (например, порядка 50-60 миллиампер на драйвер). В типичном приемном устройстве используется компаратор с сигналом опорного напряжения (ОН), скомпонованный на полпути между входным высоким напряжением (ВхВН) и входным низким напряжением (ВхНН). Сигнал ОН представляет собой сигнал источника опорного напряжения постоянного тока высокого полного сопротивления, который свободно отслеживают источники электропитания по времени, но не может реагировать на мгновенный шум. Обычно высокое выходное напряжение (ВыхВН) и низкое выходное напряжение (ВыхНН) означают сигналы, поступающие от передающего источника, а ВхНН и ВхВК означают сигналы, поступающие на вход приемного устройства, хотя их можно рассматривать как один и тот же сигнал.

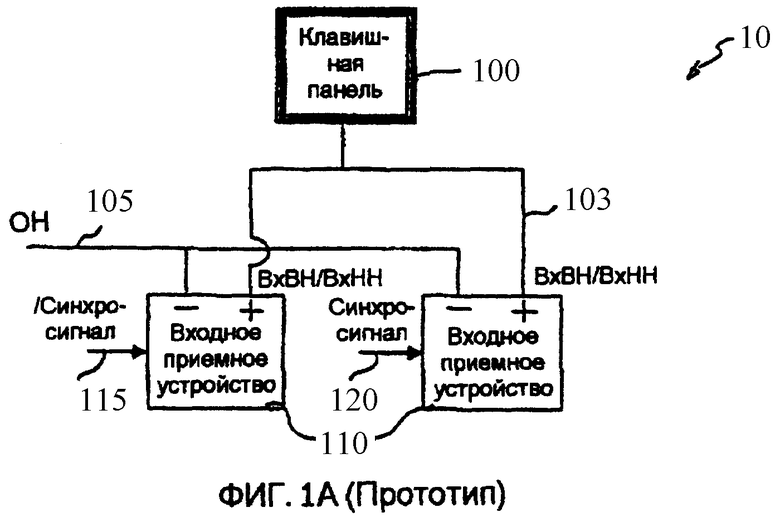

На фиг.1А представлена блок-схема, иллюстрирующая известное приемное устройство 10, использующее технологию ШОП. Система 10 включает в себя клавишную панель 100, подсоединенную через сигнальные линии 103 к внутренним входным приемным устройствам 110. К каждому внутреннему приемному устройству 110 подводят сигнал 105 ОН. Сигнал ОН генерирует источник электропитания. Обычно величина постоянного тока источника электропитания изменяется на пять процентов (5%). На фиг.1В представлена временная диаграмма 125, иллюстрирующая примерный сигнал относительно высокого опорного напряжения (ОНв) и низкого опорного напряжения (ОНн). Значения ОНв и ОНн обычно зависят от изменения напряжения источника электропитания, используемого для генерирования сигнала ОН. Для надежного обнаружения полярности сигнала требуются большой размах напряжения, то есть разница между сигналом высокого напряжения (ВхВН) и сигналом низкого напряжения (ВхНН), и устойчивые уровни сигнала выше и ниже сигнала ОН. Размах напряжения современных способов передачи несимметричных сигналов обычно составляет порядка 0,8 В.

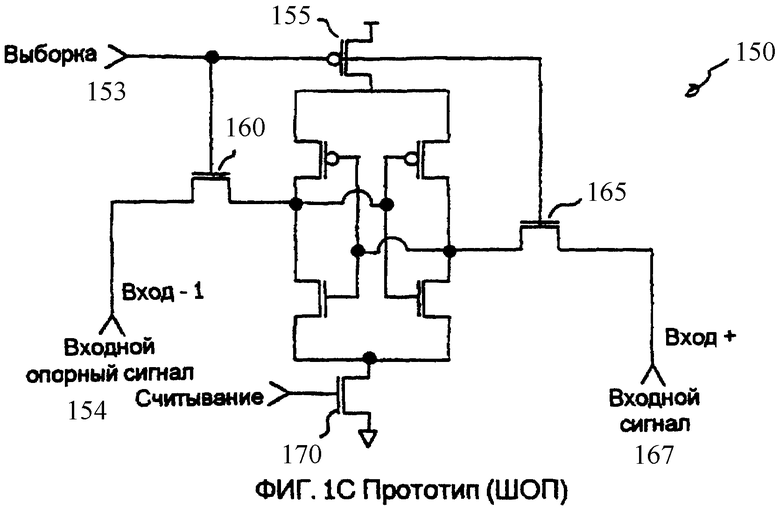

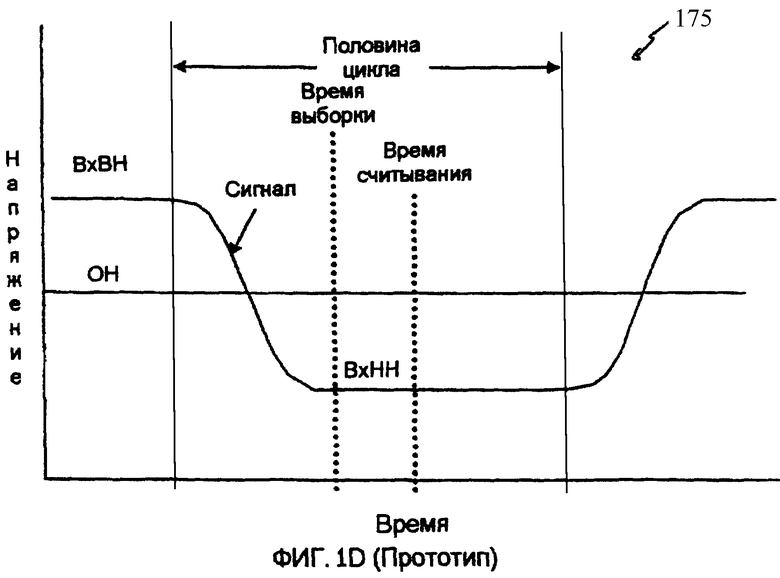

На фиг.1С представлена блок-схема, иллюстрирующая схему известного приемного устройства 150, использующую технологию ШОП. Приемное устройство 150 осуществляет выборки уровня входного сигнала 167 и сигнала 154 ОН до тех пор, пока сигнал не достигает устойчивого уровня, и в это время проходные вентили 160 и 165 запираются. При запирании проходных вентилей 160 и 165 вентиль 172 считывания отпирается для устранения инжекции носителей заряда. На фиг.1D представлена временная диаграмма 175, иллюстрирующая работу приемного устройства 150 для примерного сигнала. Приемное устройство 150 осуществляет выборки входного опорного сигнала и входного сигнала до достижения сигналом устойчивого уровня, например, низкого логического уровня (ВхНН), и когда входной сигнал оказывается устойчивым, приемное устройство 150 считывает значение входного сигнала. Как установлено выше, для надежного обнаружения сигнала размах напряжения сигнала должен быть достаточно быстрым, чтобы обеспечить возможность всем приемным устройствам 150 осуществить выборку устойчивого сигнала с адекватным запасом для времени установления и удержания соединения. Этот размах напряжения должен происходить в течение меньше чем 30% минимального времени цикла, чтобы допускать запас для времени сдвига сигнала, установления и удержания соединения. Поскольку минимальное время цикла снижается ниже 1 наносекунды, границы для сдвига сигнала, времени установления и времени удержания соединения снижаются, с дополнительной нагрузкой на ток драйвера в режиме высокой емкостной нагрузки, работающего на высокой частоте. Применяемая ИИЭР (Институтом инженеров по электротехнике и радиоэлектронике) Р1596.3 передача сигналов с низким перепадом напряжения (ПСНПН) может преодолеть эти проблемы, используя размах напряжения 250 мВ, за счет прохождения комплиментарных сигналов. Прохождения комплиментарных сигналов неизбежно увеличивает количество выводов и размер корпуса.

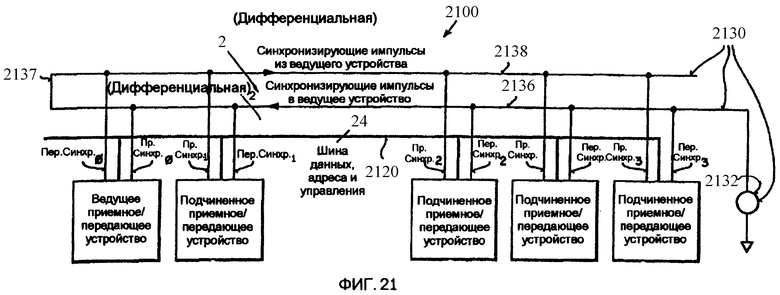

Кроме того, в компьютерных системах обычно используется магистральная система, в которой несколько устройств подсоединены к шине. В большинстве из них используются синхронизирующие импульсы для проверки достоверности сигналов данных, адреса и управления. Фиг.21 иллюстрирует известную систему 2100 для ОПУЗД (оперативная память устройства записи данных), в которой используется линия 2130 синхронизирующих импульсов, имеющая два сегмента 2136 и 2138. Один сегмент 2136 проходит от одного конца шины передачи данных к оборотной точке 2137 рядом со вторым концом шины. Другой сегмент 2138 синхронизирующих импульсов проходит от оборотной точки 2137 обратно к первому концу шины передачи данных. Шина 2120 передачи сигналов переносит сигналы данных, адреса и управления. Эта топология гарантирует, что сигнал, посылаемый по шине 2120, всегда проходит одновременно и в том же самом направлении, как синхронизирующие импульсы 2132, используемые устройством для приема сигнала. Она прекрасно работает, если нагрузка от всех сигналов и синхронизирующий импульс почти идентичны, и синхронизирующие импульсы 2132 используются для выборки и приема сигнала. Однако, иногда для системы может требоваться удвоенная полоса пропускания для данных, в этом случае этот тип магистральной системы требует удвоения количества сигналов, даже если сигналы адреса и управления идентичны и могут быть совместно использованы.

В соответствии с этим имеется необходимость в драйверах малой мощности и надежных приемных устройствах для работы на высокой частоте с большим количеством несимметричных сигналов в существующей технике для недорогостоящих цифровых систем СВСИ.

Сущность изобретения

В системе по настоящему изобретению используются опорные сигналы синхронного напряжения и тактовых импульсов (ОССНТ и /ОССНТ) дифференциального источника небольшого размаха для сравнения несимметричных сигналов такого же размаха, генерируемых той же самой интегральной схемой для передачи высокочастотных сигналов. Следует понимать, что символ "/" используется для обозначения логического "НЕ". Все сигналы оканчиваются их характеристическим сопротивлением на обоих концах линий передачи. Сигналы ОССНТ и /ОССНТ переключаются из одного состояния в другое каждый раз, когда передающая интегральная схема запускает допустимые сигналы. Каждое приемное устройство сигналов включает в себя два компаратора: один для сравнения сигнала с сигналом ОССНТ, а другой для сравнения сигнала с сигналом /ОССНТ. Присутствующее двоичное значение сигнала определяет, который компаратор соединен с ОССНТ и /ОССНТ, необязательно с использованием логики "исключающее ИЛИ". До тех пор, пока сигналы ОССНТ и /ОССНТ не изменят свое двоичное значение, подсоединенный компаратор в приемном устройстве определяет, произошло ли изменение двоичного значения сигнала. Снова следует понимать, что сигналы ОССНТ и /ОССНТ изменяют свое двоичное значение каждый раз, когда сигнал может изменять свое двоичное значение. Сигналы ОССНТ и /ОССНТ предпочтительно синхронизированы с сигналом.

Способ по настоящему изобретению включает в себя этапы получения колеблющегося опорного сигнала источника синхронного напряжения и тактовых импульсов и его дополнения (ОССНТ и /ОССНТ), и приема поступающего несимметричного сигнала. Способ сравнивает колеблющийся опорный сигнал с поступающим сигналом с помощью первого компаратора для образования первого результата и сравнивает дополнение с поступающим сигналом с помощью второго компаратора для образования второго результата. Затем, на основании предыдущего сигнала, способ выбирает один из первого результата или второго результата в качестве выходного сигнала. Этап выбора одного из результатов включает в себя сравнение выходного сигнала с опорным сигналом (ОССНТ) и с дополнением (/ОССНТ). Этап выбора далее включает в себя управление выходным сигналом от предыдущего сигнала по направлению к первому результату или второму результату, основываясь на компараторе, который подсоединен в данный момент. Если поступающий сигнал изменяется, этап выбора включает в себя сохранение подсоединения того же компаратора. Если поступающий сигнал остается тем же самым, этап выбора включает в себя отсоединение подсоединенного в данный момент компаратора и подсоединение другого компаратора. Затем способ позволяет стабилизировать схему.

Система и способ благоприятно устраняют необходимость в сигнале ОН высокого полного сопротивления для сравнения несимметричных сигналов небольшого размаха. Это снижает потребность в трех различных уровнях напряжения (высокий уровень выходного сигнала, низкий уровень выходного сигнала и уровень ОН) до двух различных уровней напряжения (высокий уровень выходного сигнала и низкий уровень выходного сигнала). Устранение ОН снижает необходимый размах напряжения и, соответственно, снижает потребление энергии. Использование приемного устройства с двумя компараторами позволяет подсоединять приемное устройство к одному и тому же компаратору, когда каждый цикл сигнал изменяется. Только один компаратор подсоединяется на основании текущего двоичного значения сигнала и ОССНТ. Система имеет индивидуально регулируемую задержку для каждого приемного устройства, чтобы подсоединять или отсоединить компаратор, вследствие чего уменьшая эффект сдвига во время передачи синхронных сигналов источника. Система может иметь множество опорных сигналов синхронного напряжения и тактовых импульсов дифференциального источника, чтобы сравнивать множественные несимметричные сигналы в одной и той же интегральной схеме, типа микропроцессора или контроллера системы, которая имеет много сигналов. Система и способ обеспечивают выгоды дифференциальной передачи сигналов в системе передачи несимметричных сигналов.

При использовании той же самой концепции система может иметь опорные сигналы двунаправленного комплиментарного источника синхронного напряжения и синхронизации для сравнивания с двунаправленными несимметричными сигналами. Система может иметь драйвер или передающее устройство для управления максимальной скоростью нарастания выходного напряжения сигнала, являющегося существенной частью общего периода сигнала, вследствие этого снижая выходной ток. Система может иметь внутренние схемы согласования полного сопротивления типа нагрузочных резисторов или канала р-типа с заземленным затвором МОП-структуры для согласования волнового сопротивления линии передачи на обоих концах прямого соединения между ЦП (центральным процессором) и сверхоперативной памятью или ЦП и контроллером системы. Система имеет двойную схему компаратора для преобразовывания несимметричной шины с двумя комплиментарными сигналами, подлежащими передаче и приему, с сопоставимой помехоустойчивостью дифференциальной шины для внутренней шины передачи данных запоминающего устройства, процессора или других интегральных схем, типа шины для передачи широкого диапазона данных. Система предпочтительно имеет переменный размер передающего устройства с медленным включением и медленным выключением, чтобы иметь аналогичные максимальные скорости нарастания выходного напряжения для всех сигналов в каждой группе сигналов ОССНТ и /ОССНТ и множества сигналов, которые передаются вместе. Кроме того, следует понимать, что управляющие сигналы и сигналы адреса можно передавать по каналам, отличающимся от каналов для сигналов данных. Это позволяет прогонять канал управления и адреса на частоте, отличающейся от частоты канала передачи данных, и позволяет к каждому из каналов прикладывать различные нагрузки.

Краткое описание чертежей

Фиг.1А представляет блок-схему, иллюстрирующую известное основанное на ШОП приемное устройство.

Фиг.1В представляет временную диаграмму, иллюстрирующую уровни сигналов показанного на фиг.1А известного приемного устройства.

Фиг.1С представляет принципиальную схему, иллюстрирующую другое известное основанное на ШОП приемное устройство.

Фиг.1D представляет временную диаграмму, иллюстрирующую работу показанного на фиг.1С известного приемного устройства.

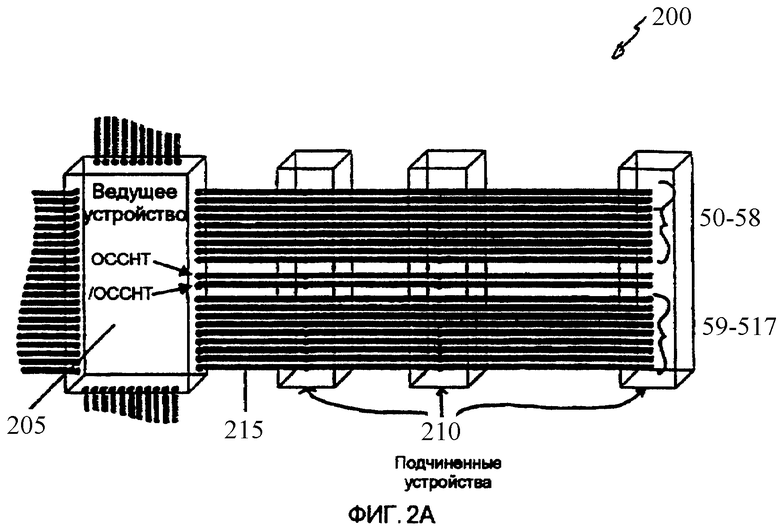

Фиг.2А представляет изображение в перспективе блок-схемы, иллюстрирующей систему с ведущим устройством и подчиненными устройствами в соответствии с настоящим изобретением.

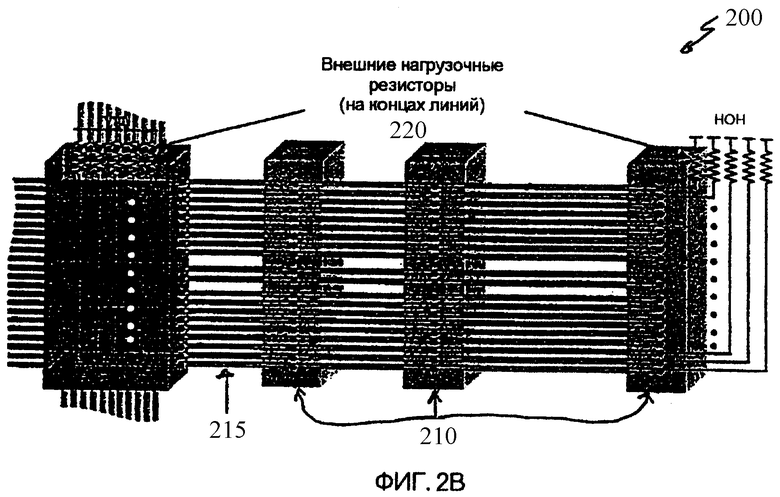

Фиг.2В представляет блок-схему, иллюстрирующую показанную на фиг.2А систему, имеющую линии передачи с резисторами согласования полного сопротивления на концах.

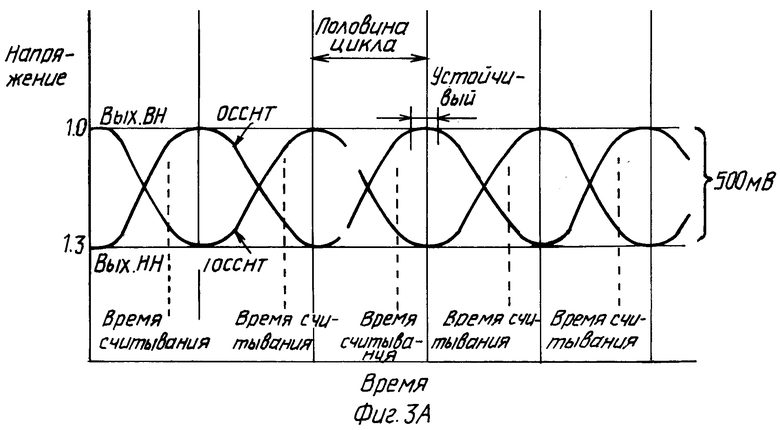

Фиг.3А представляет временную диаграмму, иллюстрирующую дифференциальные опорные сигналы ОССНТ и /ОССНТ относительно моментов считывания сигнала.

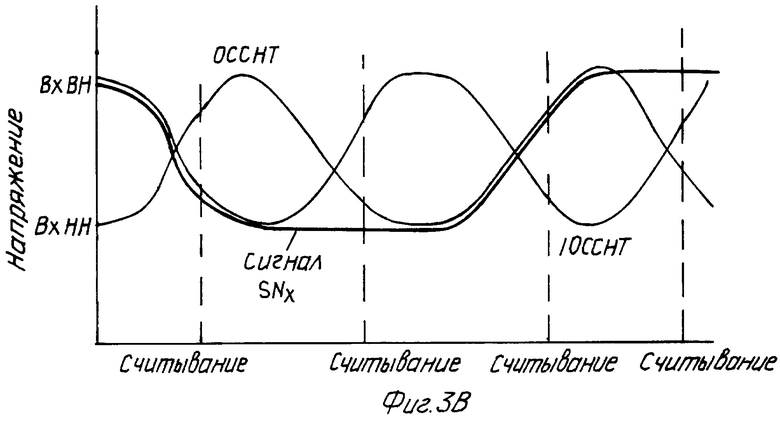

Фиг.3В представляет временную диаграмму, иллюстрирующую сигналы ОССНТ и /ОССНТ относительно несимметричного сигнала.

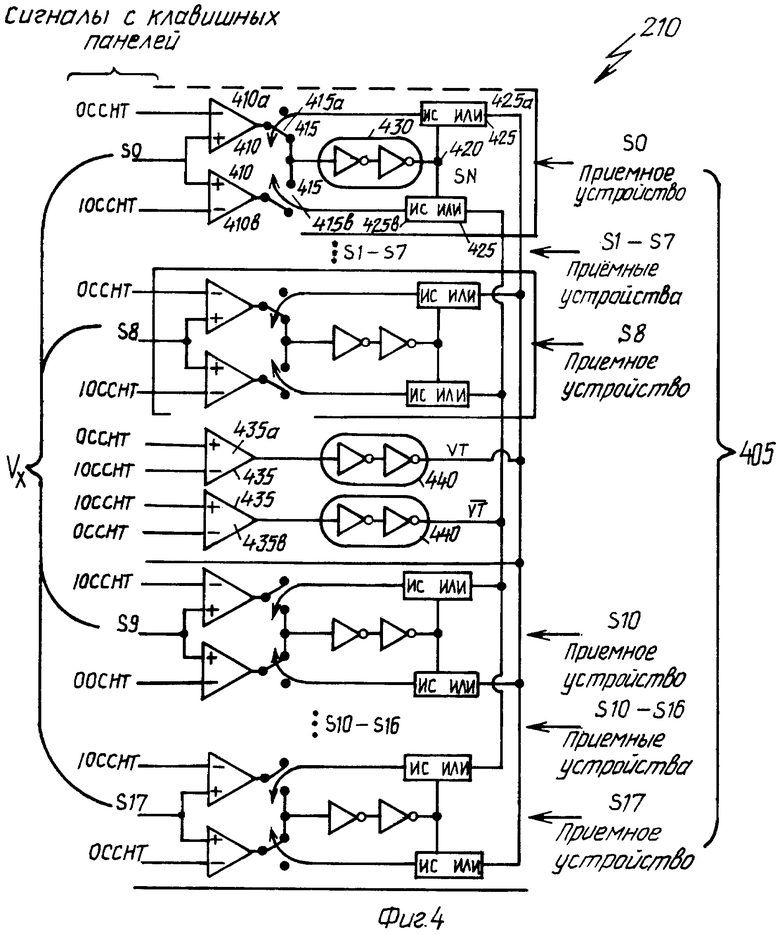

Фиг.4 представляет схемы высокого уровня, иллюстрирующие приемные устройства несимметричного сигнала.

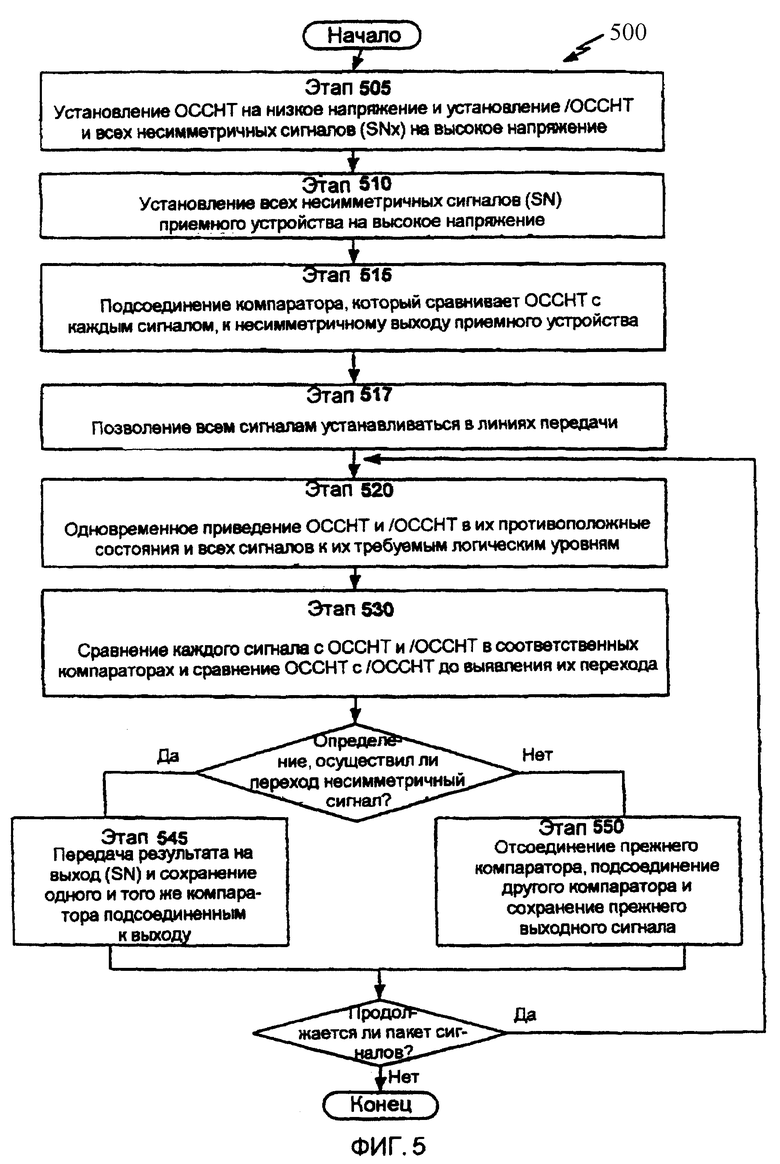

Фиг.5 представляет графическую схему программы, иллюстрирующую способ передачи сигналов от передающего устройства по линии передачи к приемному устройству.

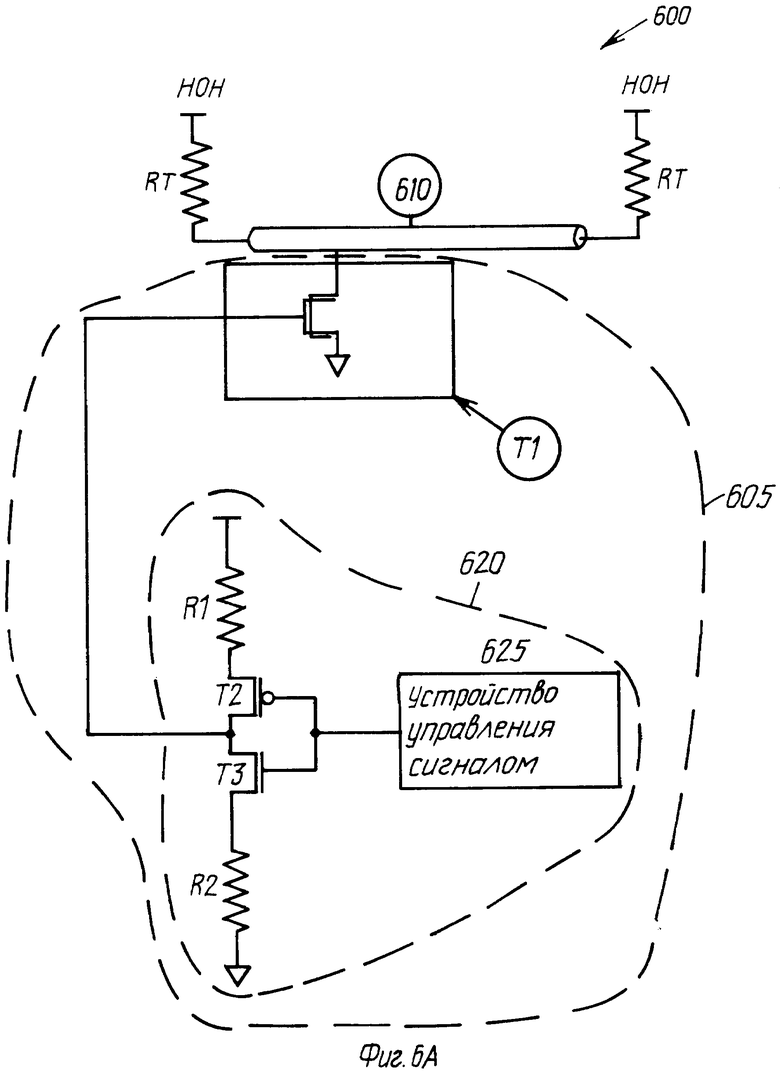

Фиг.6А представляет принципиальную схему, иллюстрирующую драйвер медленного включения и медленного выключения для всех сигналов.

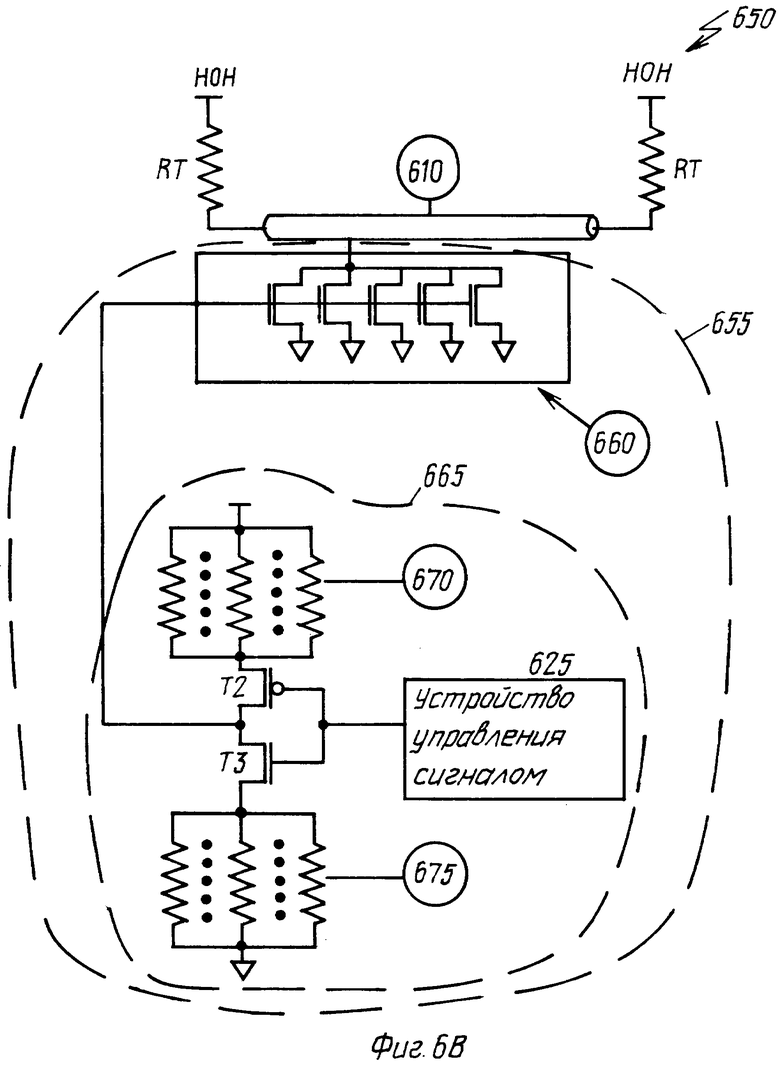

Фиг.6В представляет принципиальную схему, иллюстрирующую драйверы, имеющие регулируемые скорости максимального нарастания выходного напряжения сигнала и сдвиг между сигналами.

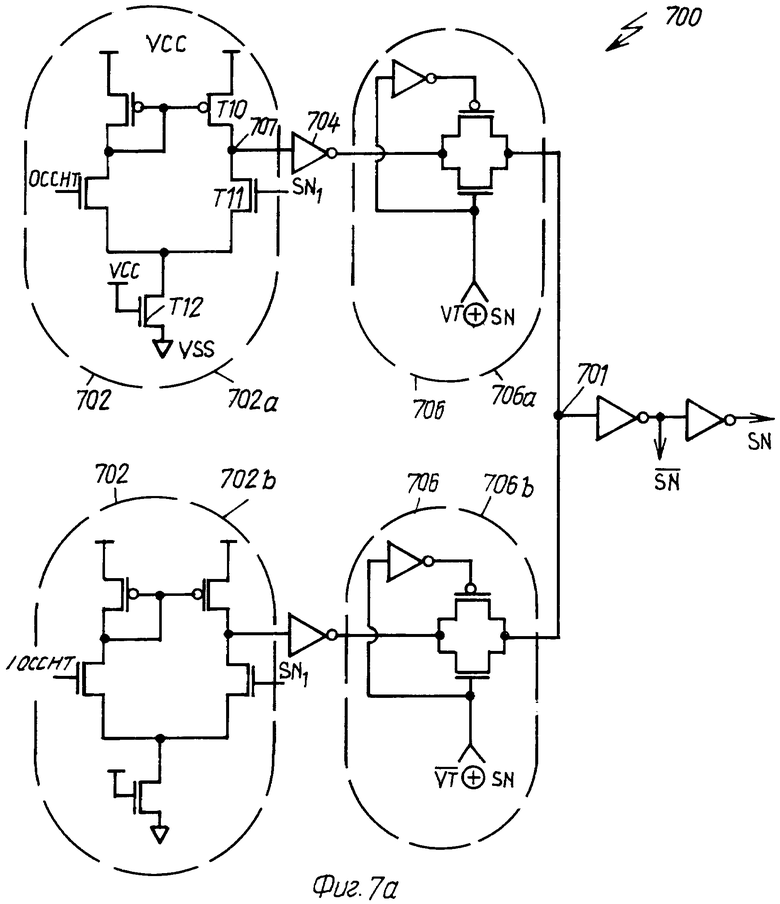

Фиг.7А представляет принципиальную схему, иллюстрирующую показанное на фиг.4 приемное устройство несимметричного сигнала в первом варианте осуществления.

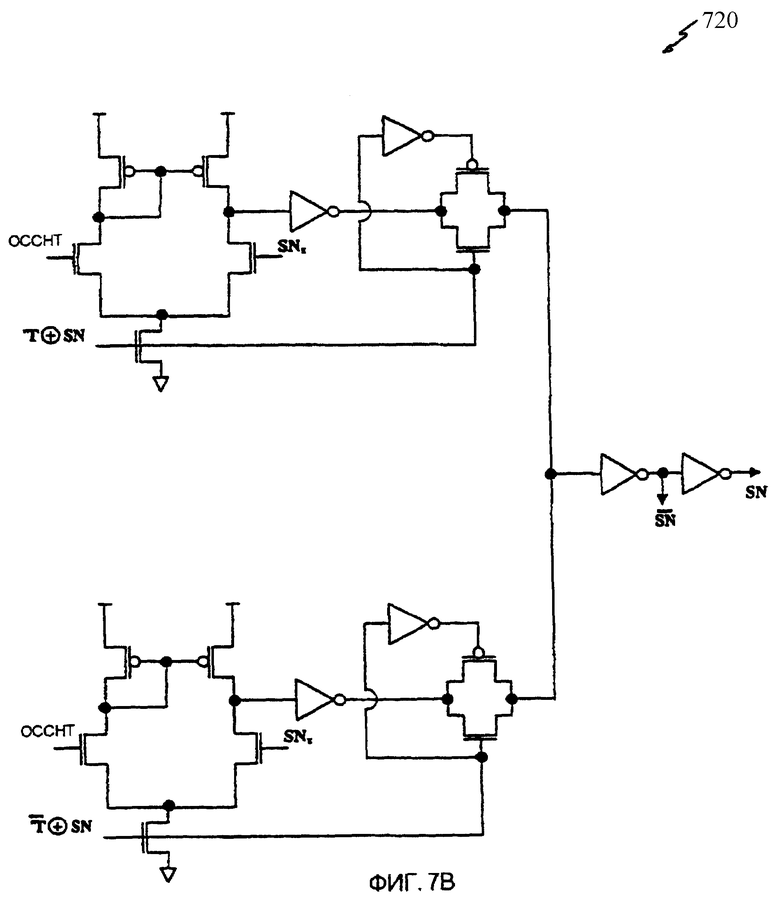

Фиг.7В представляет принципиальную схему, иллюстрирующую показанное на фиг.4 приемное устройство несимметричного сигнала во втором варианте осуществления.

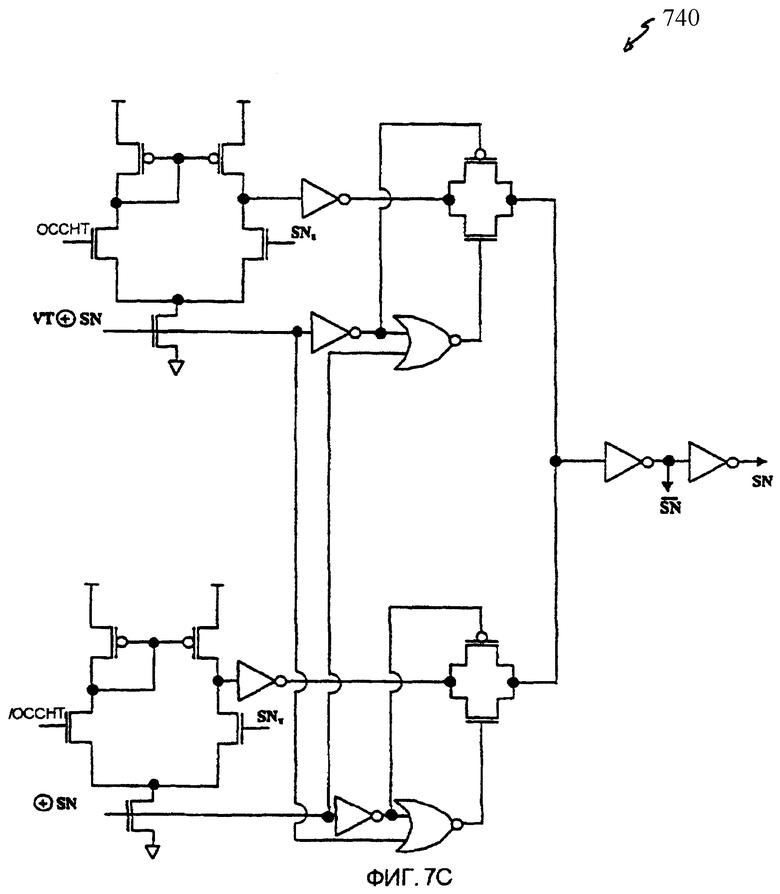

Фиг.7С представляет принципиальную схему, иллюстрирующую показанное на фиг.4 приемное устройство несимметричного сигнала в третьем варианте осуществления.

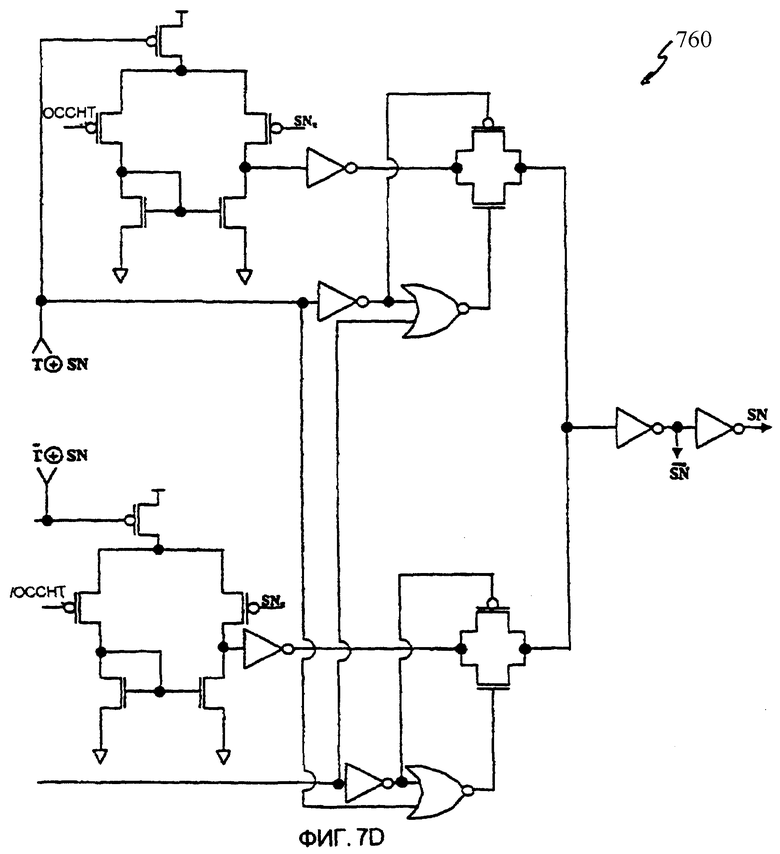

Фиг.7D представляет принципиальную схему, иллюстрирующую показанное на фиг.4 приемное устройство несимметричного сигнала в четвертом варианте осуществления.

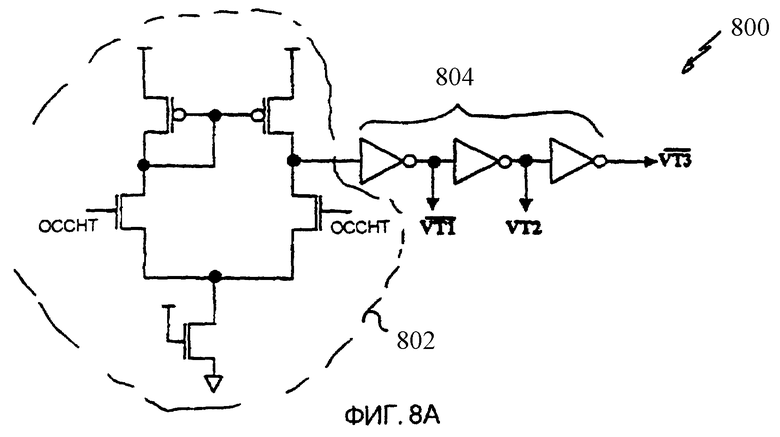

Фиг.8А представляет принципиальную схему, иллюстрирующую детали схемы показанного на фиг.4 компаратора ОССНТ-/ОССНТ.

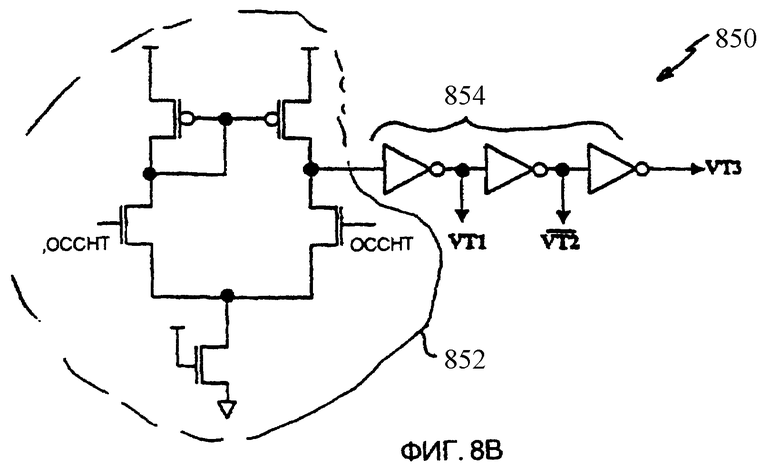

Фиг.8В представляет принципиальную схему, иллюстрирующую детали схемы показанного на фиг.4 компаратора /ОССНТ-ОССНТ.

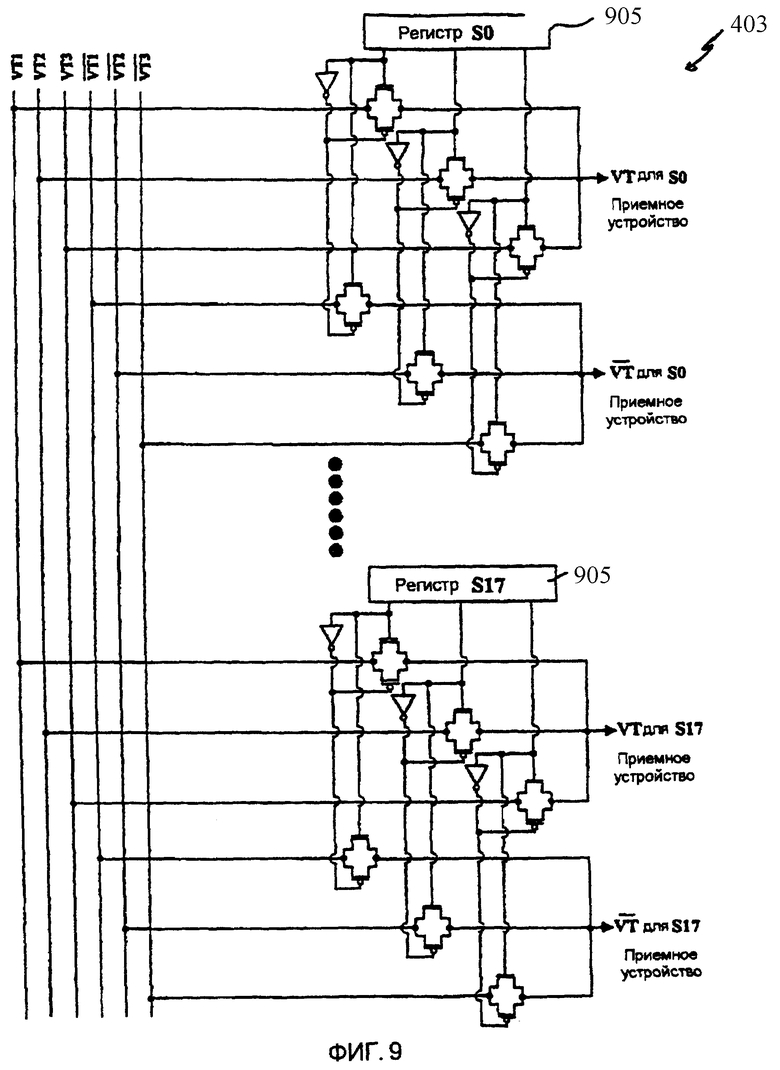

Фиг.9 представляет принципиальную схему, иллюстрирующую приемные устройства с индивидуально регулируемыми задержками для устранения сдвига во время передачи.

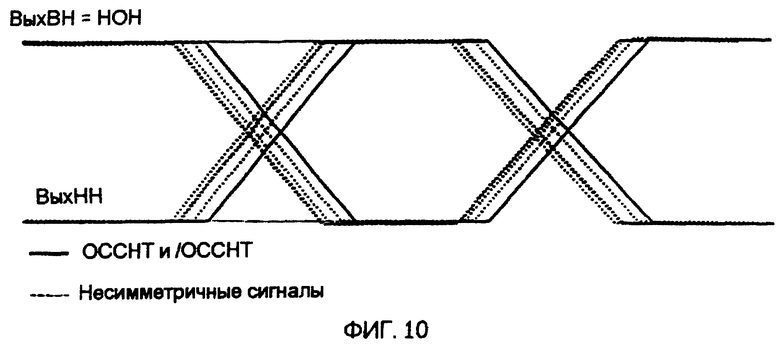

Фиг.10 иллюстрирует формы волны сигналов и сдвиг между ними.

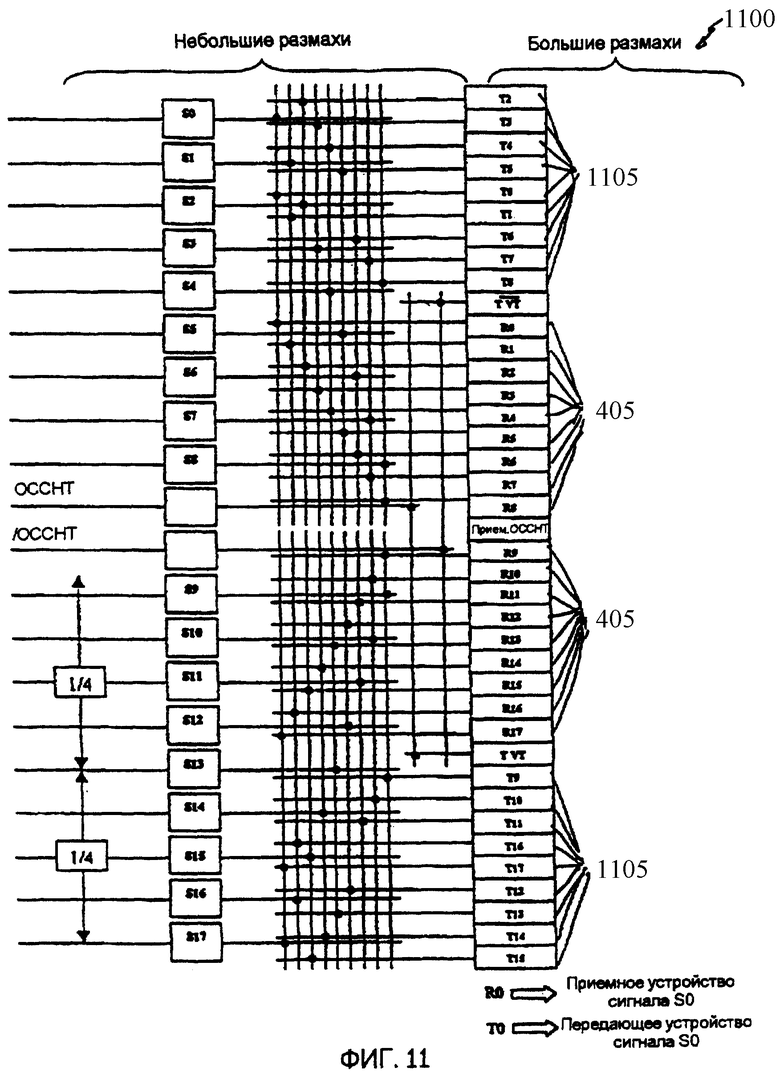

Фиг.11 представляет изображение в перспективе монтажной схемы, показанной на фиг.2 системы.

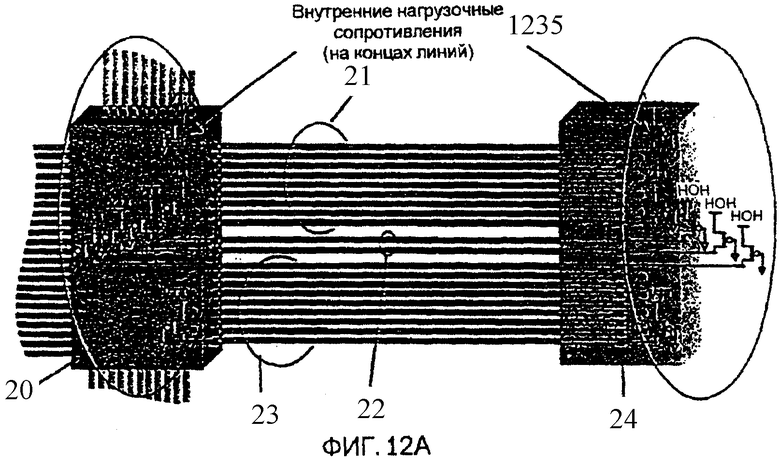

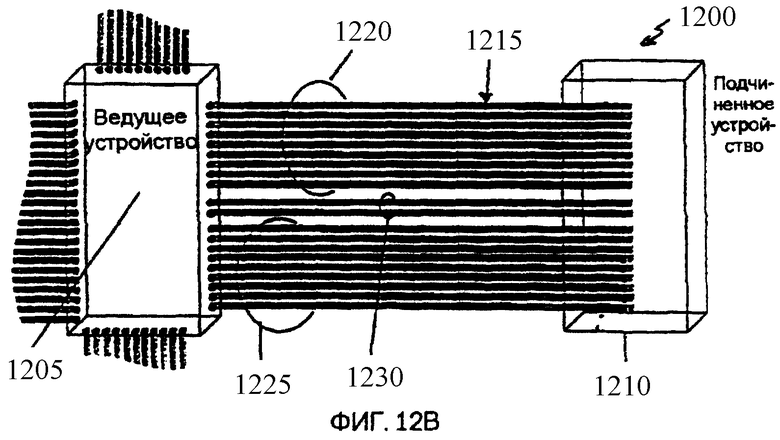

Фиг.12А представляет блок-схему, иллюстрирующую двухточечную систему в соответствии с данным изобретением.

Фиг.12В представляет блок-схему, иллюстрирующую показанное на фиг.12А прямое соединение, имеющее устройства, содержащие канал р-типа с заземленным затвором МОП-структуры для согласования полных сопротивлений внутри интегральной схемы.

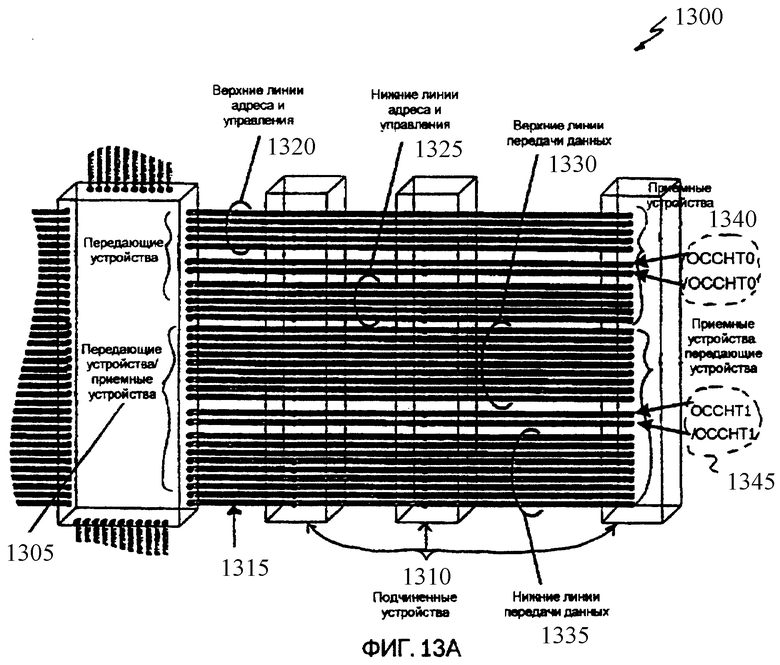

Фиг.13А представляет изображение в перспективе блок-схемы, иллюстрирующее однонаправленную систему передачи сигналов и двунаправленную систему передачи сигналов на одной интегральной схеме.

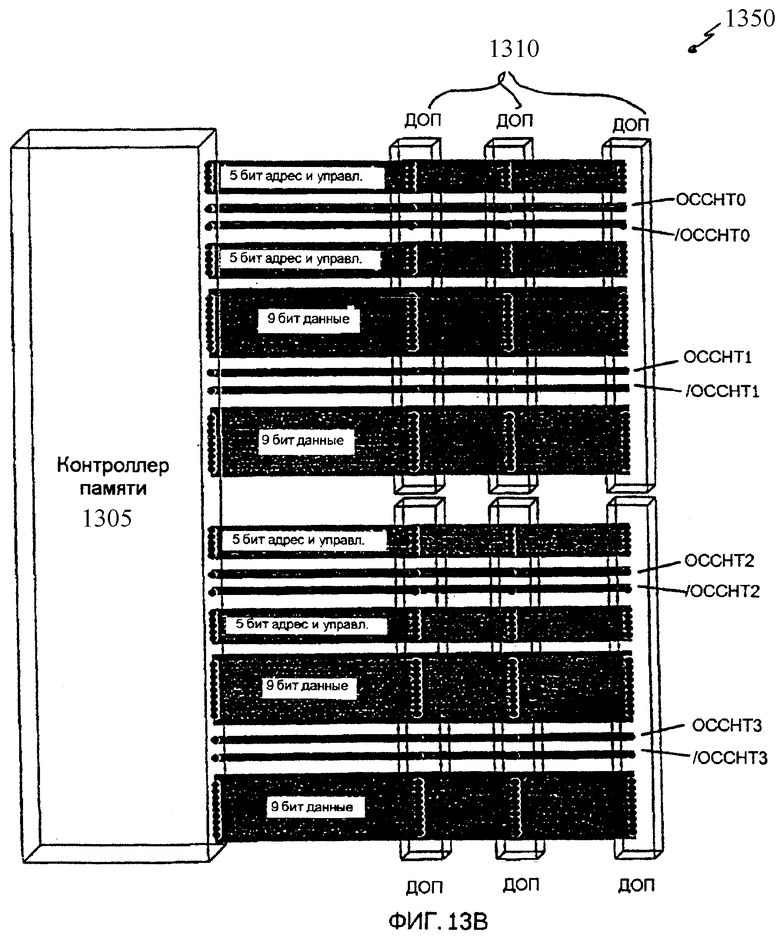

Фиг.13В представляет изображение в перспективе блок-схемы, иллюстрирующее четыре системы передачи сигналов на одной интегральной схеме.

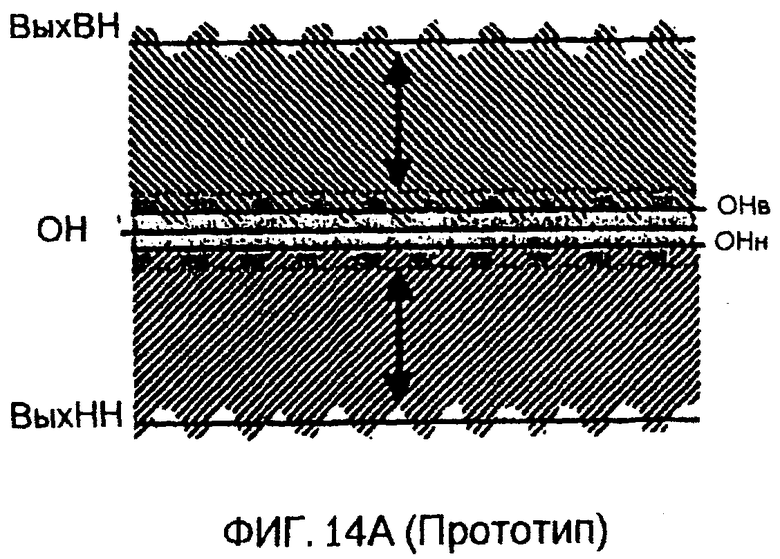

Фиг.14А иллюстрирует фиксированное опорное напряжение согласно прототипу, значение которого находится в области среднего значения между логическим высоким уровнем напряжения и логическим низким уровнем.

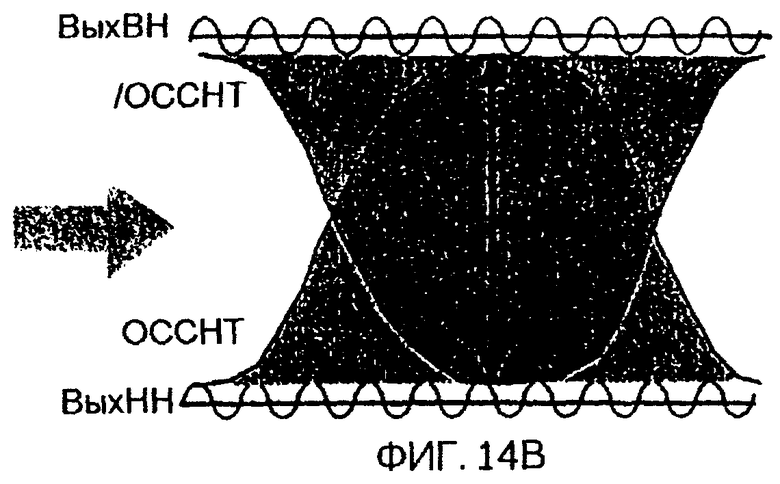

Фиг.14В иллюстрирует комплиментарные опорные сигналы, которые имеют такой же размах напряжения, как любой сигнал.

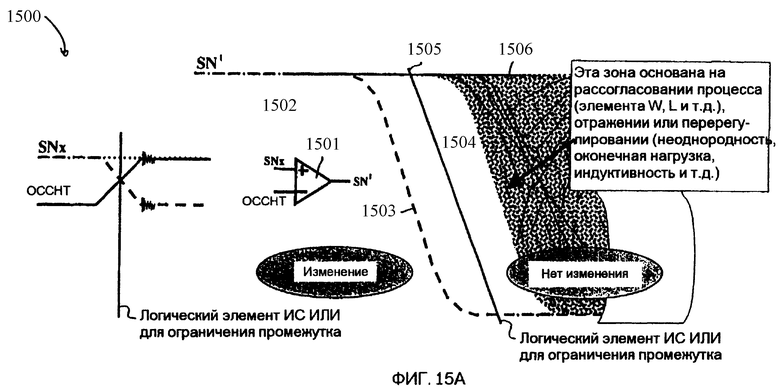

Фиг.15А иллюстрирует дифференциальный усилитель, который усиливает разность между сигналом данных и опорным сигналом.

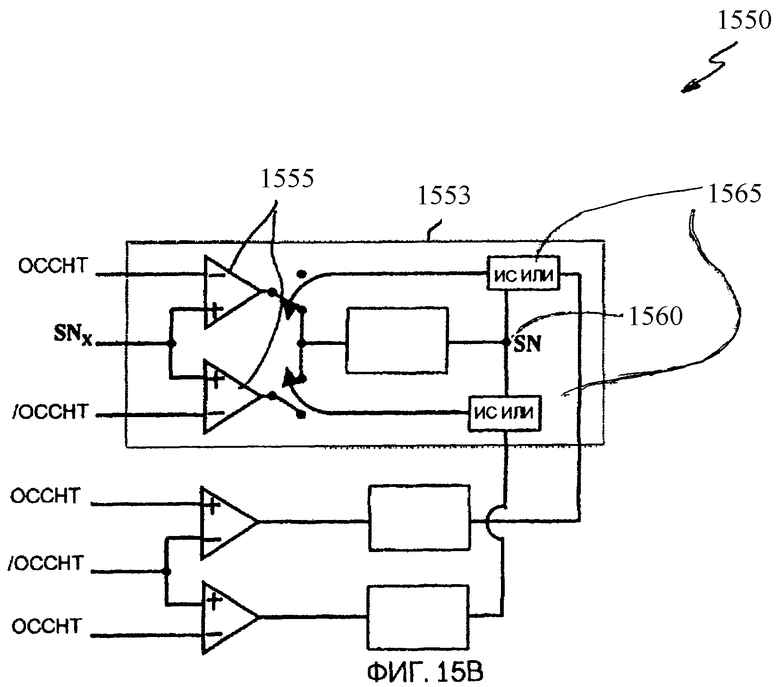

Фиг.15В представляет блок-схему, иллюстрирующую логику управления.

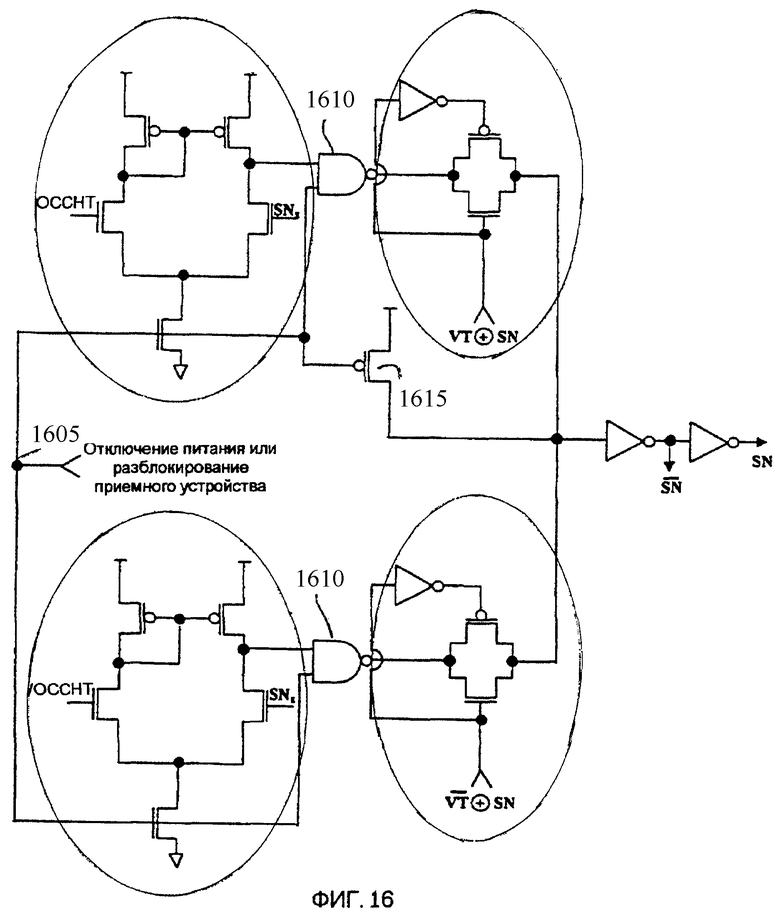

Фиг.16 представляет принципиальную схему, иллюстрирующую приемное устройство несимметричного сигнала с дифференциальными усилителями, стробируемыми понижением мощности или сигналом разблокирования приемного устройства для отключения мощности от приемного устройства, когда оно не используется.

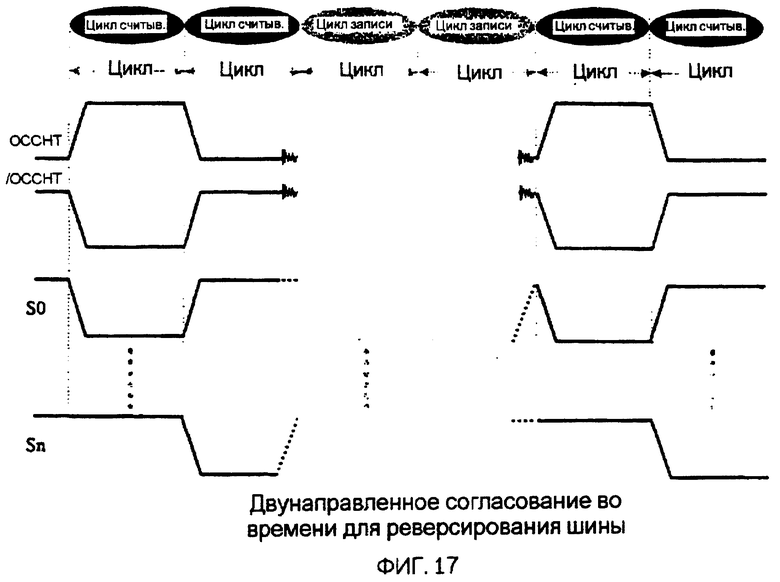

Фиг.17 представляет временную диаграмму, иллюстрирующую время перехода сигнала при применении, требующем быстрого изменения шины от считывания к записи или наоборот.

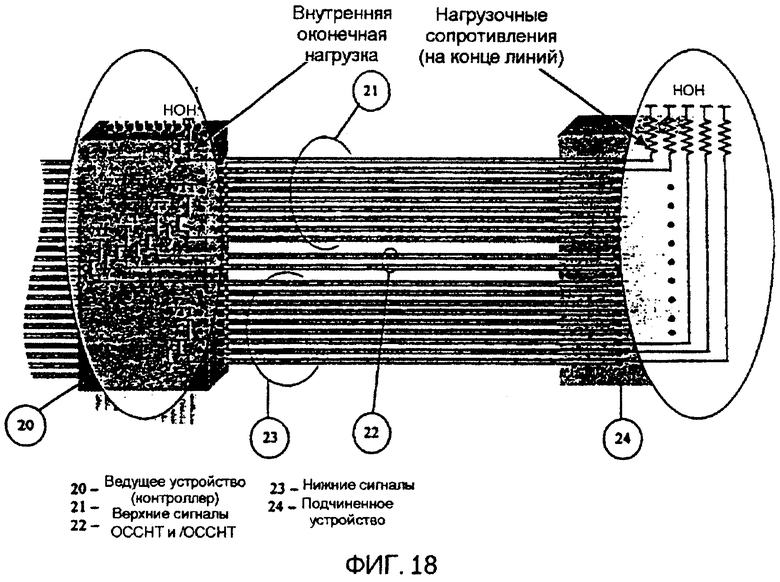

Фиг.18 представляет блок-схему, иллюстрирующую двухточечную систему.

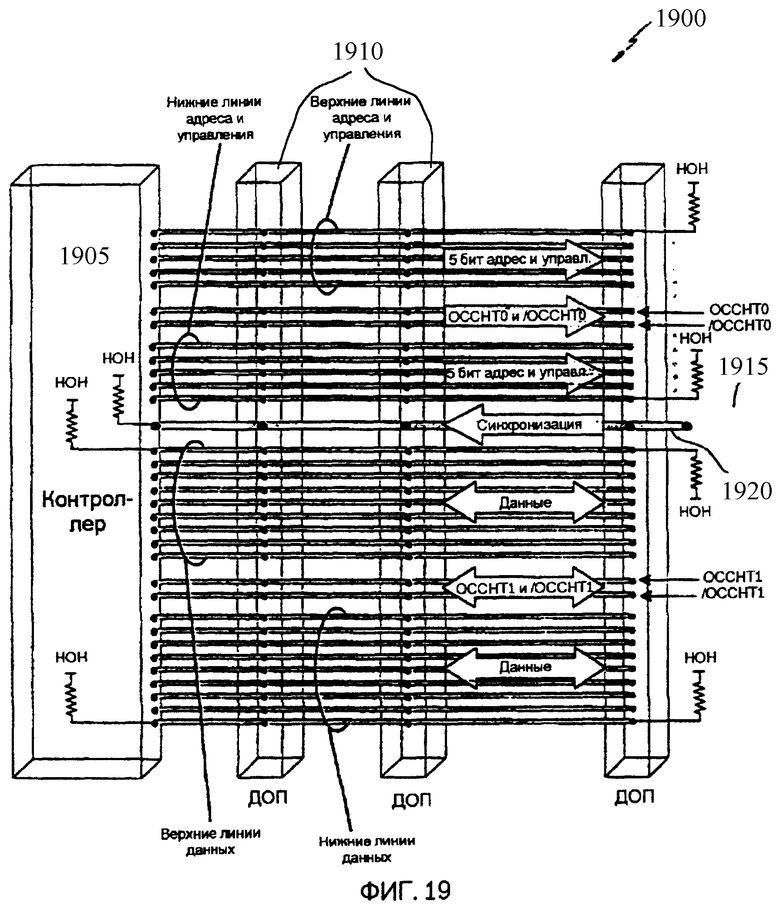

Фиг.19 изображает систему, имеющую множество шин, где сигналы принимаются одновременно.

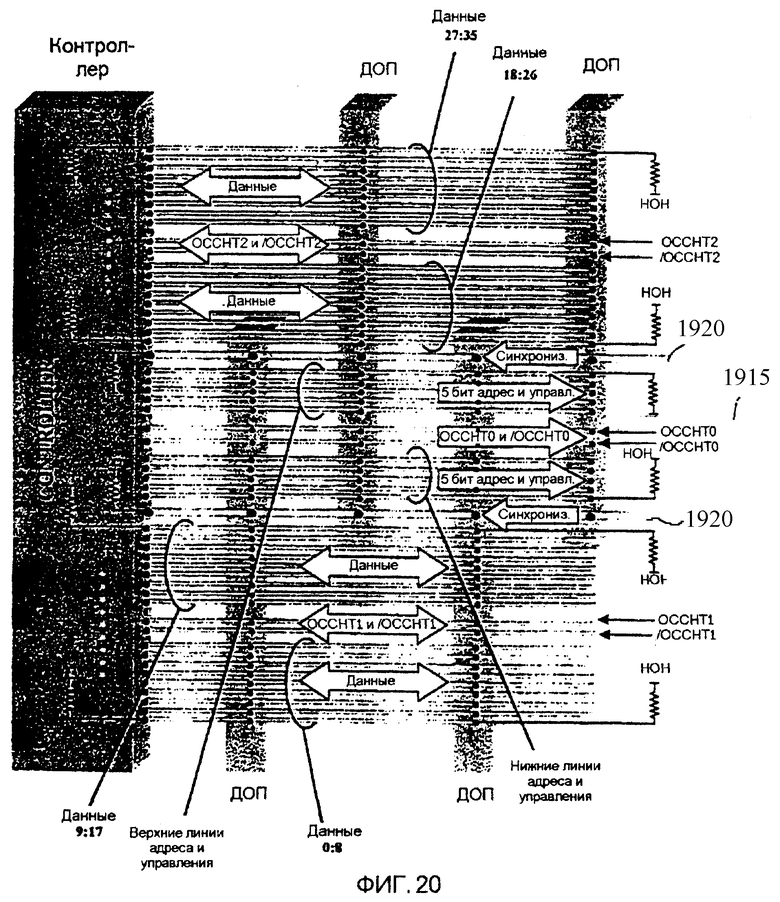

Фиг.20 представляет блок-схему, иллюстрирующую систему, имеющую три шины для получения большей полосы пропускания.

Фиг.21 иллюстрирует известную систему для ОПУЗД, в которой используется линия синхронизации, имеющая два сегмента.

Подробное описание предпочтительного варианта осуществления

Настоящее изобретение обеспечивает систему передачи сигналов и способ высокоскоростной связи на мультиплексных шинах или прямых соединениях между множеством устройств СВСИ и обеспечивает более низкое потребление энергии по сравнению с применяемым в настоящее время принципом сопряжения несимметричных сигналов. Систему передачи сигналов можно использовать для подсоединения множества запоминающих устройств с помощью мультиплексной шины к контроллеру памяти для поблочной передачи информации данных, адресов и управления. Благодаря использованию множества шин, можно собрать такие устройства, как ДОП (динамическая оперативная память), коммутационные переключатели процессоров, устройства СОП (статической оперативной памяти) широкого диапазона и системные контроллеры, чтобы получить полосы пропускания свыше 4 гигабайт в секунду. Фактически по этой шине можно посылать все сигналы, необходимые для компьютера или других цифровых систем. Специалистам в данной области техники должно быть понятно, что все устройства, подобные центральным процессорам в компьютерной системе, нуждаются в методологиях и структурах шины такой системы.

Фиг.2А представляет изображение в перспективе блок-схемы, иллюстрирующей систему 200 с ведущим устройством (передающими устройствами) 205, подсоединенным через шинную архитектуру (линии передачи) 215 к множеству подчиненных устройств (приемных устройств) 210, в соответствии с настоящим изобретением. Как показано, ведущее устройство 205 сконфигурировано таким образом, чтобы осуществлять связь, например, двадцати (20) сигналов, включая несимметричные сигналы S0-S17, опорные сигналы ОССНТ и /ОССНТ синхронного напряжения и тактовых импульсов комплиментарного источника небольшого размаха, шины электропитания (не показанные) и линии заземления (не показанные), параллельно по линиям 215 передачи к каждому подчиненному устройству 210. Следует понимать, что символ "/" используется для обозначения логического "НЕ". Сигналы S0-S17 могут быть сигналами данных, управления или адреса, либо мультиплексированными, либо немультиплексированными, в соответствии с определением протоколом. Могут иметься комплиментарные сигналы типа сигналов синхронизации или инициализации для других целей, требуемых протоколом или синхронизацией системы.

Как показано на фиг.3А, сигналы ОССНТ и /ОССНТ переключаются из одного состояния в другое каждый раз, когда ведущее устройство 205 запускает достоверные сигналы. Следует понимать, что подчиненное устройство 210 может включать в себя множество приемных устройств (405, фиг.4), где каждое приемное устройство 405 включает в себя два компаратора: один для сравнения сигнала с сигналом ОССНТ, а другой для сравнения сигнала с сигналом /ОССНТ. Присутствующее двоичное значение сигнала определяет, который компаратор подсоединен к выходному терминалу 420, необязательно с использованием логики "исключающее ИЛИ", с сигналами ОССНТ и /ОССНТ. Пока сигналы ОССНТ и /ОССНТ не изменили свое двоичное значение, разблокированный компаратор в приемном устройстве 405 определяет, произошло ли изменение двоичного значения сигнала.

Для связи между микросхемами на шине или между двумя узлами все сигналы передаются предпочтительно по существу в одно и то же время от одной и той же микросхемы к другой микросхеме или к множеству микросхем, подсоединенных к шине, и предпочтительно имеют по существу одну и ту же нагрузку, размах и максимальную скорость нарастания выходного напряжения (когда сигналы осуществляют переход). Точно также, для связи внутри микросхемы, сигналы запускаются предпочтительно по существу в одно и то же время из одной и той же области или блока к другим областям или другим блокам в одной и той же микросхеме и предпочтительно имеют по существу одну и ту же нагрузку, размах и максимальную скорость нарастания выходного напряжения (когда сигналы осуществляют переход). На фиг.19 и 20, описываемых ниже, показаны система и способ, предназначенные для гарантии, что сигнал возбуждается по существу в одно и то же время.

Чтобы способствовать чрезвычайно высоким скоростям передачи данных по этой внешней шине, циклы шины инициируются, когда сигнал ОССНТ является низким (то есть сигнал /ОССНТ высокий). Вся поблочная передача начинается во время цикла, когда ОССНТ низкий, и заканчивается, когда ОССНТ остается низким, чтобы облегчать предварительную установку приемного устройства 405 на последнее двоичное значение сигнала. Это обеспечивает возможность пакетной передачи четного количества битов. Когда сигналы должны изменить направление (вследствие мультиплексного характера сигналов), для устанавливания шины могут требоваться один или более мертвые циклы из-за задержек распространения или устанавливания сигналов ОССНТ и /ОССНТ, когда они являются двунаправленными. Описываемая ниже фиг.17 иллюстрирует двунаправленное согласование по времени для реверсирования шины, чтобы избежать потери мертвых циклов.

На фиг.2В представлена блок-схема, иллюстрирующая систему 200 (фиг.2А), имеющую линии 215 передачи с внешними резисторами 220 согласования полных сопротивлений на концах, где нагрузочные сопротивления равны их волновому сопротивлению, которое предпочтительно составляет 50-70 Ом. Напряжение оконечной нагрузки обозначено символом НОН и составляет предпочтительно порядка 1,8 В для 2,5 В рабочего напряжения (для VCC, равного 2,5 В, и VSS, равного 0 В). Номинальный размах напряжения предпочтительно установлен меньше 1 В, предпочтительно меньше 40% от номинального напряжения, и наиболее предпочтительно составляет 500 мВ. Следовательно, как показано на фиг.3А, выходное высокое напряжение (ВыхВН) составляет 1,8 В, а выходное низкое напряжение (ВыхНН) составляет 1,3 В.

Фиг.3А представляет временную диаграмму, иллюстрирующую комплиментарные опорные сигналы ОССНТ и /ОССНТ относительно моментов считывания сигнала. ОССНТ начинается при ВыхНН, а /ОССНТ начинается при ВыхВН. В первом цикле ведущее устройство 205 возбуждает все низкие существующие сигналы, включая /ОССНТ для ВыхНН, в один и тот же момент времени, а нагрузочные сопротивления 220 повышают ОССНТ до ВыхВН. Несимметричные сигналы, которые являются высокими, нагрузочными сопротивлениями удерживаются на ВыхВН. Надлежащий момент считывания, то есть момент для считывания логического уровня входного сигнала, наступает после соединения перехода ОССНТ и /ОССНТ и до времени устойчивости, то есть, когда сигнал ОССНТ или /ОССНТ достигает установившегося состояния на ВхВН или ВхНН. Сигналы ОССНТ и /ОССНТ предпочтительно имеют одинаковое время нарастания и спада, где каждое время нарастания и спада составляет приблизительно половину периода цикла любого опорного сигнала.

Фиг.3В представляет временную диаграмму, иллюстрирующую сигналы ОССНТ и /ОССНТ относительно несимметричного сигнала. Несимметричный сигнал начинается равным /ОССНТ при высоком напряжении и затем переходит вместе с /ОССНТ к низкому напряжению. Затем несимметричный сигнал остается на низком напряжении, вследствие этого становясь равным ОССНТ, и затем переходит вместе с ОССНТ к высокому напряжению. После этого несимметричный сигнал остается на высоком напряжении, вследствие этого становясь равным сигналу /ОССНТ.

Фиг.4 представляет высокий уровень, схематически иллюстрирующий подчиненное устройство 210 несимметричного сигнала, имеющее приемное устройство 405 для каждой сигнальной линии 215. Каждое приемное устройство 405 сигнала имеет два компаратора 410, один компаратор 410а для сравнения поступающего несимметричного сигнала "SNx" с ОССНТ, а другой компаратор 410b для сравнения сигнала SNx с /ОССНТ. Оба компаратора 410 имеют выходы, избирательно подсоединяемые через переключатели 415 к выходу 420. Следует понимать, что выходной сигнал (SN) на выходе 420 составляет предпочтительно сигнал полной величины (от 0 до 2,5 В).

Как отмечалось выше, сигнал ОССНТ первоначально устанавливается на ВыхНН, а /ОССНТ и SNx первоначально устанавливаются на ВыхВН. Сигнал SN первоначально устанавливается на высокое выходное напряжение полной величины. Соответственно, компаратор 410а усиливает высокое напряжение SNx минус низкое напряжение ОССНТ, вследствие этого обеспечивая высокий выходной сигнал. Компаратор 410b усиливает высокое напряжение SNx минус высокое напряжение /ОССНТ, обеспечивая усиленный шумом неизвестный выходной сигнал. Выбором переключателя 415 управляют один или более соответствующих контроллеров, причем каждый контроллер работает в соответствии с критериями, согласно которым каждый переключатель должен быть открыт или закрыт, в данном примере посредством логических схем 425 функции "исключающее ИЛИ" (ИС ИЛИ) и входного сигнала логического элемента "исключающее ИЛИ". Более конкретно, схема 425а функции ИС ИЛИ сравнивает усиленный сигнал ОССНТ полной величины (VT) с выходным сигналом SN и генерирует управляющий сигнал для управления переключателем 415а. Схема 425b функции ИС ИЛИ сравнивает сигнал /ОССНТ полной величины (/VT) с выходным сигналом SN и генерирует управляющий сигнал для управления переключателем 415b. В этом исходном состоянии только сигналы ОССНТ и, соответственно, VT низкие, вследствие этого заставляя схему 425а ИС ИЛИ замкнуть переключатель 415а. В соответствии с этим выходной сигнал (высокий) компаратора 410а достигает выхода 420. Схема 425 ИС ИЛИ заставляет переключатель 415Ь разомкнуться, вследствие чего предотвращая поступление нежелательного выходного сигнала из компаратора 410b. Приемное устройство 405 остается устойчивым.

Следуя иллюстрируемому на фиг.3В примеру, несимметричный сигнал SNx переходит к низкому напряжению. Как всегда, сигналы ОССНТ и /ОССНТ переходят противоположно друг другу. Соответственно, как только ОССНТ и /ОССНТ достигают заранее определенной разности между ними (предпочтительно 250 мВ), происходит переход VT и /VT. Точно так же, как только ОССНТ и SNx переходят к заранее определенной разности между ними (предпочтительно 250 мВ), выходной сигнал компаратора 410а также осуществляет переход (к низкому выходному напряжению). Следует понимать, что путь от внешнего сигнала SNx до вырабатывания выходного сигнала SN и каждый путь для формирования сигнала полной величины VT и /VT включает в себя один компаратор 410 или 435 и два инвертора 430 или 440. Таким образом, каждая схема ИС ИЛИ 425 принимает новые входные сигналы, основанные на скорости сравнения компараторов 410 и 435. В этом примере, как очевидно из показанной на фиг.3В примерной временной диаграммы, ОССНТ и /ОССНТ достигают заранее определенной разности в то же самое время, когда ОССНТ и SNx достигают такой же заранее определенной разности. Соответственно, схема ИС ИЛИ 425а продолжает принимать разностные входные сигналы, вследствие этого сохраняя тот же самый переключатель 415а замкнутым и позволяя низкому выходному напряжению компаратора 410а проходить к выходу 420. Приемное устройство 405 все еще остается устойчивым.

Продолжая все еще следовать примеру фиг.3В, несимметричный сигнал SNx не переходит. Как всегда, сигналы ОССНТ и /ОССНТ переходят относительно друг друга. Соответственно, разблокированный в данный момент компаратор 410а продолжает запускать низкое выходное напряжение. Когда сигналы ОССНТ и /ОССНТ достигают заранее определенной разности относительно друг друга, но прежде, чем ОССНТ достигает такого же напряжения, как SNx (вследствие этого избегая возможности неопределенного состояния выходного сигнала), схема ИС ИЛИ 425а выключается, а схема ИС ИЛИ 425b включается. Следует понимать, что с момента времени, когда сигнал /ОССНТ начинает повышаться, компаратор 410b может запускать низкое выходное напряжение. Приемное устройство 405 все еще является устойчивым.

Каждое приемное устройство 405 может легко обнаруживать и усиливать очень маленькие сигналы порядка 100-250 мВ. Если в несимметричном сигнале SNx произошел переход, выходной сигнал SN имеет новый уровень, противоположный его предыдущему уровню сигнала. Поскольку и сигнал ОССНТ (или /ОССНТ), и несимметричные сигналы осуществили переход, к сигнальной выходной клемме все еще подсоединен тот же самый компаратор 410. Если несимметричные сигналы SNx не осуществили переход, то выходной сигнал SN не изменяется, компаратор 410, подсоединенный в начале перехода, отсоединяется от выхода после того, как приемное устройство ОССНТ и /ОССНТ усилит свое новое двоичное состояние (VT и /VT), а другой компаратор 410, который имеет противоположный сигнал /ОССНТ (или ОССНТ), подсоединяется для обеспечения выходного сигнала. Вследствие этого на выходе восстанавливается старый уровень.

Следует понимать, что приемное устройство 405 можно выполнить, не используя схемы ИС ИЛИ и что соответствующие критерии переключения также могут меняться соответствующим образом. Его можно выполнить, используя известную полярность сигналов ОССНТ и /ОССНТ в начальном цикле и всех несимметричных сигналов, начинающихся на высоком уровне. Сигналы ОССНТ и /ОССНТ осуществляют переход в каждом цикле. Таким образом, их полярность в каждом цикле можно определять путем исследования синхронизирующего импульса системы в синхронной системе и определения начала цикла в четных циклах синхронизирующих импульсов (то есть в четном цикле синхронизирующих импульсов сигнал ОССНТ низкий, а /ОССНТ высокий). После этого контролируется только выходной сигнал "SN", чтобы подсоединять и отсоединять компараторы 410, основываясь на том, изменяет ли состояние выходной сигнал SN каждый цикл или нет. Если выходной сигнал SN изменяет состояние, оставляется только подсоединенный компаратор. Если выходной сигнал SN не изменяется, подсоединенный компаратор отсоединяется и подсоединяется другой компаратор, и т.д.

Кроме того, следует также понимать, что воплощающая изобретение система позволяет подавать все сигналы к источникам с низким полным сопротивлением, позволяет все сигналы представить через напряжение и шумовые условия, фактически отличающейся помехоустойчивости, и позволяет снизить размах напряжения по сравнению с другими технологиями передачи несимметричных сигналов типа ШОП, ВСЛСП или ЛСПГ. Небольшой размах в 0,5 В, выполняемый в этом примерном варианте осуществления, допускает очень высокие скорости передачи сигнала со значительно меньшим потреблением электроэнергии по сравнению с другими существующими технологиями передачи несимметричных сигналов. Далее следует понимать, что каждое приемное устройство 405 усиливает несимметричные сигналы SNx во время перехода сигналов без необходимости использования обычных синхронизирующих импульсов или других синхронизирующих сигналов, за исключением сигналов ОССНТ, /ОССНТ и их усиленных версий VT и /VT.

Фиг.5 представляет графическую схему программы, иллюстрирующую способ 500 передачи сигналов от ведущего устройства 205 по линии передачи 215 в приемное устройство 405. Способ 500 начинается с того, что ведущее устройство 205 на этапе 505 устанавливает сигнал ОССНТ на значение ВыхНН, а все несимметричные сигналы (/ОССНТ и SNx) на ВыхВН, и на этапе 510 устанавливает все несимметричные выходные сигналы (SN) приемного устройства на высоту полной величины. Приемное устройство 405 на этапе 515 подсоединяет компаратор 410а, который сравнивает сигнал ОССНТ с каждым несимметричным сигналом SNx, к выходу 420 приемного устройства 405. Приемное устройство 405 на этапе 517 позволяет всем сигналам устанавливаться в линиях передачи. Этапы 505-517 относятся к инициализации системы.

На этапе 520 ведущее устройство 205 одновременно приводит сигналы ОССНТ и /ОССНТ в их противоположные состояния и все несимметричные сигналы SNx к их требуемым уровням. На этапе 530 приемное устройство 405 сравнивает несимметричный сигнал SNx с сигналами ОССНТ и /ОССНТ в соответственных компараторах 410. На этапе 540 приемное устройство 405 определяет, осуществил ли переход несимметричный сигнал. Если осуществил, то приемное устройство 405 на этапе 545 передает результат на выход 420 и сохраняет тот же самый компаратор 410 подсоединенным к клемме 420. Если нет, то приемное устройство 405 на этапе 550 отсоединяет прежний компаратор 410, подсоединяет другой компаратор 410 к выходу 420 и сохраняет тот же самый выходной сигнал (SN). На этапе 555 передающее устройство 405 определяет, продолжается ли пакет сигналов. Если продолжается, то способ 500 возвращается к этапу 520. В противном случае способ 500 заканчивается.

Фиг.6А представляет принципиальную схему, иллюстрирующую медленное включение и медленное выключение ведущего устройства 205 для несимметричного сигнала в первом варианте осуществления, называемом передающим устройством 600. Передающее устройство 600 включает в себя понижающее устройство 605 n-канальной МОП-структуры, подсоединенное к линии 610 передачи для точной подстройки размаха выходного сигнала на 500 мВ ниже НОН. Понижающее устройство 605 n-канальной МОП-структуры включает в себя понижающий транзистор Т1 n-канальной МОП-структуры, исток которого подсоединен к линии 610 передачи, сток подсоединен к заземлению, а затвор подсоединен к схемам 620 управления сдвигом. Схемы 620 управления сдвигом включают в себя инвертор КМОП (комплиментарная МОП-структура), содержащий два транзистора Т2 и Т3, подсоединенные между двумя резисторами R1 и R2. Вход инвертора КМОП подсоединен к устройству 625 управления сигналом. Например, для генерирования сигнала ОССНТ или /ОССНТ устройство 625 управления сигналом может быть генератором. Следует понимать, что величину понижения можно регулировать, используя во время инициализации регистр (не показанный) и последовательный штыревой контакт (не показанный), чтобы установить правильный размах напряжения для любых изменений процесса или устройства. Для управления также можно использовать другие способы, аналогичные использованию приемов обратной связи, показанные в работе Ганса Шумахера (Hans Schumacher) и др. "Поднаносекундный выходной буфер КМОП на правильной эмиттерно-связанной логике", журнал "Твердотельные схемы", т.25 (1), стр. 150-154 (февраль 1990 г.). Поддерживая ток на уровне 20 мА и имея параллельные оконечные нагрузки 50 Ом на обоих концах линии 610 передачи (управляемой R1 и R2), получают размах 500 мВ при всех условиях. Чтобы иметь время медленного нарастания и спада выходного сигнала и минимизировать отражения, связью по сигналу и шумами многократного поля коммутации схемы 665 управления сдвигом управляют понижающим транзистором Т1 с целью его медленного отпирания и запирания. Предпочтительная максимальная скорость нарастания выходного напряжения составляет 1,6 нс/В с периодами перехода 0,8 нс для 500 мВ.

Для равномерного перехода пилообразного сигнала при данном способе предпочтительная максимальная скорость нарастания сигналов превышает в четыре раза сумму задержек двух инверторов и задержки схемы "исключающее ИЛИ". При технологии 0,25 мкм КМОП с рабочим напряжением 2,5 В задержка инвертора составляет 50 пикосекунд, а задержка схемы "исключающее ИЛИ" составляет приблизительно 120 пикосекунд. Таким образом, предпочтительная максимальная скорость нарастания выходного напряжения составляет приблизительно 880 пикосекунд. Для сигналов, передаваемых с частотой свыше 600 МГц, максимальная скорость нарастания сигнала составляет предпочтительно меньше 110% скорости передачи сигнала. Предпочтительная максимальная скорость нарастания выходного напряжения для экспоненциальных сигналов немного выше, если сигнал достигает 75% его установившегося значения ранее, чем за 3/4 времени перехода. Дифференциальные сигналы предпочтительно пересекаются на полпути перехода напряжения. В пределах 3/4 пути перехода напряжения сигналы имеют разность порядка 250 мВ, которая может быть быстро преобразована в сигнал большого размаха. Для избежания усиления шума и предотвращения подачи сигнала на выход приемного устройства при приеме непереходных, несимметричных сигналов время перехода между 75% и окончательной величиной сигнала предпочтительно выше, чем сумма задержек двух инверторов и задержки схемы "исключающее ИЛИ". Следует понимать, что максимальная скорость нарастания выходного напряжения может быть настолько большой, что усиленный шум достигнет выхода компаратора 410, выходной сигнал которого подается на выход 420. То есть при приеме непереходного сигнала переключатели 415 переключают состояние прежде, чем выходной сигнал компаратора изменит состояние на основании усиления шума. Выходной сигнал подсоединенного в данный момент компаратора 410 приближается к неопределенному состоянию (усиленный шум). Переключатели 415 должны переключать состояния прежде, чем образуется неопределенный выходной сигнал. Далее следует понимать, что рассогласование элементов, допуски на изготовление и отражение сигнала приводят к скорости, при которой выходной сигнал компаратора 410 достигает неопределенного состояния. По мере улучшения технологии появится возможность получения задержек на логических элементах, более быстрых максимальных скоростей нарастания выходного напряжения и более быстрых скоростей передачи сигнала.

Фиг.6В представляет принципиальную схему, иллюстрирующую ведущее устройство 205, имеющее регулируемые максимальные скорости нарастания сигнала и сдвиг между сигналами, в другом примерном варианте осуществления, называемом передающим устройством 650. Передающее устройство 650 включает в себя понижающее устройство 655 n-канальной МОП-структуры, подсоединенное к линии 610 передачи для точной подстройки размаха выходного сигнала на 500 мВ ниже НОН. Понижающее устройство 655 n-канальной МОП-структуры включает в себя подсоединенные параллельно понижающие транзисторы 660 n-канальной МОП-структуры, каждый из которых имеет исток, подсоединенный к линии 610 передачи, сток, подсоединенный к заземлению, и затвор, подсоединенный к схемам 665 управления сдвигом. Схемы 665 управления сдвигом включают в себя инвертор КМОП, содержащий два транзистора Т2 и Т3, подсоединенные между двумя наборами 670 и 675 из соединенных параллельно резисторов. Вход инвертора КМОП подсоединен к устройству 625 управления сигналом. Наборы 670 и 675 резисторов настраивают периоды нарастания и спада. Следует понимать, что периоды нарастания и спада предпочтительно оказываются по возможности симметричными, чтобы иметь среднюю точку перенесения всех сигналов и чтобы происходило одновременное считывание всех сигналов дифференциальными приемными устройствами. Достижение симметрии и установление максимальной скорости нарастания выходного напряжения и размаха выходного сигнала можно получить во время стадии испытания посредством расплавления плавких предохранителей (не показанных) или во время инициализации на панели, устанавливая регистр (не показанный).

Следует понимать, что время перехода сигнала может быть немного выше, чем скорость передачи сигнала. В некоторых интенсивно нагруженных шинах размах можно увеличивать, учитывая потери при передаче, все еще представляя 500 мВ для легкости считывания приемным устройством 210. Далее следует понимать, что возможны различные максимальные скорости нарастания выходного напряжения, экспоненциальные периоды перехода и размахи напряжения, основываясь на технологии, нагрузке и захвате приемного устройства и задержках разрешающих способностей. Периоды перехода возможны даже немного выше скорости передачи сигнала в случае перехода сигналов, достигающего 90-95% от их конечного значения, при пакетной передаче. Во время испытания регулируется также сдвиг между несимметричными сигналами и ОССНТ и /ОССНТ, используя при этом величину понижающей n-канальной МОП-структуры и резисторы в логической схеме, применяя известные способы, типа лазерного перегорания плавкого предохранителя или установки кода регистра, для достижения формы волны сигнала, как показано на фиг.10. Как изображено на фиг.10, все несимметричные сигналы SNx должны совпадать или оказываться меньше, чем за 50 пикосекунд до перехода ОССНТ и /ОССНТ. Этот сдвиг можно отрегулировать после испытания, чтобы он находился в этом диапазоне.

Фиг.7А-7D иллюстрируют альтернативные варианты осуществления каждого показанного на фиг.4 приемного устройства 405 сигналов. Следует понимать, что компараторы 410 приемного устройства 405 должны функционировать во время каждого цикла, требуя небольшой задержки на получение и разрешение, не потребляя входной ток и не вводя ток обратно в сигнальные линии. Всем этим требованиям удовлетворяет обычный дифференциальный усилитель. Рассмотрим фиг.7А, на которой в приемном устройстве 210 используются двойные дифференциальные усилители 702, один дифференциальный усилитель 702а для сравнивания сигнала SNx с ОССНТ, а другой дифференциальный усилитель 702b для сравнивания сигнала SNx с /ОССНТ. Для полноты представлен краткий обзор дифференциальных усилителей 702. Дифференциальный усилитель 702 всегда разблокирован. Основываясь на размерах канала, когда напряжение ОССНТ выше, чем напряжение SNx, в транзисторе Т10 МОП-структуры с каналом р-типа возбуждается больший ток, вследствие чего обеспечивая высокое выходное напряжение в узле 707 (близко к VCC или 2,5 В). Когда напряжение ОССНТ меньше, чем напряжение SNx, через транзистор Т11 МОП-структуры с каналом n-типа проходит больший ток, вследствие этого обеспечивая низкое выходное напряжение в узле 707 (близкое к VSS или 0 В). Дифференциальный усилитель преобразовывает входной сигнал 0,5 В (небольшой размах) в выходной сигнал большого размаха (0 В-2,5 В).

Выходные сигналы дифференциальных усилителей усиливаются и инвертируются инвертором 704, проходят через логические схемы 706 передачи КМОП и связываются вместе в узле 708. Логические схемы 706 передачи функционируют избирательно в зависимости от усиленного состояния предыдущего сигнала (SN), подвергнутого операции "исключающее ИЛИ" с усиленным состоянием ОССНТ или /ОССНТ, то есть VT или /VT, соответственно. Функцию "исключающее ИЛИ" конструируют так, чтобы она была устойчивой без сбоев в случае небольших изменений согласования во времени между SN, VT и /VT, достигающих своих соответственных логических уровней.

Показаны различные варианты осуществления. Фиг.7А в качестве альтернативного варианта осуществления 700 иллюстрирует всегда разблокированные дифференциальные усилители, где только логические схемы передачи избирательно разблокируются для небольшого количества устройств и более высокой скорости. Фиг.7В иллюстрирует одновременно разблокированные или блокированные дифференциальный усилитель и логические схемы передачи в качестве альтернативного варианта осуществления 720. Фиг.7С иллюстрирует дифференциальные усилители, разблокируемые одной и той же функцией "исключающее ИЛИ" в случае более низкой мощности, быстро блокирующие логические схемы передачи во время перехода выходного сигнала "исключающее ИЛИ" и медленно разблокирующие логические схемы передачи после установления схемы "исключающее ИЛИ" в качестве альтернативного варианта осуществления 740. Фиг.7D иллюстрирует Р-канальные дифференциальные усилители с напряжением оконечной нагрузки 1,2 В для применений более низкой мощности в качестве альтернативного варианта осуществления 760. Все логические схемы дифференциальных усилителей могут быть разблокированы для снижения мощности, когда приемное устройство или когда элемент не выбраны или элемент находится в режиме глубокого выключения электропитания. Дифференциальный усилитель можно разблокировать путем запирания транзистора Т11.

Используя 1,2 В оконечную нагрузку и приемное устройство 405, как показано на фиг.7D, можно дополнительно снизить потребление энергии еще на 33%. То есть, размах напряжения будет от 1,2 до 0,7 В, обеспечивая удовлетворительные границы, исходя из дрожания заземления и снижения потребления энергии для портативных систем. Рабочая частота может быть сравнима с меньшим количеством устройств на шинах, что является обычным в случае портативных устройств для меньшего коэффициента формы. Передающим устройством 205 все еще может быть понижающий транзистор Т1 n-канальной МОП-структуры или параллельное соединение понижающих элементов 660 n-канальной МОП-структуры. Работа приемного устройства аналогична, за исключением того, что дифференциальный усилитель 702 становится зеркальным изображением, вследствие этого увеличивая приблизительно в два раза емкость логической схемы на сигналах, поступающих в Р-канальную схему, для сравнимых характеристик, благодаря увеличенному размеру устройства Р-канального типа. Вместо показанных дифференциальных усилителей в качестве альтернативы можно использовать другие конфигурации дифференциальных усилителей, которые быстро преобразовывают дифференциальные сигналы небольшого размаха в дифференциальные сигналы большого размаха. Специалистам в данной области техники должно быть ясно, что в другом варианте осуществления можно использовать два различных напряжения НОН: одно для сигналов, равных 1,8 В, с размахом 500 мВ и другое для осциллирующих опорных сигналов, равных 1,7 В, с размахом 300 мВ. Все сигналы осуществляют переход в одно и то же время и имеют аналогичные максимальные скорости нарастания выходного напряжения. Одна и та же пара передающего и приемного устройств может управлять системой с множеством напряжений НОН.

Следует понимать, что точка смещения постоянного тока каждого дифференциального усилителя в приемном устройстве 405 образована так, чтобы выходное напряжение приемного устройства 405 было ниже половины величины VCC, когда оба напряжения малого размаха (несимметричного сигнала SNx и ОССНТ или /ОССНТ разблокированного дифференциального усилителя) близки к значению ВхВН, и выше половины величины VCC, когда оба напряжения малого размаха близки к значению ВхНН. Это смещение постоянного тока учитывает соответствующие предел и сохранение выходного сигнала SN, когда несимметричный сигнал SNx не изменяет состояние, а ОССНТ или /ОССНТ разблокированного дифференциального усилителя закрывает дифференциальный сигнал прежде, чем он отсоединяется.

Поскольку приемное устройство 405 функционирует во время перехода сигнала в случае несимметричного сигнала небольшого размаха, концепция времени установления и удержания соединения от точно указанного времени после того, как уровень сигнала достигает значения ВхВН/ВхНН, или ОН в предыдущих способах передачи сигналов, больше не применяется. Точно так же отсутствует ОН (опорное напряжение) для сравнения с напряжением сигнала. При устранении тактовых импульсов, необходимых для установления и удержания соединения, и тактовых импульсов, необходимых, чтобы разблокировать границы напряжения для считывания вблизи ОН, рабочая частота значительно увеличивается с понижением потребления энергии. Далее все приемные устройства 405 самосинхронизируются без необходимости общих синхронизирующих импульсов, позволяя регулировать приемные устройства 405 по отдельности для устранения сдвига передачи на уровне плат или модулей.

Фиг.8А и 8В представляют принципиальные схемы, иллюстрирующие детали схем, показанных на фиг.4, компараторов 435. Каждый компаратор 435 включает в себя дифференциальный усилитель 802 (фиг.8А) или 852 (фиг.8В), подобный показанному на фиг.7А дифференциальному усилителю 702, и множество соединенных последовательно инверторов 804 (фиг.8А) или 854 (фиг.8 В). Выходные сигналы полной величины компараторов 802 и 852 (VT1, VT2, VT3, /VT1, /VT2 и /VT3) передаются на все схемы ИС ИЛИ 425 несимметричных приемных устройств (фиг.4). Выбор сигнала VT1, VT2 или VT3 определяется на основании проверки скорости сигнала, по существу равной скорости на пути образования выходного сигнала SN приемного устройства 405.

Фиг.9 представляет принципиальную схему, иллюстрирующую приемные устройства 405 с отдельно регулируемыми задержками, с целью устранения сдвига во время передачи и преобразовывания компараторами 410 небольшого размаха в большой размах. Для настраивания рабочей частоты или размаха напряжения на оптимальные характеристики каждое приемное устройство 405 имеет регистр 905 для запоминания данных, чтобы обеспечить подачу одной из трех величин VT1 и /VT1, VT2 и /VT2 или VT3 и /VT3 на ИС ИЛИ 425 (фиг.4).

Фиг.11 представляет изображение в перспективе монтажной схемы объединенного ведущего устройства 1100 для двунаправленной подачи сигналов. Ведущее устройство 1100 включает в себя приемные устройства 405 и возвратные передающие устройства 1105, соединенные вместе. Более конкретно, каждый принимаемый несимметричный сигнал типа сигнала S0 подается на соответствующее приемное устройство 405 типа приемного устройства S0 и на соответствующее передающее устройство 1105 типа передающего устройства Т0. Все несимметричные сигналы SNx предпочтительно можно группировать вместе с единственной парой опорных сигналов /ОССНТ и ОССНТ. Однако специалистам в данной области техники должно быть ясно, что для данной рабочей частоты ввод ОССНТ и /ОССНТ и разбаланс сигнала снижают количество сигналов SNx, которые могут группироваться вместе. Как показано на фиг.11, расположение выполнено так, чтобы емкости, сопротивления и индуктивности в ОССНТ, /ОССНТ и всех несимметричных сигналах SNx были сбалансированы. Кроме того, поскольку сигналы ОССНТ и /ОССНТ проходят во все приемные устройства 405, общую нагрузку на ОССНТ и /ОССНТ нужно минимизировать.

Используя устройства с очень низким рассеиванием мощности и компактным физическим уплотнением, шину можно делать по возможности короче, что, в свою очередь, обеспечит краткое время распространения и высокие скорости передачи данных. Как показано на фиг.2В, оканчивающиеся резисторами линии передачи с управляемым полным сопротивлением могут функционировать со скоростями передачи сигнала 1 ГГц (1-наносекундный цикл). На характеристики линий передачи сильно влияет нагрузка, создаваемая интегральными схемами типа устройств ДОП, смонтированными на шине. Эти интегральные схемы добавляют сосредоточенную емкость в линии, которая снижает полное сопротивление линий и уменьшает скорость передачи. В нагруженных условиях полное сопротивление шины вероятно составляет порядка 25 Ом, а скорость распространения 7,5 см/нс. Следует принимать меры, чтобы не запускать шину от двух устройств в одно и то же время. Так, для шин менее приблизительно 12 см необходим один мертвый цикл (например, 2 нс), чтобы организовать шину для переключения с одного драйвера на другой драйвер. В случае более длинных шин может оказаться необходимым больше одного цикла для расположения сигналов, прежде чем сможет запустить сигнал новое передающее устройство. В отличие от ШОП длина шины снижает рабочую частоту в пакетном режиме от того же самого устройства.

Фиг.12А представляет изображение в перспективе блок-схемы, иллюстрирующей двухточечную систему 1200, которая включает в себя двунаправленное ведущее устройство 1205, подсоединенное через линии 1215 передачи к двунаправленному подчиненному устройству 1210. Линии 1215 передачи включают в себя верхние линии 1220 сигнала SNx, нижние линии 1225 сигнала SNx и линии 1230 сигналов ОССНТ и /ОССНТ. На фиг.12В представлено изображение в перспективе блок-схемы, иллюстрирующей двухточечную систему 1200, включающую оконечные сопротивления 1235, использующую внутри Р-канальные элементы с заземленными затворами. Это устраняет потребность в пространстве для подсоединения внешних сопротивлений и снижает стоимость. Следует понимать, что оконечные сопротивления 1235 можно выполнять, используя вместо Р-канальных элементов с заземленными затворами внутренние резисторы. Для двунаправленных сигналов в шине предпочтительным является завершение обоих концов соответствующим волновым сопротивлением. Поскольку блоки внутри микросхемы физически расположены ближайшим образом, резисторы для согласования полных сопротивлений не нужны. Достаточно иметь небольшие нагрузочные устройства. Точно так же, когда связи внутри микросхемы физически являются соседними, резисторы для согласования полных сопротивлений можно заменить небольшими нагрузочными элементами, чтобы снизить стоимость и энергию и сохранить ту же самую максимальную скорость нарастания выходного напряжения.

Следует понимать, что для устройств типа ДОП ЛПС (SLDRAM) (динамической оперативной памяти линии передачи сигналов), СД ОП ДСПД (DDR SDRAM) (синхронной динамической ОП с двойной скоростью передачи данных) или устройств СОП ДСПД (DDR SRAM) (статической ОП с двойной скоростью передачи данных), где сигналы передаются и принимаются одновременно, требуется множество шин. Фиг.13А представляет изображение в перспективе блок-схемы, иллюстрирующей объединенную однонаправленную и двунаправленную систему 1300 для ДОП ЛПС на единственной интегральной схеме. Система 1300 включает в себя ведущее устройство 1305 (например, контроллер памяти), подсоединенное через линии 1315 передачи к подчиненным устройствам 1310 (например, ДОП ЛПС). Ведущее устройство 1305 передает сигналы адреса и управления по линиям 1320 и 1325 адреса и управления, передает / принимает сигналы данных по линиям 1330 и 1335 данных, передает по линиям 1340 ОССНТ и /ОССНТ первый набор опорных сигналов ОССНТ и /ОССНТ (то есть ОССНТ0 и /ОССНТ0) для проверки сигналов адреса и управления и передает второй набор опорных сигналов ОССНТ и /ОССНТ (то есть ОССНТ1 и /ОССНТ1) в подчиненные устройства 1310. Участок адреса и управления системы 1300 управляет однонаправленными сигналами, необходимыми только для подчиненных устройств 1310. Участок данных системы 1300 является двунаправленным, основанным на том, определен ли управляющий сигнал для операции СЧИТЫВАНИЯ или ЗАПИСИ.

В случае ДОП ЛПС 40-битовая команда и адрес посылаются в пакете из четырех 40-битовых слов. Сигналы ОССНТ0 и /ОССНТ0, которые можно называть дифференциальными синхронизирующими импульсами системы, действуют на частоте 500 МГц. Система фазовой автоматической подстройки частоты (не показанная) используется для автоматической подстройки частоты синхронизации и согласования во времени для различных внутренних целей и управления выводом данных с помощью ОССНТ1 и /ОССНТ1 на обоих концах для частоты передачи данных 1 ГГц. Все высокочастотные сигналы оканчиваются на обоих концах шины их волновым сопротивлением. Оконечная нагрузка на конце контроллера памяти может включать в себя внешние сопротивления, внутренние сопротивления или внутренние Р-канальные элементы с заземленными затворами, поскольку этот контроллер памяти обычно представляет собой ведущее устройство и является резидентным. Поскольку количество компонентов (устройств ДОП ЛПС) 1310 (которые функционируют как подчиненные устройства) переменное, компоненты 1310 предпочтительно оканчиваются внешними резисторами на конце линий передачи. 18-Битовые двунаправленные шины 1330 и 1335 передачи данных функционируют на той же частоте, как синхронизирующие импульсы системы для синхронизации, и посылают данные в восьми 18-битовых словах четырьмя циклами синхронизирующих импульсов (8 нс), или 2,25 гигабайта в секунду, из одного устройства ДОП ЛПС. Следует принимать меры в отношении балансирования нагрузки на ОССНТ0 и /ОССНТ0 путем добавления фиктивных логических схем и линий, чтобы она была сравнимой с ОССНТ1 и /ОССНТ1. Это балансирование нагрузки делает максимальной скорость нарастания выходного напряжения, обусловленную аналогичной нагрузкой, и допускает подобные пределы рабочего режима для всех сигналов.

Когда требуется более высокая полоса пропускания, система 1350 может использовать четыре шины, как показано на фиг.14В. Два отдельных канала ДОП ЛПС 1310 используются с одним контроллером 1305 памяти. Эта конфигурация обеспечивает максимальную полосу пропускания данных 4,5 гигабайта в секунду. Хотя система 1350 не требует синхронизирующих импульсов для передающего устройства 1305 или приемного устройства 1310, система 1350 может использовать синхронизирующие импульсы для передачи данных в конкретный момент времени и с определенной частотой для простоты проверки и возможности использования с существующими протоколами синхронных устройств ДОП и СОП. Может оказаться желательным использовать на микросхеме умножитель медленных синхронизирующих импульсов или внутренний кольцевой генератор, чтобы передать данные на высокой частоте без высокоскоростных тактовых импульсов для синхронизации, с целью снижения шума и энергии системы. Следует понимать, что специалисты в данной области техники могут развивать положения данного изобретения для получения систем с различными размерами, синхронных или асинхронных, с широкой полосой пропускания.

Ниже приведены пять концепций, дополнительно объясняющих показанные на фиг.4 схемы 210 ввода и вывода.

Первая концепция касается наличия комплиментарных опорных сигналов. Как показано на фиг.14А, в известных системах используется опорный сигнал с фиксированным напряжением "ОН", величина которого находится в области средней точки логического высокого уровня напряжения (ВыхВН) и логического низкого уровня (ВыхНН). Генератор ОН (не показанный) обычно имеет некоторое смещение постоянного тока от изменения в электропитании, используемом для его генерирования, это изменение обозначено ссылочными позициями "ОНв" и "ОНн". Он также имеет некоторый шум переменного тока из-за мгновенных колебаний напряжения источника электропитания, дребезга заземления, емкостной связи и индуктивной связи с соседними сигналами. Дифференциальный размах для компаратора, используемого в известном приемном устройстве, иллюстрируется стрелками. Следует отметить, что в самом плохом случае дифференциальный сигнал в прототипе составляет порядка 1/3-1/4 от общего размаха напряжения сигнала.

Как показано на фиг.14В, в системах и способах по изобретению используются комплиментарные опорные сигналы ОССНТ и /ОССНТ, которые имеют такой же размах напряжения, как любой сигнал (например, данных или управления). В предпочтительном варианте осуществления этот размах напряжения составляет 500 мВ с логическим высоким напряжением (ВыхВН) 1,8 В и логическим низким уровнем (ВыхНН) 1,3 В. Следует понимать, что во время работы этой системы передачи сигналов среднее значение комплиментарных опорных напряжений находится в области средней точки между ВыхВН и ВыхНН в каждый момент времени. Сигналы и комплиментарные опорные сигналы имеют одни и те же время перехода и размахи напряжения и начинаются в одно и то же время из одного и того же источника (одного и того же устройства для внутренней части микросхемы или одного и того же общего местоположения для внутренней части микросхемы) с целью посылки в приемное устройство. Другими словами, комплиментарные опорные сигналы выглядят точно так же, как любой другой сигнал. Однако комплиментарные опорные сигналы переключаются из одного состояния в другое каждый раз, когда нужно передавать другие сигналы. Поскольку комплиментарные опорные сигналы используют электропитание и заземление в одно и то же время, весь шум представляет синфазный режим. Следовательно, необходимые в прототипе изменения ОН (ОНв и ОНн) размаха сигнала не нужны в системах и способах по настоящему изобретению. Благодаря двоичному характеру цифровой передачи сигналов, один комплиментарный опорный сигнал всегда имеет противоположную полярность относительно сигнала в начале перехода опорного сигнала и в конце перехода опорного сигнала. Таким образом, присутствие одного опорного сигнала имеет общий размах порядка 500 мВ в какой-то данный момент времени, вследствие этого позволяя компаратору легче считывать напряжение сигнала, чем в известной системе, которая имеет только 1/3-1/4 общего размаха сигнала. Время перехода сигнала и опорного сигнала могут составлять половину времени перехода, необходимого в прототипе, для достижения такого же дифференциального сигнала во время изменения сигнала. Специалистам в данной области техники должно быть ясно, что для получения оптимальных характеристик ВыхВН и ВыхНН следует устанавливать на величину где-то между несколькими сотнями милливольт ниже напряжения источника питания и несколькими сотнями милливольт выше значения заземления, с разностью между ними в 500 мВ. Разность можно дополнительно уменьшить до 200-300 мВ, если уменьшены рассогласования элементов и сигналы имеют небольшие отражения или не имеют отражений, особенно в связях внутри микросхемы.

Вторая концепция касается наличия двойных компараторов для каждого поступающего сигнала. Рассмотрим снова фиг.4, поскольку сигнал сравнивается с обоими комплиментарными опорными сигналами, каждое приемное устройство 210 имеет два компаратора. Один сравнивает сигнал SNx с ОССНТ, а другой сравнивает сигнал SNx с /ОССНТ. В начале пакетного перехода компаратор с полным дифференциальным сигналом на его входе подсоединяется к выходу приемного устройства 210, а другой компаратор, который не имеет дифференциального сигнала, отсоединяется от выхода приемного устройства 210. Это выполняется с помощью инициализации. Если сигнал SNx и подсоединенный опорный сигнал осуществляют переход, то компаратор быстро считывает сигнал как дифференциальный усилитель, быстро усиливает сигнал и приводит выход в противоположное состояние. Если сигнал SNx не осуществляет переход (то есть переходят только опорные сигналы), то дифференциальный входной сигнал на компаратор, который поступает в начале перехода опорного сигнала, постепенно уменьшается на протяжении времени перехода до тех пор, пока в конечном счете не будет обеспечиваться нулевой дифференциальный входной сигнал. Дифференциальный входной сигнал на компаратор, который отсоединен в начале перехода опорного сигнала, постепенно увеличивается на протяжении времени перехода до тех пор, пока в конечном счете не будет обеспечен полный дифференциальный сигнал. Первоначально подсоединенный компаратор без дифференциального сигнала в конце перехода отсоединяется, а первоначально отсоединенный компаратор с полным дифференциальным сигналом в конце перехода подсоединяется. Настоящее изобретение для считывания одного сигнала использует два компаратора. Далее двоичный характер цифровых сигналов гарантирует полный размах сигнала на одном из компараторов в начале каждого возможного достоверного перехода.

Третья концепция касается инициализации. Поскольку к выходу приемного устройства в каждый момент времени подсоединен только один компаратор, для надлежащей работы важно иметь компаратор с полным дифференциальным входным сигналом, подсоединенный к выходу приемного устройства 210 в начале пакетного сигнала. Следовательно, все сигналы S0x-SNx инициализируются на логический высокий уровень ВыхВН. Благодаря выключению всех драйверов, инициализации ОССНТ на ВыхНН, инициализации /ОССНТ на ВыхВН и подачи сигналов на нагрузочные резисторы или нагруженные р-канальные элементы с включенными их затворами и истоками, подсоединенными к НОН (НОН составляет 1,8 В), снижается потребление энергии. Выходы приемных устройств 210 для S0-SN предварительно загружают до уровня VCC, используя показанный на фиг.16 р-канальный элемент 1615, с целью гарантирования логики управления (объясняемой ниже) для подсоединения компаратора с полным дифференциальным сигналом к выходу приемного устройства 210.

Четвертая концепция касается распознавания изменения сигнала. Как известно специалистам в данной области техники, характерная черта дифференциального усилителя заключается в усилении небольшой разности напряжений до большой разности напряжений. Коэффициент усиления по напряжению обычно составляет от 3 до 5, основываясь на размере устройства и согласовании транзистора. Инвертор, расположенный после дифференциального усилителя, обеспечивает дополнительное усиление для достижения почти полного размаха на основании выбора размера устройства. Быстродействие дифференциального усилителя и инвертора для достижения полного размаха зависит от дифференциального сигнала, поступающего на их вход. Как показано на фиг.15А, дифференциальный усилитель (и инвертор) 1501 может очень быстро усиливать переход и SNx, и ОССНТ 1500. Но, когда SNx не осуществляет переход, сигнал на дифференциальном усилителе снижается только до шума, и быстродействие становится намного меньше (на основании рассогласования и шума). Переходный сигнал SN' (выходной сигнал дифференциального усилителя и инвертора) показан пунктирной линией 1503. Область 1502 слева от переходного сигнала SN' 1503 отмечена символом "Изменение". Область справа от переходного сигнала SN' 1503 отмечена символом "Без изменения". Как установлено выше, когда сигнал не переходит, усилитель 1501 понижает сигнал только до шума, который показан как неопределенная область 1506. Период времени перед тем, как усилитель достигает неопределенной области 1506, обозначен как область 1504 переходящего промежутка. Это изобретение пользуется преимуществом временного промежутка, позволяя логике управления, описанной ниже, пропускать изменяющийся сигнал к выходу приемного устройства и предотвращать прохождение неопределенного сигнала. Выбирая надлежащие размеры элемента и моменты перехода, временной промежуток можно сделать достаточным для функционирования логики управления так, чтобы проходило "изменение сигнала", а "отсутствие изменения сигнала" и образующийся в результате сигнал неопределенного напряжения не проходили. Следует понимать, что некоторый уровень неопределенного напряжения может проходить до тех пор, пока он меньше логического порога следующего за ним элемента ИС ИЛИ, и другой компаратор может быстро восстанавливать уровень напряжения. Далее следует понимать, что временной промежуток зависит от размаха сигнала, времени перехода опорного сигнала, рассогласования процесса, отражения сигнала и т.д.

Пятая концепция касается логики управления. Рассмотрим фиг.15В, на которой логическая схема 1550 управления связывает соответствующий компаратор 1555 с выходом приемного устройства 1560 и основана на тактовых импульсах, образуемых дифференциальным усилителем с использованием ОССНТ, /ОССНТ и наличия выходного сигнала приемного устройства 1553. Логика 1550 управления использует ОССНТ, /ОССНТ и наличие выходного сигнала приемного устройства 1553. Рассматривая фиг.4, отметим, что инициализация входных сигналов S0x-SNx на ВыхВН, опорного сигнала /ОССНТ на ВыхВН, опорного сигнала ОССНТ на ВыхНН и выходных сигналов приемного устройства S0-SN на VCC соединяет соответствующие компараторы 410 с выходом 420 приемного устройства перед началом пакета. В случае переходного сигнала логика 1550 управления не изменяется, поскольку схемы 1565 управляющей логики НС ИЛИ выбирают соответствующие усиленный опорный сигнал и выходной сигнал приемного устройства. Поскольку и усиленный опорный сигнал ОССНТ, и SNx осуществляют переход, а пути задержки для усиленного опорного сигнала ОССНТ и для SNx до схемы ИС ИЛИ 1565 идентичны, ИС ИЛИ 1565 не выполняет переключение. В качестве альтернативы, если поступающий сигнал не осуществляет переход, прежний компаратор 1555, который был подсоединен, отсоединяется, а другой компаратор 1555, который не был подсоединен, теперь подсоединяется. Выходной сигнал приемного устройства не изменяется, и подсоединенный компаратор 1555 активно заставляет его восстановить уровень на выходе, если это требуется. Логика 1550 управления предназначена для того, чтобы действовать в течение временного промежутка 1504 между изменением сигнала 1502 и отсутствием изменения сигнала 1506, как объяснено выше.

Логика управления выполняется, используя отдельные схемы "исключающее ИЛИ" локально для каждого компаратора для более высокого быстродействия, лучшего регулирования ограничения времени и для улучшения пределов рабочего режима или регулирования относительно сдвигов и рассогласований. Также можно иметь все компараторы отсоединенными от их выходов приемного устройства, используя тактовые импульсы ОССНТ и /ОССНТ и один управляющий сигнал для всех приемных устройств сигнала одного канала шины, чтобы при ограничении времени в течение временного промежутка происходило снижение количества устройств в приемных устройствах. Это приводит к снижению рабочей полосы пропускания, поскольку надлежащий компаратор должен быть подсоединен к выходу приемного устройства перед началом следующего перехода.

Когда все эти элементы объединены вместе, вся система передачи сигналов работает со всеми сигналами S0x-SNx и /ОССНТ, начинающимися на уровне ВыхВН, всеми выходными сигналами приемного устройства, предварительно загруженными для VCC, и ОССНТ, начинающимся на уровне ВыхНН. Перед инициированием пакета сигналов с переходом комплиментарных опорных сигналов все компараторы с дифференциальным сигналом на них (SNx и ОССНТ) подсоединяются к выходам приемного устройства. В случае переходных сигналов, логика управления позволяет сигналам приводить выходной сигнал к противоположной величине полного напряжения. В случае непереходных сигналов логика управления отсоединяет сигналы от присутствующего компаратора для того, чтобы другой компаратор удерживал и/или восстанавливал выходной сигнал приемного устройства. Следующий переход происходит конвейерным образом, продолжаясь с перекрытием переходов логикой управления до тех пор, пока задержка логики управления не ограничит полосу пропускания или интервал времени, чтобы обеспечить следующий переход.

Как показано на фиг.16, приемное устройство несимметричного сигнала имеет дифференциальные усилители, стробированные сигналом отключения питания или разблокирования приемного устройства, для отключения энергии от приемного устройства, когда оно не используется. По сравнению с фиг.7А, инверторы заменены логическими элементами Не-И 1610, связанными с сигналом отключения питания или разблокирования приемного устройства. Далее нагрузочный транзистор 1615 подсоединен к узлу 708 своим стоком, к VCC своим истоком и к сигналу отключения питания или разблокирования приемного устройства своим затвором для предварительной загрузки SN до уровня VCC. Логический элемент Не-И 1615 после дифференциальных усилителей также достигает правильной полярности в сигнале SN, чтобы начать пакетный цикл. Требуемое начальное условие заключается в предварительной установке высокого уровня сигнала SNx, где SNx делается высоким посредством оконечного сопротивления или нагрузочного элемента в сигнальной линии, и низкого ОССНТ, и высокого /ОССНТ. Остальная часть работы приемного устройства уже описана. Р-канальный элемент на общем узле выхода логических схем передачи предназначен для быстрой предварительной загрузки до высокого уровня узла 708, в случае необходимости, во время включения энергии, или когда выходные сигналы схемы "исключающее ИЛИ" не достигли устойчивых уровней.

Используя устройства с очень низким рассеиванием мощности и компактным физическим уплотнением, шину можно делать по возможности короче, что, в свою очередь, обеспечивает краткое время распространения и высокие скорости передачи данных. Как показано на фиг.12, оканчивающиеся резисторами линии передачи с управляемым полным сопротивлением могут работать на скоростях передачи сигнала 1 ГГц (1-наносекундный цикл) или выше. На характеристики линий передачи сильно влияет нагрузка, вызываемая интегральными схемами типа устройств ОП, смонтированными на шине. Эти интегральные схемы добавляют сосредоточенную емкость к линиям, которая понижает полное сопротивление линий и снижает скорость передачи. В нагруженных условиях полное сопротивление шины, вероятно, составляет порядка 25 Ом, а скорость распространения 7,5 ем/нс. В применении, требующем быстрого реверсирования шины от считывания к записи или наоборот, как показано на фиг.17, время перехода сигнала выбирают равным приблизительно 25-30% от скорости передачи сигнала (половина времени цикла). Усиление начинается в следующие 25-30% от скорости передачи сигнала. Драйвер выключается, чтобы установить сигналы в следующие приблизительно 25-30% скорости передачи сигнала. Следует понимать, что следующий цикл, когда реверсируется направление сигнала или данных, можно выполнить без потерь эффективности шины, где элементы находятся близко друг к другу, а время установления шины составляет меньше половины скорости передачи сигнала.

Фиг.18 изображает двухточечное перспективное изображение. Посредством внутреннего включения нагрузочного сопротивления, используя Р-канальные элементы с заземленными затворами, можно построить высокоэффективные двухточечные системы, как показано на фиг.13В. Внутреннее включение нагрузочных сопротивлений устраняет потребность в пространстве для подсоединения внешних сопротивлений и снижает стоимость. Можно также подключать затвор Р-канальных элементов на стороне передающего устройства, чтобы снизить ток, необходимый для разрядки линий сигналов до требуемого напряжения. Как ЦП, так и контроллер памяти имеют Р-канальные оконечные элементы, величины которых можно выбирать равными волновому сопротивлению линии, когда их затворы находятся под потенциалом заземления. Затворы Р-канальных элементов используют сигнал, который является дополнением разблокирования приемного устройства, для блокирования конца приемного устройства и передающего конца. Это переключение можно выполнить, когда приемное устройство предварительно установлено на высокий уровень, и до инициирования пакета в сигнальных линиях. Вместо Р-канального элемента с заземленными затворами также можно использовать внутренние сопротивления. Благодаря использованию множества шин, как описано в следующем разделе, ширину шины от ЦП к контроллеру памяти можно уменьшить с 64 (72) до 32 (36) или можно значительно увеличить полосу пропускания. Соединение тыловой КЭШ-памяти центральных процессоров также можно ускорить, количество контактов на ЦП можно уменьшить, а ОП клавишных переключателей (PBSRAM) можно изменить с Х36 до Х18, вследствие этого уменьшая размер кристалла и стоимость.

Фиг.19 изображает систему 1900, имеющую множество шин для устройств типа ДОП ЛПС, СД ОП ДСПД или СОП ДСПД, где сигналы принимаются одновременно. Шина 1920 синхронизации системы, начинающаяся от источника 1915 синхронизирующих импульсов на конце, противоположном контроллеру 1905 памяти, подсоединена ко всем устройствам 1910, у которых выводы данных подсоединены к шине 1920, и оканчивается у контроллера 1905 памяти. Нагрузка на сигнале синхронизации согласована с нагрузкой на выходном сигнале данных и опорных сигналах /ОССНТ1 и ОССНТ1. Следует понимать, что синхронизирующие импульсы могут быть дифференциальными (предпочтительно) или несимметричными, в зависимости от частоты импульсов синхронизации и требований системы. Размах напряжения синхронизирующих импульсов может быть подобен ОССНТ и /ОССНТ, чтобы иметь подобное приемное устройство. Чтобы иметь такую же задержку, длина трассировки шины 1920 синхронизации согласована с длиной трассировки опорных сигналов /ОССНТ1 и ОССНТ1. Источник 1915 синхронизирующих импульсов вводит ОССНТ1, /ОССНТ1 и данные из устройств ДОП ДСПД в различные периоды времени, в зависимости от их местоположения на шине 1920, так что данные ОССНТ1 и /ОССНТ1 достигают контроллер 1905 приблизительно в одно и то же время, независимо от того, которое ДОП ДСПД передает данные. Каждое устройство ДОП ДСПД необязательно может использовать САПЗ (систему автоматической подстройки по задержке), чтобы снизить синхронизирующие импульсы 1915 для задержки данных, если это необходимо для синхронизации в контроллере 1905. Чтобы снизить дополнительный контакт в синхронизированной системе, где передача данных является предсказуемой, для генерирования /ОССНТ1 можно использовать САПЗ, имеющую на конце приемного устройства такие же согласование во времени и характеристику напряжения, но противоположной полярности. САПЗ воспроизводит синхронизирующие импульсы во всех компонентах (включая контроллер 1905 и устройство ДОП ДСПД 1910). Контроллер будет знать цикл, в котором предсказывается поступление данных, и опорный сигнал ОССНТ1. После инициирования цикла записи сигналами адреса и команды, ДОП ДСПД будет знать цикл, в который могут поступать входные данные. САПЗ стробирует сигнал /ОССНТ1, только когда сигнал необходим конкретному компоненту. Линии адреса и команды можно группировать с ОССНТ0 и /OCCHT0. Шина адреса и управления однонаправлено переносит входные сигналы из контроллера 1905 памяти к устройствам ДОП ДСПД 1910. 10-Битовые команда и адрес представлены в виде 2-битовой команды и 8-битового адреса. 2-Битовая команда выполняется путем использования /СЕ (сигнал, разрешающий доступ к информационной шине одной из трех ИС микропроцессора) и /RAS (стробирующий сигнал адресов строки) в одном сигнале на двух концах сигналов ОССНТ0 и /OССНТ0 и другого сигнала для /САЗ (стробирующий сигнал адресов столбца) и /WE. 8-Битовый адрес на двух концах дает до 16 битов адреса строки, появляющихся с /СЕ и /RAS, или до 16 битов адреса колонки и блока, появляющихся с /СЕ и /САS, для цикла считывания. Цикл записи выполняется 16 битами адреса колонки и блока с /СЕ, /CAS и /WE. Сигналы OССНТ0 и /ОССНТ0 могут быть производными синхронизирующих импульсов (дифференциальных) системы и работать на той же самой или кратной частоте синхронизирующих импульсов системы. Как объяснено выше, САПЗ можно использовать для фиксирования частоты синхронизации в контроллере 1905 памяти для различных внутренних целей, для запуска сигналов команды и адреса в случае запросов считывания и для запуска ввода данных, ОССНТ1 и /ОССНТ1 в случае запросов записи.