Область техники, к которой относится изобретение

Настоящее изобретение в целом относится к системе связи с передачей пакетов данных и более конкретно к устройству и способу кодирования/декодирования передаваемой информации.

Уровень техники

Система мобильной связи IS-2000 CDMA (множественный доступ с кодовым разделением каналов (МДКР)), являясь типичной системой мобильной связи, поддерживает только услуги передачи речи (речевые услуги). Однако с развитием технологии связи и по требованию пользователей системы мобильной связи развиваются, чтобы поддерживать услуги передачи данных (услуги данных) так же, как речевые услуги.

Система мобильной связи, поддерживающая мультимедийные услуги, включающие в себя речевые услуги и услуги данных, обеспечивает речевые услуги для множества пользователей, использующих одну полосу частот. Дополнительно система мобильной связи поддерживает услуги данных посредством TDM (мультиплексирование с временным разделением каналов (МВР)) или TDM/CDM (мультиплексирование с временным разделением каналов/мультиплексирование с кодовым разделением каналов (МВР/МКР)). МВР является способом для присваивания (назначения) в пределах временного слота (временного интервала) некоторого кода, присваиваемого конкретному пользователю. МВР/МКР является способом, при котором множество пользователей одновременно используют один временной слот. Пользователи идентифицируются посредством уникальных кодов (например, ортогональных кодов, таких как коды Уолша), присвоенных пользователям.

Система мобильной связи включает в себя канал передачи пакетных данных (КППД, PDCH) для передачи пакетных данных и канал управления пакетными данными (КУПД, PDCCH), например вторичный канал управления пакетными данными (ВКУПД, SPDCCH), для эффективной передачи пакетных данных. Пакетные данные передаются по каналу передачи пакетных данных. Передача пакетных данных через воздушную среду выполняется в блоке пакетов физического уровня (ПФУ), и длина пакета физического уровня изменяется при каждой передаче. Канал управления пакетными данными передает кадр управляющей информации, необходимый для того, чтобы позволить приемнику эффективно принимать пакетные данные. Длина кадра управляющей информации изменяется в соответствии с длиной пакетных данных. Следовательно, приемник может определить изменяющуюся длину пакетных данных, произведя оценку длины кадра управляющей информации. Длина кадра управляющей информации оценивается посредством обнаружения формата фиктивного (слепого) кадра (ОФФК).

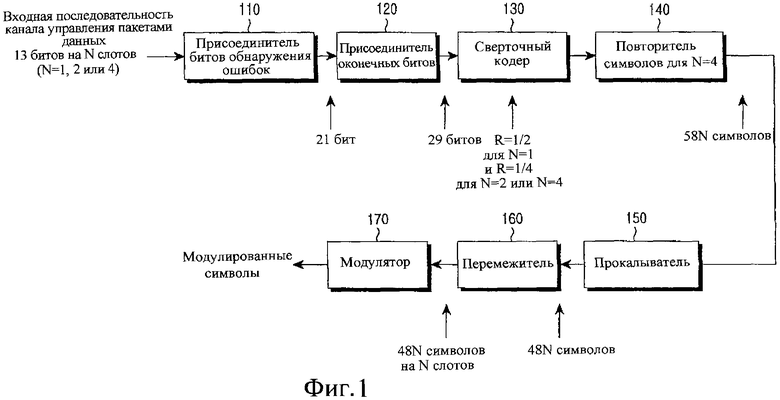

На фиг.1 иллюстрируется структура передатчика канала управления пакетными данными в соответствии с предшествующим уровнем техники. Что касается фиг.1, то предполагается, что входная последовательность канала управления пакетными данными или управляющая информация, передаваемая по каналу управления пакетными данными, имеет 13 битов на N слотов (где N=1, 2 или 4). Следует отметить, что количество битов, включенных в состав управляющей информации, не связано с длиной кадра управляющей информации и не ограничивается значением 13. Длина кадра управляющей информации, передаваемого по каналу управления пакетными данными, зависит от длины пакетных данных. Например, если пакетные данные имеют одну из длин в 1 слот, 2 слота, 4 слота и 8 слотов, то кадр управляющей информации имеет одну выбранную длину из длин 1 слот, 2 слота и 4 слота. Для пакетных данных, имеющих длину 1 слот, передается кадр управляющей информации, имеющий длину 1 слот. Для пакетных данных, имеющих длину 2 слота, передается кадр управляющей информации, имеющий длину 2 слота. Для пакетных данных, имеющих длину 4 слота, передается кадр управляющей информации, имеющий длину 4 слота. Для пакетных данных, имеющих длину 8 слотов, передается кадр управляющей информации, имеющий длину 4 слота. Причина для передачи кадра управляющей информации, имеющего длину 4 слота даже для пакетных данных, имеющих длину 8 слотов, заключается в том, чтобы препятствовать чрезмерному увеличению длины заголовка.

Биты обнаружения ошибок присоединяются с помощью присоединителя 110 битов обнаружения ошибок к управляющей информации, передаваемой по каналу управления пакетными данными. Присоединитель 110 битов обнаружения ошибок присоединяет биты обнаружения ошибок к управляющей информации, так что приемник может обнаружить ошибку передачи по кадру управляющей информации. Например, присоединитель 110 битов обнаружения ошибок присоединяет 8 битов обнаружения ошибок к 13-битной управляющей информации и генерирует 21-битную управляющую информацию. Генератор проверки с помощью циклического избыточного кода (ЦИК, CRC) является типичным примером присоединителя 110 битов обнаружения ошибок. Генератор ЦИК генерирует управляющую информацию с присоединенной информацией ЦИК посредством кодирования входной управляющей информации с помощью ЦИК. Если количество избыточных битов, сгенерированных с помощью ЦИК, увеличивается, то возможность обнаружения ошибки передачи возрастает. Однако увеличение количества избыточных битов для управляющей информации уменьшит эффективность мощности. Вот почему обычно используются 8 битов ЦИК для битов обнаружения ошибок.

Присоединитель 120 оконечных (хвостовых) битов присоединяет оконечные биты к выходной управляющей информации присоединителя 110 битов обнаружения ошибок. Сверточный кодер 130 сверточно кодирует выходные данные присоединителя 120 оконечных битов и выводит кодированные символы. Например, присоединитель 120 оконечных битов присоединяет 8 оконечных битов, все из которых имеют нули, для сверточного кодирования сверточным кодером 130 и выводит 29-битовую информацию. Сверточный кодер 130 сверточно кодирует кадр управляющей информации длиной 1 слот со скоростью кодирования 1/2, а кадр управляющей информации длиной 2 слота и кадр управляющей информации длиной 4 слота со скоростью кодирования 1/4. Количество символов в кадре управляющей информации, сверточно кодированном со скоростью кодирования 1/4, в два раза больше количества символов в кадре управляющей информации, сверточно кодированном со сскоростью кодирования 1/2. Повторитель 140 символов повторно выводит символы, полученные сверточным кодированием кадра управляющей информации длиной 4 слота, так что количество символов, полученных сверточным кодированием кадра управляющей информации длиной 4 слота, становится в два раза больше, чем количество символов, полученных сверточным кодированием кадра управляющей информации длиной 2 слота. В качестве результата повторитель 140 символов выводит 58N (где N=1, 2 или 4) символов.

Прокалыватель 150 прокалывает 10N символов в выходных символах повторителя символов 140 для минимизации снижения производительности и достижения необходимого согласования скорости передачи. Поэтому прокалыватель 150 выводит 48N символов. Перемежитель 160 перемежает выходные символы прокалывателя 150. Причина использования перемежителя 160 заключается в том, чтобы уменьшить вероятность ошибки в пакетах перемежением (или перестановкой) порядка символов для разрешения проблемы ошибки в пакетах, обусловленной сверточным кодированием. Обращенный перемежитель битов (ОПБ), являющийся разновидностью блочного перемежителя, может использоваться для перемежителя 160. ОПБ увеличивает интервал между соседними символами на столько, на сколько это возможно, и таким образом, что первая половина последовательности перемеженных символов содержит четное количество символов, а вторая половина последовательности перемеженных символов содержит нечетное количество символов. Модулятор 170 модулирует символы, перемеженные перемежителем 160, посредством модуляции методом квадратурной фазовой манипуляции (КФМ, QPSK), и генерирует модулированные символы для передачи.

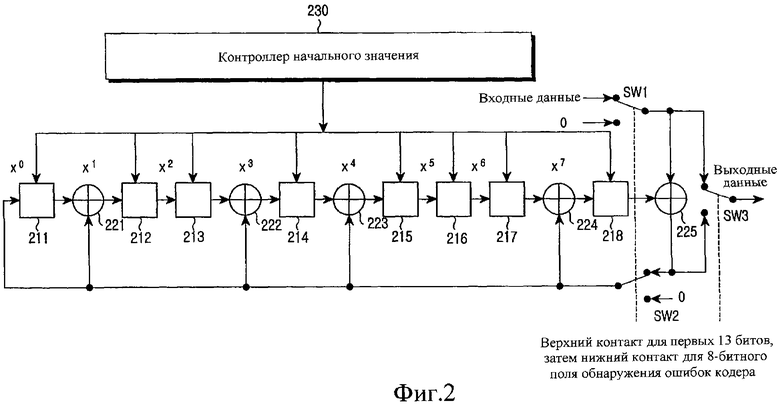

На фиг.2 иллюстрируется структура присоединителя 110 битов обнаружения ошибок, показанного на фиг.1, в соответствии с предшествующим уровнем техники. На фиг.2 иллюстрирован пример присоединителя 110 битов обнаружения ошибок, реализованного с помощью генератора ЦИК. Генератор ЦИК включает в себя множество регистров 211-218, множество сумматоров 221-224, переключатели SW1-SW3, выходной сумматор 225 и контроллер 230 начального значения.

Что касается фиг.2, то после того, как инициализированы значения регистров 211-218 начальным значением, поданным от контроллера 230 начального значения, выходным сумматором 225 выполняется двоичная операция между каждым битом входной управляющей информации и значением, полученным от оконечного регистра 218 сдвигом вправо значений регистров 211-218, и результирующее значение операции подается как выходная управляющая информация. В течение этой операции все переключатели SW1-SW3 переключены на верхние контакты. После того, как вышеуказанная операция выполнена по всем битам 13-битной управляющей информации, переключатели SW1-SW3 переключаются на нижние контакты, так что на переключатели SW1 и SW2 подаются значения "0". Далее 8 избыточных битов присоединяются посредством сдвига значений регистра столько раз, каково значение количества избыточных битов, например 8.

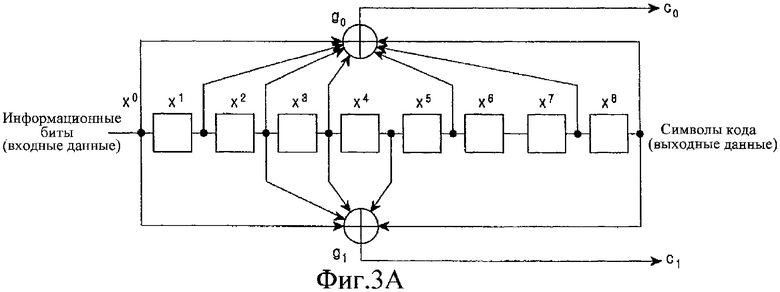

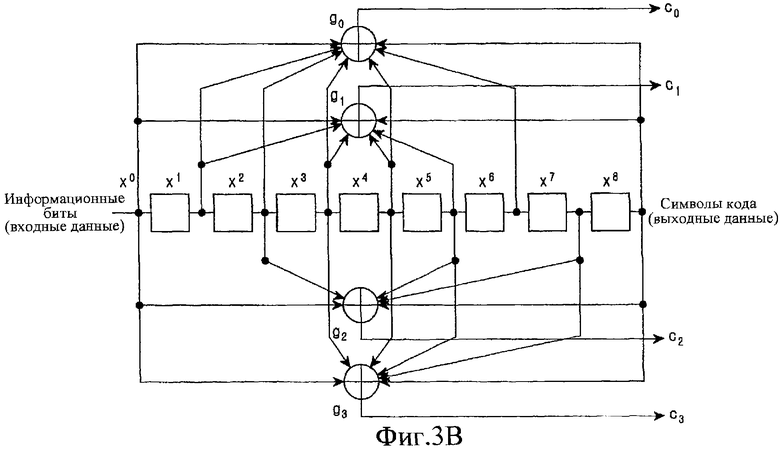

На фиг.3А и 3В приводятся иллюстративные примеры структур сверточного кодера 130, показанного на фиг.1. Более конкретно на фиг.3А приводится иллюстративный пример структуры для сверточного кодирования входных информационных битов со скоростью кодирования 1/2 и выдачи кодированных символов. На фиг.3В приводится другой иллюстративный пример структуры для сверточного кодирования входных информационных битов со скоростью кодирования 1/4 и выдачи кодированных символов.

Что касается фиг.3А, то если скорость кодирования равна R=1/2 и последовательность входных информационных битов определена как х, тогда выходные данные 2-С0 и 2-С1 сверточного кодера 130 выражаются как:

2-С0: 1+х+х2+х3+х5+х7+х8

2-С1: 1+х2+х3+х4+х8

Что касается фиг.3В, то если скорость кодирования равна R=1/4 и последовательность входных информационных битов определена как х, тогда выходные данные 4-С0, 4-С1, 4-С2 и 4-С3 сверточного кодера 130 выражаются как:

4-С0: 1+х+х2+х3+х4+х6+х8

4-С1: 1+х+х3+х4+х5+х8

4-С2: 1+х2+х5+х7+х8

4-С3: 1+х3+х4+х5+х7+х8

В приведенных выше выражениях Cs обозначает один из выходных сигналов сверточного кодера 130, при этом s означает порядок выходных символов сверточного кодера 130, а "2" или "4" означают количество выходных символов сверточного кодера 130.

Чтобы генерировать кодированные таким образом символы, необходимо спроектировать сверточный кодер 130 по фиг.3А или 3В в соответствии с заданными порождающими полиномами символов кодовых слов. Как иллюстрировано, сверточный кодер 130 может быть реализован объединением регистров и сумматоров. Порождающие полиномы символов кодовых слов для скоростей кодирования определены таким образом, что они могут показать оптимальную производительность по отношению к скоростям кодирования. То есть порождающие полиномы для сверточного кодера со скоростью кодирования R=1/2 (далее по тексту называемого сверточным кодером с R=1/2), а порождающие полиномы для сверточного кодера со скоростью кодирования R=1/4 (далее по тексту называемого сверточным кодером с R=1/4) определяются, чтобы быть независимыми друг от друга.

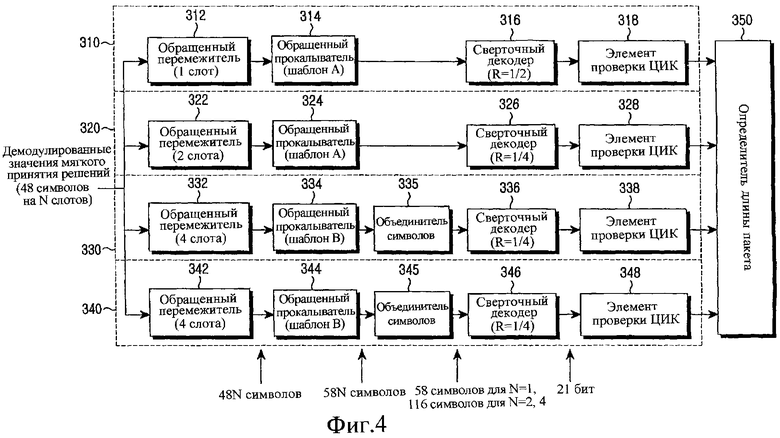

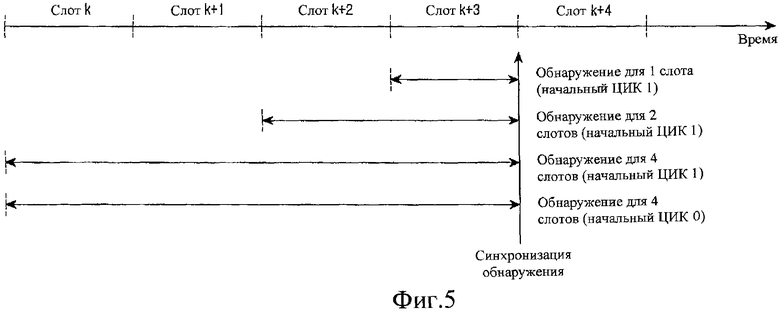

На фиг.4 иллюстрируется структура приемника канала управления пакетными данными в соответствии с предшествующим уровнем техники, а на фиг.5 иллюстрируются длины и положения слотов, используемых при обнаружении кадра управляющей информации приемником, показанным на фиг.4. В частности, на фиг.4 иллюстрируется структура приемника для определения длины пакетных данных посредством обнаружения кадра управляющей информации, переданного по каналу управления пакетными данными, с помощью ОФФК. Приемник соответствует передатчику канала управления пакетными данными, в котором генератор ЦИК используется в качестве присоединителя битов обнаружения ошибок. Приемник включает в себя элементы проверки ЦИК, соответствующие генератору ЦИК в передатчике.

Что касается фиг.4, то приемник включает в себя 4 блока 310-340 обработки приема для определения длины пакетных данных. Блок 310 обработки приема является блоком для обработки кадра управляющей информации, который имеет длину 1 слот и соответствует пакетным данным длиной 1 слот; блок 320 обработки приема является блоком для обработки кадра управляющей информации, который имеет длину 2 слота и соответствует пакетным данным длиной 2 слота; блок 330 обработки приема является блоком для обработки кадра управляющей информации, который имеет длину 4 слота и соответствует пакетным данным длиной 4 слота; и блок 340 обработки приема является блоком для обработки кадра управляющей информации, который имеет длину 4 слота и соответствует пакетным данным длиной 8 слотов.

В блоках 310-340 обработки приема обращенные перемежители 312, 322, 332 и 342 выполняют обращенное перемежение в зависимости от соответствующих длин слотов, а обращенные прокалыватели 314, 324, 334 и 344 выполняют обращенное прокалывание согласно соответствующим длинам слотов. В блоках 330 и 340 обработки приема для кадра управляющей информации длиной 4 слота объединители 335 и 345 символов выполняют объединение символов по 2 соседним символам, что является обратной операцией повторения символов, выполняемой повторителем 140 символов, показанным на фиг.1. После того, как выполнены обращенное прокалывание в блоках 310 и 320 обработки приема и объединение символов в блоках 330 и 340 обработки приема, сверточные декодеры 316, 326, 336 и 346 в блоках 310-340 обработки приема выполняют сверточное декодирование. Сверточный декодер 316 для кадра управляющей информации, имеющего длину 1 слот, сверточно декодирует выходные данные обращенного прокалывателя 314 со скоростью кодирования 1/2. Сверточный декодер 326 для кадра управляющей информации, имеющего длину 2 слота, сверточно декодирует выходные данные обращенного прокалывателя 324 со скоростью кодирования 1/4. Подобным образом сверточные декодеры 336 и 346 для кадра управляющей информации, имеющего длину 4 слота, сверточно декодируют со скоростью кодирования 1/4 выходные данные объединителей 335 и 345 символов соответственно. В оконечных каскадах блоков 310-340 обработки приема размещены элементы 318, 328, 338 и 348 проверки ЦИК. Элементы 318, 328, 338 и 348 проверки ЦИК выполняют проверку ЦИК на символах, сверточно декодированнных сверточными декодерами 316, 326, 336 и 346 соответственно. По результату проверки ЦИК элементами 318, 328, 338 и 348 проверки ЦИК определяется, присутствует ли ошибка ЦИК в кадре управляющей информации, переданном от передатчика. В течение проверки ЦИК элементы 318,328, 338 и 348 проверки ЦИК используют заданные начальные значения. Например, элемент 318 проверки ЦИК обнаруживает ошибку ЦИК посредством установки начального значения регистра декодера в "2", элемент 328 проверки ЦИК обнаруживает ошибку ЦИК посредством установки начального значения регистра декодера в "4", элемент 338 проверки ЦИК обнаруживает ошибку ЦИК посредством установки начального значения регистра декодера в "255", и элемент 348 проверки ЦИК обнаруживает ошибку ЦИК посредством установки начального значения регистра декодера в "0". Определитель 350 длины пакета определяет длину пакетных данных на основании результатов обработки приема, полученных блоками 310-340 обработки приема. При этом 4 блока 310-340 обработки приема могут быть реализованы как физически отдельные блоки обработки приема или как единый блок обработки приема, использующий различные параметры приема.

В приемнике, показанном на фиг.4, в качестве результата декодирования ЦИК в случае, если три блока обработки приема имеют ошибки и один блок обработки приема не имеет ошибки, то принимается решение, что было передано количество пакетных данных, соответствующее длине принятых блоком обработки приема, который не имеет ошибки. Однако если сообщается, что два или более блоков обработки приема не имеют ошибок или все блоки обработки приема не имеют ошибок, то невозможно определить, какой кадр управляющей информации передавался, что приводит к сбою приема пакетных данных.

В таблице 1 иллюстрируются результаты компьютерного моделирования, полученные при 10000-кратной передаче кадра управляющей информации с длиной слота 2(4) при отсутствии помехи и приеме переданного кадра управляющей информации приемниками 1(2), 2(4), 4(255) и 4(0). При этом числовые значения в скобках представляют начальные значения регистров генератора ЦИК в виде десятичных чисел. Для кадра управляющей информации, имеющего длину 1 слот, начальное значение регистра устанавливается в N1=2. Для кадра управляющей информации, имеющего длину 2 слота, начальное значение регистра устанавливается в N2=4. Для кадра управляющей информации, имеющего длину 4 слота, соответствующего пакетным данным длиной 4 слота, начальное значение регистра устанавливается в N3=255. Для кадра управляющей информации, имеющего длину 4 слота, соответствующего пакетным данным длиной 8 слотов, начальное значение регистра устанавливается в N4=0. Результирующие значения, полученные посредством компьютерного моделирования, включают в себя вероятность Pd успешного определения; вероятность Pfa ложного распознавания неверной длины слота как верной длины слота; вероятность Pm допущения ошибки при ошибочном восприятии верной длины слота как неверной длины слота, и вероятность Pe ошибки, являющуюся суммой вероятности Pfa ложного распознавания и вероятности Pm допущения ошибки. В таблице 1 отмечено, что вероятность Pe ошибки кадра управляющей информации большей частью генерируется приемником 1-слотового кадра управляющей информации.

Как описано выше, передатчик канала управления пакетными данными, показанный на фиг.1, использует одинаковые сверточные кодеры со скоростью кодирования 1/4 как для 2-слотового кадра управляющей информации, так и для 4-слотового кадра управляющей информации, и использует сверточные кодеры со скоростью кодирования 1/2 для 1-слотового кадра управляющей информации. В таком случае, если приемник канала управления пакетными данными принимает кадр управляющей информации посредством ОФФК, то вероятность Pe ошибки 2-слотового кадра управляющей информации нежелательно увеличивается из-за ошибки приемника 1-слотового кадра управляющей информации, имеющего почти все вероятности ошибок в приемнике, как описано согласно таблице 1.

Сущность изобретения

Следовательно, задачей настоящего изобретения является создание устройства и способа кодирования/декодирования для исключения ошибки, которая может произойти в течение передачи/приема управляющей информации, относящейся к передаче пакетных данных в системе связи.

Другая задача настоящего изобретения заключается в создании устройства и способа кодирования/декодирования для правильного приема управляющей информации в системе связи даже в том случае, когда длина управляющей информации, относящейся к передаче пакетных данных, изменяется.

В соответствии с одним аспектом настоящего изобретения, предложено устройство для кодирования последовательности информационных битов и генерирования кодированных символов в системе связи, которая передает пакетные данные и последовательность информационных битов для управления передачей пакетных данных. Устройство в одном варианте осуществления включает в себя кодер и контроллер. Кодер кодирует последовательность информационных битов с заданной скоростью кодирования и выводит кодированные символы. Контроллер управляет кодером таким образом, что кодер выводит кодированные символы тогда, когда длина кадра последовательности информационных битов является первой длиной, и кодер выводит частичные символы из кодированных символов тогда, когда длина кадра последовательности информационных битов является второй длиной, которая меньше, чем первая длина. Предпочтительно контроллер управляет кодером таким образом, что кодер выводит столько кодированных символов, каково значение, определяемое делением количества кодированных символов на заданное число F (при этом F является натуральное числом), в тех случаях, когда длина кадра последовательности информационных битов является второй длиной, которая в F раз меньше, чем первая длина.

В соответствии с другим аспектом настоящего изобретения предложено устройство для кодирования последовательности информационных битов и генерирования кодированных символов в системе связи, которая передает пакетные данные и последовательность информационных битов для управления передачей пакетных данных. Устройство в одном варианте осуществления включает в себя присоединитель битов обнаружения ошибок, сверточный кодер и контроллер. Присоединитель битов обнаружения ошибок присоединяет биты обнаружения ошибок к последовательности информационных битов и выводит последовательность информационных битов с присоединенными битами обнаружения ошибок. Сверточный кодер сверточно кодирует последовательность информационных битов с присоединенными битами обнаружения ошибок с заданной скоростью кодирования и выводит кодированные символы. Контроллер управляет сверточным кодером таким образом, что сверточный кодер выводит кодированные символы, когда длина кадра последовательности информационных битов является первой длиной, и сверточный кодер выводит столько кодированных символов, каково значение числа, определяемого делением количества кодированных символов на заданное число F (где F есть натуральное число), когда длина кадра последовательности информационных битов является второй длиной, которая в F раз меньше (короче), чем первая длина.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Указанные выше и другие задачи, признаки и преимущества настоящего изобретения будут более очевидны из изложенного ниже подробного описания, рассматриваемого с прилагаемыми чертежами, на которых:

фиг.1 - структура передатчика канала управления пакетными данными в соответствии с предшествующим уровнем техники;

фиг.2 - структура присоединителя битов обнаружения ошибок, показанного на фиг.1, в соответствии с предшествующим уровнем техники;

фиг.3А и 3В - иллюстративные структуры сверточного кодера, показанного на фиг.1;

фиг.4 - структура приемника канала управления пакетными данными в соответствии с предшествующим уровнем техники;

фиг.5 - длины и положения слотов, которые используются при обнаружении кадра управляющей информации приемником, показанным на фиг.4;

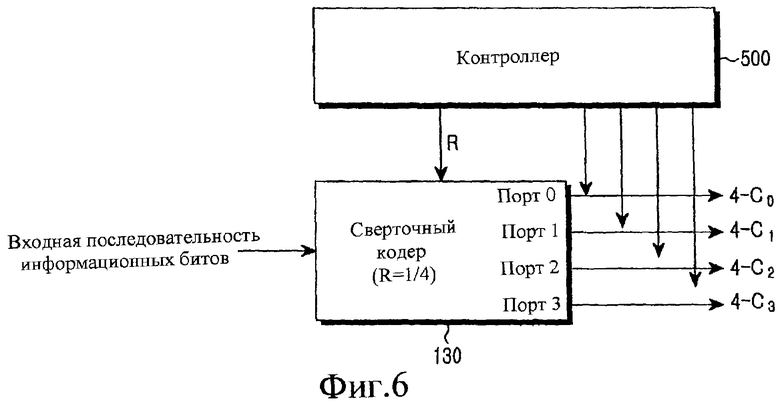

фиг.6 - структура устройства сверточного кодера в соответствии с вариантом осуществления настоящего изобретения;

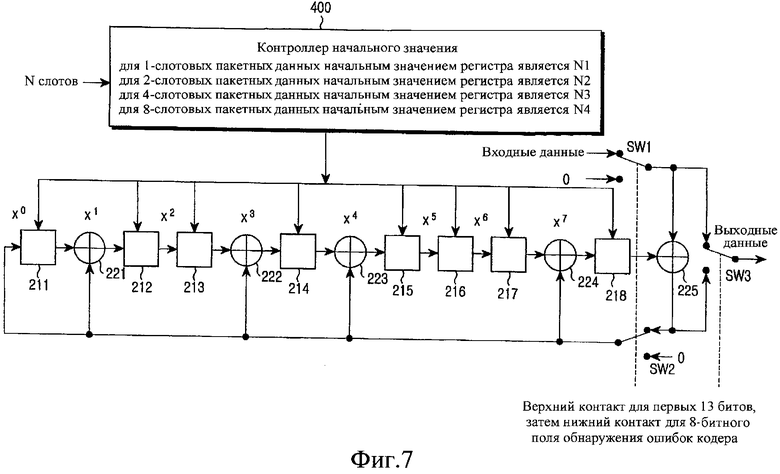

фиг.7 - подробная структура присоединителя битов обнаружения ошибок, показанного на фиг.1, в соответствии с вариантом осуществления настоящего изобретения;

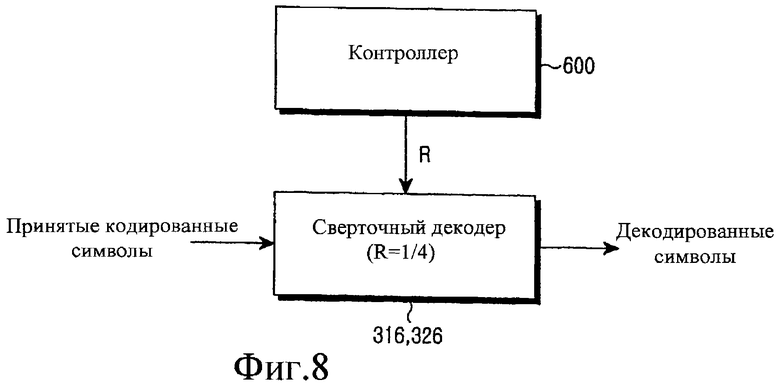

фиг.8 - структура устройства сверточного декодера в соответствии с вариантом осуществления настоящего изобретения; и

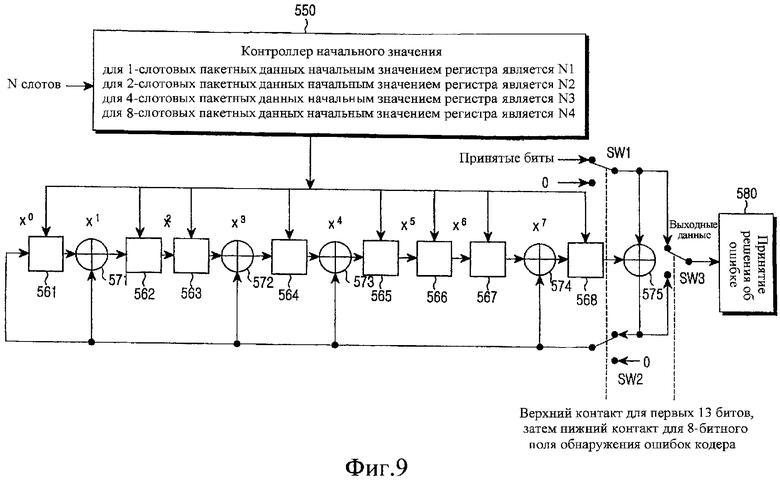

фиг.9 - подробная структура элемента проверки ЦИК, показанного на фиг.4, в соответствии с вариантом осуществления настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНЫХ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

Предпочтительный вариант осуществления настоящего изобретения будет описан в данном описании ниже со ссылками на прилагаемые чертежи. В последующем описании хорошо известные функции или конструкции подробно не описываются, поскольку это затенило бы изобретение ненужными подробностями.

Когда обычный передатчик канала управления пакетными данными использует сверточный кодер для того, чтобы генерировать символы кодового слова 2-слотового кадра управляющей информации, кодированного со скоростью кодирования 1/4, выходные данные 4-С0 и 4-С2 сверточного кодера располагаются в первом слоте, а выходные данные 4-С1 и 4-С3 сверточного кодера располагаются во втором слоте. То есть если из порождающих полиномов для сверточного кодера с R=1/4 выбраны два порождающих полинома в качестве порождающих полиномов для сверточного кодера с R=1/2 для кодирования 1-слотового кадра управляющей информации вместо использования порождающих полиномов, отличных от порождающих полиномов для сверточного кодера с R=1/4, то существует высокая вероятность того, что приемник 1-слотового кадра управляющей информации и приемник 2-слотового кадра управляющей информации будут генерировать одинаковые выходные данные на (своих) сверточных декодерах. Хотя сверточные декодеры генерируют одинаковые выходные данные, принятые символы могут быть идентифицированы посредством различных начальных значений регистров ЦИК, используемых элементами проверки ЦИК, следующими за индивидуальными сверточными декодерами. То есть хотя сверточные декодеры генерируют одинаковые выходные данные, в том случае, когда один приемник имеет "Хороший" результат проверки ЦИК, второй приемник имеет 100% "Плохой" результат проверки ЦИК, уменьшая таким образом ошибку ОФФК, которая может произойти, когда оба из двух приемников одновременно имеют "Хороший" результат проверки ЦИК.

Другими словами, используемые в настоящее время порождающие полиномы для сверточного кодера с R=1/2 не являются оптимальными порождающими полиномами с точки зрения производительности ОФФК, и для того чтобы максимизировать производительность ОФФК, необходимо выбрать два порождающих полинома из порождающих полиномов для сверточного кодирования 2-слотового кадра управляющей информации со скоростью кодирования 1/4 в качестве порождающих полиномов для сверточного кодирования 1-слотового кадра управляющей информации со скоростью кодирования R=1/2.

Принцип

Предлагается способ генерирования кодированных символов описанным ниже образом в системе связи, согласно которому кодируют входную последовательность информационных битов и генерируют кодированные символы. Предлагаемый способ может быть применен к сверточному кодеру 130, показанному на фиг.1.

Изобретение предлагает способ кодирования последовательности информационных битов с первой длиной с первой скоростью кодирования и вывода кодированных символов. Дополнительно настоящее изобретение предлагает способ кодирования входной последовательности информационных битов со второй длиной, которая в заданное значение F раз меньше первой длины, с первой скоростью кодирования и выбирают несколько (1/F) кодированных символов из закодированных символов. Входная последовательность информационных битов, как описано в предшествующем уровне техники и ниже в настоящем описании, может стать управляющей информацией, относящейся к передаче пакетных данных. Предполагается, что в системе связи существуют несколько пакетов с различными длинами и соотношение длин пакетов составляет 1:2:4. Для одной и той же последовательности информационных битов в силу того, что каждый пакет имеет различную скорость кодирования, соотношение которых составляет 1:1/2:1/4, длины пакетов передачи отличаются одна от другой в соответствии со скоростью кодирования. Заданное значение F определяется по рассмотрению длины пакета передачи. Например, входная последовательность информационных битов с первой длиной может стать 2-слотовым кадром управляющей информации, а входная последовательность информационных битов со второй длиной может стать 1-слотовым кадром управляющей информации. В таком случае первой скоростью кодирования может стать 1/4, а второй скоростью кодирования может стать 1/2. Несколько кодированных символов, выбранных из числа кодированных символов, полученных посредством кодирования входной последовательности информационных битов со второй длиной с первой скоростью кодирования R=1/4, могут быть нечетным количеством символов или четным количеством символов из числа символов, кодированных с первой скоростью кодирования. В противоположном случае частично выбранные кодированные символы могут стать первой половиной или второй половиной символов, кодированных с первой скоростью кодирования.

В настоящем описании будет предполагаться, что принцип настоящего изобретения применим к случаю, при котором сверточный кодер 130, показанный на фиг.3А и 3В, генерирует сверточно кодированные символы. То есть сверточный кодер 130 кодирует 1-слотовый кадр управляющей информации со скоростью кодирования R=1/4 и затем выбирает только некоторые из кодированных символов. В вариантах 1, 2, 3, и 4 ниже по тексту символы, кодированные сверточным кодером 130, представлены посредством 4-С0, 4-С1, 4-С2, 4-С3, и символы, частично выбранные из кодированных символов, представлены посредством 2-С0, 2-С1:

Вариант 1

2-С0: 4-С0 (или 4-С2)

2-С1: 4-С2 (или 4-С0)

Вариант 2

2-С0: 4-С1 (или 4-С3)

2-С1: 4-С3 (или 4-С1)

Вариант 3

2-С0: 4-С0 (или 4-С1)

2-С1: 4-С1 (или 4-С0)

Вариант 4

2-С0: 4-С2 (или 4-С3)

2-С1: 4-С3 (или 4-С2)

В вариантах от 1 до 4, 4-С0, 4-С1, 4-С2 и 4-С3 являются выходными данными сверточного кодера с R=1/4 и порождающие полиномы для этих выходных данных могут быть предварительно определены так, как следует ниже. Как показано ниже, порождающие полиномы для генерирования символов кодового слова для 4-С0, 4-С1, 4-С2 и 4-С3 могут быть заменены другими порождающими полиномами при условии, что удовлетворяется оптимальная производительность кодирования:

4-С0: 1+х+х2+х3+х4+х6+х8

4-С1: 1+х+х3+х4+х5+х8

4-С2: 1+х2+х5+х7+х8

4-С3: 1+х3+х4+х5+х7+х8

Между тем, в тех случаях, когда информация обнаружения ошибок присоединяется генератором ЦИК к каждому из 1-слотовых кадров управляющей информации и из 2-слотовых кадров управляющей информации, предпочтительно устанавливать начальные значения регистров ЦИК в различные значения.

Вариант осуществления

Настоящее изобретение будет описано со ссылкой на вариант осуществления, в котором принцип изобретения применен к передатчику для кодирования управляющей информации, относящейся к передаче пакетных данных, посредством сверточного кодера, как проиллюстрировано на фиг.1 и 2, и осуществляемого до передачи, и к приемнику для выполнения декодирования сверточным декодером, соответствующим сверточному кодеру. Однако следует отметить, что настоящее изобретение не ограничено таким вариантом осуществления. Предлагаемый способ для кодирования информационных битов таких, как кадр управляющей информации, относящийся к передаче пакетных данных, осуществляемого до передачи, и для декодирования принятых символов кодового слова, отличается тем, что выбирают в качестве порождающих полиномов для кодирования 1-слотового кадра управляющей информации некоторых порождающих полиномов из порождающих полиномов для кодирования 2-слотового кадра управляющей информации. Дополнительно вариант осуществления настоящего изобретения отличается тем, что используют различные начальные значения регистров при присоединении информации для обнаружения ошибок к 1-слотовому кадру управляющей информации и к 2-слотовому кадру управляющей информации, выполняемом генератором ЦИК.

На фиг.6 иллюстрируется структура устройства сверточного кодера в соответствии с вариантом осуществления настоящего изобретения. Что касается фиг.6, устройство сверточного кодера включает в себя сверточный кодер 130 и контроллер 500. Сверточный кодер 130 кодирует входную последовательность информационных битов с заданной скоростью кодирования R=1/4 и выводит кодированные символы через выходные порты PORT0-PORT3, количество которых соответствует значению скорости кодирования. Контроллер 500 определяет длину входной последовательности информационных битов и выполняет операцию в соответствии с этой определенной длиной. Если входная последовательность информационных битов является 1-слотовым кадром управляющей информации, контроллер 500 активизирует выходные порты таким образом, чтобы кодированные символы выводились через два из выходных портов. Если входная последовательность информационных битов является 2-слотовым кадром управляющей информации, контроллер 500 активизирует выходные порты таким образом, чтобы кодированные символы выводились через четыре выходных порта. В частности, если входная последовательность информационных битов является 1-слотовым кадром управляющей информации, контроллер 500 среди выходных портов активизирует выходные порты с нечетными номерами 4-С0 и 4-С2, с нечетными номерами 4-С1 и 4-С3, выходные порты первой половины 4-С0 и 4-С1, или выходные порты второй половины 4-С2 и 4-С3. Предпочтительно контроллер 500 среди выходных портов активизирует выходные порты с нечетными номерами 4-С0 4-С2 или с четными номерами 4-С1 и 4-С3.

Таким образом, когда передается 1-слотовый кадр управляющей информации, контроллер 500 использует для кодирования только два из четырех порождающих код полиномов, используемых в сверточном кодере 130 с R=1/4, и также активизирует только те выходные порты, которые соответствуют 2 порождающим полиномам, задействованным в 4 выходных портах. Однако когда передается 2-слотовый или 4-слотовый кадр управляющей информации, контроллер 500 использует все из 4 порождающих код полиномов, используемых в сверточном кодере с R=1/4.

Хотя настоящее изобретение было описано со ссылкой на пример кодирования 1-слотового кадра управляющей информации, соответствующего скорости кодирования R=1/2, выполняемого сверточным кодером с R=1/4, настоящее изобретение может быть применено к другому примеру. Например, в случае когда кодирование выполняется со скоростью кодирования R=1/6, только 3 порождающих полинома из 6 порождающих код полиномов могут быть использованы для кодирования 1-слотового кадра, соответствующего скорости кодирования R=1/3. То есть настоящее изобретение не ограничивается конкретным значением скорости кодирования. Дополнительно, чтобы использовать одинаковый кодер для каналов, имеющих различные структуры кадров, возможно использование заданного количества выходных портов вместо использования только половины из возможных выходных портов.

На фиг.7 иллюстрируется подробная структура присоединителя 110 битов обнаружения ошибок, показанного на фиг.1, соответствующая варианту осуществления настоящего изобретения. На фиг.7 проиллюстрирован пример присоединителя 110 битов обнаружения ошибок, реализованного посредством генератора ЦИК, причем присоединитель 110 битов обнаружения ошибок соответствует генератору ЦИК, показанному на фиг.2. Генератор ЦИК в соответствии с настоящим изобретением устанавливает различные начальные значения регистра для кадров управляющей информации, поддерживающих пакетные данные различной длины, вне зависимости от длины кадров управляющей информации. Например, при присоединении 8 битов обнаружения ошибок к кадру управляющей информации генератор ЦИК устанавливает "1" или "0" для каждого из 8 регистров. В десятичной форме 8 регистров устанавливаются в начальные значения от 0 до 255 (=28-1). То есть если количество регистров, образующих генератор ЦИК (или количество избыточных информационных битов для обнаружения ошибок), равно m, то регистры генератора ЦИК могут быть установлены в начальные значения от 0 до 2m-1 в десятичной форме. Например, начальные значения N1, N2, N3 и N4 регистров ЦИК генератора, подлежащих использованию для передачи 1-слотового кадра управляющей информации для 1-слотовых пакетных данных, 2-слотового кадра управляющей информации для 2-слотовых пакетных данных, 4-слотового кадра управляющей информации для 4-слотовых пакетных данных и 4-слотового кадра управляющей информации для 8-слотовых пакетных данных, могут быть установлены в конкретные значения в диапазоне от 0 до 255. В данном случае N1 и N2 установлены в различные значения.

Что касается фиг.7, присоединитель 110 битов обнаружения ошибок в соответствии с настоящим изобретением включает в себя множество регистров 211-218, множество сумматоров 221-224, переключатели SW1-SW3, выходной сумматор 225 и контроллер 400 начального значения. Контроллер 400 начального значения инициализирует значения регистров 211-218 в N1, когда передаются пакетные данные длиной 1 слот. Контроллер 400 начального значения инициализирует значения регистров 211-218 в N2, когда передаются пакетные данные длиной 2 слота. Контроллер 400 начального значения инициализирует значения регистров 211-218 в N3, когда передаются пакетные данные длиной 4 слота. Контроллер 400 начального значения инициализирует значения регистров 211-218 в N4, когда передаются пакетные данные длиной 8 слотов.

После того, как значения регистров 211-218 инициализированы, выходным сумматором 225 выполняется двоичная операция (или операция ИСКЛЮЧАЮЩЕГО ИЛИ, или операция по модулю 2) между каждым битом входной управляющей информации и конечным значением, полученным от регистра 218 сдвигом направо значений регистров 211-218, и значение результата операции генерируется как последовательность битов обратной связи. Сгенерированная последовательность битов обратной связи подается в качестве входных данных регистра 211 начального значения из регистров 211-218 и в качестве входных данных сумматоров 221-224. В течение этой операции все переключатели SW1-SW3 переключены на верхние контакты. После того, как данная операция выполнена по всем битам 13-битного кадра управляющей информации, переключатели SW1-SW3 переключаются на нижние контакты, так что на переключатели SW1-SW3 подается значение "0". Далее 8 избыточных битов присоединяются сдвигом значений регистров столько раз, каково количество избыточных битов, т.е. 8.

На фиг.8 иллюстрируется структура устройства сверточного декодера в соответствии с вариантом осуществления настоящего изобретения. Что касается фиг.8, устройство сверточного декодера включает в себя сверточный декодер 316 (или 326) и контроллер 600. То есть сверточный декодер служит как сверточный декодер 316 или сверточный декодер 326, показанные на фиг.4.

Сверточный декодер принимает кодированные символы, включенные в состав принятого сигнала, и декодирует принятые кодированные символы в соответствии со скоростью кодирования R, обеспечиваемой от контроллера 600. Сверточный декодер 316, показанный на фиг.4, выполняет декодирование со скоростью кодирования R=1/2 и сверточный декодер 326 выполняет декодирование со скоростью кодирования R=1/4. Однако сверточный декодер 316, показанный на фиг.8, выполняет декодирование в соответствии со скоростью кодирования R (например, R=1/4), обеспечиваемой от контроллера 600. Контроллер 600 выбирает порождающие код полиномы в соответствии с длиной слота кадра управляющей информации для пакетных данных. То есть при передаче 1-слотового кадра контроллер 600 выбирает для декодирования только два порождающих полинома из 4 порождающих код полиномов, подлежащих использованию для сверточного декодера с R=1/4. В отличие от этого, при передаче 2-слотового кадра или 4-слотового кадра контроллер 600 выбирает для декодирования все из 4 порождающих полиномов, предназначенных для использования для сверточного декодера с R=1/4. Контроллер 600 определяет длину слота посредством ОФФК. То есть когда приемник служит в качестве приемника 310, показанного на фиг.4, контроллер 600 определяет, что длина слота кадра управления пакетами равна 1. Когда приемник служит в качестве приемника 320, показанного на фиг.4, контроллер 600 определяет, что длина слота кадра управления пакетами равна 2. Когда приемник служит в качестве приемника 330 или 340, которые показаны на фиг.4, контроллер 600 определяет, что длина слота кадра управления пакетами равна 4.

На фиг.9 иллюстрируется подробная структура элемента 318 (или 328) проверки ЦИК, показанного на фиг.4, в соответствии с вариантом осуществления настоящего изобретения. Устройство соответствует присоединителю 110 битов обнаружения ошибок, подробно показанному на фиг.7, и выполняет такую же операцию, что и присоединитель 110 битов обнаружения ошибок. Однако это устройство отличается от присоединителя 110 битов обнаружения ошибок в том, что принятые биты подаются на SW1. В частности, в элементе 318 (или 328) проверки ЦИК начальное значение регистра ЦИК, используемое для проверки ЦИК на 1-слотовом кадре управления, и начальное значение регистра ЦИК, используемое для проверки ЦИК на 2-слотовом кадре управления, устанавливаются в различные значения.

Что касается фиг.9, элемент проверки ЦИК в соответствии с вариантом осуществления настоящего изобретения включает в себя множество регистров 561-568, множество сумматоров 571-574, выходной сумматор 575, переключатели SW1-SW3, контроллер начального значения 550 и блок 580 принятия решений о наличии ошибки. Контроллер начального значения 550 подает первое начальное значение для первой информации (например, 1-слотовый кадр управляющей информации) или второе начальное значение для второй информации (например, 2-слотовый кадр управляющей информации), как значение для инициализации регистров. Подаваемые начальные значения определяются в соответствии с длиной (N слотов) пакетных данных. Предпочтительно первое начальное значение и второе начальное значение определяются в пределах диапазона значений, соответствующих количеству присоединяемых информационных битов обнаружения ошибок.

Регистры 561-568, количество которых равно количеству присоединяемых информационных битов обнаружения ошибок, каскадированы и инициализированы в соответствии с начальными значениями, поданными от контроллера 550 начального значения. Сумматоры 571-574 установлены в трактах, определяемых по заданному производящему полиному из трактов между регистрами 561-568. Каждый из сумматоров 571-574 добавляет входную последовательность битов, принятую по входному тракту, к последовательности битов обратной связи, и подает выходные данные посредством выходного тракта. Последовательность битов обратной связи относится к последовательности битов, получаемой на выходе выходного сумматора 575 через второй переключатель SW2.

Выходной сумматор 575 и переключатели SW1-SW3 составляют (образуют) оператор для выполнения следующей операции. Оператор при приеме информационной последовательности (первой информации или второй информации) генерирует последовательность битов обратной связи посредством последовательного добавления битов принятой информационной последовательности к выходным битам оконечного регистра 568 и подает сгенерированную последовательность битов обратной связи в сумматоры 571-574 и в регистр 561 начального значения через второй переключатель SW2. Дополнительно оператор после завершения приема принятой информационной последовательности подает входной бит предустановки "0" в сумматоры 571-574 и в регистр 561 начального значения через второй переключатель SW2, последовательно добавляет входной бит предустановки "0" к выходным битам оконечного регистра 568 посредством выходного сумматора 575 и выводит результат суммирования как принятую последовательность информационных битов обнаружения ошибок.

Первый переключатель SW1 выбирает принятую информационную последовательность или входной бит предустановки "0". Первый переключатель SW1 выводит принятую информационную последовательность при приеме (пока идет прием) принятой информационной последовательности и выводит входной бит предустановки "0" после завершения приема принятой информационной последовательности. Выходной сумматор 575 добавляет выходные данные первого переключателя SW1 к выходным битам оконечного регистра 568. Второй переключатель SW2 выбирает выходные данные выходного сумматора 575 или входной бит предустановки "0" и подает выбранное значение в сумматоры 571-574 и в регистр 561 начального значения в качестве последовательности битов обратной связи. Второй переключатель SW2 подает выходные данные выходного сумматора 575 в сумматоры 571-574 и в регистр561 начального значения в течение приема принятой информационной последовательности и подает входной бит предустановки "0" в сумматоры 571-574 и в регистр561 начального значения после завершения приема принятой информационной последовательности. Третий переключатель SW3 выбирает принятую информационную последовательность или выходную последовательность битов, т.е. принятую последовательность информационных битов обнаружения ошибок, выходного сумматора 575. Третий переключатель SW3 выводит принятую информационную последовательность в течение приема принятой информационной последовательности и выводит принятую последовательность информационных битов обнаружения ошибок, обеспеченную от выходного сумматора 575 после завершения приема принятой информационной последовательности.

Блок 580 принятия решения о наличии ошибки сравнивает принятую последовательность информационных битов обнаружения ошибок с последовательностью информационных битов обнаружения ошибок, соответствующей выбранному начальному значению, чтобы таким образом определить, присутствует ли ошибка в принятых битах. То есть блок 580 принятия решения о наличии ошибки решает, что в принятых битах отсутствует ошибка, если принятая последовательность информационных битов обнаружения ошибок идентична последовательности информационных битов обнаружения ошибок, соответствующей выбранному начальному значению. В противоположном случае, если принятая последовательность информационных битов обнаружения ошибок не идентична последовательности информационных битов обнаружения ошибок, соответствующей выбранному начальному значению, блок 580 принятия решения о наличии ошибки решает, что в принятых битах присутствует ошибка. На основании результата решения блока 580 принятия решения о наличии ошибки определитель 350 длины пакета, показанный на фиг.4, может определить длину принятых битов.

Как описано выше, в устройстве, показанном на фиг.9, контроллер 550 начального значения функционирует в соответствии с длиной пакетных данных. Когда первые 13 битов из принятых битов, переданных от передатчика, полностью приняты, переключатели SW1-SW3 переключаются на нижние контакты, так что на переключатели SW1-SW3 подаются входные биты предустановки "0". Следовательно, 8 битов обнаружения ошибок (или избыточных битов) генерируются сдвигом значений регистра столько раз, каково количество битов обнаружения ошибок, т.е. 8. Блок 580 принятия решения о наличии ошибки сравнивает биты обнаружения ошибок (присоединенные передатчиком), включенные в состав принятых битов, с заново сгенерированными битами обнаружения ошибок. Блок 580 принятия решения о наличии ошибки решает, что в принятых битах отсутствует ошибка, если биты обнаружения ошибок, включенные в состав принятых битов, идентичны заново сгенерированным битам обнаружения ошибок. Однако если биты обнаружения ошибок, включенные в состав принятых битов, не идентичны заново сгенерированным битам обнаружения ошибок, блок 580 принятия решения о наличии ошибки решает, что в принятых битах присутствует ошибка. Хотя контроллер 550 начального значения и блок 580 принятия решения о наличии ошибки в настоящем варианте осуществления построены раздельно, эти элементы могут быть реализованы в одном контроллере.

В таблице 2 иллюстрируются результаты компьютерного моделирования, полученные 10000-кратной передачей кадра управляющей информации с длиной слота 2(4) при отсутствии помехи и приемом переданного кадра управляющей информации приемниками 1(2), 2(4), 4(255) и 4(0), в соответствии с вариантом осуществления настоящего изобретения. При сравнении таблицы 1 с таблицей 2 отмечено, что вероятность ошибки из-за 1-слотового кадра управляющей информации значительно снизилась, вызывая снижение вероятности ошибки 2-слотового кадра управляющей информации.

Как описано выше, при кодировании второй последовательности информационных битов, имеющей вторую длину меньшую, чем первая длина первой последовательности информационных битов, настоящее изобретение выбирает только частичные символы из символов, кодированных с первой скоростью кодирования, используемой для кодирования первой последовательности информационных битов с первой длиной. Осуществляя это, настоящее изобретение повышает вероятность того, что приемник последовательности информационных битов, имеющей первую длину, и приемник последовательности информационных битов, имеющей вторую длину, будут генерировать одинаковые выходные данные декодирования. Хотя генерируются одинаковые выходные данные декодирования, принятые символы могут быть идентифицированы посредством различных начальных значений регистров ЦИК, используемых в элементах проверки ЦИК. То есть когда один приемник имеет "Хороший" результат проверки ЦИК, другой приемник имеет 100%-ный "Плохой" результат проверки ЦИК, таким образом уменьшая ошибку ОФФК, которая может произойти, когда оба из двух приемников одновременно имеют "Хороший" результат проверки ЦИК.

В то время как изобретение было показано и описано в настоящем описании со ссылкой на некоторый предпочтительный вариант осуществления, специалистам в данной области техники будет понятно, что в нем могут быть сделаны различные изменения в форме и деталях, не отступая от сущности и объема изобретения, определенных прилагаемой формулой изобретения.

Устройство для кодирования последовательности информационных битов и генерирования кодированных символов относится к технике связи и может быть использовано в системе связи, которая передает пакетные данные и последовательность информационных битов для управления передачей пакетных данных. Технический результат - повышение точности передачи информации. В устройстве кодер кодирует последовательность информационных битов с заданной скоростью кодирования и выводит кодированные символы. Контроллер управляет кодером таким образом, что в случае, когда длина кадра последовательности информационных битов является первой длиной, кодер выводит кодированные символы, а в случае, когда длина кадра последовательности информационных битов является второй длиной, кодер выводит частичные символы из кодированных символов, при этом вторая длина меньше первой длины. 3 н. и 20 з.п. ф-лы, 9 ил., 2 табл.

| RU 99125665 А1, 27.09.2001 | |||

| US 5583889 А, 10.12.1996 | |||

| Почвообрабатывающее орудие | 1977 |

|

SU716529A1 |

Авторы

Даты

2005-08-10—Публикация

2002-11-30—Подача