Изобретение относится к электро- и радиосвязи и может использоваться в проводных, радио-, радиорелейных и метеорных линиях связи.

Известна система связи для непрерывной передачи дискретной информации, в которой перед каждым сообщением посылается «зондирующий ключ». Если приходит этот сигнал, приемник открывается для регистрации сообщения и после приема отправляет квитанцию по обратному каналу. В противном случае приемник остается закрытым и передатчик повторяет сообщение, продолжая попытки для получения нужной квитанции [1]. Однако такая система связи имеет низкую помехоустойчивость, а в стартстопном режиме - недопустимо высокую вероятность ложной тревоги.

Наиболее близкой по технической сущности к предлагаемой системе связи является стартстопная система связи [2], принятая за прототип.

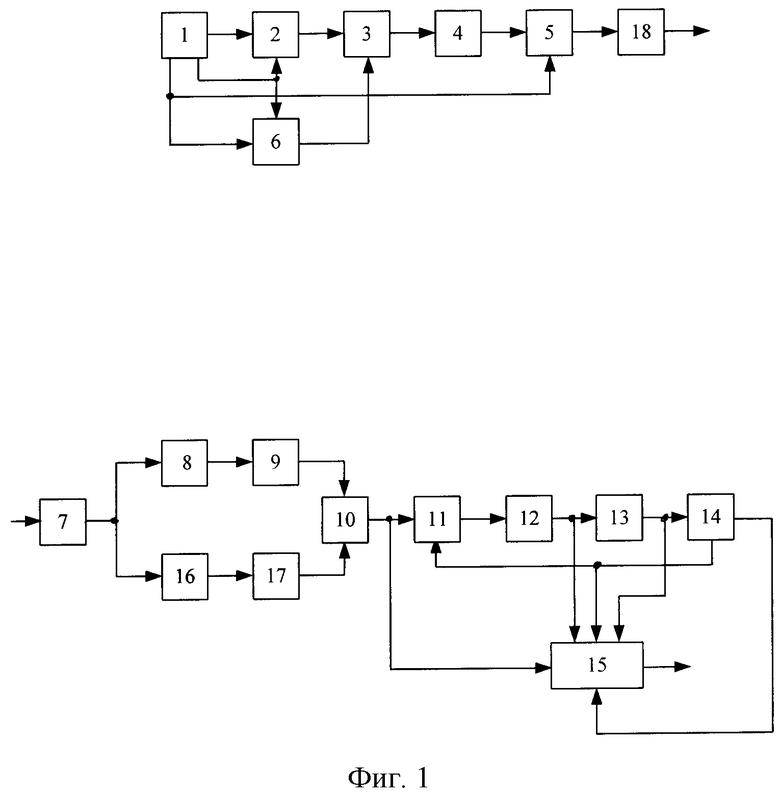

Схема системы-прототипа приведена на фиг.1, где обозначено:

на передающей стороне

1 - источник информации; 2 - регистр сдвига; 3 - сумматор по модулю два (СМД); 4 - генератор несущих частот (ГНЧ); 5 - передатчик; 6 - генератор псевдослучайной последовательности (ГПСП);

на приемной стороне

7 - приемник; 8, 16 - первый и второй полосовой фильзр (ПФ); 9, 17 - первый и второй амплитудный детектор (АД); 10 - вычитающее устройство; 11 - прерыватель; 12 - согласованный фильтр; 13, 15 - первое и второе решающее устройство; 14 - формирователь импульсов; 18 - линия связи.

Система-прототип содержит на передающей стороне последовательно соединенные источник информации 1, регистр сдвига 2, СМД 3, ГНЧ 4 и передатчик 5, выход которого соединен с входом линии связи 18, а также ГПСП 6, выход которого соединен с тактовым входом СМД 3. При этом второй выход источника информации 1 соединен с тактовым входом регистра сдвига 2 и первым входом ГПСП 6, второй вход которого соединен со вторым входом передатчика 5 и третьим выходом источника информации 1.

На приемной стороне - последовательно соединенные приемник 7, первый ПФ 8, первый амплитудный детектор 9, вычитающее устройство 10, прерыватель 11, согласованный фильтр 12, первое решающее устройство 13, формирователь импульсов 14 и второе решающее устройство 15, выход которого является выходом системы связи. А также последовательно соединенные второй полосовой фильтр 16 и второй амплитудный детектор 17, выход которого подключен к второму входу вычитающего устройства 10, выход которого подсоединен к второму входу второго решающего устройства 15, третий, четвертый и пятый входы которого подключены соответственно к выходу согласованного фильтра 12, второму выходу формирователя импульсов 14 и выходу первого решающего устройства 13. Причем второй выход формирователя импульсов 14 соединен со вторым входом прерывателя 11. Кроме того, выход приемника 7 соединен с входом второго ПФ 16. Передающая и приемная стороны соединены посредством линии связи 18.

Система-прототип работает следующим образом.

Источник информации 1 в случайный момент времени создает на первом выходе сообщение, состоящее из n двоичных символов одинаковой длительности τ, а на втором и третьем выходах в момент начала сообщения - сетку из S коротких импульсов с периодом следования τ и положительный импульс, соответственно. При этом в ГПСП 6 формируется синхросигнал - псевдослучайная последовательность, состоящая из S двоичных элементов длительности τ, а сообщение задерживается в регистре сдвига 2 на время, равное sτ. В результате этого на выходе СМД 3 формируется последовательность, состоящая из синхросигнала и сообщения. Элементы этих сигналов используются для управления частотой ГНЧ 4. Полученный частотно-манипулированный сигнал усиливается в передатчике 5, включаемом импульсом длительности (n+S)τ, действующем на третьем выходе источника 1, и передается по линии связи 18.

На приемной стороне после общей фильтрации в приемнике 7 осуществляется демодуляция полученного сигнала в частотном дискриминаторе (блоки 8, 9, 10, 16, 17) и согласованная фильтрация синхросигнала в согласованном фильтре 12, который вместе с блоком 13 составляет первый измерительный канал. В решающем устройстве 13 осуществляется сравнение входного сигнала с определенным порогом и, при условии его превышения сигналом, - формирование в момент действия его максимального значения короткого импульса, который при отсутствии помех точно совпадает по времени с моментом окончания синхросигнала при приеме. По положительному фронту этого импульса на первом выходе формирователя 14 с задержкой на время τ создается сетка из n коротких тактовых импульсов с периодом τ, а на втором - импульс длительности nτ, который с помощью прерывателя 11 отключает вход согласованного фильтра 12 от выхода блока 10. Во втором решающем устройстве 15, предоставляющем собой второй измерительный канал, в момент действия тактовых импульсов осуществляется модульное накопление n сигнальных элементов сообщения, сложение полученной суммы с выходным сигналом согласованного фильтра 12 в момент действия последнего импульса на первом выходе блока 14, сравнение полученного результата с определенным порогом и, в случае его превышения сигналом, - выдача сообщения на выход системы.

Недостаток системы-прототипа - наличие дополнительных энергетических затрат на передачу синхросигнала.

Следует заметить, что первый измерительный канал представляет собой устройство оптимального измерения временного положения синхросигнала и является устройством известным (см., например, с.115, рис.7.2 в книге Ю.С.Лезина «Введение в теорию и технику радиотехнических систем», Радио и связь, 1986).

Изобретение направлено на исключение энергетических затрат на передачу синхросигнала.

Для достижения этого в стартстопную систему связи, содержащую на передающей стороне последовательно соединенные источник информации и первый регистр сдвига (PC), последовательно соединенные генератор несущих частот (ГНЧ) и передатчик, последовательно соединенные генератор псевдослучайной последовательности (ГПСП) и первый сумматор по модулю два (СМД), а на приемной стороне - приемник, последовательно соединенные первый согласованный фильтр (СФ), первое решающее устройство и формирователь импульсов, причем вход приемника посредством линии связи соединен с выходом передатчика, согласно изобретению введены на передающей стороне последовательно соединенные мультиплексор, схема «НЕ», первая схема «3И» и Т-триггер, выход которого соединен со входом ГНЧ, последовательно соединенные генератор тактовых импульсов (ГТИ) и двоичный счетчик (ДС), выходы которого шиной соединены с управляющими входами мультиплексора, последовательно соединенные делитель частоты на два и вторая схема «3И», выход которой подключен к установочному входу Т-триггера, причем первый выход ГТИ соединен также с установочными входами делителя частоты на два и ГПСП, второй выход ГТИ - с тактовым входом первого PC, а третий выход ГТИ - с тактовыми входами делителя частоты на два, ГПСП и вторым входом первого СМД, первый выход делителя частоты на два подключен также к вторым входам ДС и первой схемы «3И», выход мультиплексора соединен со вторым входом второй схемы «3И», третьи входы первой и второй схем «3И» соединены со вторым входом передатчика и подключены к выходу первого СМД, второй выход делителя частоты на два соединен со счетным входом Т-триггера; кроме того, второй выход источника информации соединен с входом ГТИ, выход первого PC шиной соединен с входами мультиплексора, на приемной стороне - последовательно соединенные частотный детектор (ЧД), первый согласованный фильтр (СФ), последовательно соединенные первая схема «ИЛИ-НЕ», RS-триггер и первая схема «И», а также k параллельных блоков обработки и первую и вторую схемы «ИЛИ», при этом первый выход приемника соединен с входом ЧД, второй выход приемника - с входом второго СФ, (k+1) выход формирователя импульсов соединен со вторым входом RS-триггера и первым входом первой схемы «И», выход которой соединен с третьими (с) входами k параллельных блоков обработки, первые входы (а) которых соединены с выходом первого СФ, вторые входы (б) соединены по одному с выходами (1-k) формирователя импульсов, первые выходы (д) подключены по одному к входам (1-k) первой схемы «ИЛИ-НЕ» соответственно, вторые выходы (е) по одному соединены с k входами первой схемы «ИЛИ» соответственно, а третьи выходы (ж) - с k входами второй схемы «ИЛИ» соответственно, выход которой является информационным выходом системы, при этом каждый из k параллельных блоков обработки содержит последовательно соединенные формирователь символов (ФС) и второй РС, n выходов которого попарно соединены с первым и вторым входами п параллельных СМД [2-(n-1)], выходы которых соединены с соответствующими входами второй схемы «ИЛИ-НЕ», выход которой соединен с входами четвертой схемы «И» и второй схемы «НЕ», выход которой соединен с первым входом второй схемы «И», выход которой является вторым выходом (е) блока обработки, кроме того, выход элемента задержки соединен с тактовыми входами второго и третьего PC, выход последнего является третьим выходом (ж) блока обработки, при этом первые входы n параллельных СМД [2-(n-1)] соединены по одному с первыми входами n параллельных [2-(n+1)] схем «И» соответственно, выходы которых подсоединены к соответствующим входам третьего PC, выход третьей схемы «И» соединен с первым выходом (д) блока обработки, с третьими входами n параллельных СМД [2-(n-1)] и со вторыми входами второй и четвертой схем «И», при этом выход последней соединен со вторыми входами n параллельных [2-(n+1)] схем «И», кроме того, вход элемента задержки соединен с первым входом третьей схемы «И» и со вторым входом ФС и является входом (б) блока обработки, второй вход третьей схемы «И» является третьим входом (с) блока обработки.

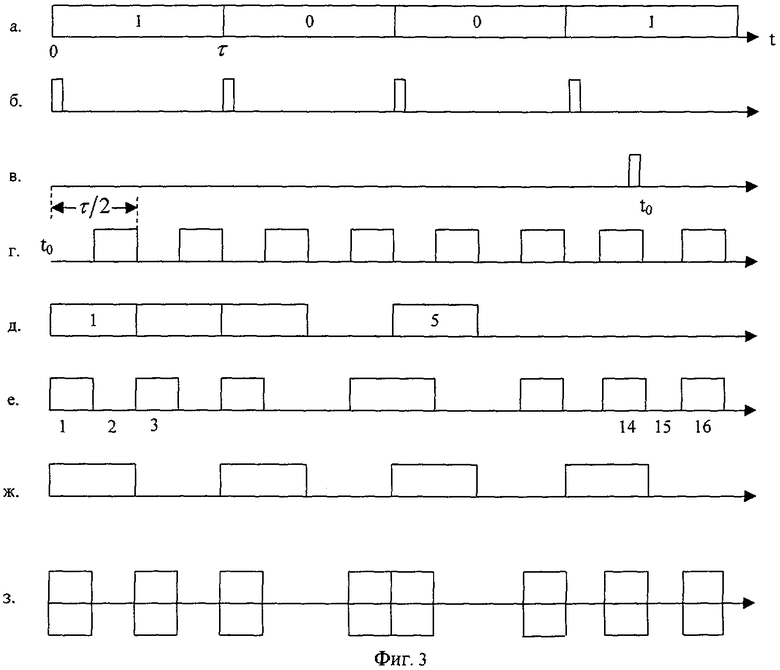

На фиг.2 и 3 представлены соответственно функциональная схема предлагаемой стартстопной системы связи и временные диаграммы, иллюстрирующие ее работу.

На фиг.2 введены следующие обозначения:

на передающей стороне

1 - источник информации; 2 - первый регистр сдвига (РС);3 - мультиплексор (МП); 4 - первая схема «НЕ»; 5, 12 - первая и вторая схема «ЗИ»; 6 - Т-триггер; 7 - генератор несущей частоты (ГНЧ); 8 - передатчик; 9 - генератор тактовых импульсов (ГТИ); 10 - двоичный счетчик (ДС); 11 - делитель частоты на два (ДЧ); 13 - генератор псевдослучайной последовательности (ГПСП); 14 - первый сумматор по модулю два (СМД);

на приемной стороне

15 - приемник; 16 - частотный детектор (ЧД); 17, 18 - первый и второй согласованный фильтр (СФ); 19 - решающее устройство (РУ); 20 - формирователь импульсов (ФИ); 21, 32, 34, 35 - первая, вторая, третья и четвертая схема «И»; 22, 30 - первая и вторая схема «ИЛИ-НЕ»; 23 - RS-триггер; (24-1)-(24-k) - k параллельные блоки обработки; 25, 26 - первая и вторая схемы «ИЛИ»; 27 - формирователь символов (ФС); 28, 37- второй и третий регистр сдвига (PC); (29-1)-(29-n) - n параллельные [2-(n+1)] СМД; 31 - вторая схема «НЕ»; 33 - элемент задержки (ЭЗ); (36-1)÷(36-n) - n параллельные [2-(n+1)] схемы «И»; 38 - линия связи.

Стартстопная система связи содержит на передающей стороне последовательно соединенные источник информации 1, PC 2, МП 3, схему «НЕ» 4, схему «3И» 5, Т-триггер 6, ГНЧ 7 и передатчик 8, последовательно соединенные ГТИ 9 и ДС 10, выходы которого шиной соединены с управляющими входами МП 3, последовательно соединенные ДЧ 11 и вторую схему «3И» 12, выход которой подключен к установочному входу Т-триггера 6, причем первый выход ГТИ 9 соединен также с установочными входами ДЧ 11 и ГПСП 13, выход которого соединен с первым входом первого СМД 14, второй выход ГТИ 9 - с тактовым входом PC 2, а третий - с тактовыми входами ДЧ 11, ГПСП 13 и вторым входом первого СМД 14, первый выход ДЧ 11 подключен также к вторым входам ДС 10 и первой схемы «3И» 5, выход МП 3 соединен со вторым входом второй схемы «3И» 12, третьи входы первой 5 и второй 12 схем «3И» и второй вход передатчика 8 подключены к выходу первого СМД 14, второй выход ДЧ 11 соединен со счетным входом Т-триггера 6. При этом второй выход источника информации 1 соединен с входом ГТИ 9.

На приемной стороне содержит последовательно соединенные приемник 15, ЧД 16 и первый СФ 17, последовательно соединенные второй СФ 18, РУ 19, ФИ 20 и схему «И» 21, последовательно соединенные схему «ИЛИ-НЕ» 22 и RS-триггер 23, выход которого подключен ко второму входу схемы «И» 21, а второй вход RS-триггера 23 соединен с первым входом схемы «И» 21, k параллельных блоков обработки [(24.1)-(24.k)], первые входы (а) которых подключены к выходу первого СФ 17, вторые входы (б) соединены по одному с выходами 1-k ФИ 20, а третьи (с) - с выходом схемы «И» 21, первые выходы (д) блоков обработки 24 подключены по одному к входам 1-k схемы «ИЛИ-НЕ» 22, вторые (е) - к входам первой схемы «ИЛИ» 25, а третьи (ж) - ко входам второй схемы «ИЛИ» 26, выход которой является информационным выходом системы. Каждый из блоков обработки (24-1)-(24-k) содержит последовательно соединенные ФС 27 и второй PC 28, n параллельных СМД (29-1)-(29-n), последовательно соединенные вторую схему «ИЛИ-НЕ» 30, вторую схему «НЕ» 31 и вторую схему «И» 32, выход которой соединен с выходом (е) блока обработки 24, выход ЭЗ 33 соединен с тактовым входом PC 28, последовательно соединенные третью 34 и четвертую 35 схемы «И», n [2-(n+1)] параллельных схем «И» (36-1)-(36-n), выходы которых подключены к соответствующим входам третьего PC 37, тактовый вход которого соединен выходом ЭЗ 33, а выход соединен с выходом (ж) блока обработки 24, причем определенные выходы PC 28 попарно подключены к первому и второму входам параллельных СМД 29 [2-(n+1)]-го, выходы которых по одному соединены с соответствующими входами второй схемы «ИЛИ-НЕ» 30, первые входы параллельных СМД 29 соединены по одному с первыми входами схем «И» (36-1)-(36-n), а третьи входы СМД 29 подключены к выходу схемы «И» 34, который подключен также ко второму входу схемы «И» 32 и к выходу (д) блока обработки 24, вход ФС 27 соединен со входом (а), а его второй вход - со входом (б) блока обработки 24, подключенного также к входам ЭЗ 33 и первому входу схемы «И» 34, второй вход которой соединен со входом (с) блока обработки 24, второй вход схемы «И» 35 подключен к выходу схемы «ИЛИ-НЕ» 30, а ее выход соединен со вторыми входами параллельных схем «И» 36, выход схемы «ИЛИ» 25 является дополнительным выходом системы. При этом вход второго СФ 18 соединен со вторым выходом приемника 15.

Передающая и приемная стороны системы соединены посредством линии связи 38.

Стартстопная система работает следующим образом.

В случайный момент времени (t=0, фиг.3а) на первом выходе источника информации 1 создаются n>5 информационных символов («0» или «1») длительности τ (например, n=4-1001), а на его втором выходе в тот же момент времени - короткий импульс, поступающий на вход ГТИ 9, на втором выходе которого при этом формируются n коротких импульсов (фиг.3б), записывающие информационные символы в n-разрядный регистр сдвига PC 2. На первом выходе ГТИ 9 создается короткий импульс с задним фронтом, действующим в момент времени t0 (фиг.3в), который устанавливает на выходах счетчика ДС 10 (в шине) двоичное число в десятичной форме, равное единице, первый выход ДЧ 11 - в единичное состояние, а его второй (инверсный) выход - в нулевое состояние и запускает ГПСП 13. На третьем выходе ГТИ 9 формируется меандр (фиг.3г), состоящий из 2n импульсов длительности τ/4, поступающий на тактовые входы ДЧ 11 и ГПСП 13 и на второй вход СМД 14; в результате этого на выходе ГПСП 13 формируется S - импульсная псевдослучайная последовательность (ПСП) (S≥9, S=5 на фиг.3д, для примера), а на выходе СМД 14 - результат ее суммирования с меандром (фиг.3е). Этот сигнал управляет работой блоков 5, 12 и открывает положительными импульсами передатчик 8 для передачи на его выход входного сигнала. Таким образом, в момент действия заднего фронта импульса (фиг.3в) к выходу МП 3 подключается n-й разряд PC 2, в котором записан первый информационный символ («1», фиг.3а). Этот символ поступает на второй вход блока 12, а его инверсия - на первый вход блока 5. Поскольку при этом импульсы на всех трех входах блока 12 оказываются положительными, то на ее выходе создается положительный перепад напряжения, который устанавливает Т-триггер 6 в единичное состояние, и на выходе ГНЧ 7 создается гармонический сигнал с частотой f1. Задний фронт первого импульса на третьем выходе ГТИ 9 изменяет сигнал на первом выходе ДЧ 11 на инверсный (фиг.3ж); при этом на его втором выходе создается положительный импульс, который переводит передним фронтом Т-триггер 6 в нулевое состояние, при котором на выходе ГНЧ 7 формируется сигнал с частотой f2. Таким образом, информационному символу «1» на выходе передатчика соответствует последовательность двух сигналов длительности τ/4 с частотами f1 и f2. При появлении второго положительного импульса на первом выходе ДЧ 11 на выходах ДС 10 (в шине) устанавливается двоичное число, равное двум, и через МП 3 на его выход считывается символ с (n-1)-го разряда PC 2 и, если его значение равно «0», то положительный сигнал будет действовать на первом входе блока 5, Т-триггер 6 установится в нулевое состояние и на выходе ГНЧ 7 установится сигнал частоты f2 (а затем f1). Т.е. информационному символу «0» на выходе передатчика должна соответствовать последовательность из двух сигналов с частотами f2, f1 и т. д.

На приемной стороне сигнал с первого выхода приемника 15, представляющего собой выход усилителя промежуточной частоты с ограничителем, поступает на вход ЧД 16, на выходе которого частоте f1 соответствует положительный, a f2 - отрицательный сигнал, и затем после фильтрации в первом согласованном (квазисогласованном) фильтре СФ 17 - на входы формирователей символов ФС 27 блоков обработки (24-1)-(24-k) (k=2-5). Со второго выхода приемника 15 амплитудно продетектированный сигнал после фильтрации во втором согласованном (квазисогласованном) фильтре для ПСП СФ 18 поступает на вход РУ 19, в котором осуществляется сравнение входного сигнала с определенным порогом и, при условии его превышения сигналом, формирование в момент действия его максимального значения короткого импульса, который при отсутствии помех точно совпадает с моментом окончания ПСП при приеме. На выходах (1-k) ФИ 20 формируются последовательности коротких тактовых импульсов с периодом τ/4 со сдвигом по времени у i-й из них (i=2,...k) относительно последовательности на первом выходе - (τ/4 k)(i-1), на (k+1)-м выходе - положительный импульс длительности τ/2 с задержкой относительно его входного импульса на (4n-2S+1)τ/4, который передним фронтом устанавливает блок 23 в единичное состояние. Последовательность c j-го выхода ФИ 20 (j=1...k) поступает на второй вход ФС 27, вход элемента задержки 33 и первый вход схемы 34 j-го блока обработки 24-j. На выходе ФС 27 формируется символ «1» длительности τ/4, если в момент действия импульса на его втором входе сигнал на первом входе положительный, и символ «0» - если отрицательный. Задержанные на интервал времени меньше τ/4 в блоке 33 входные импульсы записывают задними фронтами символы, поступающие с выхода ФС 27 в 4n-разрядный PC 28. Если импульс на первом входе схемы «И» 34 совпадет по времени с импульсом длительности τ/4, действующим на ее втором входе, то ее выходной импульс через схему «ИЛИ-НЕ» 22 установит RS-триггер 23 в нулевое состояние и на вторые входы схем «И» 34 всех блоков обработки поступит нулевой сигнал, запрещающий передачу на их входы тактовых импульсов. При отсутствии помех в момент действия импульса на выходе блока 34 j-го блока обработки 24-j (для ПСП фиг.3д) на выходах разрядов PC 28 с номерами 1, 8, 12, 14 будут действовать сигналы логического нуля, а с номерами 3, 5, 9 и 16 - сигналы логической единицы. К первому и второму входам сумматоров (29-1)-(29-n) подключены выходы разрядов второго PC 28 с номерами 3, 1; 5, 8; 9, 12 и 16, 14, соответственно. В результате при действии на их третьих входах импульса с выхода схемы 34 на их выходах уровень сигналов будет нулевым, а на выходе схемы 30 - единичным. При этом схема «И» 35 будет открытой для выходного импульса блока 34, который считает информационные символы со входов схем (36-1)-(36-n) на их выходы и в третий PC 37. Тактовые импульсы, поступающие с выхода блока 33, считают информацию из PC 37 через схему «ИЛИ» 26 на информационный выход системы. Если при наличии помех на первом и втором входах хотя бы одного из блоков 29 установится одинаковый уровень, то на выходе схемы 30 установится сигнал логического «0», а на выходе схемы «И» 32 - логической «1». Поэтому выходной импульс блока 34 пройдет через схему «И» 32 и блок 25 на дополнительный выход системы. Таким образом, выносится решение о наличии ошибок в сообщении. Информация на выход блока 26 не выдается и при наличии обратного канала по нему посылается запрос на передающую сторону о повторении сообщений.

Таким образом, в системе осуществляется совместная передача синхросигнала (ПСП) и сообщения, применение предлагаемой стартстопной системы связи позволяет исключить дополнительные энергетические затраты на передачу синхросигнала.

Все блоки, входящие в систему связи, являются известными. В качестве приемника 15 с двумя выходами может быть использована одна из микросхем (например, СХА 1003 BM/BN), описанных в разделе «Микросхемы современных связных ЧМ приемников» (с.14-25, CHIP NEWS, №1, янв. 1996). Формирователь символов 27 может быть выполнен, например, на стробируемом компараторе К.554СА1 (с.310, «Аналоговые и цифровые интегральные микросхемы», под ред. С.В.Якубовского, Радио и связь, 1984).

Источники информации

1. Каневский З.М., Ледовских В.И. Передача дискретной информации по каналам с обратной связью с прерываниями. «Электросвязь, №2, 1970.

2. Г.Б.Волобуев, В.И.Ледовских. О помехоустойчивости стартстопных систем связи с частотной манипуляцией сигнала. «Теория и техника радиосвязи», вып.2, 1998.

| название | год | авторы | номер документа |

|---|---|---|---|

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2003 |

|

RU2252489C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2006 |

|

RU2308164C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2006 |

|

RU2316905C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ СИГНАЛА | 2008 |

|

RU2357372C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2308163C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2005 |

|

RU2284668C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396721C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2229200C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2000 |

|

RU2177209C2 |

Изобретение относится к электро- и радиосвязи и может использоваться в проводных, радио-, радиорелейных и метеорных линиях связи. Технический результат заключается в исключении дополнительных энергетических затрат на передачу синхросигнала, поскольку в системе связи осуществляется совместная передача синхросигнала (ПСП) и сообщения. Технический результат достигается тем, что в систему стартстопной связи введены на передающей стороне: мультиплексор 3, схема «НЕ» 4, первая 5 и вторая 12 схемы «3И», Т-триггер 6, генератор тактовых импульсов 9, двоичный счетчик 10, делитель частоты 11; на приемной стороне: частотный детектор 16, второй согласованный фильтр 18, первая схема «И» 21, первая схема «ИЛИ-НЕ» 22, RS-триггер 10, первая 25 и вторая 26 схемы «ИЛИ» и k параллельных блоков обработки (24-1)-(24-k), 3 ил.

Стартстопная система связи, содержащая на передающей стороне последовательно соединенные источник информации и первый регистр сдвига (PC), последовательно соединенные генератор несущих частот (ГНЧ) и передатчик, последовательно соединенные генератор псевдослучайной последовательности (ГПСП) и первый сумматор по модулю два (СМД), а на приемной стороне - приемник, последовательно соединенные второй согласованный фильтр (СФ), первое решающее устройство и формирователь импульсов, причем вход приемника посредством линии связи соединен с выходом передатчика, отличающаяся тем, что введены на передающей стороне последовательно соединенные мультиплексор, схема НЕ, первая схема 3И и Т-триггер, выход которого соединен со входом ГНЧ, последовательно соединенные генератор тактовых импульсов (ГТИ) и двоичный счетчик (ДС), выходы которого шиной соединены с управляющими входами мультиплексора, последовательно соединенные делитель частоты на два и вторая схема 3И, выход которой подключен к установочному входу Т-триггера, причем первый выход ГТИ соединен также с установочными входами делителя частоты на два и ГПСП, второй выход ГТИ - с тактовым входом первого PC, а третий выход ГТИ - с тактовыми входами делителя частоты на два, ГПСП и вторым входом первого СМД, первый выход делителя частоты на два подключен также к вторым входам ДС и первой схемы 3И, выход мультиплексора соединен со вторым входом второй схемы 3И, третьи входы первой и второй схем 3И соединены со вторым входом передатчика и подключены к выходу первого СМД, второй выход делителя частоты на два соединен со счетным входом Т-триггера; кроме того, второй выход источника информации соединен с входом ГТИ, выход первого PC шиной соединен с входами мультиплексора, на приемной стороне - последовательно соединенные частотный детектор (ЧД), первый согласованный фильтр (СФ), последовательно соединенные первая схема ИЛИ-НЕ, RS-триггер и первая схема И, а также k параллельных блоков обработки и первая и вторая схемы ИЛИ, при этом первый выход приемника соединен с входом ЧД, второй выход приемника - с входом второго СФ, (k+1) выход формирователя импульсов соединен со вторым входом RS-триггера и первым входом первой схемы И, выход которой соединен с третьими (с) входами k параллельных блоков обработки, первые входы (а) которых соединены с выходом первого СФ, вторые входы (б) соединены по одному с выходами (1-k) формирователя импульсов, первые выходы (д) подключены по одному к входам (1-k) первой схемы ИЛИ-НЕ соответственно, вторые выходы (е) по одному соединены с k входами первой схемы ИЛИ соответственно, а третьи выходы (ж) - с k входами второй схемы ИЛИ соответственно, выход которой является информационным выходом системы, при этом каждый из k параллельных блоков обработки содержит последовательно соединенные формирователь символов (ФС) и второй РС, n выходов которого попарно соединены с первым и вторым входами n параллельных СМД [2-(n-1)], выходы которых соединены с соответствующими входами второй схемы ИЛИ-НЕ, выход которой соединен с входами четвертой схемы И и второй схемы НЕ, выход которой соединен с первым входом второй схемы И, выход которой является вторым выходом (е) блока обработки, кроме того, выход элемента задержки соединен с тактовыми входами второго и третьего PC, выход последнего является третьим выходом (ж) блока обработки, при этом первые входы n параллельных СМД [2-(n-1)] соединены по одному с первыми входами n параллельных [2-(n+1)] схем И соответственно, выходы которых подсоединены к соответствующим входам третьего PC, выход третьей схемы И соединен с первым выходом (д) блока обработки, с третьими входами n параллельных СМД [2-(n-1)] и со вторыми входами второй и четвертой схем И, при этом выход последней соединен со вторыми входами n параллельных [2-(n+1)] схем И, кроме того, вход элемента задержки соединен с первым входом третьей схемы И и со вторым входом ФС, и является входом (б) блока обработки, второй вход третьей схемы И является третьим входом (с) блока обработки, первый вход (а) которого является первым входом ФС.

| ВОЛОБУЕВ Г.Б., ЛЕДОВСКИХ В.И | |||

| О помехоустойчивости стартстопных систем связи с частотной манипуляцией сигнала | |||

| «Теория и техника радиосвязи» | |||

| Вып | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

2006-02-20—Публикация

2004-07-20—Подача