Область техники, к которой относится изобретение

Настоящее изобретение относится к буферизации между схемами синхронизации, осуществляющими связь посредством глобальной синхронной шины, в частности к уменьшению нагрузки шины в системе мультиплексированной шины с разделением по времени (TDM).

Уровень техники

Взаимодействующие схемы синхронизации, осуществляющие связь по общей синхронной шине, будут в случаях, когда необходимо, чтобы более одного приемопередатчика для каждой печатной платы (PCB) включали в себя использование буферов, чтобы избежать ухудшения сигнала или звон на шине.

Например, более низкий уровень в сетях связи, такой как уровень связности в базовой сети сотового окружения может рассматриваться как уровень распределенных ресурсов для управления потоками данных. Коммутаторы и мультиплексоры являются некоторыми из основных компонентов для этой цели. В сложных сетях связи, управляющих данными различных форматов и варьирующих скорости передачи данных, очень важно поддерживать на минимуме степень ухудшения сигнала и величину битовых ошибок.

Обычно коммутаторы содержат несколько последовательных входов и выходов. Поток данных одного входа может быть направлен целиком на определенную выходную линию, или может состоять из смеси кадров мультиплексированных данных с разделением во времени, которые должны быть распределены на несколько выходов. Различные линии могут проходить через разные интерфейсы, например Е1, Е2, Е3 и STM-1.

Коммутация происходит в системе мультиплексированной шины с разделением во времени, содержащей шину данных (ДАННЫЕ) (обычно 8 бит) и схему синхронизации данных (TDM CLK). Временная область разделена на кадры, причем каждый кадр имеет фиксированную длительность (обычно 125 мкс), причем начало каждого кадра указывается с помощью сигнала синхронизации кадра (ССФ-FSYNC). Кадры разделены на фиксированное число временных интервалов, идентифицируемых локальными счетчиками временных интервалов. В каждом временном интервале данные могут быть переданы от передатчика на приемник путем использования мультиплексирования с разделением во времени (TDM).

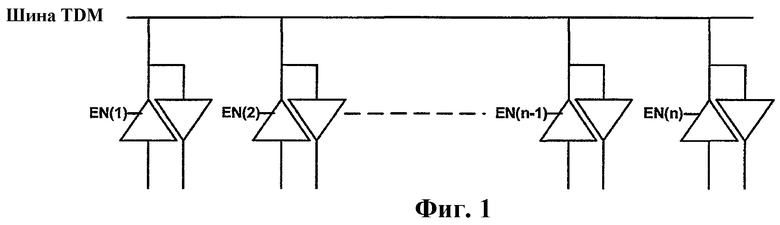

Несколько передатчиков и приемников способны осуществлять связь друг с другом через TDM шину, когда каждый локальный счетчик временных интервалов синхронизирован с ССФ. Фиг.1 представляет, как приемопередатчики шины обычно подключаются к шине TDM задней панели. EN(1..N) - это сигналы разрешения (активации) временных интервалов, обеспечивающие выдачу временных интервалов на шину TDM.

Архитектура, указанная выше на чертеже, т.е. система с большим числом нагрузок, может иметь проблемы, связанные с ухудшением принятых сигналов. Чем большим нагрузкам подвергается шина, тем больше будет происходить затухание сигнала.

Другой недостаток, вызывающий ухудшение сигнала в результате двух или более приемопередатчиков на одной печатной плате, подключенных к одному и тому же разъему шины TDM, заключается в увеличении длин шлейфов (проводников). Множественное подключение будет обусловливать большие длины шлейфов от приемопередатчика к шине TDM из-за физических размеров корпусов ИС (интегральной схемы) приемопередатчика. Большая длина шлейфов может привести к слабым оконечным нагрузкам шины, что в свою очередь может вызвать отражения и ослабления сигнала, которые могут увеличить частоту появления битовых ошибок и частоту повторных передач и снизить качество данных.

Другой путь решения проблемы нагрузки шины состоит в том, чтобы иметь древовидную структуру буферов, т.е. соединение вместе пар нагрузок посредством пассивных буферов и, в случае более двух нагрузок, соединение выхода буферов посредством дополнительных буферов, пока не останется только одна нагрузка для подключения к шине TDM. Однако это вводит временные задержки, которые неприемлемы в большинстве приложений. Только задержки, которые являются кратными целым кадрам, обычно принимаются для общей задержки от выхода локальной шины TDM на шину TDM коммутационной платы и обратно на локальную шину TDM.

Из предыдущего уровня техники известны конструктивные решения, которые могут представлять некоторый интерес.

Из патента США 5758131 известен адаптер шины для синхронизации данных между двумя различными интервалами синхронизации. Адаптер шины включает в себя буфер обратного магазинного типа (FIFO - первым прибыл, первым обслужен) для хранения данных.

Патент США 4788660 описывает схему управления буфером шины данных. Назначение этой схемы состоит в том, чтобы обеспечивать оптимальную задержку для доступов по шине центрального процессора (ЦП, CPU) между ЦП и низкоскоростными устройствами. Данные задерживаются на некоторое число циклов синхронизации.

Заявка на Европейский патент EP 388574 A1 описывает способ для устранения «несправедливости» при распределении нагрузки по узлам и терминалам в сети. Элементы задержки используются для задержки данных.

Помимо того, что эти три публикации описывают различные элементы задержки и задерживание данных, они предназначены для других целей и имеют очень мало общего с настоящим изобретением.

Сущность изобретения

Задача настоящего изобретения состоит в создании устройства, которое устраняет вышеописанные недостатки. Признаки, сформулированные в прилагаемой формуле, характеризуют это решение.

В частности, настоящее изобретение предлагает устройство в узле с коммутацией цепей с (глобальной) мультиплексированной шиной передачи данных с разделением по времени - TDM коммутационной платы, передающей кадры данных временных интервалов, между одной или более печатными платами (РСВ), причем каждая включает в себя ряд нагрузок, передающих данные как в направлении RX (приемника), так и в направлении ТХ (передатчика). Это устройство включает в себя, по меньшей мере, локальную шину (передачи) данных TDM на каждой печатной плате, к которой подключено соответствующее число нагрузок, и промежуточную логическую схему, управляемую ЦП, в каждом направлении соединяющую локальную шину данных TDM с глобальной шиной данных TDM, причем логическая схема включает в себя буфер обратного магазинного типа, через который временные интервалы данных от локальной или глобальной шины данных TDM записываются на локальную или глобальную шину данных TDM и считываются из нее, вводя разность фаз, обеспечивающую общую задержку для любого временного интервала, передаваемого от локальной шины TDM на глобальную шину данных TDM и обратно на локальную шину данных TDM, равную длительности целого числа кадров данных.

Краткое описание чертежей

Чтобы сделать настоящее изобретение более понятным, в обсуждении, которое следует далее, приводятся ссылки на прилагаемые чертежи.

Фиг.1 иллюстрирует типичное подключение шины согласно уровню техники.

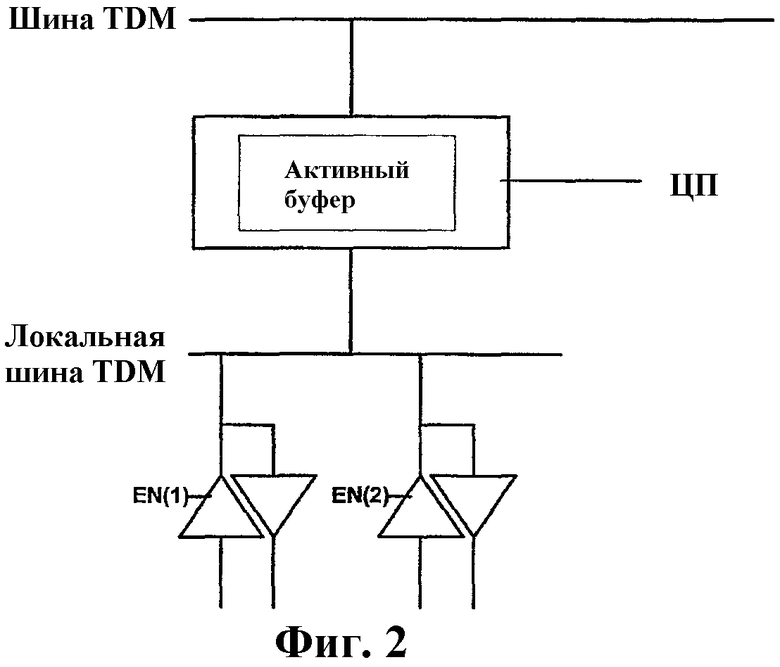

Фиг.2 представляет общий вид подключения шины согласно одному варианту осуществления настоящего изобретения.

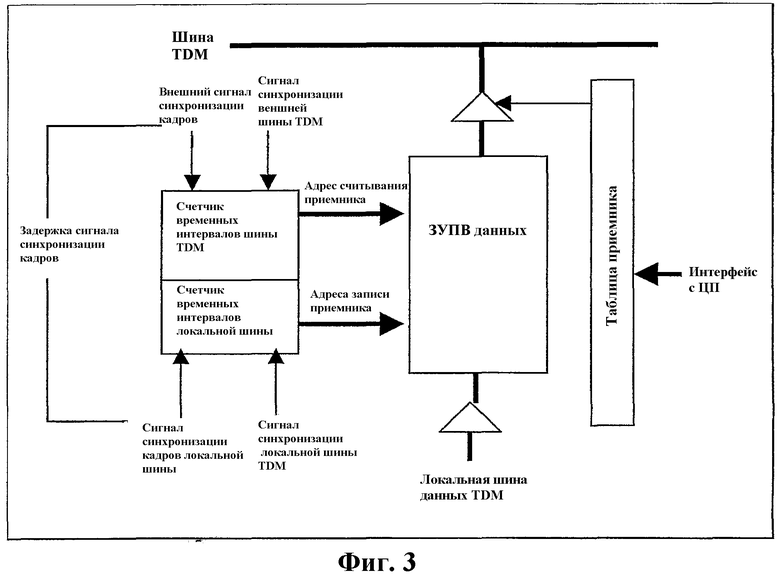

Фиг.3 представляет конструкцию активного буфера в направлении приемника согласно одному варианту осуществления настоящего изобретения.

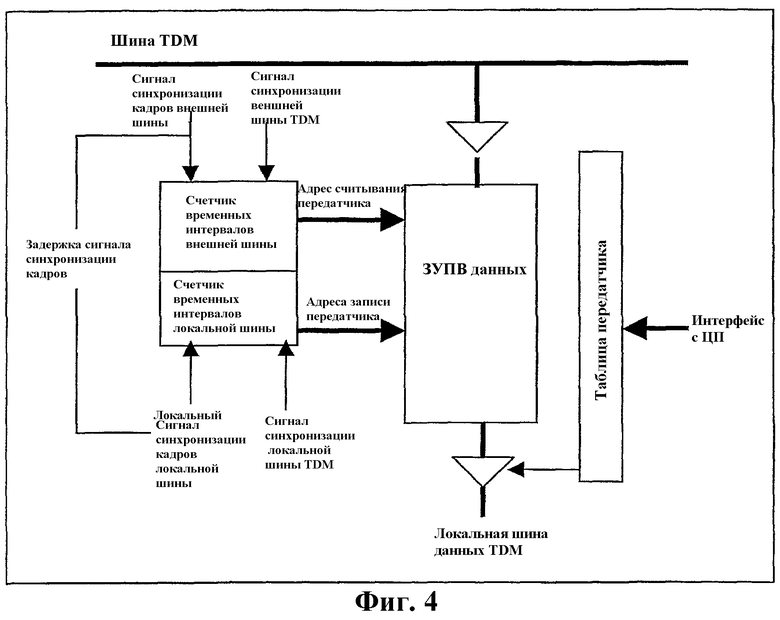

Фиг.4 представляет конструкцию активного буфера в направлении передатчика согласно одному варианту осуществления настоящего изобретения.

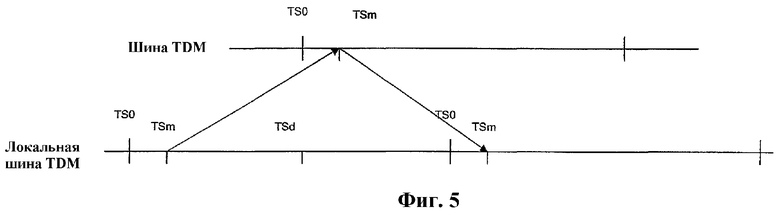

Фиг.5 представляет задержку между шиной TDM и локальной шиной TDM при использовании предпочтительного варианта осуществления настоящего изобретения.

Описание предпочтительного варианта осуществления настоящего изобретения.

Настоящее изобретение предлагает новое устройство (схему), в целом решающее проблемы, описанные выше, посредством введения локальной синхронной шины данных (ниже называемой локальной шиной данных TDM) и активного буфера, включающего в себя логическую схему, управляемую центральным процессором ЦП, между нагрузками приемопередатчика и глобальной синхронной шиной данных (ниже называемой глобальной шиной данных TDM), как показано на Фиг.2. Активные буферы в направлениях приемника и передатчика вместе обеспечивают временную задержку для данных, передаваемых от первой локальной синхронной шины данных на синхронную шину данных коммутационной платы и обратно на вторую локальную синхронную шину данных с длительностью управляемой задержки, в предпочтительном варианте осуществления, описанном ниже, с точной длительностью одного кадра TDM или целым числом кадров TDM.

Ниже описывается предпочтительный вариант осуществления настоящего изобретения. Однако настоящее изобретение не ограничивается этим примером. Другие вариации и изменения могут выполняться без отступления от объема правовой охраны изобретения, как определено в прилагаемом независимом пункте формулы и соответствующих эквивалентных пунктах.

Согласно изобретению активный буфер содержит отдельные цифровые аппаратные средства, такие как специализированная интегральная схема (ASIC) или программируемая логика, как FPGA (вентильная матрица с программированием пользователем), CPLD (сложное устройство с программируемой логикой) и т.д., расположенные между локальной шиной TDM на печатной плате и шиной TDM на коммутационной плате. Настоящее изобретение позволяет сократить полную нагрузку шины на шине TDM, поскольку число приемопередатчиков, подключенных к шине, будет сокращено от двух или более до одного в расчете на печатную плату.

Настоящее изобретение также позволяет сократить длины шлейфов (проводников) между приемопередатчиками шины TDM и шиной, потому что расстояние между приемопередатчиком и разъемом шины будет короче, чем в случае двух или более приемопередатчиков, непосредственно подключенных к разъему. Буфер должен включать в себя приемопередатчики шин (т.е. LVDS шины - низковольтная дифференциальная передача сигнала), которые совместимы с исходными приемопередатчиками. Они должны также содержать память (RAM-ЗУПВ - запоминающее устройство с произвольной выборкой) для хранения, по меньшей мере, одного кадра данных и таблицы приемника и передатчика, которые хранят информацию о тех временных интервалах, которые используются на отдельных шинах.

Фиг.3 и 4 представляют структуры активных буферов в направлениях приемника и передатчика, соответственно. Ниже предпочтительный активный буфер в направлении приемника описан с дополнительными подробностями, но эквивалентное описание также применимо к активному буферу, как показано на Фиг.4, за исключением того, что буфер приемника адаптируется для потока данных в обратном направлении.

Кроме ЗУПВ данных, которое предпочтительно имеет признаки FIFO (первым прибыл, первым обслужен), активный буфер включает в себя таблицу приемника, «шину TDM со счетчиком временных интервалов», «локальную шину со счетчиком временных интервалов», буфер записи и считывания (в/из ЗУПВ данных). Данные синхронизируются в ЗУПВ данных посредством локального сигнала синхронизации TDM_CLK LOCAL, который является сигналом синхронизации TDM локальной шины TDM, и выходят из ЗУПВ с помощью сигнала TDM_CLK EXTERN (внешний сигнал синхронизации), представляющий собой сигнал синхронизации TDM шины TDM коммутационной платы, управляемой главной схемой системы. Счетчики временных интервалов имеют в качестве входов FSYNC EXTERNAL, TDM_CLK EXTERNAL и FSYNC LOCAL, TDM_CLK LOCAL, соответственно. Счетчики временных интервалов инициируются соответствующим сигналом FSYNC, используя ту же частоту, как и их соответствующие TDM_CLK, и отслеживают те временные интервалы, которые есть на шине. Выходные сигналы этих счетчиков (READ RX ADDR и WRITE RX ADDR - СЧИТЫВАНИЕ АДРЕСА ПРИЕМНИКА и ЗАПИСЬ АДРЕСА ПРИЕМНИКА) используются для обращения к ЗУПВ данных, т.е. READ RX ADDR указывает то место в ЗУПВ, в котором расположен временной интервал, который возможно должен считываться на шину TDM коммутационной платы, а WRITE RX ADDR указывает на то место в ЗУПВ, в котором временной интервал, который возможно будет записан в ЗУПВ данных, должен быть расположен. Дополнительно, TDM_CLK EXTERN и TDM_CLK LOCAL (также как для FSYNC EXTERN и FSYNC LOCAL) должны иметь одну и ту же частоту, но разность фаз должна быть настроена так, чтобы обеспечить предпочтительную задержку от локальной шины TDM на шину TDM коммутационной платы. Фактически разница между READ RX ADDR и WRITE RX ADDR, которая в свою очередь контролируется посредством TDM_CLK и FSYNC с помощью счетчиков временных интервалов, представляет действительную задержку в терминах временных интервалов через активный буфер. TDM_CLK LOCAL и FSYNC LOCAL предпочтительно определяются из TDM_CLK EXTERN и FSYNC EXTERN, соответственно, но также должно быть возможно получить TDM_CLK EXTERN и FSYNC EXTERN из TDM_CLK LOCAL и FSYNC LOCAL, соответственно.

Содержание таблицы приемника централизованно управляется посредством ЦП рассматриваемой системы. Один бит на временной интервал приписывается местоположению каждого временного интервала в ЗУПВ данных. Значение «1» делает возможным считывание данных, на которые в текущий момент указывает READ RX ADDR из буфера считывания, а «0» блокирует(выключает) буфер считывания. Заметим, что расположения данных в ЗУПВ, соответствующие временным интервалам коммутационной платы, не используемым нагрузкой, подключенной к локальной шине TDM, не включают в себя значимые данные, и соответствующие биты таблицы приемника имеют значение «0».

Как ранее указывалось, фазовые соотношения между временными интервалами локальной шины TDM и шины TDM коммутационной платы должны быть такими, чтобы задержка от локальной шины TDM к шине (приемнику) TDM коммутационной платы плюс задержка от шины TDM к локальной шине (передатчику) TDM была бы точно равна длительности одного кадра или целому числу кадров. Кроме того, задержка (d) между шинами должна равняться целому числу временных интервалов. Это показано на Фиг.5 и выполнимо посредством осуществления управляемого ЗУПВ, описанного выше. TSd указывает фазовый сдвиг в количестве TS между локальной шиной и шиной коммутационной платы. Число m указывает задержку для произвольного временного интервала, переданного от локальной шины TDM на шину TDM коммутационной платы и обратно на локальную шину TDM снова.

Настоящее изобретение может преимущественно осуществляться в телекоммуникационных коммутаторах, таких как контроллеры базовых станций (BSC), контроллеры радиоузлов (RNC's) или любые другие коммутаторы сотовых сетей специального назначения или сетей обмена данными общего назначения. Изобретение может использоваться путем подключения печатных плат STM-1 к шине TDM, используя только одну нагрузку на печатную плату STM-1 вместо двух, так что полная нагрузка на шину может быть вдвое уменьшена.

Одно из главных преимуществ настоящего изобретения состоит в том, что нагрузка шины уменьшается, что приводит к меньшему ослаблению сигнала на шине TDM.

Дополнительно длины шлейфов могут быть сокращены, поскольку только один, вместо, например, двух приемопередатчиков, подключается к каждому разъему шины. Это означает улучшенные оконечные нагрузки и меньшее отражение и ослабление сигнала.

Кроме того, хотя вводится дополнительная буферная ступень из-за интеллектуального признака буфера, не вводятся никакие задержки комбинационных элементов, только синхронные задержки, которые являются кратными целому числу кадров.

Настоящее изобретение также предлагает упрощенную маршрутизацию печатной платы на основе упрощенных подключений и более коротких длин шлейфов.

Аббревиатуры

PCB - печатная плата;

RX - направление приема (от локальной шины TDM к шине TDM коммутационной платы);

ТХ - направление передачи (от шины TDM коммутационной платы к локальной шине TDM);

FPGA - вентильная матрица с эксплуатационным программированием;

ASIC - специализированная интегральная схема;

TDM - мультиплексирование с разделением времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОТЕЛЕФОННАЯ СИСТЕМА ДЛЯ ГРУПП УДАЛЕННЫХ АБОНЕНТОВ | 2004 |

|

RU2341038C2 |

| УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ И ДОСТУПА К КАНАЛУ ДЛЯ ЛОКАЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 1992 |

|

RU2060539C1 |

| УСТРОЙСТВО КОММУТАЦИИ, СОДЕРЖАЩЕЕ ШИНЫ ВРЕМЕННЫХ ИНТЕРВАЛОВ И НЕСКОЛЬКО БУФЕРОВ | 2002 |

|

RU2291479C2 |

| ПОВТОРНЫЙ ЗАХВАТ СИГНАЛОВ СЕТИ БЕСПРОВОДНОГО ВЕЩАНИЯ | 2006 |

|

RU2390951C2 |

| СИНХРОНИЗАЦИЯ ХРОНИРОВАНИЯ И ОЦЕНКА КАНАЛА ПРИ ПЕРЕХОДЕ МЕЖДУ ЛОКАЛЬНЫМИ И ГЛОБАЛЬНЫМИ ФОРМАМИ СИГНАЛА С ИСПОЛЬЗОВАНИЕМ НАЗНАЧЕННОГО ПИЛОТ-СИГНАЛА TDM | 2006 |

|

RU2379847C2 |

| ДЕТЕРМИНИРОВАННАЯ КОММУНИКАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2423007C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ СЕТЕВЫХ ИДЕНТИФИКАТОРОВ В СИСТЕМЕ СВЯЗИ | 2007 |

|

RU2407231C1 |

| БЕСКАБЕЛЬНАЯ ЛОКАЛЬНАЯ СЕТЬ | 1994 |

|

RU2107396C1 |

| СПОСОБЫ И УСТРОЙСТВА ДЛЯ УМЕНЬШЕНИЯ КОНФЛИКТОВ В СЕТЯХ РАДИОСВЯЗИ | 2014 |

|

RU2598035C1 |

| СИСТЕМА И СПОСОБ ПОДДЕРЖАНИЯ ВРЕМЕННОЙ СИНХРОНИЗАЦИИ В СЕТИ ЦИФРОВОГО ВИДЕО | 1998 |

|

RU2222116C2 |

Изобретение относится к буферизации между схемами синхронизации, осуществляющими связь посредством глобальной синхронной шины, в частности к уменьшению нагрузки шины в системе мультиплексированной шины с разделением во времени (TDM). Технический результат - уменьшение степени ухудшения сигнала и величины битовых ошибок. Для этого введена локальная шина данных TDM и активный буфер, включающий в себя контролируемую центральным процессором логическую схему, между нагрузками приемопередатчика и шиной TDM. Активные буферы в направлении приемника и передатчика вместе обеспечивают временную задержку для данных, выходящих с первой локальной шины TDM на шину TDM коммутационной платы и обратно на вторую локальную шину TDM с точной длительностью одного кадра TDM или целого числа кадров TDM. 12 з.п. ф-лы, 5 ил.

локальную шину данных TDM в каждой печатной плате, к которой подключается соответствующее число нагрузок,

логическую схему, управляемую центральным процессором, в каждом направлении подключающую локальную шину данных TDM к глобальной шине данных TDM, причем эта логическая схема включает в себя запоминающее устройство с произвольной выборкой (ЗУПВ), работающее по принципу FIFO (первым пришел, первым обслужен), посредством которого синхронные данные с локальной или глобальной шины данных TDM записываются на локальную или глобальную шину данных TDM и считываются с нее, вводя разность фаз, обеспечивающую полную задержку для любых данных, передаваемых от локальной шины данных TDM к глобальной шине данных TDM и обратно на локальную шину данных TDM, которая является регулируемой и принимающей целое значение, равное количеству кадров данных.

| ЕР 0388574 А, 26.09.1990 | |||

| РАСШИРЯЕМАЯ ТЕЛЕКОММУНИКАЦИОННАЯ СИСТЕМА | 1995 |

|

RU2154346C2 |

| МНОГОРЕЖИМНОЕ УСТРОЙСТВО РАДИОСВЯЗИ И МНОГОРЕЖИМНЫЙ СОТОВЫЙ РАДИОТЕЛЕФОН | 1993 |

|

RU2128886C1 |

| US 5758131 А, 26.05.1998 | |||

| US 4788660 А, 29.11.1988 | |||

| US 6249834 В1, 19.06.2001 | |||

| US 6119190 А, 19.09.2000 | |||

| US 5216637 А, 01.06.1993 | |||

| US 5946327 А, 31.08.1999 | |||

| US 6362974 В1, 26.03.2002. | |||

Авторы

Даты

2007-03-10—Публикация

2002-12-27—Подача