Область техники, к которой относится изобретение

Настоящее изобретение относится к принтерам и к запоминающим устройствам для принтеров. Более конкретно, изобретение относится к надежной битовой схеме для запоминающего устройства сменного компонента принтера.

Предшествующий уровень техники

Область техники струйной технологии сравнительно хорошо развита. Коммерческие продукты, такие как компьютерные принтеры, графические плоттеры и факсимильные машины реализованы с помощью струйной технологии для создания отпечатанных носителей. Обычно струйное изображение формируется согласно точному размещению на печатном носителе капель чернил, испускаемых устройством генерирования капель чернил, известным как устройство струйной печатающей головки. Устройство струйной печатающей головки включает в себя, по меньшей мере, одну печатающую головку. Обычно устройство струйной печатающей головки поддерживается на подвижной каретке, которая перемещается в поперечном направлении над поверхностью печатного носителя и управляется так, чтобы испускать капли чернил в соответствующие моменты времени, согласно команде микрокомпьютера или другого контроллера, в котором синхронизация применения капель чернил предназначена для того, чтобы соответствовать шаблону пикселей печатаемого изображения.

Струйные принтеры имеют, по меньшей мере, одно устройство подачи чернил. Устройство подачи чернил включает в себя контейнер чернил, имеющий резервуар чернил. Устройство подачи чернил может быть размещено вместе с устройством струйной печатающей головки в струйном чернильном картридже или пере или может быть размещено отдельно. Когда устройство подачи чернил размещено отдельно от устройства струйной печатающей головки, пользователи могут заменять устройство подачи чернил без замены устройства струйной печатающей головки. Тогда устройство струйной печатающей головки заменяют в конце или близко к концу срока службы печатающей головки, а не когда заменяют устройство подачи чернил.

Современные системы принтеров обычно включают в себя один или более сменных компонентов принтеров, включая струйные чернильные картриджи, устройства струйных печатающих головок и устройства подачи чернил. В некоторых существующих системах эти сменные компоненты принтеров оснащены встроенным запоминающим устройством для того, чтобы передавать информацию в принтер о сменном компоненте. Встроенное запоминающее устройство, например, для струйного чернильного картриджа, может хранить информацию, такую как тип пера, уникальный код пера, уровень наполнения чернил, маркетинговая информация, а также другая информация. Такое запоминающее устройство также может хранить другую информацию о контейнере чернил, такую как информация о текущем уровне чернил. Информация об уровне чернил может передаваться в принтер для индикации количества остающихся чернил. Пользователь может следить за информацией об уровне чернил и предвидеть необходимость замены опустошенного контейнера чернил.

Если данные, принятые принтером из запоминающего устройства компонента принтера, содержат ошибку, принтер может выполнить неправильное действие или может оказаться неспособным использовать компонент принтера. Такая ошибка может быть результатом короткого замыкания или обрыва в адресной линии, соединяющей запоминающее устройство с другими компонентами принтера, такими как контроллер принтера, или из-за некоторой другой проблемы.

Желательно иметь схему запоминающего устройства, которая является более надежной, чем современные схемы запоминающих устройств, используемые в сменных компонентах принтеров для того, чтобы обнаруживать и исправлять ошибки и обеспечить бесперебойную работу.

Сущность изобретения

Настоящее изобретение предоставляет способ, предназначенный для обнаружения ошибки в данных, принятых из запоминающего устройства сменного компонента принтера. Запоминающее устройство включает в себя множество битов. Способ включает в себя обеспечение первого бита контроля четности, ассоциированного с первым элементом данных. Первый элемент данных и первый бит контроля четности хранятся в запоминающем устройстве принтера. Принтер включает в себя множество электропроводящих линий. По меньшей мере, одна из электропроводящих линий ассоциирована с каждым битом. Первый элемент данных и первый бит контроля четности считывают из запоминающего устройства. Выполняют электрический тест, по меньшей мере, одной из электропроводящих линий. Ошибку в первом элементе данных идентифицируют на основе первого бита контроля четности, считанного из запоминающего устройства, и электрического теста.

Один аспект изобретения направлен на печатающую систему, включающую в себя струйную печатающую головку для выборочного осаждения капель чернил на поверхности носителя. Устройство подачи чернил хранит чернила, подаваемые в струйную печатающую головку. Запоминающее устройство хранит первый бит контроля четности и первый элемент данных. Первый бит контроля четности ассоциирован с первым элементом данных. Процессор соединен с запоминающим устройством с помощью множества электропроводящих линий. Процессор реагирует на выходной сигнал запоминающего устройства. Процессор выполняет электрический тест, по меньшей мере, одной из электропроводящих линий. Процессор идентифицирует ошибку в первом элементе данных на основе первого бита контроля четности и электрического теста.

Другой аспект изобретения направлен на струйный чернильный картридж для струйной печатающей системы, имеющей контроллер. Струйный чернильный картридж включает в себя устройство струйной печатающей головки, имеющее, по меньшей мере, одну струйную печатающую головку, которая выборочно осаждает капли чернил на печатном носителе. Устройство подачи чернил хранит чернила, подаваемые в струйную печатающую головку. Информационное запоминающее устройство хранит первый бит контроля четности и первый элемент данных. Первый бит контроля четности ассоциирован с первым элементом данных. Первый бит контроля четности используется контроллером совместно с электрическим тестом электропроводящих линий, соединенных с информационным запоминающим устройством, для идентификации ошибки в первом элементе данных.

Другой аспект изобретения направлен на запоминающее устройство для сменного компонента струйного принтера печатающей системы. Запоминающее устройство включает в себя полупроводниковый кристалл. На полупроводниковом кристалле сформировано множество схем. Каждая схема ассоциирована с состоянием бита в запоминающем устройстве и определяет состояние бита. Запоминающее устройство хранит первый элемент данных, который обеспечивает информацию идентификации относительно сменного компонента струйного принтера. Первый элемент данных используется печатающей системой для определения того, является ли сменный компонент струйного принтера подходящим для использования в печатающей системе. Схемы, ассоциированные с первым элементом данных, расположены, по существу, около центра полупроводникового кристалла.

Перечень чертежей

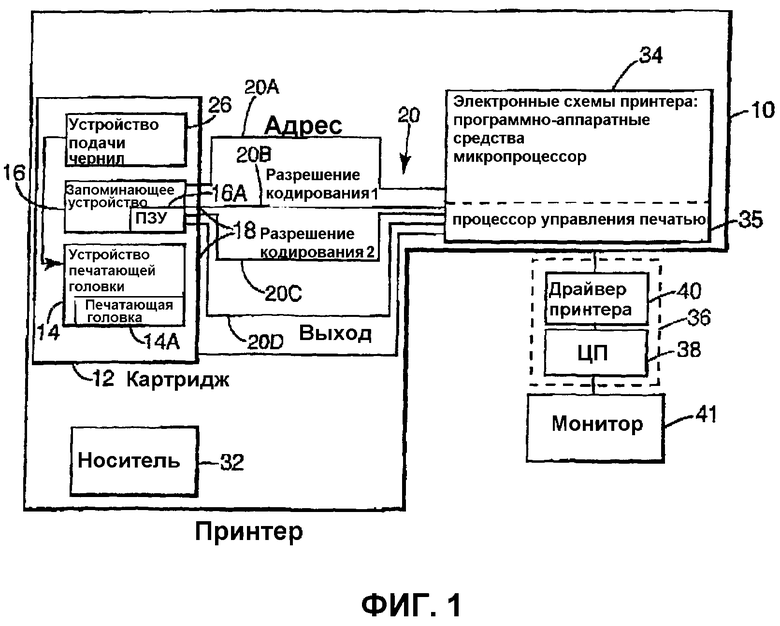

Фиг.1 - электрическая блок-схема основных компонентов струйного принтера в соответствии с настоящим изобретением.

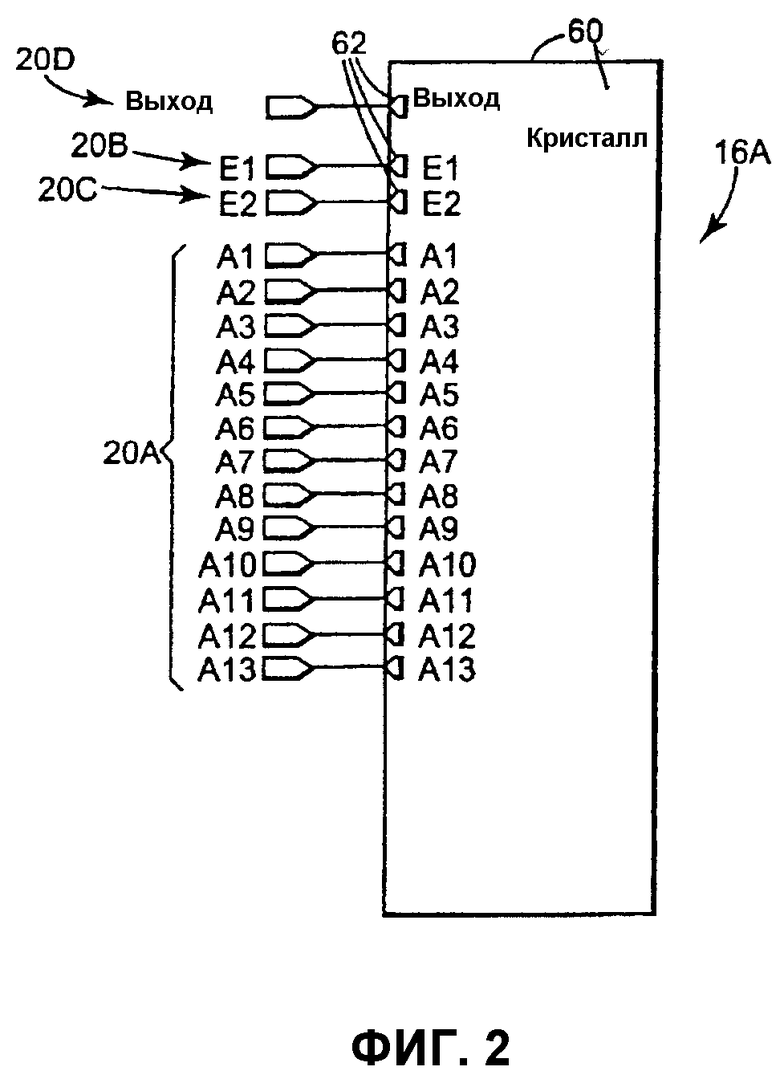

Фиг.2 - схема, иллюстрирующая ПЗУ (ROM) принтера, изображенного на фиг.1.

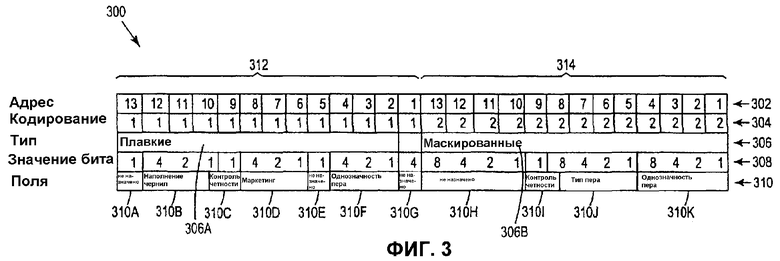

Фиг.3 - таблица, иллюстрирующая информацию, хранящуюся в запоминающем устройстве струйного чернильного картриджа в соответствии с настоящим изобретением.

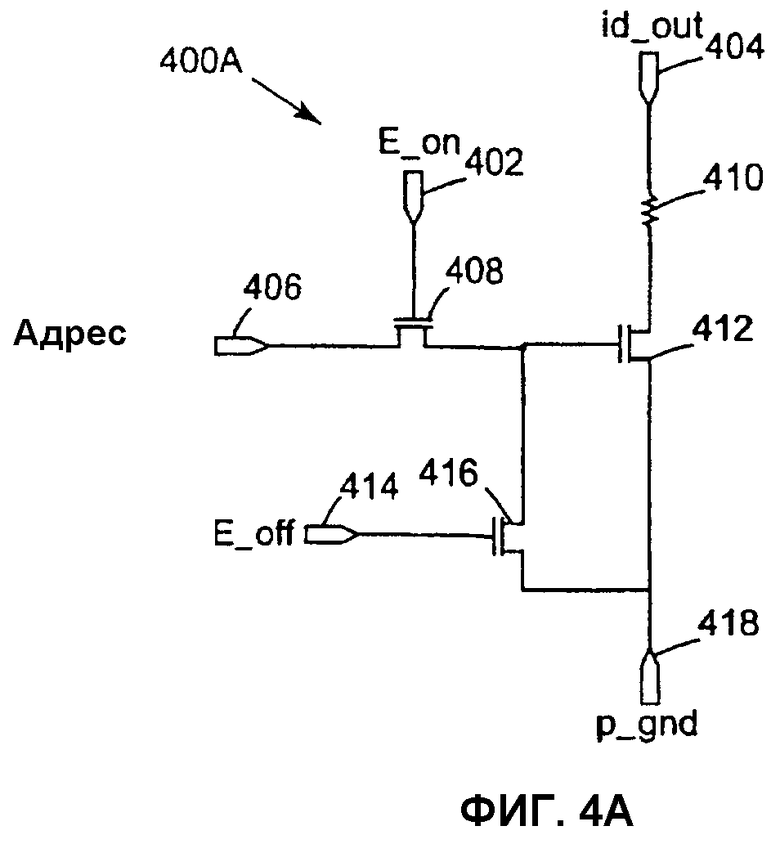

Фиг.4А - иллюстрация схемы для определения состояния плавкого бита запоминающего устройства струйного чернильного картриджа настоящего изобретения.

Фиг.4В - иллюстрация схемы для определения состояния маскированного бита запоминающего устройства струйного картриджа настоящего изобретения.

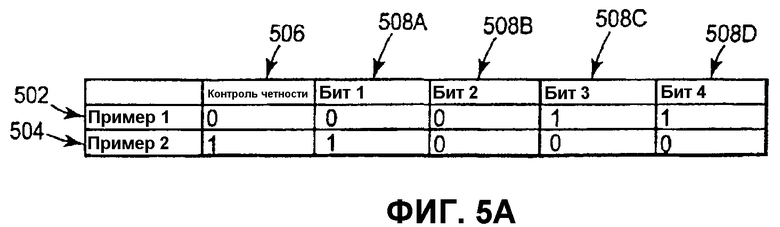

Фиг.5А - таблица, иллюстрирующая два примера назначений битов в запоминающем устройстве струйного чернильного картриджа в соответствии с настоящим изобретением.

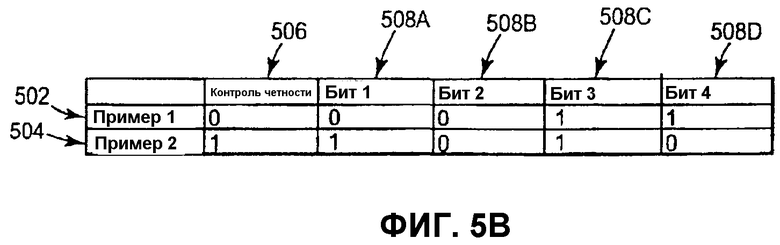

Фиг.5В - таблица, иллюстрирующая назначения битов по фиг.5А после того, как произошла ошибка.

Описание предпочтительных вариантов осуществления

В следующем подробном описании предпочтительных вариантов осуществления сделана ссылка на сопровождающие чертежи, которые образуют часть описания, и на которых в качестве иллюстрации изображены конкретные варианты осуществления, в которых может быть применено настоящее изобретение. Следует понимать, что могут быть использованы другие варианты осуществления и могут быть сделаны конструктивные и логические изменения, не выходя за рамки объема настоящего изобретения. Таким образом, следующее подробное описание не следует воспринимать в ограничивающем смысле, и объем настоящего изобретения определен прилагаемой формулой изобретения.

Фиг.1 - электрическая блок-схема основных компонентов струйного принтера в соответствии с настоящим изобретением. Струйный принтер 10 включает в себя сменный струйный чернильный картридж 12, который включает в себя устройство 14 струйной печатающей головки, интегрально установленное запоминающее устройство 16 и устройство 26 подачи чернил. Струйный чернильный картридж 12 является съемным из принтера 10 с подключением через межсоединения 18. Устройство 14 струйной печатающей головки включает в себя, по меньшей мере, одну печатающую головку 14А. Запоминающее устройство 16 может включать в себя множество видов запоминающих устройств, включая ОЗУ (RAM), ПЗУ и электрически стираемое программируемое ПЗУ (EEPROM), и хранит данные, ассоциированные с устройством 14 струйной печатающей головки и устройством 26 подачи чернил. В одном варианте осуществления запоминающее устройство 16 включает в себя записанные при изготовлении данные и записанные принтером данные. В одном варианте осуществления запоминающее устройство 16 включает в себя 26-битовое ПЗУ 16А, имеющее 13 плавких битов и 13 маскированных битов. В альтернативном варианте осуществления все 26 битов являются плавкими битами. В другом варианте настоящего изобретения все 26 битов являются маскированными битами. ПЗУ 16А также может включать в себя различное суммарное число битов, отличное от 26 битов. Преимущество использования как плавких, так и маскированных битов заключается в том, что может быть уменьшен размер запоминающего устройства ПЗУ 16А. Каждый плавкий бит может быть установлен с помощью пережигания резистора в схеме 400А (изображенной на фиг.4А), представляющей плавкий бит. Каждый маскированный бит может быть установлен с помощью добавления резистора в схеме 400В (изображенной на фиг.4В). В одном варианте осуществления ПЗУ 16А объединено с устройством 14 струйной печатающей головки. В альтернативном варианте осуществления ПЗУ 16А может быть объединено с устройством 26 подачи чернил. Специалистам в данной области техники будет понятно, что вместо встраивания устройства 14 струйной печатающей головки и устройства 26 подачи чернил в состав струйного чернильного картриджа 12, устройство 14 струйной печатающей головки и устройство 26 подачи чернил могут быть размещены отдельно и могут включать в себя отдельные запоминающие устройства.

Принтер включает в себя линии 20 связи для связи между струйным чернильным картриджем 12 и контроллером 34. Более конкретно, линии 20 связи включают в себя адресные линии 20А, первую линию 20В разрешения кодирования, вторую линию 20С разрешения кодирования и выходную линию 20D, все из которых соединены с ПЗУ 16А. В одном варианте осуществления адресные линии 20 включают в себя 13 адресных линий. Первая линия 20В разрешения кодирования используется для того, чтобы выбирать плавкие биты в ПЗУ 16А, а вторая линия 20В разрешения кодирования используется для того, чтобы выбирать маскированные биты в ПЗУ 16А. Адресные линии 20А используются для того, чтобы выбирать конкретный плавкий бит или маскированный бит. Значение выбранного плавкого или маскированного бита считывается с помощью считывания выходного сигнала выходной линии 20D.

Устройство 14 струйной печатающей головки, запоминающее устройство 16 и устройство 26 подачи чернил соединены с контроллером 34, который включает в себя как электронные схемы, так и программно-аппаратные средства для управления различными компонентами принтера или отдельными узлами. Процедура 35 управления печатью, которая может быть встроена в драйвер принтера, вызывает считывание данных из запоминающего устройства 16 и регулирует работу принтера в соответствии с данными, выбранными из запоминающего устройства 16. Контроллер 34 управляет устройством 14 струйной печатающей головки и устройством 26 подачи чернил таким образом, чтобы выброс капель чернил выполнялся управляемым образом на печатный носитель 32.

Главный процессор 36 соединен с контроллером 34 и включает в себя центральный процессор (ЦП, CPU) 38 и программный драйвер 40 принтера. Монитор 41 соединен с главным процессором 36 и используется для того, чтобы отображать различные сообщения, которые служат индикаторами состояния струйного принтера 10. Альтернативно принтер 10 может быть сконфигурирован для автономной или сетевой работы, при которой сообщения отображаются на передней панели принтера.

На фиг.2 представлена схема, иллюстрирующая ПЗУ 16А по фиг.1 более подробно. ПЗУ 16А включает в себя полупроводниковый кристалл 60, имеющий множество контактных площадок 62. Адресные линии 20А, первая линия (Е1) 20В разрешения кодирования, вторая линия (Е2) 20С разрешения кодирования и выходная линия 20D соединены с полупроводниковым кристаллом 60 через контактные площадки 62. Адресные линии 20А включают в себя 13 адресных линий (А1-А13). В одном варианте осуществления ПЗУ 16А включает в себя другие электрические соединения (не изображены), включая соединения заземления.

На фиг.3 представлена таблица, иллюстрирующая информацию, хранящуюся в ПЗУ 16А в соответствии с настоящим изобретением. Таблица 300 включает в себя идентификаторы 302 адресных линий, идентификаторы 304 линий разрешения кодирования, идентификаторы 306А и 306В типов битов (совместно упоминаемые как идентификаторы 306 типов битов), значения 308 битов и поля 310. Таблица 300 разделена на часть 312 и часть 314. Часть 312 таблицы 300 представляет информацию, ассоциированную с плавкими битами, как указано с помощью идентификатора 306А типа «плавкий». Часть 314 таблицы 300 представляет информацию, ассоциированную с маскированными битами, как указано с помощью идентификатора 306В типа «маскированный». Как упомянуто выше, вместо того, чтобы использовать как плавкие, так и маскированные биты, все биты в ПЗУ 16А могут быть плавкими битами или все биты в ПЗУ 16А могут быть маскированными битами. Каждый из идентификаторов 302 адресных линий представляет одну из адресных линий и соответствует либо плавкому, либо маскированному биту. Как плавкие, так и маскированные биты пронумерованы 1-13, указывая конкретную адресную линию 20А, ассоциированную с битом. Идентификаторы 304 линий разрешения кодирования указывают линию 20В или 20С разрешения кодирования, которая должна быть установлена для того, чтобы выбрать соответствующий бит. «1» в идентификаторах 304 линий разрешения кодирования соответствует первой линии 20 В разрешения кодирования, которая используется для того, чтобы выбирать плавкие биты. «2» в идентификаторах 304 линий разрешения кодирования соответствует второй линии 20С разрешения кодирования, которая используется для того, чтобы выбирать маскированные биты.

Плавкие биты 1-13 и маскированные биты 1-13 разделены на множество полей 310. Каждый бит в конкретном поле 310 включает в себя значение 308 бита. Когда бит установлен, он имеет значение, указанное в соответствующем ему значении 308 бита. Когда бит не установлен, он имеет значение 0. В одном варианте осуществления плавкие биты 1-13 и маскированные биты 1-13 устанавливаются во время изготовления ПЗУ 16А.

Поле 310А включает в себя плавкий бит 13. В одном варианте осуществления плавкий бит 13 не используется для хранения данных, таким образом, поле 310А включает в себя буквы "NA" (т.е. не назначено).

Поле 310В наполнения чернил включает в себя плавкие биты 10-12. В одном варианте осуществления плавкие биты 10-12 обеспечивают эталонный уровень или уровень запуска для того, чтобы определить, когда должно быть отображено предупреждение о малом количестве чернил.

Поле 310С контроля четности включает в себя плавкий бит 9. В одном варианте осуществления плавкий бит 9 является битом контроля четности, используемым в связи с битами, соответствующими полю 310D маркетинга. В альтернативном варианте осуществления плавкий бит 9 является битом контроля четности, используемым в связи с множеством битов полей 310. Плавкий бит 9 также может использоваться в связи с битами запоминающего устройства, ассоциированными с другим компонентом принтера, таким как устройство 26 подачи чернил.

Поле 310D маркетинга включает в себя плавкие биты 6-8. В одном варианте осуществления плавкие биты 6-8 используются для идентификации того, может ли быть использован струйный картридж в конкретном принтере.

Поле 310Е включает в себя плавкий бит 5. В одном варианте осуществления плавкий бит 5 не используется для хранения данных, таким образом, поле 310Е включает в себя буквы "NA" (т.е. не назначено).

Поле 310F однозначности пера включает в себя плавкие биты 2-4. В одном варианте осуществления плавкие биты 2-4 представляют случайное число, которое однозначно идентифицирует струйный чернильный картридж, что позволяет контроллеру 34 принтера определять, когда установлен новый струйный картридж.

Поле 310G включает в себя плавкий бит 1. В одном варианте осуществления плавкий бит 1 не используется для хранения данных, таким образом, поле 310G включает в себя буквы "NA" (т.е. не назначено).

Поле 310Н включает в себя маскированные биты 10-13. В одном варианте осуществления маскированные биты 10-13 не используются для хранения данных, таким образом, поле 310Н включает в себя буквы "NA" (т.е. не назначено).

Поле 310I включает в себя маскированный бит 9. В одном варианте осуществления маскированный бит 9 является битом контроля четности, используемым в связи с битом, соответствующим полю 310J типа пера. В альтернативном варианте осуществления маскированный бит 9 является битом контроля четности, используемым в связи с множеством битов полей 310. Маскированный бит 9 также может использоваться в связи с битами запоминающего устройства, ассоциированными с другим компонентом принтера, таким как устройство 26 подачи чернил.

Поле 310J типа пера включает в себя маскированные биты 5-8. В одном варианте осуществления маскированные биты 5-8 обеспечивают идентификацию типа струйного чернильного картриджа, который ассоциирован с запоминающим устройством.

Поле 310К однозначности пера включает в себя маскированные биты 1-4. В одном варианте осуществления маскированные биты 1-4 представляют случайное число, которое однозначно идентифицирует конкретный струйный чернильный картридж, что позволяет контроллеру 34 принтера определять, когда установлен новый струйный чернильный картридж.

На Фиг.4А изображена иллюстрация схемы для определения состояния плавкого бита в ПЗУ 16А. Схема 400А включает в себя первый вход (Е_on) 402 разрешения кодирования, выход (id_out) 404, адресный вход 406, транзистор 408, резистор 410, транзистор 412, второй вход (Е_off) 414 разрешения кодирования, транзистор 416 и контакт заземления (p_gnd) 418. Адресный вход 406 соединен с одной из адресных линий 20А (см. фиг.1). Первый вход (Е_on) 402 разрешения кодирования соединен с первой линией 20 В разрешения кодирования (изображенной на фиг.1). Второй вход (Е_off) 414 разрешения кодирования соединен со второй линией 20С разрешения кодирования (см. фиг.1). Выход 404 соединен с выходной линией 20D (см. фиг.1).

В одном варианте осуществления каждый из транзисторов 408, 412 и 416 является полевым транзистором (ПТ, FET). Адресный вход 406 соединен со стоком транзистора 408. Первый вход 402 разрешения кодирования соединен с затвором транзистора 408. Исток транзистора 408 соединен с затвором транзистора 412 и стоком транзистора 416. Затвор транзистора 416 соединен со вторым входом 414 разрешения кодирования. Сток транзистора 416 соединен с истоком транзистора 408 и затвором транзистора 412. Исток транзистора 416 соединен с контактом заземления 418. Резистор 410 расположен между выходом 404 и стоком транзистора 412. Исток транзистора 412 соединен с землей 418.

Плавкий бит в ПЗУ 16А, такой как бит, представленный схемой 400А, считывается с помощью установки высокого уровня на первом входе 402 разрешения кодирования, установки высокого уровня на адресном входе 406 и считывания сигнала на выходе 404. Высокий уровень на первом входе 402 разрешения кодирования устанавливается контроллером 34 с помощью установки высокого уровня на первой линии 20В разрешения кодирования. Высокий уровень на адресной линии 406 устанавливается контроллером 34 с помощью установки высокого уровня на адресной линии 20А, соединенной с адресным входом 406. Выходное напряжение на выходе 404 считывается контроллером 34 с помощью считывания напряжения на выходной линии 20D.

Транзистор 408 действует как логический элемент И (AND) с входами 402 и 406. Если на обоих входах 402 и 406 высокий уровень, то ток течет через транзистор 408, открывая транзистор 412. Транзистор 412 действует как управляющий транзистор, управляя выходом 404. Если резистор 410 пережжен, то напряжение на выходе 404 будет высоким, указывая логическую 1. Если резистор 410 не пережжен, то напряжение на выходе 404 будет низким, указывая логический 0. Транзистор 416 используется как активная развязка, чтобы препятствовать отпиранию транзистора 412 током утечки из транзистора 408, когда транзистор 412 должен быть заперт. Транзистор 416 отпирается с помощью установки высокого уровня на втором входе 414 разрешения кодирования. При отпирании транзистор 416 отводит ток от транзистора 408 на землю.

В одном варианте осуществления каждый транзистор 408 и 416 имеет длину около 4 микрон, а ширину около 15,5 микрон, а транзистор 412 имеет длину около 4 микрон, а ширину около 600 микрон. В одном варианте осуществления резистор 410 имеет сопротивление выше приблизительно 1000 Ом, когда пережжен, и сопротивление ниже приблизительно 400 Ом, когда не пережжен. Кроме пережигания резистора 410 другие способы могут использоваться для того, чтобы создать разомкнутую цепь для определения состояния бита в ПЗУ 16А, включая механическое отрезание, лазерное отрезание, а также другие способы.

На фиг.4В представлена иллюстрация схемы для определения состояния маскированного бита в ПЗУ 16А. Схема 400В, по существу, является такой же, как схема 400А, изображенная на фиг.4А, за исключением того, что резистор 410 заменен переключателем 420, а транзистор 422 включает в себя другие характеристики по сравнению с транзистором 412. В одном варианте осуществления переключатель 420 не является фактическим физическим переключателем, а представляет либо присутствие, либо отсутствие резистора. Если резистор присутствует на месте переключателя 420, то резистор имеет достаточное сопротивление, чтобы действовать как разомкнутая цепь между выходом 404 и транзистором 422. Если резистор не присутствует на месте переключателя 420, то не имеется дополнительного сопротивления между выходом 404 и транзистором 422. В одном варианте осуществления транзистор 422 является полевым транзистором (ПТ) с длиной около 4 микрон и шириной около 100 микрон.

Адресный вход 406 соединен с одной из адресных линий 20А (см. фиг.1). Первый вход 402 разрешения кодирования соединен со второй линией 20С разрешения кодирования (см. фиг.1). Второй вход 414 разрешения кодирования соединен с первой линией 20 В разрешения кодирования (см. фиг.1). Выход 404 соединен с выходной линией 20D (см. фиг.1).

Адресный вход 406 соединен со стоком транзистора 408. Первый вход 402 разрешения кодирования соединен с затвором транзистора 408. Исток транзистора 408 соединен с затвором транзистора 422 и стоком транзистора 416. Затвор транзистора 416 соединен со вторым входом 414 разрешения кодирования. Сток транзистора 416 соединен с истоком транзистора 408 и затвором транзистора 422. Исток транзистора 416 соединен с контактом заземления 418. Переключатель 420 расположен между выходом 404 и стоком транзистора 422. Исток транзистора 422 соединен с контактом заземления 418.

Маскированный бит в ПЗУ 16А, такой как бит, представленный схемой 400В, считывается с помощью установки высокого уровня на первом входе 402 разрешения кодирования, установки высокого уровня на адресном входе 406 и считывания сигнала на выходе 404. Высокий уровень на первом входе 402 разрешения кодирования устанавливается контроллером 34 с помощью установки высокого уровня на второй линии 20С разрешения кодирования. Высокий уровень на адресном входе 406 устанавливается контроллером 34 с помощью установки высокого уровня на адресной линии 20А, соединенной с адресным входом 406. Выходное напряжение на выходе 404 считывается контроллером 34 с помощью считывания напряжения на выходной линии 20D.

Транзистор 408 действует как логический элемент И с входами 402 и 406. Если на обоих входах 402 и 406 высокий уровень, то ток течет через транзистор 408, открывая транзистор 422. Транзистор 422 действует как управляющий транзистор, управляя выходом 404. Если переключатель 420 разомкнут (т.е. резистор присутствует), то напряжение на выходе 404 будет высоким, указывая логическую 1. Если переключатель 420 замкнут (т.е. резистор не присутствует), то напряжение на выходе 404 будет низким, указывая логический 0. Транзистор 416 используется как активная развязка, чтобы препятствовать отпиранию транзистора 422 током утечки из транзистора 408, когда транзистор 422 должен быть заперт. Транзистор 416 отпирается с помощью установки высокого уровня на втором входе 414 разрешения кодирования. При отпирании транзистор 416 отводит ток от транзистора 408 на землю.

В ПЗУ 16А настоящего изобретения плавкие и маскированные биты могут быть дополнительно классифицированы либо как функциональные, либо как информационные. Поля функциональных битов должны соответствовать величинам, ожидаемым принтером для правильной работы. Примером поля функциональных битов является поле 310J типа пера. Если биты, соответствующие полю 310J типа пера, указывают тип струйного чернильного картриджа, который не совместим с принтером, то принтер может отключить струйный чернильный картридж. Таким образом, ошибка в поле 310J типа пера могла бы заставить принтер ошибочно отключить струйный чернильный картридж. Поля информационных битов не являются критичными для правильной работы и могут быть игнорированы, или может быть предпринято действие на основании неправильной информации в поле информационных битов, не вызывая прекращение работы. Примеры полей информационных битов включают в себя поля 310F и 310К однозначности пера.

Короткие замыкания, вызванные случайно попавшими чернилами ("чернильные короткие замыкания") в ПЗУ 16А струйного картриджа, обычно происходят более часто на краях полупроводникового кристалла 60 (изображенного на фиг.2). Контактные площадки 62, которые расположены около краев полупроводникового кристалла 60, имеют тенденцию претерпевать коррозию, потенциально вызывая электрические отказы. В одном варианте осуществления функциональные биты и другие значимые биты, такие как биты контроля четности, расположены к центру полупроводникового кристалла 60, чтобы уменьшить вероятность чернильных коротких замыканий относительно этих битов и, таким образом, обеспечить более надежное ПЗУ 16А. В одном варианте осуществления биты 310D маркетинга, биты 310J типа пера и биты 310С контроля четности расположены, по существу, около центра полупроводникового кристалла 60.

В одном варианте осуществления для того, чтобы дополнительно повысить надежность ПЗУ 16А струйного чернильного картриджа, в соответствии с настоящим изобретением биты контроля четности назначены полям значимых битов, включая поля функциональных битов. Как изображено на фиг.3, бит 310С контроля четности назначен полю 310D битов маркетинга, а бит 310I контроля четности назначен полю 310J битов типа пера. Использование битов контроля четности, таких как биты 310С и 310I контроля четности, для повышения надежности ПЗУ струйного чернильного картриджа, обсуждено более подробно ниже со ссылкой на фиг.5А и фиг.5В.

На фиг.5А представлена таблица, иллюстрирующая два примера назначения битов в ПЗУ струйного чернильного картриджа в соответствии с настоящим изобретением. Таблица включает в себя строки 502 и 504 и столбцы 506 и 508А-D. Столбец 506 включает в себя значение бита контроля четности для каждого примера, таких как биты 310С или 310I контроля четности. Столбцы 508А-D включают в себя значения битов в поле битов данных для каждого примера, таком как поле 310D маркетинга или поле 310J типа пера. В примере 1, изображенном в строке 502, бит контроля четности установлен в 0, бит 1 установлен в 0, бит 2 установлен в 0, бит 3 установлен в 1, и бит 4 установлен в 1. В примере 2, изображенном в строке 504, бит контроля четности установлен в 1, бит 1 установлен в 1, бит 2 установлен в 0, бит 3 установлен в 1, и бит 4 установлен в 0.

В одном варианте осуществления проверка на четность используется при определении того, какое значение назначить битам контроля четности. Поскольку биты 1-4 в примере 1 суммируются до четного числа, бит контроля четности для примера 1 устанавливается в 0, чтобы поддерживать четное число для суммы битов 1-4 и бита контроля четности. Поскольку биты 1-4 в примере 2 суммируются до нечетного числа, бит контроля четности для примера 2 устанавливается в 1, чтобы получить четное число для суммы битов 1-4 и бита контроля четности. В альтернативном варианте осуществления проверка на нечетность используется вместо проверки на четность.

На фиг.5В изображена таблица, иллюстрирующая назначения битов по фиг.5А после того, как произошла ошибка в полях битов данных. На фиг.5В предполагается, что произошло чернильное короткое замыкание в адресной линии 20А, соответствующей биту 3 данных. Контроллер 34 определяет, имеет ли какая-либо из адресных линий 20А короткое замыкание или обрыв, с помощью электрического тестирования каждой из адресных линий 20А. В одном варианте осуществления электрический тест включает в себя контроль непрерывности. Способы для тестирования электрических проводящих линий и электрических цепей известны специалистам в данной области техники. После электрического тестирования адресных линий 20А контроллер 34 определяет, что адресная линия 20А, соответствующая биту 3, имеет короткое замыкание. Когда в адресной линии происходит чернильное короткое замыкание, выходной сигнал, считанный контроллером 34, будет равен 1, независимо от того, был ли бит равен 1 перед чернильным коротким замыканием. Таким образом, бит 3 равен 1 как для примера 1, так и для примера 2 на фиг.5В, даже несмотря на то, что бит 3 в примере 2 должен быть равен 0, как изображено на фиг.5А.

В примере 1 контроллер 34 исследует бит контроля четности, чтобы определить, содержит ли поле битов данных ошибку. Поскольку сумма битов 1-4 и бита контроля четности является четным числом, контроллер 34 определяет, что поле битов данных не содержит ошибку.В примере 2 после исследования бита контроля четности для определения того, содержит ли поле битов данных ошибку, контроллер 34 определяет, что ошибка произошла, поскольку сумма битов 1-4 и бита контроля четности является нечетным числом, и используется проверка на четность. На основании электрического теста адресной линии, соответствующей биту 3, который указывает чернильное короткое замыкание, и определения из теста контроля четности, что ошибка произошла, контроллер 34 определяет, что бит 3 должен быть равен 0 и соответствующим образом корректирует этот бит. Таким образом, ошибка не вызывает прерывания работы принтера 10.

Несмотря на то, что специфические варианты осуществления проиллюстрированы и изложены в настоящем описании для целей описания предпочтительного варианта осуществления, специалисты в данной области техники поймут, что широкое множество альтернативных и/или эквивалентных реализаций может заменить изображенные и описанные специфические варианты осуществления, не выходя за рамки объема настоящего изобретения. Специалисты в области химии, механики, электромеханики, электрической и компьютерной техники легко поймут, что настоящее изобретение может быть реализовано в очень широком множестве вариантов осуществления. Подразумевается, что эта заявка охватывает любые адаптации или вариации предпочтительных вариантов осуществления, обсужденных в настоящем описании. Следовательно, явным образом предполагается, что это изобретение ограничено только формулой изобретения и ее эквивалентами.

Группа изобретений относится к принтерам и запоминающим устройствам для принтеров. Согласно предложенному способу для обнаружения ошибки в данных, принятых из запоминающего устройства сменного компонента принтера, обеспечивают первый бит контроля четности, ассоциированный с первым элементом данных. Первый элемент данных и первый бит контроля четности хранят в запоминающем устройстве. Принтер включает в себя множество электропроводящих линий. Запоминающее устройство включает в себя множество битов. По меньшей мере, одна из электропроводящих линий ассоциирована с каждым битом. Первый элемент данных и первый бит контроля четности считывают из запоминающего устройства. Выполняют электрический тест, по меньшей мере, одной из электропроводящих линий. Идентифицируют ошибку в первом элементе данных на основе первого бита контроля четности, считанного из запоминающего устройства, и электрического теста. Другие изобретения группы охватывают печатающую систему, два варианта исполнения сменного компонента принтера для печатающей системы и способ хранения информации в сменном компоненте принтера. Группа изобретений позволяет создать запоминающее устройство с повышенной надежностью. Своевременное обнаружение и исправление ошибок в сменных компонентах принтеров гарантирует их бесперебойную работу. 5 н. и 40 з.п. ф-лы, 7 ил.

| Устройство для разметки деталей | 1980 |

|

SU956963A1 |

| ЕР 1027986 A1, 16.08.2000 | |||

| ЕР 1078759 А2, 28.02.2001 | |||

| Струйная печатающая головка и способ ее изготовления | 1989 |

|

SU1635896A3 |

Авторы

Даты

2007-03-20—Публикация

2002-05-24—Подача