Предлагаемое изобретение относится к области электротехники, а именно к системам управления инверторами.

Транзисторные инверторы как однотактные, так и двухтактные нашли широкое применение в составе различных вторичных источников питания [1, 2, 3].

Системы управления транзисторными инверторами разработаны на уровне типовых микроконтроллеров [4].

Особой разновидностью двухтактных инверторов является так называемый полумостовой инвертор [4, 5], представляющий собой два последовательно соединенных транзистора и два последовательно соединенных конденсатора, общие точки которых представляют собой диагональ переменного тока, в которую включена нагрузка, а свободные концы объединены соответственно и подключены к источнику постоянного напряжения. Как и в мостовых инверторах, транзисторы шунтированы обратными диодами. Система управления полумостовым транзисторным инвертором, как уже упомянуто, типовая и приведена в [4] на стр.376, рис.33.12. Эта система применяется для управления любыми двухтактными инверторами и может отличаться лишь числом выходных каналов (для мостового - четыре канала, для полумостового - два канала).

Данная система управления полумостовым транзисторным инвертором является наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков и принимается за прототип.

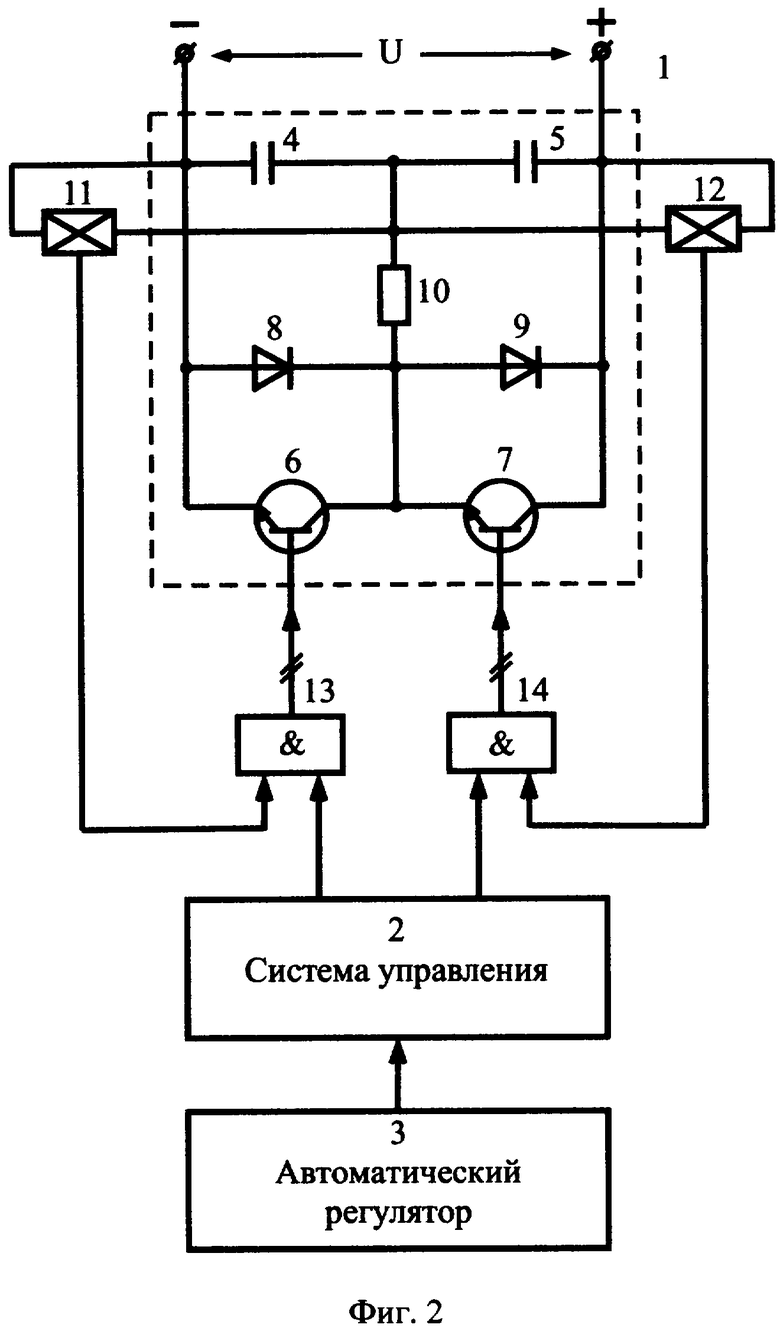

Система [4] представляет собой «классическую» систему широтно-импульсной модуляции (ШИМ) и, в совокупности с полумостовым транзисторным инвертором и автоматическим регулятором, приведена в упрощенном виде на фиг.1:

1 - полумостовой транзисторный инвертор;

2 - типовая система широтно-импульсной модуляции [4] (стр.376, рис.33.12);

3 - автоматический регулятор.

К причинам, препятствующим достижению указанного ниже технического результата при использовании как известных аналогов, так и прототипа, относится то, что в известном устройстве система управления генерирует на управляющие входы транзисторов инвертора импульсы, скважность которых определяет продолжительность включенного состояния транзисторов.

Однако в полумостовом инверторе необходимая продолжительность включенного состояния транзисторов уменьшается с ростом нагрузки. То есть необходимая продолжительность включенного состояния транзистора может быть значительно меньше, чем длительность отпирающих импульсов с выхода системы управления. Это приводит к неоправданным потерям в транзисторах.

Технический результат - уменьшение потерь в транзисторах полумостового инвертора.

Указанный технический результат при осуществлении изобретения достигается тем, что в систему управления полумостовым транзисторным инвертором по принципу широтно-импульсной модуляции, выходные каналы которой связаны с управляющими входами транзисторов полумостового инвертора, а вход подключен к выходу автоматического регулятора, дополнительно введены два логических двухвходовых элемента «И» и два датчика напряжения на конденсаторах полумостового транзисторного инвертора, причем выходы упомянутых датчиков напряжения и выходы упомянутой системы управления полумостовым транзисторным инвертором подключены соответственно к входам двухвходных логических элементов «И», а выходы упомянутых двухвходовых логических элементов «И» связаны с соответствующими управляющими входами транзисторов полумостового транзисторного инвертора. Это позволило автоматически согласовать длительность отпирающих импульсов на управляющих входах транзисторов полумостового транзисторного инвертора с необходимой длительностью включения упомянутых транзисторов и, таким образом, уменьшить потери в транзисторах.

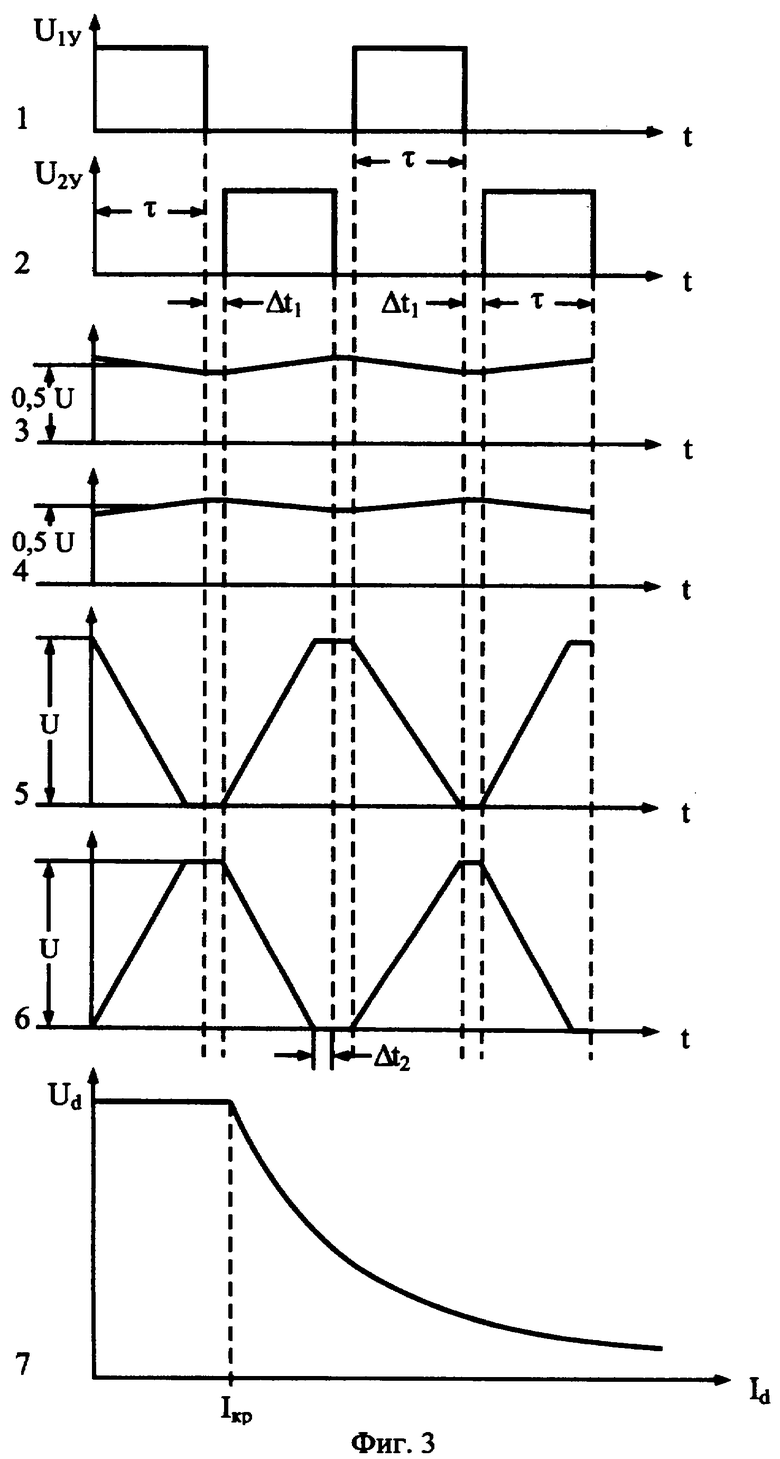

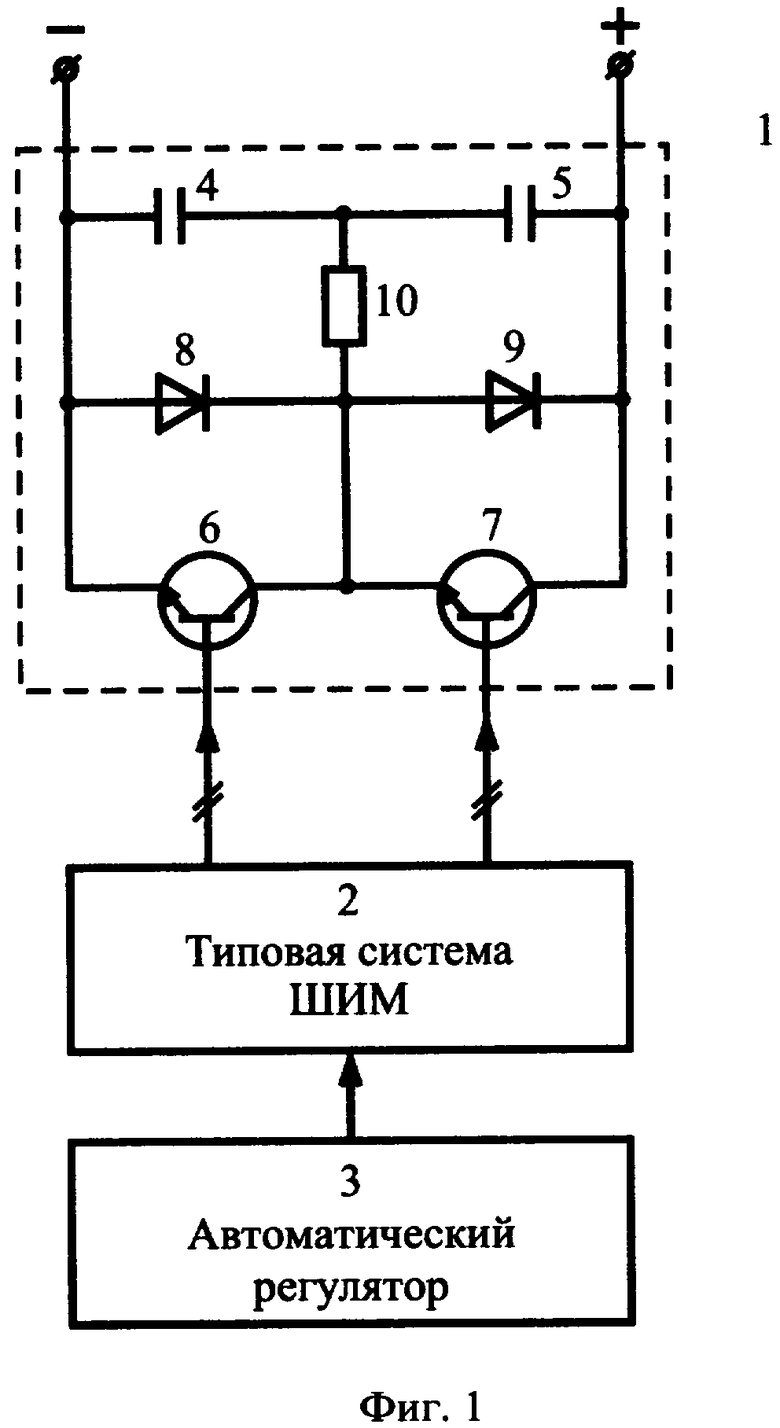

Сущность изобретения поясняется фиг.2, на которой представлена упрощенная схема устройства, и фиг.3, где даны диаграммы напряжений на конденсаторах и внешняя характеристика полумостового транзисторного инвертора.

Предлагаемая система управления полумостовым транзисторным инвертором (фиг.2) содержит полумостовой транзисторный инвертор 1, систему управления 2 и автоматический регулятор 3. В состав инвертора входят два конденсатора 4 и 5, соединенные между собой последовательно, два транзистора 6 и 7, также соединенные последовательно, и два обратных диода 8 и 9, шунтирующие в обратном направлении упомянутые транзисторы 6 и 7. Общие точки конденсаторов 4 и 5 и транзисторов 6 и 7 образуют диагональ переменного тока, в которую включена нагрузка 10.

Свободные концы конденсаторов 4, 5 и транзисторов 6, 7 объединены и соответственно подключены к источнику постоянного напряжения.

Таким образом, блок 1 представляет собой полумостовой транзисторный инвертор, идентичный известным аналогам и прототипу.

Как упомянуто выше, блок 2 содержит типовую систему управления транзисторным полумостовым инвертором, построенную по принципу широтно-импульсной модуляции и имеющую два выхода (по числу транзисторов инвертора). Подробная схема блока 2 приведена в [4] на стр.376, рис.33.12. К входу блока 2 подключен автоматический регулятор 3, также являющийся типовым узлом, обычно представляющим аналоговый компаратор. Дополнительными элементами схемы фиг.2 являются два датчика напряжения 11 и 12 и два логических двухвходовых элемента «И» 13 и 14. Датчик напряжения 11 включен входом параллельно конденсатору 4, а датчик напряжения 12 включен входом параллельно конденсатору 11.

Выход датчика 11 подключен к одному из входов логического двухвходового элемента «И» 13, а выход датчика напряжения 12 подключен к одному из входов логического двухвходового элемента 14. Свободные входы логических двухвходных элементов «И» 13 и 14 соединены с соответствующими выходами системы управления 2, а выходы логических двухвходных элементов «И» 13 и 14 подключены к соответствующим управляющим входам транзисторов 6 и 7. Для простоты промежуточные цепи гальванической развязки и формирования сигналов с датчиков 11, 12 на фиг.2 не показаны.

Устройство (фиг.2) функционирует следующим образом. При включении напряжения U конденсаторы 4, 5 заряжаются каждый до 0,5 U. Пусть из системы управления 2 поступил импульс напряжения U1y (диаграмма 1 на фиг.3) на вход логического двухвходного элемента «И» 13. На другом входе логического двухвходного элемента 13 также есть сигнал с датчика напряжения 11, поэтому с выхода логического двухвходного элемента «И» 13 поступит на вход транзистора 6 логическая единица и транзистор 6 включится.

Если ток нагрузки мал, то конденсатор 4 за время действия τ (фиг.3) отпирающего импульса U1y не успеет разрядиться, поэтому транзистор 6 будет отперт в течение времени τ.

После исчезновения отпирающего импульса из системы управления 2 в течение времени Δt1 (диаграмма 2 на фиг.3) импульс со второго входа системы управления 2 не поступает. Время Δt1 необходимо для восстановления запирающих свойств транзистора, а установка величины Δt1 предусмотрена в типовой системе управления 2. По истечении времени Δt1 поступает отпирающий импульс U2y из системы управления 2 на вход логического двухвходного элемента «И» 14. На втором входе логического двухвходного элемента «И» 14 сигнал с датчика напряжения 12 есть (диаграмма 4 на фиг.3) и на вход транзистора 7 поступает отпирающий импульс. В дальнейшем цикл повторяется.

Таким образом, при малых токах нагрузки время отпертого состояния транзисторов 6, 7 определяется только «шириной» τ (диаграмма 1, фиг.3) отпирающего импульса из системы управления 2.

Если ток нагрузки превысит некоторую критическую величину Iкр (см. внешнюю характеристику устройства на диаграмме 7, фиг.3), конденсаторы 4 и 5 будут успевать разряжаться полностью за полупериод работы инвертора.

Устройство в этом режиме обеспечивает постоянную мощность в нагрузке (Ud·Id=const). В схеме прототипа (фиг.1) транзисторы при любом токе нагрузки отперты в течение времени τ, поэтому после разряда соответствующего конденсатора, например 4, накопленная в индуктивности нагрузки 10 электромагнитная энергия разряжается по цепи: нагрузка 10 - транзистор 6, конденсатор 4. При этом затягивается время схода тока до нуля и создаются ненужные дополнительные потери в транзисторе, да и во всем контуре разряда конденсатора.

В предлагаемом устройстве (фиг.2) как только напряжение на конденсаторе, например, 4 достигает нуля, исчезнет «единица» на выходе логического двухвходного элемента «И» 13, транзистор 6 запрется, а накопленная в нагрузке 10 электромагнитная энергия будет разряжаться по контуру: нагрузка 10 - диод 9 - конденсатор 5 - нагрузка 10. Кроме того, ток разряда пойдет и через выходную емкость источника питания.

Потери в транзисторе 6 на этом интервале (Δt2 на диаграмме 6, фиг.3) исключаются, а запасенная в нагрузке электромагнитная энергия частично переходит в конденсатор 5, частично возвращается в источник питания. Очевидно, что эффективность предложенного устройства тем выше, чем больше ток нагрузки.

Например, при использовании инвертора для питания через понижающий трансформатор электрической дуги в сварочном аппарате работа устройства протекает либо при холостом ходе, либо при токах больше Iкр (фиг.3, диаграмма 7). В этом режиме Δt2>>Δt1 (фиг.3, диаграммы 2, 6) и предложенное устройство существенно уменьшает непроизводительные потери в транзисторах инвертора.

Технический результат достигнут весьма простыми средствами.

Источники информации

1. «Transpoket» - Австрия, каталог, 1995-1996.

2. «Al - Технотрон» - Россия, проспект фирмы, 1995.

3. «Invertec V-130-S-Linkoln» - США, каталог, 1998-1999.

4. В.А.Прянишников. «Электроника», С.-Петербург, 1988, 400 с.

5. Источники вторичного электропитания. Под ред. Ю.И.Конева. М.: Радио и связь, 1983.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУМОСТОВОЙ ТРАНЗИСТОРНЫЙ ИНВЕРТОР | 2007 |

|

RU2326484C1 |

| ОДНОФАЗНЫЙ ПОЛУМОСТОВОЙ ТИРИСТОРНЫЙ ИНВЕРТОР | 2005 |

|

RU2294591C1 |

| ПОЛУМОСТОВОЙ ТИРИСТОРНЫЙ ИНВЕРТОР | 2007 |

|

RU2321942C1 |

| ОДНОФАЗНЫЙ ПОЛУМОСТОВОЙ ТИРИСТОРНЫЙ ИНВЕРТОР | 2005 |

|

RU2294590C1 |

| МОСТОВОЙ ИНВЕРТОР | 2002 |

|

RU2223590C1 |

| ТИРИСТОРНО-КОНДЕНСАТОРНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2325024C1 |

| ТИРИСТОРНЫЙ ИНВЕРТОР | 2006 |

|

RU2314631C1 |

| ОДНОФАЗНЫЙ ПОЛУМОСТОВОЙ ИНВЕРТОР | 2005 |

|

RU2291550C1 |

| Инвертор | 1988 |

|

SU1677829A1 |

| ТРАНЗИСТОРНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1999 |

|

RU2165125C1 |

Предлагается в типовую систему управления полумостовым транзисторным инвертором ввести дополнительно логическую схему в составе двух логических элементов «И» и двух датчиков напряжения на конденсаторах инвертора, причем выходы упомянутых датчиков напряжения и выходы упомянутой системы управления инвертором подключены соответственно к входам двухвходовых логических элементов «И», а выходы упомянутых логических элементов «И» связаны с соответствующими управляющими входами транзисторов полумостового транзисторного инвертора, что позволило получить технический результат - уменьшить потери в транзисторах упомянутого инвертора. 3 ил.

Система управления полумостовым транзисторным инвертором по принципу широтно-импульсной модуляции, выходные каналы которой связаны с управляющими входами транзисторов полумостового инвертора, а вход подключен к выходу автоматического регулятора, отличающаяся тем, что в упомянутую систему управления дополнительно введены два логических двухвходовых элемента И и два датчика напряжения на конденсаторах полумостового транзисторного инвертора, причем выходы упомянутых датчиков напряжения и выходы упомянутой системы управления подключены соответственно к входам двухвходовых логических элементов И, а выходы упомянутых двухвходовых логических элементов И связаны с соответствующими управляющими входами транзисторов полумостового транзисторного инвертора.

| Стабилизированный преобразователь постоянного напряжения | 1990 |

|

SU1728950A1 |

| Способ импульсной стабилизации двухтактного преобразователя постоянного напряжения в постоянное или переменное напряжение | 1987 |

|

SU1536362A1 |

| Устройство для автоматического согласования СВЧ тракта с нагрузкой | 1984 |

|

SU1241153A1 |

Авторы

Даты

2007-11-27—Публикация

2006-07-05—Подача