Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны устройства сравнения двоичных чисел (см., например, нижний рис.в табл.3.5 на стр.103 в книге Справочник по цифровой вычислительной технике. Малиновский Б.Н., Александров В.Я., Боюн В.П. и др. / Под ред. Б.Н.Малиновского. Киев: Техника, 1974 г.), реализующие оператор отношения x2≥x1, где х1, х2∈{0,1} - одноразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных устройств сравнения двоичных чисел, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается сравнение n-разрядных двоичных чисел, задаваемых двоичными сигналами.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятое за прототип устройство сравнения двоичных чисел (рис.4.18 на стр.163 в книге Бибило П.Н. Основы языка VHDL. М.: Солон-Р, 2000 г.), которое содержит элемент НЕ и при варьировании размерности реализует оператор отношения А≥В, где A=an-1...a0 и В=bn-1...b0 есть n-разрядные двоичные числа, задаваемые двоичными сигналами a0, ..., an-1, b0, ..., bn-1∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложность устройства, обусловленная неоднородностью состава (прототип состоит из элементов пяти типов).

Техническим результатом изобретения является упрощение устройства за счет повышения однородности состава при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в устройстве сравнения двоичных чисел, содержащем элемент НЕ, особенность заключается в том, что в него дополнительно введены n мажоритарных элементов, имеющих по три входа, и n-1 элементов НЕ, причем выход i-го ( ) элемента НЕ соединен с третьим входом i-го мажоритарного элемента, выход предыдущего мажоритарного элемента подключен к второму входу последующего мажоритарного элемента, а выход n-го мажоритарного элемента является выходом устройства сравнения двоичных чисел, i-й и (n+i)-й входы которого соединены соответственно с первым входом i-го мажоритарного элемента и входом i-го элемента НЕ.

) элемента НЕ соединен с третьим входом i-го мажоритарного элемента, выход предыдущего мажоритарного элемента подключен к второму входу последующего мажоритарного элемента, а выход n-го мажоритарного элемента является выходом устройства сравнения двоичных чисел, i-й и (n+i)-й входы которого соединены соответственно с первым входом i-го мажоритарного элемента и входом i-го элемента НЕ.

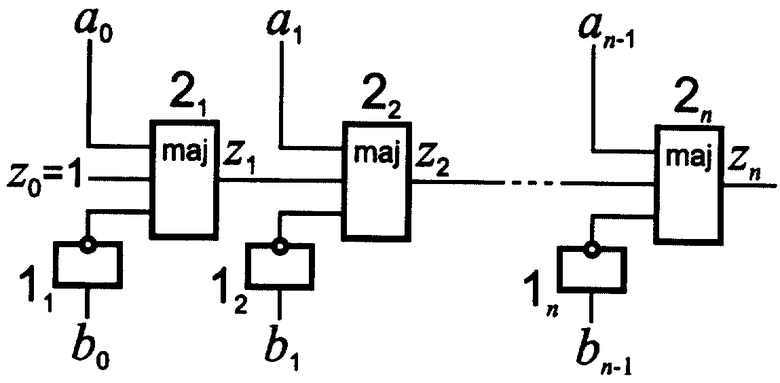

На чертеже представлена схема предлагаемого устройства сравнения двоичных чисел.

Устройство сравнения двоичных чисел содержит элементы НЕ 11, ..., 1n и мажоритарные элементы 21, ..., 2n, имеющие по три входа, причем выход элемента 1i ( ) соединен с третьим входом элемента 2i, выход элемента 2j (

) соединен с третьим входом элемента 2i, выход элемента 2j ( ) подключен к второму входу элемента 2j+1, а выход элемента 2n является выходом устройства сравнения двоичных чисел, i-й и (n+i)-й входы которого соединены соответственно с первым входом элемента 2i и входом элемента 1i.

) подключен к второму входу элемента 2j+1, а выход элемента 2n является выходом устройства сравнения двоичных чисел, i-й и (n+i)-й входы которого соединены соответственно с первым входом элемента 2i и входом элемента 1i.

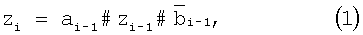

Работа предлагаемого устройства сравнения двоичных чисел осуществляется следующим образом. На его первый, ..., n-й и (n+1)-й, ..., (2n)-й входы подаются соответственно произвольные двоичные сигналы a0, ..., an-1∈{0,1} и b0, ..., bn-1∈{0,l}, которые задают подлежащие сравнению n-разрядные двоичные числа А=аn-1...a0 и В=bn-1...b0 (an-1, bn-1 задают значения старших, а а0, b0 - младших разрядов). На втором входе элемента 21 фиксируется сигнал логической единицы. Тогда сигнал на выходе элемента 2i ( ) будет определяться выражением

) будет определяться выражением

где # - символ операции Maj; z0=1. В представленной ниже таблице приведены значения реализуемой выражением (1) мажоритарной функции на всех возможных наборах значений ее аргументов.

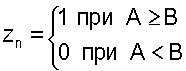

Анализ данных, приведенных в таблице, позволяет заключить, что: 1) если ai-1<bi-1 или ai-1=bi-1 и zi-1=0, то zi=0; 2) если ai-1>bi-1 или ai-1=bi-1 и zi-1=1, то zi=1. Таким образом, на выходе предлагаемого устройства получим

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство сравнения двоичных чисел реализует оператор отношения А≥В, где А=an-1...a0 и В=bn-1...b0 есть n-разрядные двоичные числа, задаваемые двоичными сигналами a0, ..., an-1, b0,..., bn-1∈{0,1}, и имеет более однородный по сравнению с прототипом состав, так как состоит из элементов только двух типов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2020 |

|

RU2762621C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2020 |

|

RU2757829C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2012 |

|

RU2507564C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2009 |

|

RU2420789C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2012 |

|

RU2504825C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363036C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2017 |

|

RU2677371C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363037C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2019 |

|

RU2709653C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2324971C1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых компараторах, ассоциативных процессорах и машинах баз данных. Техническим результатом является упрощение устройства. Устройство сравнения двоичных чисел предназначено для реализации оператора отношения А≥В, где A=an-1...a0, B=bn-1...b0 есть n-разрядные двоичные числа, задаваемые двоичными сигналами α0, ..., an-1, b0, ..., bn-1∈{0,1}. Устройство содержит n элементов НЕ и n мажоритарных элементов, имеющих по три входа. 1 ил.

Устройство сравнения двоичных чисел, содержащее элемент НЕ, отличающееся тем, что в него дополнительно введены n мажоритарных элементов, имеющих по три входа, и n-1 элементов НЕ, причем выход i-го  элемента НЕ соединен с третьим входом i-го мажоритарного элемента, выход предыдущего мажоритарного элемента подключен к второму входу последующего мажоритарного элемента, а выход n-го мажоритарного элемента является выходом устройства сравнения двоичных чисел, i-й и (n+1)-й входы которого соединены соответственно с первым входом i-го мажоритарного элемента и входом i-го элемента НЕ.

элемента НЕ соединен с третьим входом i-го мажоритарного элемента, выход предыдущего мажоритарного элемента подключен к второму входу последующего мажоритарного элемента, а выход n-го мажоритарного элемента является выходом устройства сравнения двоичных чисел, i-й и (n+1)-й входы которого соединены соответственно с первым входом i-го мажоритарного элемента и входом i-го элемента НЕ.

| БИБИЛО П.Н | |||

| Основы языка VHDL | |||

| - М.: Солон-Р, 2000, с.163, рис.4.18 | |||

| УСТРОЙСТВО ДЛЯ ВЫБОРА ОПТИМАЛЬНЫХ РЕШЕНИЙ МЕТОДОМ ГЛАВНОГО КРИТЕРИЯ | 2002 |

|

RU2256218C2 |

| Устройство для сравнения одноразрядных чисел | 1980 |

|

SU947852A1 |

| Устройство для сравнения @ -разрядных двоичных чисел | 1981 |

|

SU1019437A1 |

| US 5623519 A, 22.04.1997 | |||

| US 6795842 B2, 21.09.2004 | |||

| JP 6044044, 18.02.1994. | |||

Авторы

Даты

2008-07-20—Публикация

2007-03-09—Подача