Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (ДУ) на n-р-n и р-n-р транзисторах [1-36], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УД3 и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 100 патентов. Предлагаемое изобретение относится к данному подклассу устройств.

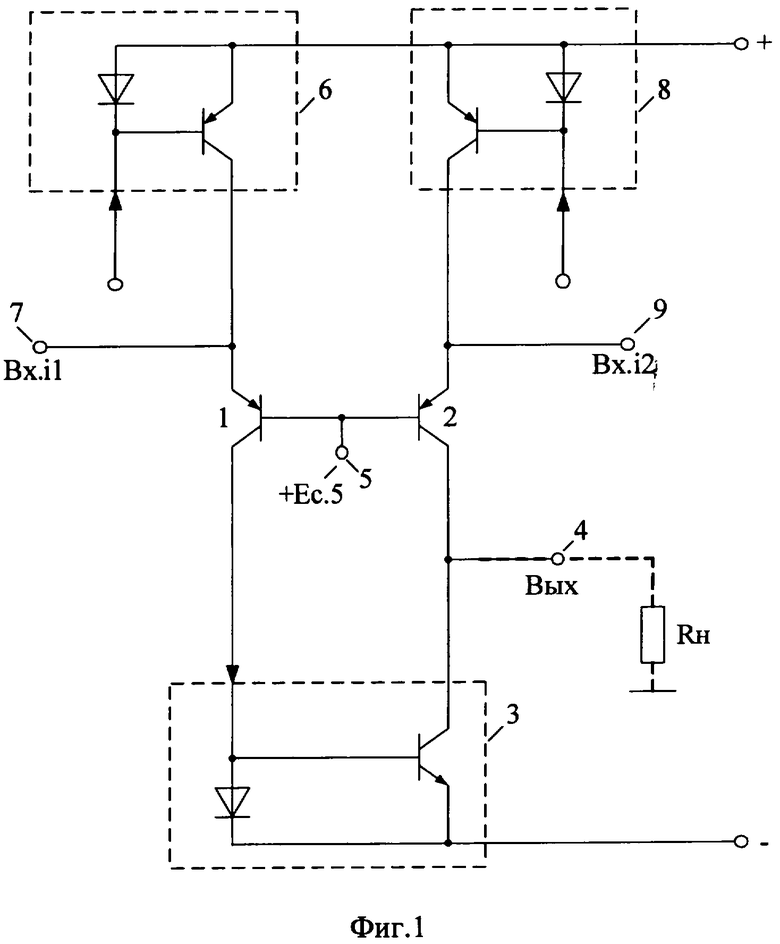

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный дифференциальный усилитель (КДУ), описанный в патенте США №6.529.076, содержащий первый 1 и второй 2 входные транзисторы, выходное токовое зеркало 3, вход которого связан с коллектором первого 1 входного транзистора, а выход подключен к коллектору второго 2 входного транзистора и выходу 4 каскодного дифференциального усилителя, источник напряжения смещения 5, подключенный к базам первого 1 и второго 2 входных транзисторов, первый управляемый источник опорного тока 6, выход которого связан с эмиттером первого 1 входного транзистора и первым 7 входом каскодного дифференциального усилителя, второй управляемый источник опорного тока 8, выход которого связан с эмиттером второго 2 входного транзистора и вторым 9 входом каскодного дифференциального усилителя.

Существенный недостаток известного КДУ (фиг.1) состоит в том, что он имеет сравнительно узкий диапазон линейной работы, в пределах которого сохраняется пропорциональность между входным и выходным током. Это отрицательно сказывается на быстродействии аналоговых устройств на его основе, например, операционных усилителей.

Основная цель предлагаемого изобретения состоит в расширении диапазона линейной работы КДУ.

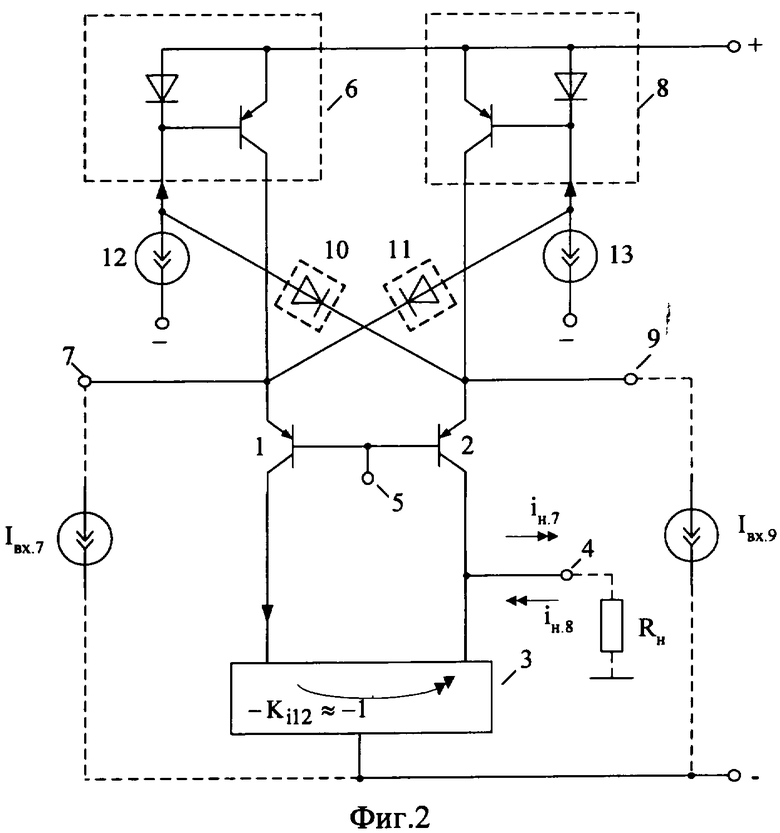

Поставленная цель достигается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, выходное токовое зеркало 3, вход которого связан с коллектором первого 1 входного транзистора, а выход подключен к коллектору второго 2 входного транзистора и выходу 4 каскодного дифференциального усилителя, источник напряжения смещения 5, подключенный к базам первого 1 и второго 2 входных транзисторов, первый управляемый источник опорного тока 6, выход которого связан с эмиттером первого 1 входного транзистора и первым 7 входом каскодного дифференциального усилителя, второй управляемый источник опорного тока 8, выход которого связан с эмиттером второго 2 входного транзистора и вторым 9 входом каскодного дифференциального усилителя, предусмотрены новые элементы и связи - в схему введены первый 10 и второй 11 дополнительные двухполюсники, причем первый 10 дополнительный двухполюсник включен между входом первого 6 управляемого источника опорного тока и эмиттером второго 2 входного транзистора, а второй 11 дополнительный двухполюсник включен между входом второго 8 управляемого источника опорного тока и эмиттером первого 1 входного транзистора.

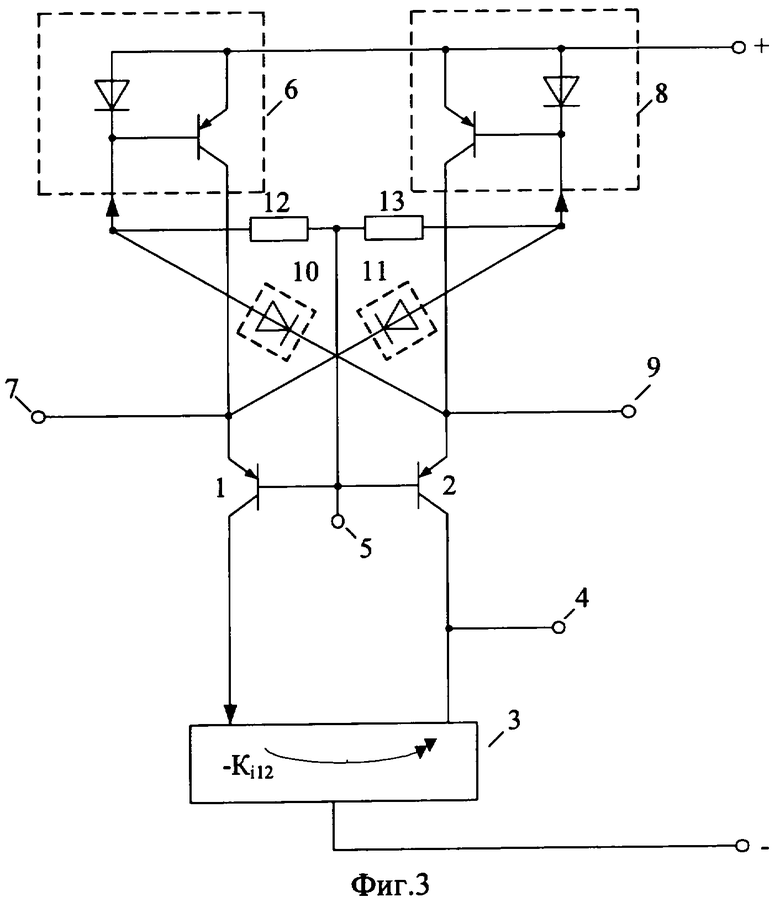

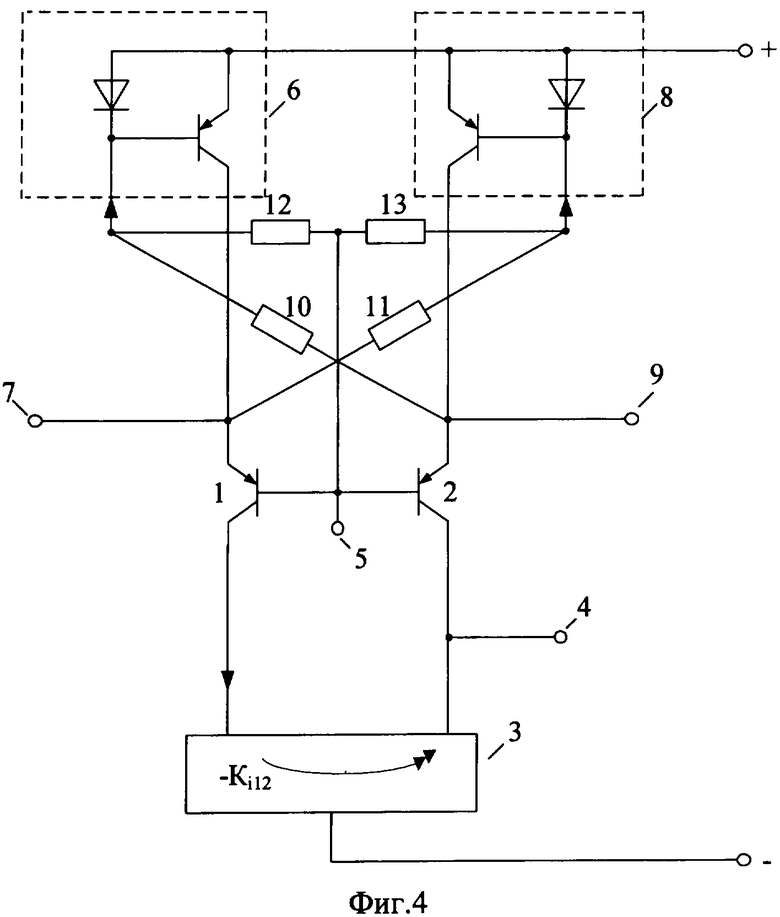

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1, п.2 и п.4 формулы изобретения. На фиг.3 показана схема заявляемого устройства в соответствии с п.4 и п.3 формулы изобретения. На фиг.4 изображен КДУ, соответствующий п.3 и п.5 формулы изобретения.

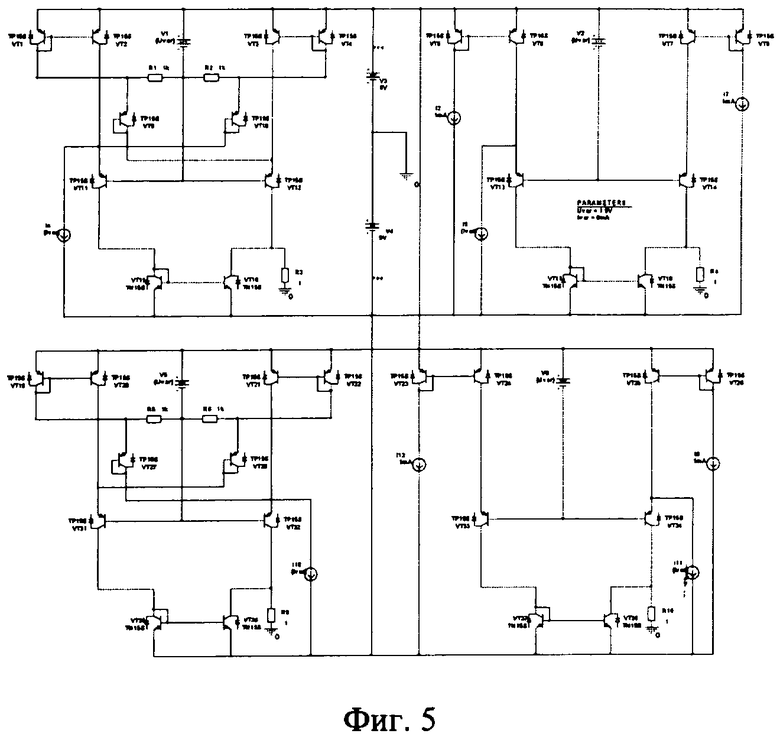

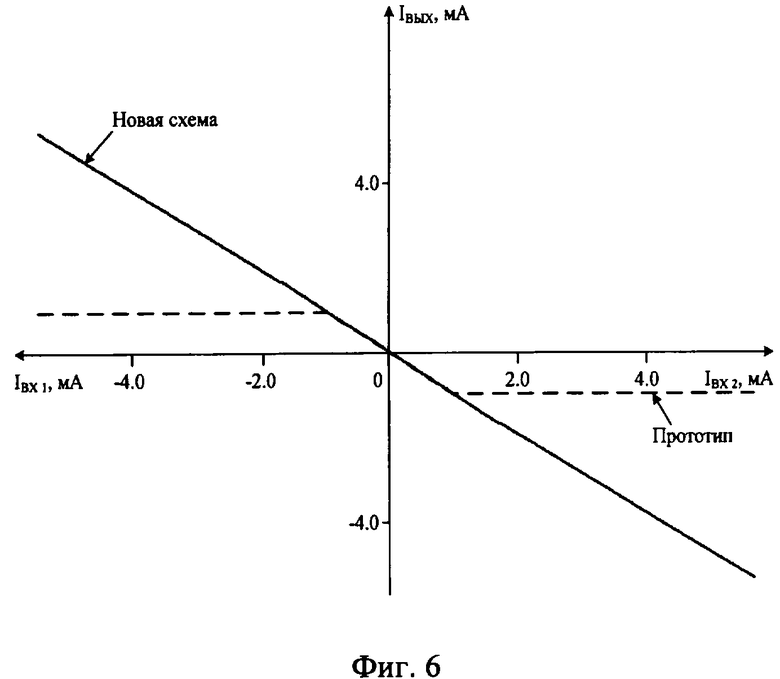

На фиг.5 изображен заявляемый КДУ фиг.3 и КДУ-прототип фиг.1 в среде компьютерного моделирования PSpice, а на фиг.6 показаны результаты расчета их амплитудной характеристики - зависимости выходного тока от токов на входах 7 и 9.

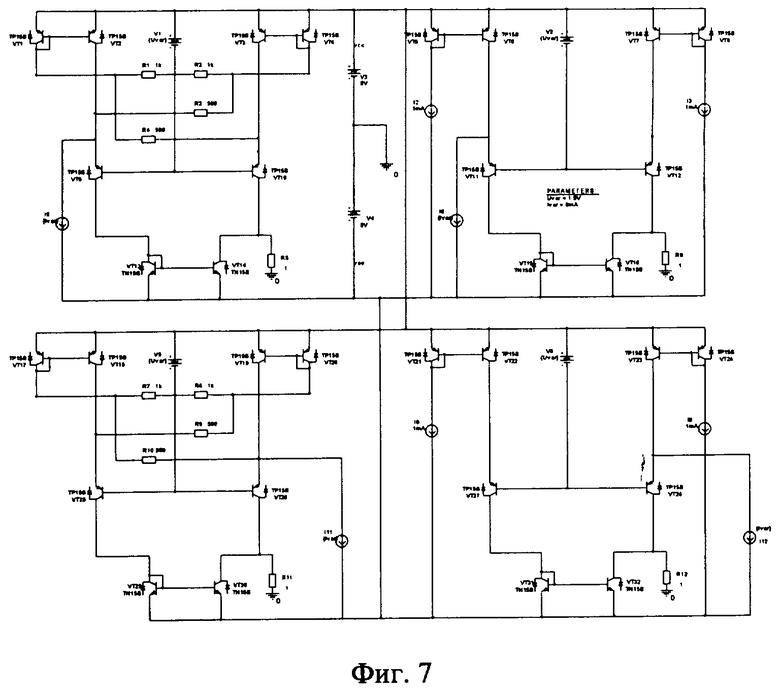

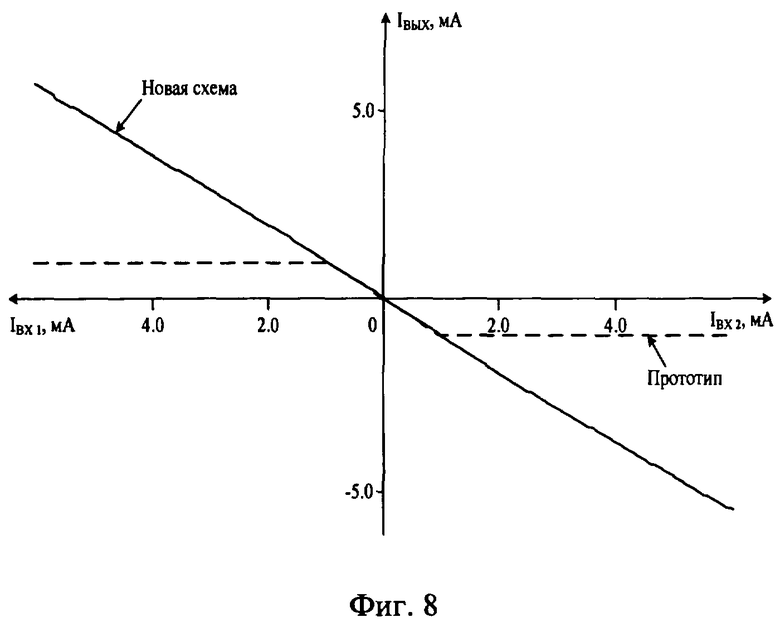

На фиг.7 изображен заявляемый КДУ фиг.4 и КДУ-прототип фиг.1 в среде компьютерного моделирования PSpice, а на фиг.8 - результаты расчета их амплитудной характеристики - зависимости выходного тока от токов на входах 7 и 9.

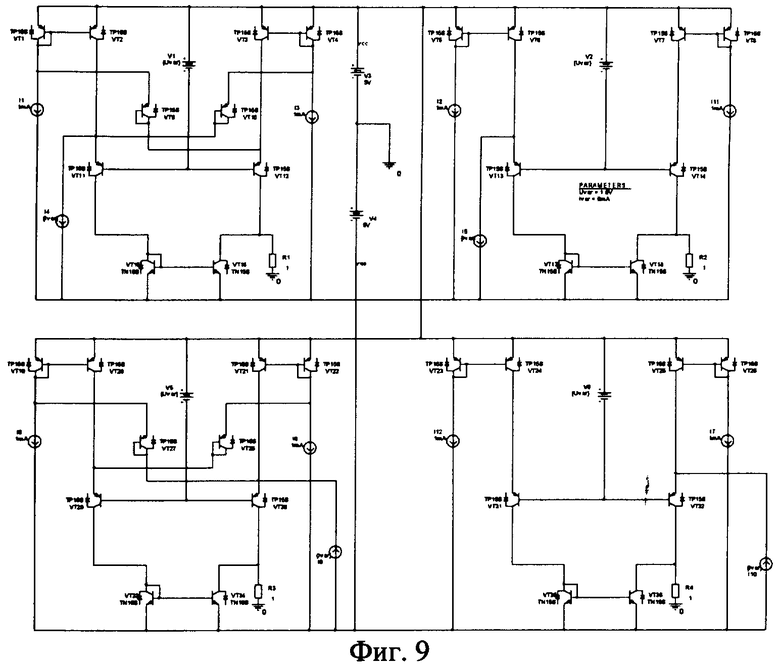

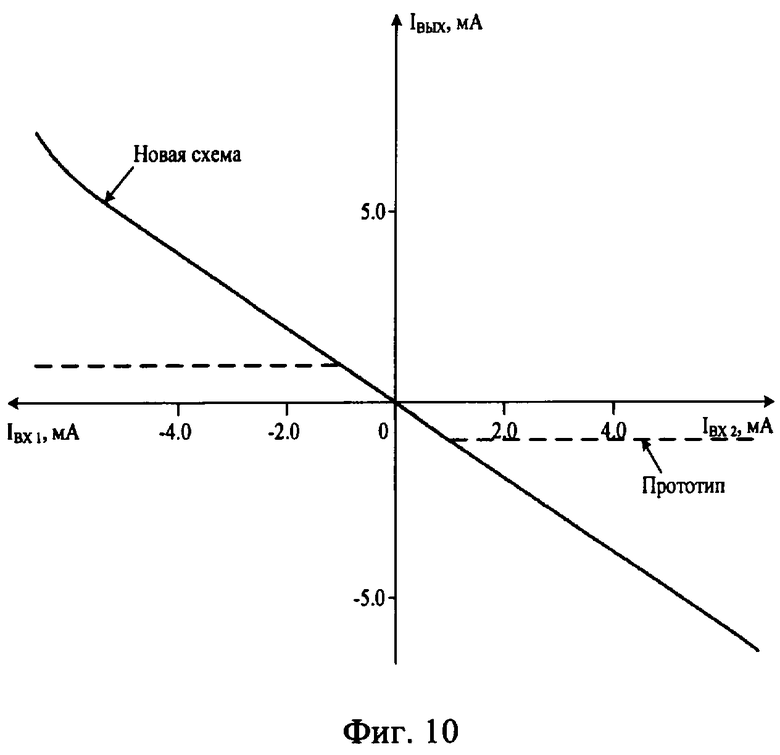

На фиг.9 изображен заявляемый КДУ фиг.2 и КДУ-прототип фиг.1 в среде компьютерного моделирования PSpice, а на фиг.10 - результаты расчета их амплитудной характеристики - зависимости выходного тока от токов на входах 7 и 9.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, выходное токовое зеркало 3, вход которого связан с коллектором первого 1 входного транзистора, а выход подключен к коллектору второго 2 входного транзистора и выходу 4 каскодного дифференциального усилителя, источник напряжения смещения 5, подключенный к базам первого 1 и второго 2 входных транзисторов, первый управляемый источник опорного тока 6, выход которого связан с эмиттером первого 1 входного транзистора и первым 7 входом каскодного дифференциального усилителя, второй управляемый источник опорного тока 8, выход которого связан с эмиттером второго 2 входного транзистора и вторым 9 входом каскодного дифференциального усилителя. В схему введены первый 10 и второй 11 дополнительные двухполюсники, причем первый 10 дополнительный двухполюсник включен между входом первого 6 управляемого источника опорного тока и эмиттером второго 2 входного транзистора, а второй 11 дополнительный двухполюсник включен между входом второго 8 управляемого источника опорного тока и эмиттером первого 1 входного транзистора.

На фиг.2 в соответствии с п.2 формулы изобретения ко входу первого 6 управляемого источника опорного тока подключен первый 12 вспомогательный токостабилизирующий двухполюсник, а ко входу второго 8 управляемого источника опорного тока подключен второй 13 вспомогательный токостабилизирующий двухполюсник.

На фиг.3 в соответствии с п.3 формулы изобретения первый 12 вспомогательный токостабилизирующий двухполюсник включен между базой первого 1 входного транзистора и входом первого 6 управляемого источника опорного тока, а второй 13 вспомогательный токостабилизирующий двухполюсник включен между базой второго 2 входного транзистора и входом второго 8 управляемого источника опорного тока.

На фиг.2 и фиг.3 в соответствии с п.4 формулы изобретения в качестве первого 10 и второго 11 дополнительных двухполюсников используются р-n переходы.

На фиг.4 в соответствии с п.5 формулы изобретения в качестве первого 10 и второго 11 дополнительных двухполюсников используются резисторы.

Рассмотрим работу заявляемого каскодного дифференциального усилителя на примере анализа схемы фиг.2.

Статический режим по току КДУ фиг.2 устанавливается вспомогательными двухполюсниками 12 и 13 и управляемыми источниками тока, которые подключаются ко входам 7 и 9.

В качестве Iвх.7 и Iвх.9 используются, например, входные дифференциальные каскады [], у которых выходные токи Iвх.7 и Iвх.9 изменяются от нуля до некоторого максимального значения Imax. За счет надлежащего выбора напряжения на базах транзисторов 1 и 2 обеспечивается закрытое (или почти закрытое) состояние р-n переходов 10 и 11. Этим обеспечивается минимизация влияния двухполюсников 10 и 11 на работу схемы при малых изменениях токов Iвх.7 и Iвх.9.

Действительно, небольшие увеличения входного тока КДУ фиг.2 Iвх.7 приводят к уменьшению коллекторного тока транзистора 1 и появлению приращения тока в нагрузке iн7. Однако максимальные значения iн7 не превышают уровня:

Iн.7.max<I12,

где I12=I6 - статический ток двухполюсника 12 (выходной статический ток первого управляемого источника опорного тока 6).

Таким образом, при небольших изменениях входных токов КДУ фиг.2, так же как и КДУ-прототип, имеет ограничения на амплитудной характеристике iн=f(iвх), что является хорошо известной особенностью каскадов режима класса «А».

При дальнейшем увеличении входного тока Iвх.7 транзистор 1 полностью запирается, что создает условие для перехода двухполюсника 11 в активное состояние. Поэтому дальнейшее приращение Iвх.7>I12 передается через р-n переход 11 на вход повторителя тока 8, а затем в эмиттер и коллектор транзистора 2. Как следствие, ток в нагрузке Rн получает дальнейшее приращение, пропорциональное Iвх.7. Таким образом, в заявляемой схеме обеспечивается более широкий диапазон линейной работы. Это позволяет на 1-2 порядка повысить максимальную скорость нарастания выходного напряжения ОУ на основе КДУ фиг.2 [1].

Особенность схем фиг.3 и фиг.4 состоит в том, что статический режим управляемых источников опорного тока 6 и 8 устанавливается здесь выбором сопротивлений двухполюсников 12, 13 и напряжения смещения на базе транзисторов 1 и 2.

Кроме этого, в схеме фиг.4 в качестве двухполюсников 10 и 11 используются резисторы. При надлежащем выборе напряжения на базах транзисторов 1 и 2 токи через них в статическом режиме могут быть близки к нулю. Однако при запирании эмиттерно-базового перехода транзисторов 1 (2) эти резисторы создают дополнительный канал передачи входного тока в нагрузку.

Представленные на фиг.5 - 10 схемы заявляемого и известного КДУ, а также результаты их компьютерного моделирования подтверждают преимущества заявляемой схемы - в отличие от прототипа новая схема обеспечивает линейную зависимость выходной токовой координаты от входных токов. Это создает условия для улучшения многих динамических параметров аналоговых микросхем на ее основе.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. Л., 1979. 148 с.

2. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - с.74, рис.4.15, стр.98, рис.6.7.

3. Патент США №6.218.900, фиг.1

4. Патентная заявка US 2002/0196079

5. Патент США №6.788.143

6. Патент США №3.644.838, фиг.2

7. Патент США Re 30.587

8. Патент ЕР 1.227.580

9. Патент США №6.714.076

10. Патент США №5.786.729

11. Патент США №5.327.100

12. Патентная заявка US 2004/0090268 A1

13. Патент США №4.274.061

14. Патент США №5.422.600, фиг.2

15. Патент США №6.788.143, фиг.2

16. Патент США №4.959.622, фиг.1

17. Патент США №4.406.990, фиг.4

18. Патент США №5.418.491

19. Патент США №6.018.268

20. Патент США №5.952.882

21. Патент США №4.723.111

22. Патент США №4.293.824

23. Патент США №6.580.325

24. Патент США №6.965.266

25. Патент США №6.867.643

26. Патент США №6.236.270

27. Патент США №5.323.121

28. Патент США №6.229.394

29. Патент США №5.734.296

30. Патент США №5.477.190

31. Патент США №5.091.701

32. Патент США №6.717.474

33. Патент США №6.084.475

34. Патент США №3.733.559

35. Патентная заявка US 2005/0001682 A1

36. Патент США №6.300.831

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2337469C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319292C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411642C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| КОМПЛЕМЕНТАРНЫЙ ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2370879C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2390911C2 |

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)). Технический результат: расширение диапазона линейной работы. Каскодный дифференциальный усилитель (КДУ) содержит первый (1) и второй (2) входные транзисторы (Т), выходное токовое зеркало (3), вход которого связан с коллектором первого (1) входного Т, а выход подключен к коллектору второго (2) входного Т и выходу (4) КДУ, источник напряжения смещения (5), подключенный к базам первого (1) и второго (2) входных Т, первый управляемый источник опорного тока (ИОТ) (6), выход которого связан с эмиттером первого (1) входного Т и первым (7) входом КДУ, второй управляемый ИОТ (8), выход которого связан с эмиттером второго (2) входного Т и вторым (9) входом КДУ. В схему введены первый (10) и второй (11) дополнительные двухполюсники, причем первый (10) дополнительный двухполюсник включен между входом первого (6) управляемого ИОТ и эмиттером второго (2) входного Т, а второй (11) дополнительный двухполюсник включен между входом второго (8) управляемого ИОТ и эмиттером первого (1) входного Т. 4 з.п. ф-лы, 10 ил.

| US 6529076 B1, 04.03.2003 | |||

| Каскодный дифференциальный усилитель | 1980 |

|

SU1164865A1 |

| US 6229394 B1, 08.05.2001 | |||

| US 5748040 A, 05.05.1998 | |||

| US 5455535 A, 03.10.1995. | |||

Авторы

Даты

2009-03-10—Публикация

2007-09-10—Подача