Изобретение относится к области «полевые транзисторы», в частности к силовым вертикальным транзисторам, содержащим МОП-структуру, изготавливаемую с применением двойной диффузии, имеющим электроды истока (эмиттера) и затвора на одной поверхности подложки, а электрод стока (коллектора) - на противоположной поверхности подложки.

Известна конструкция транзистора с изолированным затвором (ТИЗ), ограничивающая максимальный ток, состоящая из полупроводниковой подложки, имеющей первую и вторую противолежащие большие поверхности, на первой из которых сформирован вертикальный N-канальный МОП-транзистор с электродами эмиттера и затвора, а на второй поверхности с высокой концентрацией примеси Р+-типа в полупроводниковой подложке - электрод коллектора (патент US 4,641,162 от 03.02.1987 МПК H01L 29/02). Достоинством описанного ТИЗ является наличие конструкции эмиттера, разделенного на несколько частей в каждой ячейке, позволяющей путем уменьшения периметра эмиттера каждой ячейки ограничивать максимальный ток коллектора, что имеет большое значение при применении его в режимах, допускающих кратковременное короткое замыкание нагрузки.

Основным недостатком ТИЗ является повышенная степень интеграции транзистора, так как при современной миниатюризации ячеек мощных транзисторов, какими являются ТИЗ, необходимо область эмиттера разделить еще на несколько частей с помощью дополнительных операций фотолитографии, что в свою очередь приведет к дальнейшей миниатюризации, снижению выхода годных приборов и удорожанию транзистора.

Известны конструкции БТИЗ с короткозамкнутым коллектором (патент US 4,841,345 от 20.06.1989, МПК H01L 29/739, US 5,070,377 от 03.12.1991, МПК H01L 29/66), состоящие из полупроводниковой подложки, имеющей первую и вторую противолежащие большие поверхности. На первой поверхности сформирован вертикальный N-канальный ДМОП-транзистор с электродами эмиттера и затвора, а на второй поверхности - чередующиеся области высокой концентрации примеси Р+ и N+-типа, прилегающие к коллекторному электроду.

Из описания этих транзисторов следует, что перемежающиеся области Р+ и N+-типа, прилегающие к коллекторному электроду, используются для встраивания обратного диода у БТИЗ, как у ДМОП-транзистора, что имеет большое значение при переключении индуктивной нагрузки и для повышения быстродействия БТИЗ, у которого неосновные носители рассасываются значительно быстрее благодаря наличию на второй поверхности областей N-типа, чередующихся с инжектирующими дырки Р-областями.

Недостатком известных транзисторов является отсутствие ограничения коллекторного тока.

Патент US 4,641,162 от 03.02.1987 МПК H01L 29/02 взят за прототип.

Целью изобретения является изготовление транзистора с заданным ограничением тока, увеличение точности воспроизводимости заданного токоогранничения, увеличение выхода годных транзисторов в процентном соотношении, снижение себестоимости изготовления транзисторов.

Технический результат достигается тем, что изготавливают транзистор с ограничением тока, содержащий подложку, имеющую первую и вторую противолежащие поверхности, ДМОП-транзистор, расположенный на первой поверхности подложки, многочисленные чередующиеся между собой области N-типа и Р-типа проводимости, расположенные на второй поверхности подложки, отличающийся тем, что ячейки ДМОП-транзистора на первой поверхности подложки имеют форму полос, многочисленные чередующиеся между собой области N-типа и Р-типа проводимости имеют форму полос на второй поверхности подложки, причем полосы на второй поверхности подложки расположены перпендикулярно относительно полос на первой поверхности подложки, в соответствии со способом изготовления транзистора с ограничением тока, заключающимся в формировании ДМОП-транзистора на первой поверхности подложки и многочисленных чередующихся между собой областей N-типа и Р-типа проводимости на второй поверхности подложки, противолежащей первой поверхности подложки, отличающийся тем, что для расчета тока ограничения коллектора IK макс, который равен IP+IN, формируют отношение площадей областей N-типа и Р-типа проводимости на второй поверхности подложки посредством маски фотошаблона в соответствии с соотношением:

IP/IN=SP/SN×1/(1/y-1),

где IP - суммарный ток инжекции дырок из Р-типа областей;

IN - суммарный ток электронов N-типа областей;

SP - суммарная площадь областей Р-типа проводимости на второй поверхности подложки;

SN - суммарная площадь областей N-типа проводимости на второй поверхности подложки;

y - коэффициент инжекции P/N переходов на второй поверхности подложки.

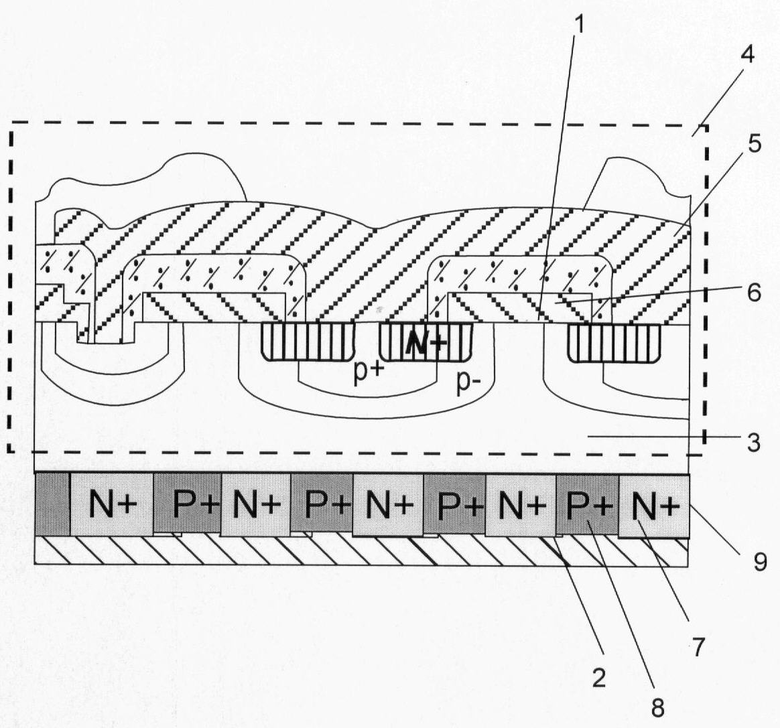

На чертеже изображен транзистор с ограничением тока, содержащий полупроводниковую подложку 3 N-типа с первой поверхностью 1 и второй поверхностью 2, которые противолежат друг другу, ДМОП-транзистор 4 с электродом 5 истока-эмиттера и затвора 6, сформированный на первой поверхности 1, многочисленные области 7 N-типа проводимости, смежные с областями 8 Р-типа проводимости, сформированные на второй поверхности 2, контактный металл 9 стока-коллектора, напыленный на области 7 и 8.

Для ограничения максимального тока коллектора-стока транзистора на определенном уровне для защиты его от разрушения при внезапном превышении максимального тока (например, при коротком замыкании цепи нагрузки) на время срабатывания внешней схемы защиты устройства отношение площадей области 7 N-типа и области 8 Р-типа проводимости на второй поверхности задается маской фотошаблона при формировании этих областей в соответствии с формулой:

где IP - суммарный ток инжекции дырок из Р-типа областей;

IN - суммарный ток электронов N-типа областей;

SP - суммарная площадь областей Р-типа проводимости на второй поверхности подложки;

SN - суммарная площадь областей N-типа проводимости на второй поверхности подложки;

y - коэффициент инжекции P/N переходов на второй поверхности подложки.

В других конструкциях транзисторов с короткозамкнутым коллектором ток проводимости IN растет по линейному закону, а ток инжекции IP - по квадратичному в зависимости от напряжения сток - исток (коллектор - эмиттер). После превышения на P/N переходе напряжения ~0,5 В IP может стать значительно больше как IN, так и предельного тока эксплуатации транзистора, особенно в режиме короткого замыкания нагрузки.

Однако если транзистор сконструирован в соответствии с условием формулы [1] так, что IP<IK макс (IK макс - максимальный ток коллектора, который транзистор может выдержать без разрушения более 10 микросекунд), то он сможет без разрушения выдержать время, достаточное для срабатывания внешней схемы защиты от перегрузки, то есть не менее 10 микросекунд.

Разберем принцип действия транзистора с ограничением тока по изобретению. У транзистора с короткозамкнутым коллектором при положительном напряжении затвор - исток (затвор - эмиттер), превышающем пороговое, ток стока (коллектора) нарастает линейно при нарастании положительного напряжения сток - исток (коллектор - эмиттер) от 0 до ~0,5 В, как у ДМОП-транзистора. При повышении напряжения сток - исток (коллектор - эмиттер) выше 0,5 В ток стока (коллектора) через транзистор, за счет модуляции проводимости неосновными носителями, инжектируемыми из Р+-областей на второй поверхности, растет по квадратичному закону, как у БТИЗ, и достигает высоких значений при напряжениях сток - исток (коллектор - эмиттер), значительно меньших, чем у ДМОП-транзистора. Падение напряжения в открытом состоянии у такого транзистора значительно ниже, чем у равного по площади ДМОП-транзистора, а поэтому и ток коллектора может достигать значений, значительно превышающих рабочий ток. С целью ограничения тока, что особенно важно при работе транзистора в режиме короткого замыкания нагрузки, у транзистора с ограничением тока по изобретению отношение площадей областей Р-типа и N-типа проводимости на второй поверхности изготавливаются в соответствии с формулой [1], которая связывает между собой отношение дырочного и электронного токов с соответствующими площадями областей N-типа и Р-типа проводимости на второй поверхности через коэффициент инжекции y.

Заявленный транзистор можно изготавливать несколькими способами. В первом варианте способа изготовление начинается с формирования на второй поверхности подложки методами микроэлектроники (ионное легирование, фотолитография, высокотемпературные обработки) многочисленных областей N-типа проводимости, смежных с областями Р-типа проводимости с дальнейшим формированием на первой поверхности подложки ДМОП-транзистора с электродами истока и затвора.

Во втором варианте способа изготовление транзистора начинается с формирования ДМОП-транзистора с электродами истока и затвора на первой поверхности подложки с последующим формированием многочисленных областей N-типа проводимости, смежных с областями Р-типа проводимости на второй поверхности подложки.

В третьем варианте способа изготовление транзистора начинается с формирования областей N-типа и Р-типа проводимости на второй поверхности подложки перед последней высокотемпературной обработкой, применяемой при изготовлении ДМОП-транзистора на первой поверхности подложки.

При изготовлении транзистора используется монокристаллический кремний, который в 1,5-2 раза дешевле эпитаксиального, используемого при изготовлении БТИЗ и ДМОП-транзисторов.

С целью повышения воспроизводимости уровня ограничения тока транзистора с ограничением тока по изобретению преимущественно используется полосковая топология как ДМОП-ячеек на первой поверхности, так и областей Р-типа и N-типа проводимости на второй стоковой (коллекторной) стороне, причем их ориентация на первой и второй стороне взаимоперпендикулярна.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА | 2010 |

|

RU2431905C1 |

| ПОЛУПРОВОДНИКОВЫЙ ПРИБОР | 2010 |

|

RU2437183C1 |

| БИПОЛЯРНЫЙ ТРАНЗИСТОР С ИЗОЛИРОВАННЫМ ДИЭЛЕКТРИКОМ ЗАТВОРОМ | 1992 |

|

RU2065642C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА | 2013 |

|

RU2531122C1 |

| ПЕРИФЕРИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА, НЕЙТРАЛИЗУЮЩАЯ ВЛИЯНИЕ ЗАРЯДОВ НА СТАБИЛЬНОСТЬ ОБРАТНЫХ УТЕЧЕК И ПРОБИВНОГО НАПРЯЖЕНИЯ | 2008 |

|

RU2379786C1 |

| ПОЛУПРОВОДНИКОВЫЙ ПРИБОР | 1992 |

|

RU2065229C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ТРАНЗИСТОР С КОМБИНИРОВАННЫМ ЗАТВОРОМ | 2002 |

|

RU2230394C1 |

| ПОЛУПРОВОДНИКОВЫЙ ПРИБОР С ИЗОЛИРОВАННЫМ ЗАТВОРОМ | 2006 |

|

RU2407107C2 |

| ПЛАНАРНЫЙ СИЛОВОЙ МОП ТРАНЗИСТОР С БЛОКИРУЮЩИМ ЕМКОСТЬ СТОКА БАРЬЕРОМ ШОТТКИ | 2002 |

|

RU2229758C1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

Изобретение относится к силовым вертикальным транзисторам, содержащим МОП-структуру, изготавливаемую с применением двойной диффузии, имеющим электроды истока (эмиттера) и затвора на одной поверхности подложки, а электрод стока (коллектора) - на противоположной поверхности подложки. Сущность изобретения: в транзисторе с ограничением тока, содержащем подложку, имеющую первую и вторую противолежащие поверхности, ДМОП-транзистор, расположенный на первой поверхности подложки, чередующиеся между собой области N-типа и Р-типа проводимости, расположенные на второй поверхности подложки, ячейки ДМОП-транзистора на первой поверхности подложки имеют форму полос, чередующиеся между собой области N-типа и Р-типа проводимости имеют форму полос на второй поверхности подложки, причем полосы на второй поверхности подложки расположены перпендикулярно относительно полос на первой поверхности подложки. При изготовлении транзистора формируют области N-типа и Р-типа проводимости на второй поверхности подложки с определенным соотношеним площадей. Техническим результатом изобретения является изготовление транзистора повышенной стойкости к короткому замыканию цепи нагрузки с заданным ограничением тока, увеличение точности воспроизводимости заданного токоограничения, увеличение выхода годных транзисторов в процентном соотношении, снижение себестоимости изготовления транзисторов. 2 н. и 5 з.п. ф-лы, 1 ил.

1. Транзистор с ограничением тока, содержащий подложку, имеющую первую и вторую противолежащие поверхности, ДМОП-транзистор, расположенный на первой поверхности подложки, чередующиеся между собой области N-типа и Р-типа проводимости, расположенные на второй поверхности подложки, отличающийся тем, что ячейки ДМОП-транзистора на первой поверхности подложки имеют форму полос, чередующиеся между собой области N-типа и Р-типа проводимости имеют форму полос на второй поверхности подложки, причем полосы на второй поверхности подложки расположены перпендикулярно относительно полос на первой поверхности подложки.

2. Способ изготовления транзистора с ограничением тока, заключающийся в формировании ДМОП-транзистора на первой поверхности подложки и чередующихся между собой областей N-типа и Р-типа проводимости на второй поверхности подложки противолежащей первой поверхности подложки, отличающийся тем, что для расчета тока ограничения коллектора IK макс., который равен IP+IN, формируют отношение площадей областей N-типа и Р-типа проводимости на второй поверхности подложки посредством маски фотошаблона в соответствии с соотношением

IP/IN=SP/SN×1/(1/γ-1),

где IP - суммарный ток инжекции дырок из Р-типа областей;

IN - суммарный ток электронов N-типа областей;

SP - суммарная площадь областей Р-типа проводимости на второй поверхности подложки;

SN - суммарная площадь областей N-типа проводимости на второй поверхности подложки;

γ - коэффициент инжекции P/N переходов на второй поверхности подложки.

3. Способ изготовления транзистора по п.2, отличающийся тем, что сначала формируют области N-типа и Р-типа проводимости на второй поверхности подложки, после чего формируют ДМОП-транзистор на первой поверхности подложки.

4. Способ изготовления транзистора по п.2, отличающийся тем, что сначала формируют ДМОП-транзистор на первой поверхности подложки, после чего формируют области N-типа и Р-типа проводимости на второй поверхности подложки.

5. Способ изготовления транзистора по п.2, отличающийся тем, что формируют области N-типа и Р-типа проводимости на второй поверхности подложки перед последней высокотемпературной обработкой, применяемой при изготовлении ДМОП-транзистора на первой поверхности подложки.

6. Способ изготовления транзистора по п.2, отличающийся тем, что формируют ячейки ДМОП-транзистора на первой поверхности подложки в виде полос, расположенных перпендикулярно относительно чередующихся между собой в виде полос областей N-типа и Р-типа проводимости на второй поверхности подложки.

7. Способ изготовления транзистора по п.2, отличающийся тем, что изготавливают транзистор из монокристаллического кремния.

| US 4841345 А, 20.06.1989 | |||

| US 5475243 А, 12.12.1995 | |||

| US 4641162 А, 03.02.1987 | |||

| US 7071513 B1, 04.07.2006 | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНОГО ДМОП-ТРАНЗИСТОРА | 2000 |

|

RU2189089C2 |

Авторы

Даты

2009-10-20—Публикация

2008-02-18—Подача