Изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, а также в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления.

Аналоговый перемножитель (АПН) является базовым узлом современных систем приема и обработки сигналов ВЧ и СВЧ-диапазонов, аналоговой вычислительной и измерительной техники, позволяет решать задачи выделения разностной частоты, аттенюации сигналов. АПН является неотъемлемым звеном квадратурных модуляторов и демодуляторов, а также синхронных фильтров. Высоколинейный широкополосный АПН может служить базовой ячейкой нелинейных СФ-блоков систем на кристале.

Аналоговый перемножитель напряжений (АПН) современных систем связи и телекоммуникаций реализуется, в основном, на базе перемножающей ячейки Джильберта, которая совершенствовалась в более чем 50 патентах ведущих микроэлектронных фирм (см., например, [1-16]).

На основе ячейки Джильберта выполняются не только перемножители напряжений, но и управляемые усилители и смесители (миксеры) сигналов ВЧ и СВЧ диапазонов, удвоители частоты. В этом смысле АНН является базовым функциональным узлом современной микроэлектроники, определяющим качественные показатели многих систем связи.

Предлагаемое изобретение относится к данному классу устройств.

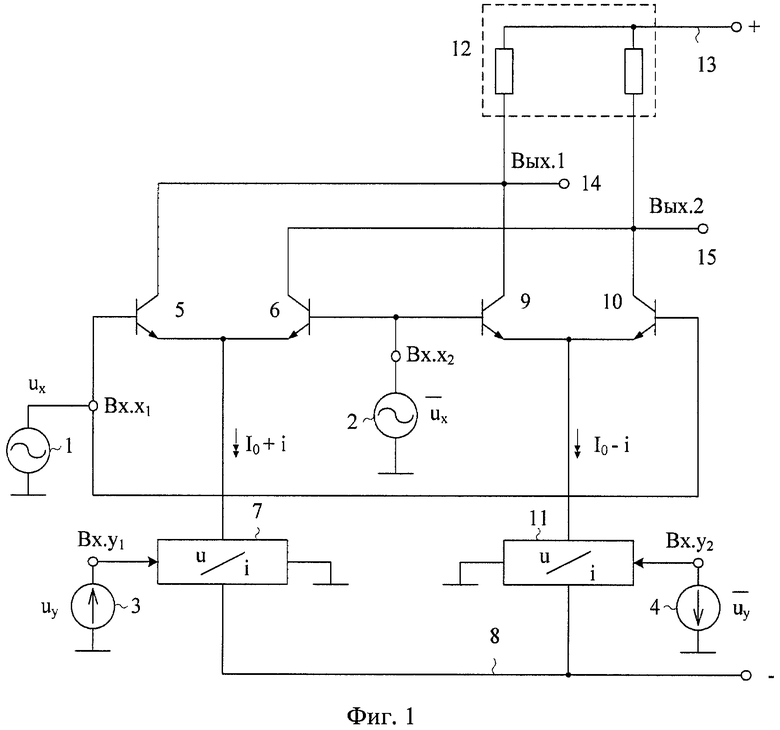

Ближайшим прототипом заявляемого устройства является аналоговый перемножитель, представленный в патенте фирмы Texas Instruments Inc. US №7024448 fig.2, содержащий первый 1 (ux) и второй 2  противофазные источники входного напряжения канала «X», первый 3 (uу) и второй 4

противофазные источники входного напряжения канала «X», первый 3 (uу) и второй 4  противофазные источники входного напряжения канала «Y», первый 5 и второй 6 входные транзисторы, эмиттеры которых объединены и подключены к первому 7 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником напряжения питания, третий 9 и четвертый 10 входные транзисторы, эмиттеры которых объединены и подключены ко второму 11 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником питания, цепь нагрузки 12, связанную со вторым 13 источником питания, а также первым 14 и вторым 15 выходами устройства, коллектор первого 5 входного транзистора подключен к первому 14 выходу устройства, коллектор четвертого 10 входного транзистора соединен со вторым 15 выходом устройства, причем базы второго 6 и третьего 9 входных транзисторов объединены, а база первого 5 входного транзистора соединена с первым 1 (ux) источником входного напряжения канала «X»

противофазные источники входного напряжения канала «Y», первый 5 и второй 6 входные транзисторы, эмиттеры которых объединены и подключены к первому 7 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником напряжения питания, третий 9 и четвертый 10 входные транзисторы, эмиттеры которых объединены и подключены ко второму 11 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником питания, цепь нагрузки 12, связанную со вторым 13 источником питания, а также первым 14 и вторым 15 выходами устройства, коллектор первого 5 входного транзистора подключен к первому 14 выходу устройства, коллектор четвертого 10 входного транзистора соединен со вторым 15 выходом устройства, причем базы второго 6 и третьего 9 входных транзисторов объединены, а база первого 5 входного транзистора соединена с первым 1 (ux) источником входного напряжения канала «X»

Существенный недостаток известного перемножителя напряжений состоит в том, что он не работоспособен при малых напряжениях питания (например, ±1 В). Это связано с «двухъярусной» архитектурой АПН-прототипа.

Основная задача предлагаемого изобретения состоит в снижении напряжения питания до ±0,9÷1 В.

Первая дополнительная цель - расширение частотного диапазона за счет исключения из структуры АПН управляемых источников тока канала «Y», которые реализуются в известной схеме на четырех транзисторах. Такое количество инерционных активных элементов сказывается на частотном диапазоне АПН.

Вторая дополнительная цель - «привязка» источников входного напряжения ux и uу к общей шине источника питания. Решение этой задачи существенно упрощает согласование АПН по входам с источниками сигналов ux и uу, которые могут подаваться относительно общей шины без цепей смещения статического режима, влияющих на стабильность нулевого уровня АПН.

Поставленные цели достигаются тем, что в АПН, содержащем первый 1 (ux) и второй 2  противофазные источники входного напряжения канала «X», первый 3 (uу) и второй 4 (

противофазные источники входного напряжения канала «X», первый 3 (uу) и второй 4 ( ) противофазные источники входного напряжения канала «Y», первый 5 и второй 6 входные транзисторы, эмиттеры которых объединены и подключены к первому 7 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником напряжения питания, третий 9 и четвертый 10 входные транзисторы, эмиттеры которых объединены и подключены ко второму 11 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником питания, цепь нагрузки 12, связанную со вторым 13 источником питания, а также первым 14 и вторым 15 выходами устройства, коллектор первого 5 входного транзистора подключен к первому 14 выходу устройства, коллектор четвертого 10 входного транзистора соединен со вторым 15 выходом устройства, причем базы второго 6 и третьего 9 входных транзисторов объединены, а база первого 5 входного транзистора соединена с первым 1 (ux) источником входного напряжения канала «X», предусмотрены новые элементы и связи - в схему введены пятый 16, шестой 17, седьмой 18 и восьмой 19 входные транзисторы, эмиттеры пятого 16 и шестого 17 входных транзисторов через третий 20 токостабилизирующий двухполюсник связаны с первым 8 источником питания, эмиттеры седьмого 18 и восьмого 19 входных транзисторов через четвертый 21 токостабилизирующий двухполюсник соединены с первым 8 источником питания, базы второго 6 и третьего 9 входных транзисторов подключены к первому 3 источнику входного напряжения uу канала «Y», базы шестого 17 и седьмого 18 входных транзисторов объединены и подключены ко второму 4

) противофазные источники входного напряжения канала «Y», первый 5 и второй 6 входные транзисторы, эмиттеры которых объединены и подключены к первому 7 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником напряжения питания, третий 9 и четвертый 10 входные транзисторы, эмиттеры которых объединены и подключены ко второму 11 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником питания, цепь нагрузки 12, связанную со вторым 13 источником питания, а также первым 14 и вторым 15 выходами устройства, коллектор первого 5 входного транзистора подключен к первому 14 выходу устройства, коллектор четвертого 10 входного транзистора соединен со вторым 15 выходом устройства, причем базы второго 6 и третьего 9 входных транзисторов объединены, а база первого 5 входного транзистора соединена с первым 1 (ux) источником входного напряжения канала «X», предусмотрены новые элементы и связи - в схему введены пятый 16, шестой 17, седьмой 18 и восьмой 19 входные транзисторы, эмиттеры пятого 16 и шестого 17 входных транзисторов через третий 20 токостабилизирующий двухполюсник связаны с первым 8 источником питания, эмиттеры седьмого 18 и восьмого 19 входных транзисторов через четвертый 21 токостабилизирующий двухполюсник соединены с первым 8 источником питания, базы второго 6 и третьего 9 входных транзисторов подключены к первому 3 источнику входного напряжения uу канала «Y», базы шестого 17 и седьмого 18 входных транзисторов объединены и подключены ко второму 4  источнику противофазного входного напряжения канала «Y», база пятого 16 входного транзистора подключена к базе первого 5 входного транзистора, база восьмого 19 входного транзистора соединена с базой четвертого 10 входного транзистора и вторым 2

источнику противофазного входного напряжения канала «Y», база пятого 16 входного транзистора подключена к базе первого 5 входного транзистора, база восьмого 19 входного транзистора соединена с базой четвертого 10 входного транзистора и вторым 2  источником противофазного входного напряжения канала «X», коллектор пятого 16 входного транзистора подключен ко второму 15 выходу устройства, коллектор восьмого 19 входного транзистора соединен с первым 14 выходом устройства, общий узел объединенных коллекторов шестого 17 и восьмого 18 входных транзисторов связан через первый 22 дополнительный резистор со вторым 15 выходом устройства, а через второй 23 дополнительный резистор соединен с первым 14 выходом устройства, общий узел объединенных коллекторов второго 6 и третьего 9 входных транзисторов через третий 24 дополнительный резистор соединен со втором 15 выходом устройства, а через четвертый 25 дополнительный резистор соединен с первым 14 выходом устройства.

источником противофазного входного напряжения канала «X», коллектор пятого 16 входного транзистора подключен ко второму 15 выходу устройства, коллектор восьмого 19 входного транзистора соединен с первым 14 выходом устройства, общий узел объединенных коллекторов шестого 17 и восьмого 18 входных транзисторов связан через первый 22 дополнительный резистор со вторым 15 выходом устройства, а через второй 23 дополнительный резистор соединен с первым 14 выходом устройства, общий узел объединенных коллекторов второго 6 и третьего 9 входных транзисторов через третий 24 дополнительный резистор соединен со втором 15 выходом устройства, а через четвертый 25 дополнительный резистор соединен с первым 14 выходом устройства.

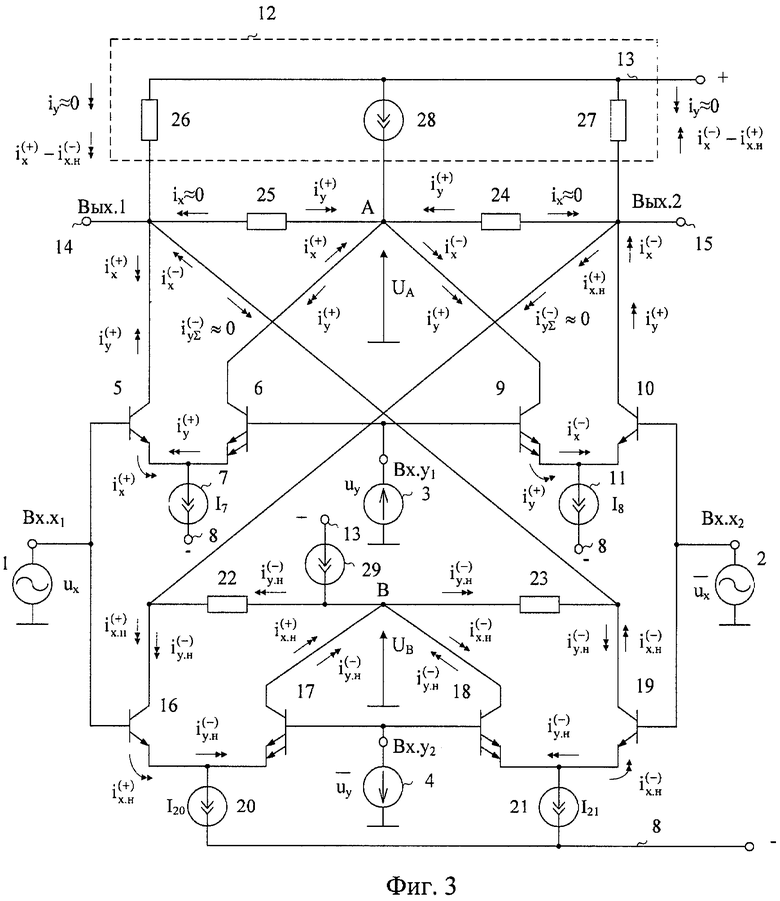

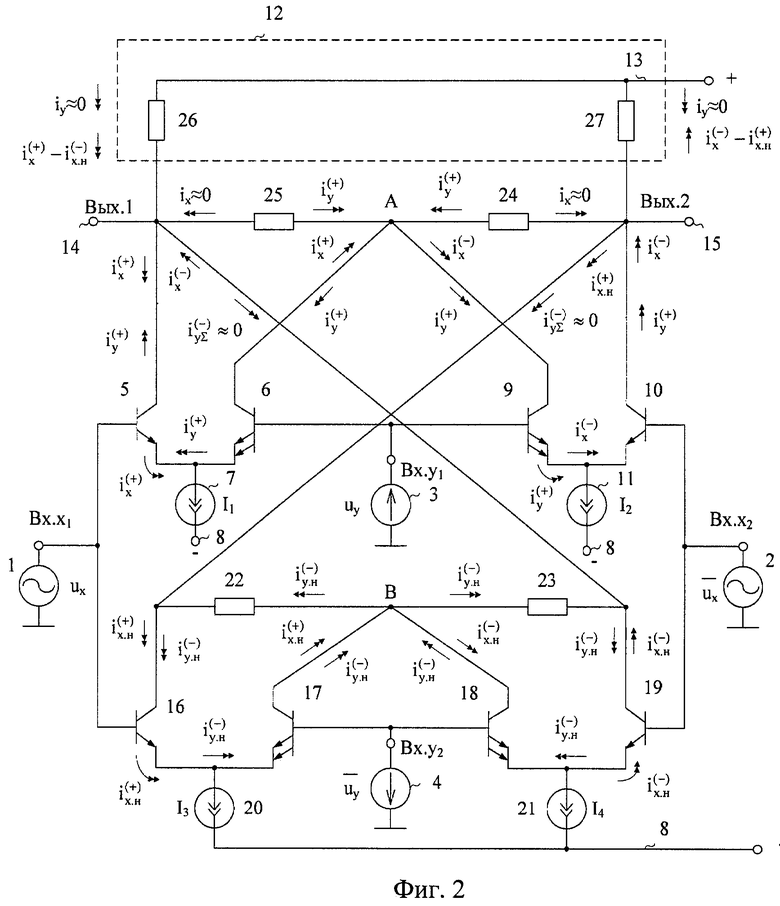

На фиг.1 показана схема АПН-прототипа, а на фиг.2 - схема заявляемого АПН в соответствии с п.1, п.2, п.3 и п.4 формулы изобретения. Схема фиг.3 соответствует п.5 формулы изобретения.

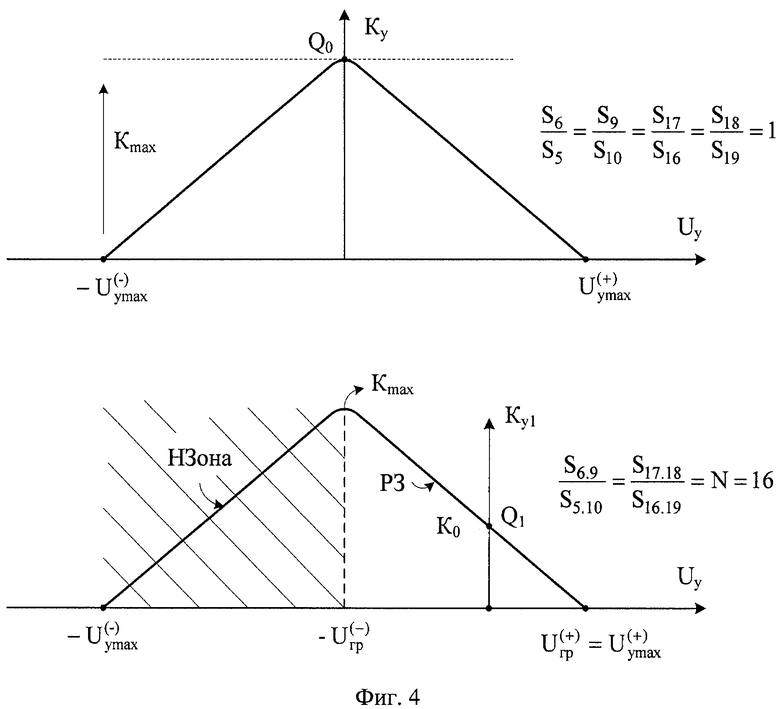

Графики фиг.4 поясняют работу верхнего (транзисторы 5, 6, 9, 10) и нижнего (транзисторы 16, 17, 18, 19) каналов усиления при разных значениях коэффициента N, характеризующего отношение площадей эмиттерных переходов транзисторов 6, 9 и 17, 18 к площадям эмиттерных переходов транзисторов 5, 10 и 16, 19.

Заявляемый АПН фиг.2 содержит первый 1 (ux) и второй 2 ( ) противофазные источники входного напряжения канала «X», первый 3 (uу) и второй 4

) противофазные источники входного напряжения канала «X», первый 3 (uу) и второй 4  противофазные источники входного напряжения канала «Y», первый 5 и второй 6 входные транзисторы, эмиттеры которых объединены и подключены к первому 7 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником напряжения питания, третий 9 и четвертый 10 входные транзисторы, эмиттеры которых объединены и подключены ко второму 11 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником питания, цепь нагрузки 12, связанную со вторым 13 источником питания, а также первым 14 и вторым 15 выходами устройства, коллектор первого 5 входного транзистора подключен к первому 14 выходу устройства, коллектор четвертого 10 входного транзистора соединен со вторым 15 выходом устройства, причем базы второго 6 и третьего 9 входных транзисторов объединены, а база первого 5 входного транзистора соединена с первым 1 (ux) источником входного напряжения канала «X». В схему введены пятый 16, шестой 17, седьмой 18 и восьмой 19 входные транзисторы, эмиттеры пятого 16 и шестого 17 входных транзисторов через третий 20 токостабилизирующий двухполюсник связаны с первым 8 источником питания, эмиттеры седьмого 18 и восьмого 19 входных транзисторов через четвертый 21 токостабилизирующий двухполюсник соединены с первым 8 источником питания, базы второго 6 и третьего 9 входных транзисторов подключены к первому 3 источнику входного напряжения uу канала «Y», базы шестого 17 и седьмого 18 входных транзисторов объединены и подключены ко второму 4 (

противофазные источники входного напряжения канала «Y», первый 5 и второй 6 входные транзисторы, эмиттеры которых объединены и подключены к первому 7 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником напряжения питания, третий 9 и четвертый 10 входные транзисторы, эмиттеры которых объединены и подключены ко второму 11 токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником питания, цепь нагрузки 12, связанную со вторым 13 источником питания, а также первым 14 и вторым 15 выходами устройства, коллектор первого 5 входного транзистора подключен к первому 14 выходу устройства, коллектор четвертого 10 входного транзистора соединен со вторым 15 выходом устройства, причем базы второго 6 и третьего 9 входных транзисторов объединены, а база первого 5 входного транзистора соединена с первым 1 (ux) источником входного напряжения канала «X». В схему введены пятый 16, шестой 17, седьмой 18 и восьмой 19 входные транзисторы, эмиттеры пятого 16 и шестого 17 входных транзисторов через третий 20 токостабилизирующий двухполюсник связаны с первым 8 источником питания, эмиттеры седьмого 18 и восьмого 19 входных транзисторов через четвертый 21 токостабилизирующий двухполюсник соединены с первым 8 источником питания, базы второго 6 и третьего 9 входных транзисторов подключены к первому 3 источнику входного напряжения uу канала «Y», базы шестого 17 и седьмого 18 входных транзисторов объединены и подключены ко второму 4 ( ) источнику противофазного входного напряжения канала «Y», база пятого 16 входного транзистора подключена к базе первого 5 входного транзистора, база восьмого 19 входного транзистора соединена с базой четвертого 10 входного транзистора и вторым 2

) источнику противофазного входного напряжения канала «Y», база пятого 16 входного транзистора подключена к базе первого 5 входного транзистора, база восьмого 19 входного транзистора соединена с базой четвертого 10 входного транзистора и вторым 2  источником противофазного входного напряжения канала «X», коллектор пятого 16 входного транзистора подключен ко второму 15 выходу устройства, коллектор восьмого 19 входного транзистора соединен с первым 14 выходом устройства, общий узел объединенных коллекторов шестого 17 и восьмого 18 входных транзисторов связан через первый 22 дополнительный резистор со вторым 15 выходом устройства, а через второй 23 дополнительный резистор соединен с первым 14 выходом устройства, общий узел объединенных коллекторов второго 6 и третьего 9 входных транзисторов через третий 24 дополнительный резистор соединен со втором 15 выходом устройства, а через четвертый 25 дополнительный резистор соединен с первым 14 выходом устройства. Цепь нагрузки 12 реализована на основе резисторов 26 и 27.

источником противофазного входного напряжения канала «X», коллектор пятого 16 входного транзистора подключен ко второму 15 выходу устройства, коллектор восьмого 19 входного транзистора соединен с первым 14 выходом устройства, общий узел объединенных коллекторов шестого 17 и восьмого 18 входных транзисторов связан через первый 22 дополнительный резистор со вторым 15 выходом устройства, а через второй 23 дополнительный резистор соединен с первым 14 выходом устройства, общий узел объединенных коллекторов второго 6 и третьего 9 входных транзисторов через третий 24 дополнительный резистор соединен со втором 15 выходом устройства, а через четвертый 25 дополнительный резистор соединен с первым 14 выходом устройства. Цепь нагрузки 12 реализована на основе резисторов 26 и 27.

Кроме этого, в схеме фиг.2, в соответствии с п.2 формулы изобретения, площади эмиттерных p-n переходов второго 6, третьего 9, шестого 17 и седьмого 18 входных транзисторов в N>2 раз больше площадей эмиттерных p-n переходов первого 5, четвертого 10, пятого 16 и восьмого 19 входных транзисторов.

Причем, в соответствии с п.3 формулы изобретения, отношение площадей второго 6, третьего 9, шестого 17 и седьмого 18 входных транзисторов к площадям первого 5, четвертого 10, пятого 16 и восьмого 19 входных транзисторов равно 16 единицам (N=16).

В соответствии с п.4 формулы изобретения, в качестве первого 7, второго 11, третьего 20 и четвертого 21 токостабилизирующих двухполюсников могут использоваться резисторы.

В схеме фиг.3, в соответствии с п.5 формулы изобретения, общий узел объединенных коллекторов второго 6 и третьего 9, а также общий узел объединенных коллекторов шестого 17 и седьмого 18 входных транзисторов соединены со вторым 13 источником питания через первый 28 и второй 29 вспомогательные двухполюсники.

Рассмотрим работу АПН фиг.2.

Статический режим по току входных транзисторов 5, 6, 9. 10 (верхний канал усиления) и 16, 17, 18 и 19 (нижний канал усиления) устанавливается токостабилизирующими двухполюсниками 7, 11, 20 и 21. В частном случае данные двухполюсники могут быть резисторами. В схемах АПН, имеющих напряжения первого 8 и второго 13 источников питания более 1,5÷1,6 В, в качестве этих токостабилизирующих двухполюсников можно использовать классические транзисторные стабилизаторы тока или токовые зеркала, описанные в технической литературе.

Напряжение на выходах 14 и 15 АНН фиг.2 зависят от токов, протекающих в резисторах нагрузки 26 и 27. В свою очередь переменные токи через эти резисторы формируются входными транзисторами 5, 6, 9, 10 (верхний канал усиления) и входными транзисторами 16, 17, 18 и 19 (нижний канал усиления). Причем эти токи имеют несколько составляющих:

,

,  - переменные токи, пропорциональные ux, формируемые верхним каналом усиления на входных транзисторах 5, 6, 9, 10;

- переменные токи, пропорциональные ux, формируемые верхним каналом усиления на входных транзисторах 5, 6, 9, 10;

,

,  - переменные токи, пропорциональные ux, формируемые нижним каналом усиления на входных транзисторах 16, 17, 18, 19;

- переменные токи, пропорциональные ux, формируемые нижним каналом усиления на входных транзисторах 16, 17, 18, 19;

- переменные токи, зависящие от сигнала управления uу транзисторами верхнего канала усиления (элементы 5, 6, 9, 10);

- переменные токи, зависящие от сигнала управления uу транзисторами верхнего канала усиления (элементы 5, 6, 9, 10);

- переменные токи, зависящие от сигнала управления uу транзисторами нижнего канала усиления (элементы 16, 17, 18, 19).

- переменные токи, зависящие от сигнала управления uу транзисторами нижнего канала усиления (элементы 16, 17, 18, 19).

Численные значения токов  ,

,  ,

,  ,

,  определяются сопротивлениями эмиттерных переходов соответствующих транзисторов, которые управляются напряжениями uу и

определяются сопротивлениями эмиттерных переходов соответствующих транзисторов, которые управляются напряжениями uу и  . При этом увеличение положительного напряжения источника 3 входного напряжения канала «Y» uу вызывает уменьшение коэффициентов передачи сигналов ux (1) и

. При этом увеличение положительного напряжения источника 3 входного напряжения канала «Y» uу вызывает уменьшение коэффициентов передачи сигналов ux (1) и  (2) со входов Bx.x1 и Вх.x2 канала «X» через входные транзисторы 5, 6, 9, 10 (верхний канал усиления) в цепь нагрузки (фиг.4), а увеличение отрицательного напряжения источника сигнала (4)

(2) со входов Bx.x1 и Вх.x2 канала «X» через входные транзисторы 5, 6, 9, 10 (верхний канал усиления) в цепь нагрузки (фиг.4), а увеличение отрицательного напряжения источника сигнала (4)  приводит к увеличению противофазной передачи

приводит к увеличению противофазной передачи  (1) и (их) (2) через транзисторы 16, 17, 18, 19 в цепь нагрузки (12) по нижнему каналу усиления (фиг.4). Если

(1) и (их) (2) через транзисторы 16, 17, 18, 19 в цепь нагрузки (12) по нижнему каналу усиления (фиг.4). Если  , то передача ux и

, то передача ux и  на выход будет близка к нулю.

на выход будет близка к нулю.

Для расширения рабочего диапазона изменения ux и uу следует использовать предварительное логарифмирование этих сигналов, которое применяется в традиционных схемах перемножителей на основе ячейки Джильберта.

Первая существенная особенность заявляемого устройства состоит в том, что площади эмиттерных переходов входных транзисторов 6, 9, 17 и 19 в N-раз превышают площади эмиттерных переходов входных транзисторов 5, 10, 16, 20. При N=16 и uу=0 коэффициенты передачи ux и uу в цепь нагрузки через транзисторы 5, 6, 9, 10 (верхний канал) и транзисторы 16, 17, 19, 20 (нижний канал) одинаковы и составляют, примерно, половину от максимального значения коэффициентов передачи по этим каналам. Если N≠16, то коэффициенты передачи этих каналов при uу=0 оказываются неодинаковы, что приводит к несимметрии характеристики управления и снижению допустимых амплитуд перемножаемых напряжений. При N=1, также как и при N>>1, схема фиг.2 теряет свойства перемножителя напряжений ux и uу. Таким образом, следует подчеркнуть, что оптимальная работоспособность схемы фиг.2 обеспечивается в том случае, когда N≈16.

Вторая существенная особенность схемы фиг.2, обязательная для любых перемножителей, состоит в том, что передача напряжений источников 3 и 4 uу и  в цепь нагрузки 12 близка к нулю. То есть, сигнал uу подавляется в заявляемом устройстве, причем это подавление обеспечивается в верхнем канале (транзисторы 5, 6, 9, 10) независимо от подавления в нижнем канале (транзисторы 16, 17, 18, 19). Данное свойство схемы допускает некоторую асимметрию амплитуд uу и

в цепь нагрузки 12 близка к нулю. То есть, сигнал uу подавляется в заявляемом устройстве, причем это подавление обеспечивается в верхнем канале (транзисторы 5, 6, 9, 10) независимо от подавления в нижнем канале (транзисторы 16, 17, 18, 19). Данное свойство схемы допускает некоторую асимметрию амплитуд uу и  без существенного ухудшения точности перемножения.

без существенного ухудшения точности перемножения.

Спектр выходных сигналов при перемножении ux и uу с частотой 1 ГГц и 10 мГц показывает, что в выходном сигнале практически отсутствуют первые гармоники входных сигналов fx и fy. Данное свойство характерно для перемножителей напряжения.

Анализ предельных значений минимального напряжения питания  показывает, что при малых амплитудах выходного напряжения в АПН фиг.2

показывает, что при малых амплитудах выходного напряжения в АПН фиг.2  напряжения

напряжения  . Отрицательное напряжение питания

. Отрицательное напряжение питания  при использовании известных способов стабилизации может принимать значение

при использовании известных способов стабилизации может принимать значение  . Таким образом, общее напряжение питания АПН фиг.2

. Таким образом, общее напряжение питания АПН фиг.2  , что недостижимо в АПН-прототипе.

, что недостижимо в АПН-прототипе.

Замечательная особенность схемы фиг.3 состоит в следующем.

Во-первых, введение резисторов 25, 24 и 22, 23 позволяет «изолировать» выходы АПН 14 и 15 от емкости на подложку транзисторов 6, 9 и 17, 18, что расширяет частотный диапазон АПН по каналу «X».

Во-вторых, статический ток, протекающий в резисторах нагрузки 26 и 27, равен сумме коллекторных токов только двух транзисторов, что позволяет при низковольтном питании увеличить сопротивления этих резисторов (26 и 27) и получить более высокое усиление в АПН. За счет оптимального выбора тока двухполюсников 28 и 29 можно обеспечить симметрирование статического режима по напряжению коллектор-база транзисторов 5, 6, 9, 10, 16, 17, 18 и 19, что позволяет выбрать сопротивления резисторов 25 и 24, 22 и 23 на уровне сопротивлений резисторов 26 и 27 и тем самым повысить Ку.

Таким образом, предлагаемое устройство выполняет функции перемножителя сигналов, может работать при малых напряжениях питания, обеспечивает более широкий диапазон рабочих частот и не требует входных согласующих статический режим цепей, отрицательно влияющих на стабильность нуля АПН.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 7024448 fig.2.

2. Патент US 5157350 fig.2.

3. Патент US 5877974 fig.4.

4. Патент US 5886916 fig.2.

5. Патент US 3689752.

6. Патент US 5684419 fig.3.

7. Патент US 4458211.

8. Патент US 4572975.

9. Патент US 5889425.

10. Патент US 5331289 fig.1.

11. Патент US 5914639 fig.4.

12. Патент US 6111463 fig.11.

13. Патент US 5886560 fig.1.

14. Патентная заявка US 2006/0232334 fig.1.

15. Патент JP 53-25780 кл. 98(5).

16. Патент ЕР 917285 fig.1.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419188C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2010 |

|

RU2419189C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2010 |

|

RU2419145C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2396595C2 |

| НИЗКОВОЛЬТНЫЙ АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2009 |

|

RU2394358C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2421883C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2011 |

|

RU2439785C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2383054C1 |

| ДВУХКАНАЛЬНЫЙ УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2009 |

|

RU2394364C1 |

| УПРАВЛЯЕМЫЙ УСИЛИТЕЛЬ И АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ СИГНАЛОВ НА ЕГО ОСНОВЕ | 2009 |

|

RU2390922C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в устройствах автоматической регулировки усиления, фазовых детекторах и модуляторах, а также в системах фазовой автоподстройки и умножения частоты или в качестве усилителя, коэффициент передачи по напряжению которого зависит от уровня сигнала управления. Технический результат: снижение напряжения питания до ±0,9÷1 В. Аналоговый перемножитель напряжений содержит первый (1) (ux) и второй (2)  противофазные источники входного напряжения канала «X», первый (3) (uy) и второй (4)

противофазные источники входного напряжения канала «X», первый (3) (uy) и второй (4)  противофазные источники входного напряжения канала «Y», первый (5) и второй (6) входные транзисторы, эмиттеры которых объединены и подключены к первому (7) токостабилизирующему двухполюснику, связанному вторым выводом с первым (8) источником напряжения питания, третий (9) и четвертый (10) входные транзисторы, эмиттеры которых объединены и подключены ко второму (11) токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником питания, цепь нагрузки (12), связанную со вторым (13) источником питания, а также первым (14) и вторым (15) выходами устройства, коллектор первого (5) входного транзистора подключен к первому (14) выходу устройства, коллектор четвертого (10) входного транзистора соединен со вторым (15) выходом устройства, причем базы второго (6) и третьего (9) входных транзисторов объединены, а база первого (5) входного транзистора соединена с первым (1) (их) источником входного напряжения канала «X». В схему введены пятый (16), шестой (17), седьмой (18) и восьмой (19) входные транзисторы, эмиттеры пятого (16) и шестого (17) входных транзисторов через третий (20) токостабилизирующий двухполюсник связаны с первым (8) источником питания, эмиттеры седьмого (18) и восьмого (19) входных транзисторов через четвертый (21) токостабилизирующий двухполюсник соединены с первым (8) источником питания, базы второго (6) и третьего (9) входных транзисторов подключены к первому (3) источнику входного напряжения uy канала «Y», базы шестого (17) и седьмого (18) входных транзисторов объединены и подключены ко второму (4)

противофазные источники входного напряжения канала «Y», первый (5) и второй (6) входные транзисторы, эмиттеры которых объединены и подключены к первому (7) токостабилизирующему двухполюснику, связанному вторым выводом с первым (8) источником напряжения питания, третий (9) и четвертый (10) входные транзисторы, эмиттеры которых объединены и подключены ко второму (11) токостабилизирующему двухполюснику, связанному вторым выводом с первым 8 источником питания, цепь нагрузки (12), связанную со вторым (13) источником питания, а также первым (14) и вторым (15) выходами устройства, коллектор первого (5) входного транзистора подключен к первому (14) выходу устройства, коллектор четвертого (10) входного транзистора соединен со вторым (15) выходом устройства, причем базы второго (6) и третьего (9) входных транзисторов объединены, а база первого (5) входного транзистора соединена с первым (1) (их) источником входного напряжения канала «X». В схему введены пятый (16), шестой (17), седьмой (18) и восьмой (19) входные транзисторы, эмиттеры пятого (16) и шестого (17) входных транзисторов через третий (20) токостабилизирующий двухполюсник связаны с первым (8) источником питания, эмиттеры седьмого (18) и восьмого (19) входных транзисторов через четвертый (21) токостабилизирующий двухполюсник соединены с первым (8) источником питания, базы второго (6) и третьего (9) входных транзисторов подключены к первому (3) источнику входного напряжения uy канала «Y», базы шестого (17) и седьмого (18) входных транзисторов объединены и подключены ко второму (4)  источнику противофазного входного напряжения канала «Y», база пятого (16) входного транзистора подключена к базе первого (5) входного транзистора, база восьмого (19) входного транзистора соединена с базой четвертого (10) входного транзистора и вторым (2)

источнику противофазного входного напряжения канала «Y», база пятого (16) входного транзистора подключена к базе первого (5) входного транзистора, база восьмого (19) входного транзистора соединена с базой четвертого (10) входного транзистора и вторым (2)  источником противофазного входного напряжения канала «X», коллектор пятого (16) входного транзистора подключен ко второму (15) выходу устройства, коллектор восьмого (19) входного транзистора соединен с первым (14) выходом устройства, общий узел объединенных коллекторов шестого (17) и восьмого (18) входных транзисторов связан через первый (22) дополнительный резистор со вторым (15) выходом устройства, а через второй (23) дополнительный резистор соединен с первым (14) выходом устройства, общий узел объединенных коллекторов второго (6) и третьего (9) входных транзисторов через третий (24) дополнительный резистор соединен со втором (15) выходом устройства, а через четвертый (25) дополнительный резистор соединен с первым (14) выходом устройства. 4 з.п. ф-лы, 4 ил.

источником противофазного входного напряжения канала «X», коллектор пятого (16) входного транзистора подключен ко второму (15) выходу устройства, коллектор восьмого (19) входного транзистора соединен с первым (14) выходом устройства, общий узел объединенных коллекторов шестого (17) и восьмого (18) входных транзисторов связан через первый (22) дополнительный резистор со вторым (15) выходом устройства, а через второй (23) дополнительный резистор соединен с первым (14) выходом устройства, общий узел объединенных коллекторов второго (6) и третьего (9) входных транзисторов через третий (24) дополнительный резистор соединен со втором (15) выходом устройства, а через четвертый (25) дополнительный резистор соединен с первым (14) выходом устройства. 4 з.п. ф-лы, 4 ил.

1. Аналоговый перемножитель напряжений с низковольтным питанием, содержащий первый (1) (ux) и второй (2)  противофазные источники входного напряжения канала «X», первый (3) (uy) и второй (4) (uy) противофазные источники входного напряжения канала «Y», первый (5) и второй (6) входные транзисторы, эмиттеры которых объединены и подключены к первому (7) токостабилизирующему двухполюснику, связанному вторым выводом с первым (8) источником напряжения питания, третий (9) и четвертый (10) входные транзисторы, эмиттеры которых объединены и подключены ко второму (11) токостабилизирующему двухполюснику, связанному вторым выводом с первым (8) источником питания, цепь нагрузки (12), связанную со вторым (13) источником питания, а также первым (14) и вторым (15) выходами устройства, коллектор первого (5) входного транзистора подключен к первому (14) выходу устройства, коллектор четвертого (10) входного транзистора соединен со вторым (15) выходом устройства, причем базы второго (6) и третьего (9) входных транзисторов объединены, а база первого (5) входного транзистора соединена с первым (1) (ux) источником входного напряжения канала «X», отличающийся тем, что в схему введены пятый (16), шестой (17), седьмой (18) и восьмой (19) входные транзисторы, эмиттеры пятого (16) и шестого (17) входных транзисторов через третий (20) токостабилизирующий двухполюсник связаны с первым (8) источником питания, эмиттеры седьмого (18) и восьмого (19) входных транзисторов через четвертый (21) токостабилизирующий двухполюсник соединены с первым (8) источником питания, базы второго (6) и третьего (9) входных транзисторов подключены к первому (3) источнику входного напряжения uy канала «Y», базы шестого (17) и седьмого (18) входных транзисторов объединены и подключены ко второму (4)

противофазные источники входного напряжения канала «X», первый (3) (uy) и второй (4) (uy) противофазные источники входного напряжения канала «Y», первый (5) и второй (6) входные транзисторы, эмиттеры которых объединены и подключены к первому (7) токостабилизирующему двухполюснику, связанному вторым выводом с первым (8) источником напряжения питания, третий (9) и четвертый (10) входные транзисторы, эмиттеры которых объединены и подключены ко второму (11) токостабилизирующему двухполюснику, связанному вторым выводом с первым (8) источником питания, цепь нагрузки (12), связанную со вторым (13) источником питания, а также первым (14) и вторым (15) выходами устройства, коллектор первого (5) входного транзистора подключен к первому (14) выходу устройства, коллектор четвертого (10) входного транзистора соединен со вторым (15) выходом устройства, причем базы второго (6) и третьего (9) входных транзисторов объединены, а база первого (5) входного транзистора соединена с первым (1) (ux) источником входного напряжения канала «X», отличающийся тем, что в схему введены пятый (16), шестой (17), седьмой (18) и восьмой (19) входные транзисторы, эмиттеры пятого (16) и шестого (17) входных транзисторов через третий (20) токостабилизирующий двухполюсник связаны с первым (8) источником питания, эмиттеры седьмого (18) и восьмого (19) входных транзисторов через четвертый (21) токостабилизирующий двухполюсник соединены с первым (8) источником питания, базы второго (6) и третьего (9) входных транзисторов подключены к первому (3) источнику входного напряжения uy канала «Y», базы шестого (17) и седьмого (18) входных транзисторов объединены и подключены ко второму (4)  источнику противофазного входного напряжения канала «Y», база пятого (16) входного транзистора подключена к базе первого (5) входного транзистора, база восьмого (19) входного транзистора соединена с базой четвертого (10) входного транзистора и вторым (2)

источнику противофазного входного напряжения канала «Y», база пятого (16) входного транзистора подключена к базе первого (5) входного транзистора, база восьмого (19) входного транзистора соединена с базой четвертого (10) входного транзистора и вторым (2)  источником противофазного входного напряжения канала «X», коллектор пятого (16) входного транзистора подключен ко второму (15) выходу устройства, коллектор восьмого (19) входного транзистора соединен с первым (14) выходом устройства, общий узел объединенных коллекторов шестого (17) и восьмого (18) входных транзисторов связан через первый (22) дополнительный резистор со вторым (15) выходом устройства, а через второй (23) дополнительный резистор соединен с первым (14) выходом устройства, общий узел объединенных коллекторов второго (6) и третьего (9) входных транзисторов через третий (24) дополнительный резистор соединен со втором (15) выходом устройства, а через четвертый (25) дополнительный резистор соединен с первым (14) выходом устройства.

источником противофазного входного напряжения канала «X», коллектор пятого (16) входного транзистора подключен ко второму (15) выходу устройства, коллектор восьмого (19) входного транзистора соединен с первым (14) выходом устройства, общий узел объединенных коллекторов шестого (17) и восьмого (18) входных транзисторов связан через первый (22) дополнительный резистор со вторым (15) выходом устройства, а через второй (23) дополнительный резистор соединен с первым (14) выходом устройства, общий узел объединенных коллекторов второго (6) и третьего (9) входных транзисторов через третий (24) дополнительный резистор соединен со втором (15) выходом устройства, а через четвертый (25) дополнительный резистор соединен с первым (14) выходом устройства.

2. Аналоговый перемножитель напряжений с низковольтным питанием по п.1, отличающийся тем, что площади эмиттерных p-n переходов второго (6), третьего (9), шестого (17) и седьмого (18) входных транзисторов в N≥2 раз больше площадей эмиттерных p-n переходов первого (5), четвертого (10), пятого (16) и восьмого (19) входных транзисторов.

3. Аналоговый перемножитель напряжений с низковольтным питанием по п.1, отличающийся тем, что отношение площадей второго (6), третьего (9), шестого (17) и седьмого (18) входных транзисторов к площадям первого (5), четвертого (10), пятого (16) и восьмого (19) входных транзисторов равно (16) единицам (N=16).

4. Аналоговый перемножитель напряжений с низковольтным питанием по п.1, отличающийся тем, что в качестве первого (7), второго (11), третьего (20) и четвертого (21) токостабилизирующих двухполюсников используются резисторы.

5. Аналоговый перемножитель напряжений с низковольтным питанием по п.1, отличающийся тем, что общий узел объединенных коллекторов второго (6) и третьего (9), а также общий узел объединенных коллекторов шестого (17) и седьмого (18) входных транзисторов соединены со вторым (13) источником питания через первый (28) и второй (29) вспомогательные двухполюсники.

| US 7024448 В2, 04.04.2006 | |||

| Аналоговый перемножитель сигналов | 1989 |

|

SU1626257A1 |

| Перекатываемый затвор для водоемов | 1922 |

|

SU2001A1 |

| US 3689752 А, 05.09.1972. | |||

Авторы

Даты

2011-05-20—Публикация

2010-02-15—Подача