ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Изобретение относится к способу передачи и приема сигнала и устройству для передачи и приема сигнала, более конкретно к способу передачи и приема сигнала и устройству для передачи и приема сигнала, которые способны повысить эффективность передачи данных.

УРОВЕНЬ ТЕХНИКИ

Поскольку была разработана технология цифрового вещания, пользователи стали принимать движущееся изображение высокой четкости (ВЧ, HD). При постоянном развитии алгоритма сжатия и высокоэффективных аппаратных средств в будущем пользователям будет обеспечиваться улучшенная среда. Система цифрового телевидения (ЦТВ, DTV) может принимать сигнал цифрового вещания и предоставлять разнообразие дополнительных услуг пользователям, а также видеосигнал и звуковой сигнал.

При разработке технологии цифрового вещания потребность в услуге, такой как передача видеосигнала и звукового сигнала, возрастает, и объем данных, требуемых пользователем, или количество вещательных каналов постепенно увеличивается.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Техническая задача изобретения

Соответственно настоящее изобретение касается способа передачи и приема сигнала и устройства для передачи и приема сигнала, которые по существу устраняют одну или несколько проблем, обусловленных ограничениями и недостатками уровня техники.

Задача настоящего изобретения состоит в том, чтобы обеспечить способ для передачи и приема сигнала и устройство для передачи и приема сигнала, которые способны повысить эффективность передачи данных.

Другая задача настоящего изобретения состоит в том, чтобы обеспечить способ передачи и приема сигнала и устройство для передачи и приема сигнала, которые способны повысить способность исправления ошибок для битов, составляющих структуру услуги.

Решение технической задачи изобретения

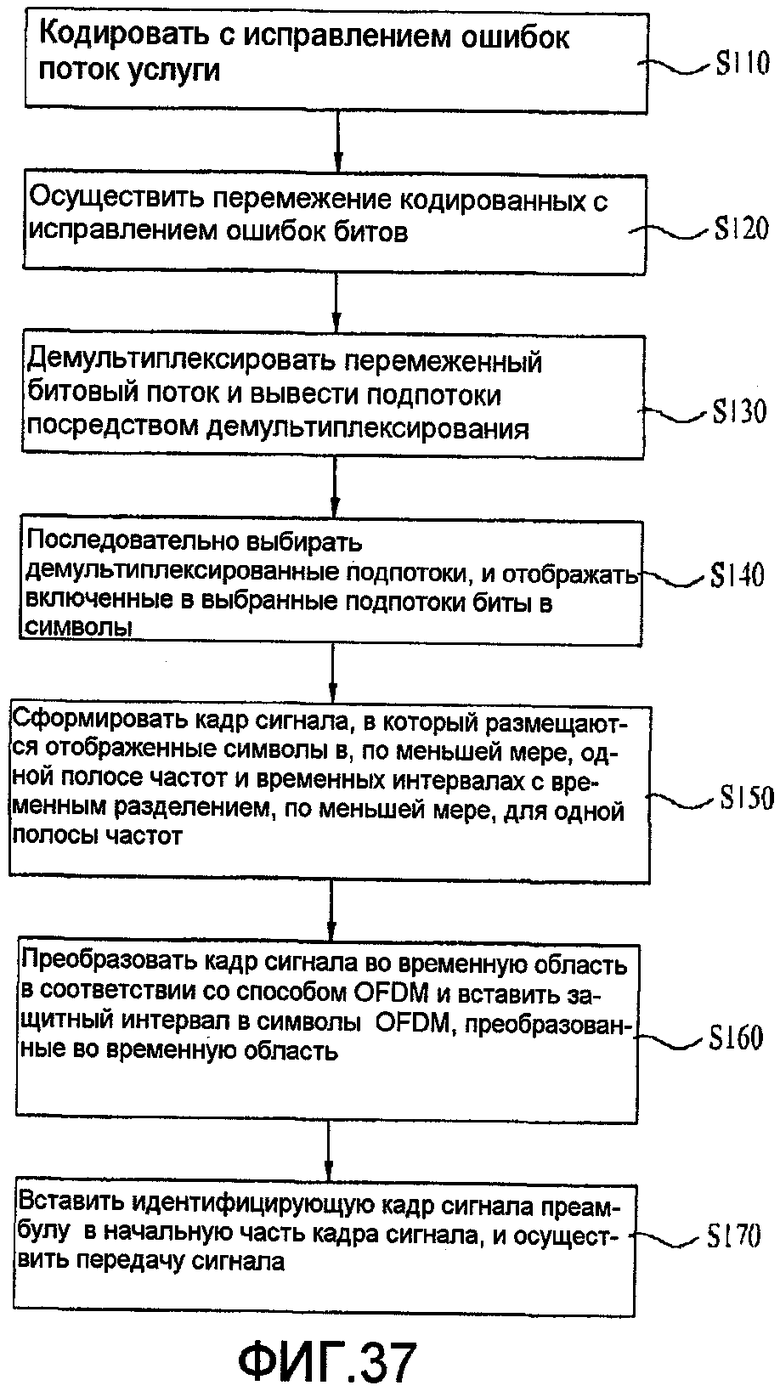

Для выполнения этих задач и получения других преимуществ и в соответствии с целью изобретения, как осуществлено и в широком смысле описано в документе, способ для передачи сигнала включает в себя этапы кодирования с исправлением ошибок потока услуги и перемежения битового потока в кодированном с исправлением ошибок потоке услуги, демультиплексирования перемеженного битового потока и вывода подпотоков посредством демультиплексирования, выбора битов, включенных в демультиплексированные подпотоки, и отображения выбранных битов на символы, формирования кадра сигнала, в котором отображенные символы разделены и размещены, по меньшей мере, в одной полосе частот и во временных интервалах с временным разделением, по меньшей мере, для одной полосы частот и модулирования кадра сигнала способом мультиплексирования с ортогональным частотным разделением (OFDM) и передачи модулированного сигнала.

На этапе демультиплексирования перемеженного битового потока этап демультиплексирования может изменять порядок выбранных битов. Порядок битов, отображенных в символы, может изменяться в соответствии с кодовой скоростью кодирования с исправлением ошибок или/и способом отображения символа.

В другом аспекте настоящего изобретения способ для приема сигнала включает в себя этапы приема сигнала из первой полосы частот в кадре сигнала, включающего в себя, по меньшей мере, одну полосу частот, демодулирования принятого сигнала способом мультиплексирования с ортогональным частотным разделением (OFDM) и анализа кадра сигнала, извлечения потока символов потока услуги из, по меньшей мере, одной полосы частот, включенной в проанализированный кадр сигнала, обратного отображения символов, включенных в поток символов, и вывода обратно отображенных символов в подпотоки, мультиплексирования выводимых подпотоков и вывода одного битового потока с использованием мультиплексированных подпотоков и обратного перемежения и декодирования с исправлением ошибок выводимого битового потока.

Этап вывода битового потока может включать в себя этапы выбора битов, включенных в подпотоки, и вывода одного битового потока. Порядок выбора битов может изменяться в соответствии с кодовой скоростью кодирования с исправлением ошибок, соответствующего декодированию с исправлением ошибок или/и способу обратного отображения символов.

В другом аспекте настоящего изобретения устройство для передачи сигнала включает в себя кодер с исправлением ошибок для кодирования с исправлением ошибок потока услуги, перемежитель битов, осуществляющий перемежение битового потока в кодированном с исправлением ошибок потоке услуги, модуль отображения символов, предназначенный для демультиплексирования перемеженного битового потока, для вывода подпотоков посредством демультиплексирования, для выбора битов, включенных в демультиплексированные подпотоки, и для отображения выбранных битов в символы, формирователь кадра сигнала, предназначенный для формирования кадра сигнала, в котором отображенные символы разделены и размещены, по меньшей мере, в одной полосе частот и временных интервалах с временным разделением, по меньшей мере, для одной полосы частот, модулятор для модулирования кадра сигнала способом мультиплексирования с ортогональным частотным разделением (OFDM) и передатчик для осуществления передачи модулированного сигнала.

Перемежитель битов выполнен с возможностью перемежения битового потока путем сохранения кодированных с исправлением ошибок битов в машинной памяти и их считывания в различных направлениях.

Модуль отображения символов может включать в себя демультиплексор для демультиплексирования перемеженного битового потока в подпотоки в соответствии с кодовой скоростью кодирования с исправлением ошибок или/и способом отображения символа и модуль отображения, чтобы отображать демультиплексированные подпотоки на символы.

В другом аспекте настоящего изобретения устройство для приема сигнала включает в себя приемник, осуществляющий прием сигнала из первой полосы частот в кадре сигнала, содержащий приемник для приема сигнала из первой полосы частот в кадре сигнала, включающего в себя, по меньшей мере, одну полосу частот, демодулятор для демодулирования принятого сигнала способом мультиплексирования с ортогональным частотным разделением (OFDM), анализатор кадра сигнала, предназначенный для анализа кадра сигнала демодулированного сигнала и для вывода потока символов потока услуги, по меньшей мере, из одной полосы частот, модуль обратного отображения символа, предназначенный для обратного отображения символов, включенных в поток символов, для вывода обратно отображенных символов в подпотоки, для мультиплексирования выводимых подпотоков и вывода одного битового потока с использованием мультиплексированных подпотоков, обратный перемежитель битов, предназначенный для обратного перемежения выводимого битового потока, и декодер с исправлением ошибок для декодирования с исправлением ошибок обратно перемеженного битового потока.

Модуль обратного отображения символа может включать в себя модуль обратного отображения, чтобы осуществлять обратное отображение символов в подпотоки, и мультиплексор, чтобы мультиплексировать подпотоки в соответствии с кодовой скоростью кодирования с исправлением ошибок, соответствующего декодированию с исправлением ошибок или/и способу обратного отображения символов.

Полезные эффекты изобретения

В соответствии с устройством для передачи и приема сигнала и способом передачи и приема сигнала по настоящему изобретению является возможным легко детектировать и восстанавливать передаваемый сигнал. Кроме того, является возможным улучшить рабочую характеристику передачи/приема сигнала для передающей/приемной системы.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - изображение, демонстрирующее кадр сигнала для передачи услуги;

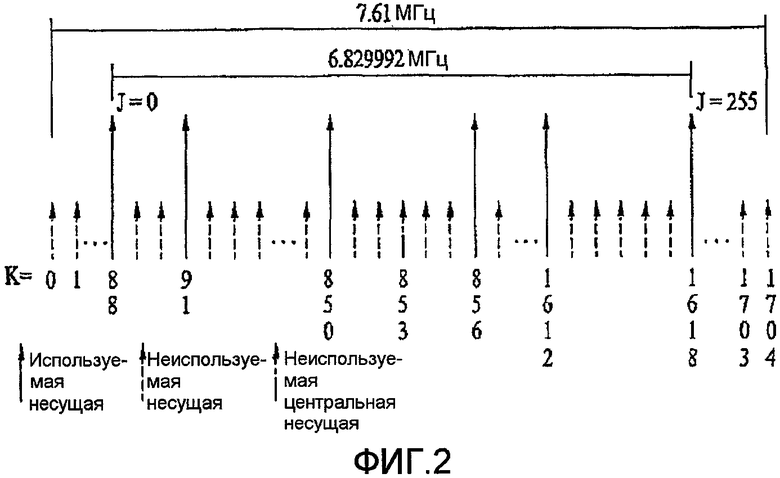

Фиг.2 - изображение, демонстрирующее структуру первого пилот-сигнала P1 кадра сигнала;

Фиг.3 - изображение, демонстрирующее окно сигнализации;

Фиг.4 - схематическое изображение, демонстрирующее вариант осуществления устройства для передачи сигнала;

Фиг.5 - изображение, демонстрирующее пример процессора 110 ввода;

Фиг.6 - изображение, демонстрирующее вариант осуществления модуля кодирования и модуляции;

Фиг.7 - изображение, демонстрирующее вариант осуществления формирователя кадра;

Фиг.8 - изображение, демонстрирующее первый пример отношения символов, когда модули 131a и 131b отображения выполняют гибридное отображение символов;

Фиг.9 - изображение, демонстрирующее второй пример отношения символов, когда модули 131a и 131b преобразования выполняют гибридное отображение символов;

Фиг.10 - изображение, демонстрирующее вариант осуществления каждого из модулей 131a и 131b отображения символов, показанных на Фиг.7;

Фиг.11 - изображение, демонстрирующее другой вариант осуществления модуля отображения символов;

Фиг.12 - изображение, демонстрирующее принцип перемежения битов перемежителями 1312a и 1312b битов по Фиг.11;

Фиг.13 - изображение, демонстрирующее первый пример ряда строк и столбцов машинной памяти перемежителей 1312a и 1312b битов в соответствии с типами модулей 1315a и 1315b преобразования символов;

Фиг.14 - изображение, демонстрирующее второй пример ряда строк и столбцов машинной памяти перемежителей 1312a и 1312b битов в соответствии с типами модулей 1315a и 1315b отображения символов;

Фиг.15 - изображение, демонстрирующее принцип демультиплексирования входных битов относительно демультиплексоров 1313a и 1313b;

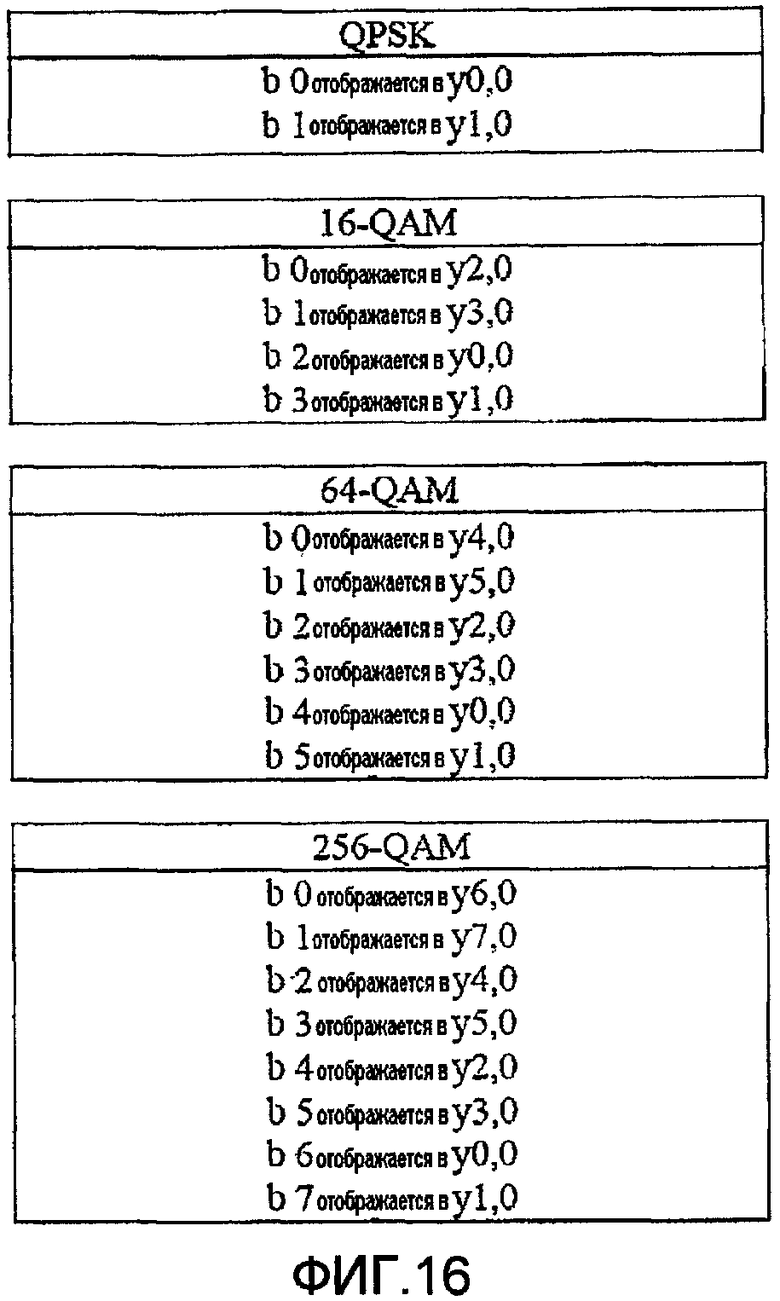

Фиг.16 - изображение, демонстрирующее вариант осуществления демультиплексирования входного потока демультиплексором;

Фиг.17 - изображение, демонстрирующее пример типа демультиплексирования в соответствии со способом отображения символа;

Фиг.18 - изображение, демонстрирующее вариант осуществления демультиплексирования входного битового потока в соответствии с типом демультиплексирования;

Фиг.19 - изображение, демонстрирующее тип демультиплексирования, который определяется в соответствии с кодовой скоростью кодирования с исправлением ошибок и способом отображения символа;

Фиг.20 - изображение, демонстрирующее пример выражения способа демультиплексирования посредством уравнения;

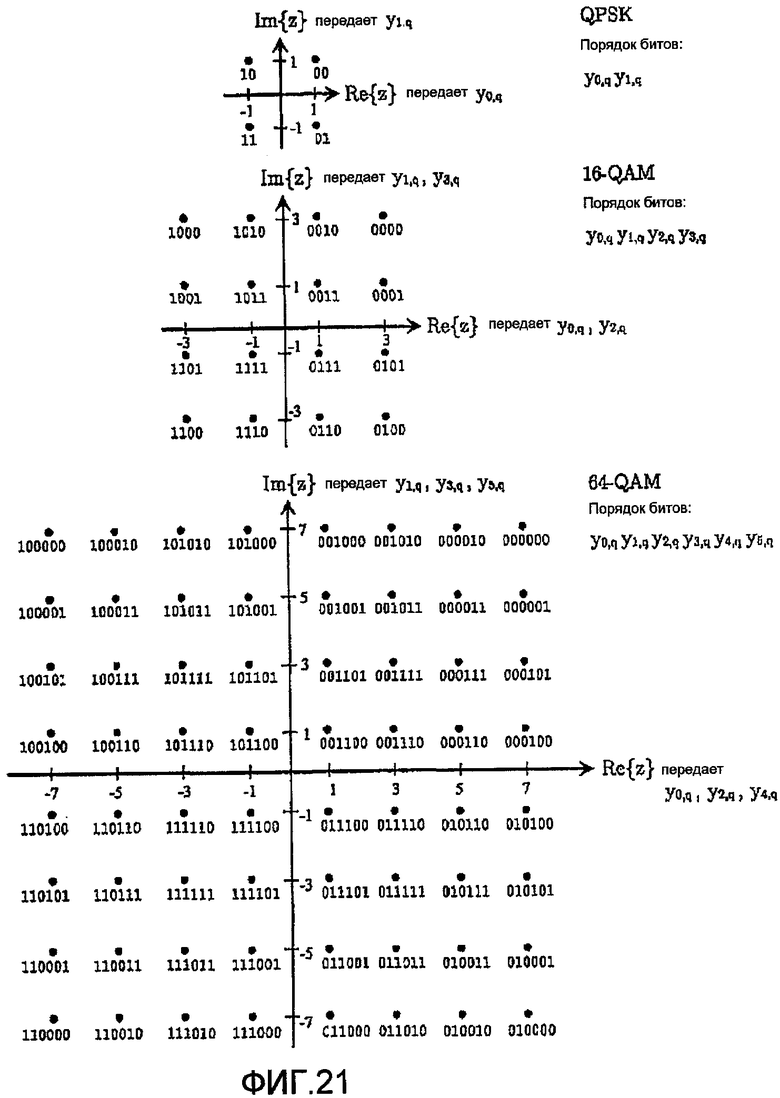

Фиг.21 - изображение, демонстрирующее пример отображения символа посредством модуля отображения символа;

Фиг.22 - изображение, демонстрирующее пример кодера сигнала многолучевого распространения;

Фиг.23 - изображение, демонстрирующее вариант осуществления модулятора;

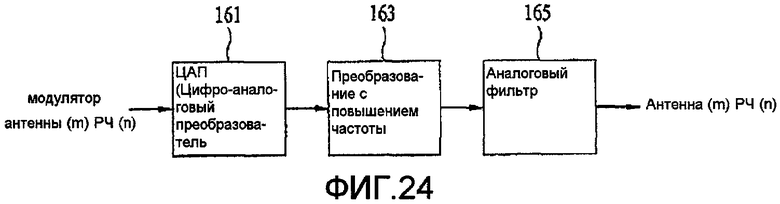

Фиг.24 - изображение, демонстрирующее вариант осуществления аналогового процессора 160;

Фиг.25 - изображение, демонстрирующее вариант осуществления устройства приема сигнала, способного принимать кадр сигнала;

Фиг.26 - изображение, демонстрирующее вариант осуществления приемника сигнала;

Фиг.27 - изображение, демонстрирующее вариант осуществления демодулятора;

Фиг.28 - изображение, демонстрирующее декодер сигнала многолучевого распространения;

Фиг.29 - изображение, демонстрирующее вариант осуществления анализатора кадра;

Фиг.30 - изображение, демонстрирующее вариант осуществления каждого из модулей 247a и 247p обратного отображения символа;

Фиг.31 - изображение, демонстрирующее другой вариант осуществления каждого из модулей 247a и 247p обратного отображения символа;

Фиг.32 - изображение, демонстрирующее вариант осуществления мультиплексирования демультиплексированного подпотока;

Фиг.33 - изображение, демонстрирующее пример модуля декодирования и демодуляции;

Фиг.34 - изображение, демонстрирующее вариант осуществления процессора вывода;

Фиг.35 - изображение, демонстрирующее другой вариант осуществления устройства передачи сигнала, предназначенного для передачи кадра сигнала;

Фиг.36 - изображение, демонстрирующее другой вариант осуществления устройства приема сигнала, предназначенного для приема кадра сигнала;

Фиг.37 - изображение, демонстрирующее вариант осуществления способа передачи сигнала;

Фиг.38 - изображение, демонстрирующее вариант осуществления способа приема сигнала.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

В нижеследующем описании термин "услуга" обозначает либо содержание вещания, которое может передаваться/приниматься устройством передачи/приема сигнала, либо предоставление содержания.

Перед описанием устройства для передачи и приема сигнала в соответствии с вариантом осуществления настоящего изобретения будет описан кадр сигнала, который передается и принимается устройством для передачи и приема сигнала в соответствии с вариантом осуществления настоящего изобретения.

На Фиг.1 показан кадр сигнала для передачи услуги в соответствии с настоящим изобретением.

Кадр сигнала, показанный на Фиг.1, показывает примерный кадр сигнала для передачи вещательной услуги, включая потоки аудио/видео (A/V). В этом случае одиночная услуга мультиплексируется во временных и частотных каналах и передается как мультиплексированная услуга. Вышеупомянутая схема передачи сигнала называется схемой частотно-временного квантования (ЧВК, TFS). По сравнению со случаем, в котором одиночная услуга передается только в одной полосе радиочастоты (РЧ, RF), устройство передачи сигнала в соответствии с настоящим изобретением передает сигнал услуги, по меньшей мере, посредством одной полосы РЧ (возможно, нескольких полос РЧ), так что оно может использовать преимущество статистического мультиплексирования, способного передавать намного больше услуг. Устройство передачи/приема сигнала передает/принимает одиночную услугу по нескольким каналам RF, так что оно может использовать преимущество частотного разнесения.

Услуги от первой до третьей (Услуги 1-3) передаются на четырех полосах РЧ (RF1-RF4). Однако это количество полос РЧ и это количество услуг были представлены только для иллюстративных целей, так что другое количество также может использоваться, если это необходимо. Два опорных сигнала (то есть первый пилот-сигнал (P1) и второй пилот-сигнал (P2)) находятся в начальной части кадра сигнала. Например, в случае полосы RF1 первый пилот-сигнал (P1) и второй пилот-сигнал (P2) находятся в начальной части кадра сигнала. Полоса RF1 включает в себя три временных интервала, связанных с Услугой 1, два временных интервала, связанных с Услугой 2, и один временной интервал, связанный с Услугой 3. Временные интервалы, связанные с другими услугами, также могут находиться в других временных интервалах (Временные интервалы 4-17), расположенных после одиночного временного интервала, связанного с Услугой 3.

Полоса RF2 включает в себя первый пилот-сигнал (P1), второй пилот-сигнал (P2) и другие временные интервалы 13-17. Кроме того, полоса RF2 включает в себя три временных интервала, связанных с Услугой 1, два временных интервала, связанных с Услугой 2, и один временной интервал, связанный с Услугой 3.

Услуги 1-3 мультиплексируются и затем передаются в полосе RF3 и RF4 в соответствии со схемой частотно-временного квантования (TFS). Схема модуляции для передачи сигнала может основываться на схеме мультиплексирования с ортогональным частотным разделением (OFDM).

В кадре сигнала индивидуальные услуги смещаются на полосы РЧ (в случае когда имеется множество полос РЧ в кадре сигнала) и по оси времени.

Если кадры сигнала, соответствующие вышеупомянутому кадру сигнала, последовательно расположены во времени, то из нескольких кадров сигнала может быть составлен суперкадр. Кадр будущего расширения также может находиться среди нескольких кадров сигнала. Если кадр будущего расширения расположен среди нескольких кадров сигнала, суперкадр может завершаться в будущем кадре расширения.

На Фиг.2 показан первый пилот-сигнал (P1), содержащийся в кадре сигнала по Фиг.1 в соответствии с настоящим изобретением.

Первый пилот-сигнал P1 и второй пилот-сигнал P2 находятся в начальной части кадра сигнала. Первый пилот-сигнал P1 модулируется согласно режиму быстрого преобразования Фурье (FFT) размером 2 кбайт и может передаваться одновременно, включая в себя при этом защитный интервал в соотношении 1/4. На Фиг.2 полоса 7,61 МГц для первого пилот-сигнала P1 включает в себя полосу 6,82992 МГц. Первый пилот-сигнал использует 256 несущих из числа 1705 активных несущих. Одна активная несущая используется для каждых 6 несущих в среднем. Интервалы несущих для данных могут неравномерно располагаться в порядке 3, 6 и 9. На Фиг.2 сплошная линия указывает положение используемой несущей, тонкий пунктир указывает положение неиспользуемой несущей, и штрихпунктирная линия указывает центральное положение неиспользуемой несущей. В первом пилот-сигнале используемая несущая может быть отображенной в символ посредством двоичной фазовой манипуляции (BPSK) и может быть модулированной псевдослучайной последовательностью битов (PRBS). Размер FFT, используемого для второго пилот-сигнала, может указываться согласно нескольким PRBS.

Устройство приема сигнала выявляет структуру пилот-сигнала и распознает частотно-временное квантование (TFS), используя выявленную структуру. Устройство приема сигнала получает размер FFT для второго пилот-сигнала, компенсирует грубый сдвиг частоты сигнала приема и входит во временную синхронизацию.

В первом пилот-сигнале могут задаваться тип передачи сигнала и параметр передачи.

Второй пилот-сигнал P2 может передаваться с размером FFT и защитным интервалом, соответствующим таковому для символа данных. Во втором пилот-сигнале одна несущая используется в качестве несущей пилот-сигнала с интервалами в три несущие. Устройство приема сигнала компенсирует тонкий сдвиг частоты синхронизации, используя второй пилот-сигнал, и выполняет точную временную синхронизацию. Второй пилот-сигнал передает информацию, соответствующую первому уровню (L1) из числа уровней Модели взаимодействия открытых систем (ВОС, OSI). Например, второй пилот-сигнал может включать в себя информацию физического параметра и структуры кадра. Второй пилот-сигнал передает значение параметра, посредством которого приемник может осуществлять доступ к потоку услуги канала физического уровня (PLP).

Информацией L1 (Уровень 1), содержащейся во втором пилот-сигнале P2, является нижеследующая.

Информация уровня-1 (L1) включает в себя указатель длины, указывающий длину данных, включая информацию L1, так что она может легко использовать каналы сигнализации Уровней 1 и 2 (L1 и L2). Информация уровня-1 (L1) включает в себя указатель частоты, длину защитного интервала, максимальное число блоков FEC (прямое исправление ошибок) для каждого кадра в связи с отдельными физическими каналами и число фактических блоков FEC, которые должны содержаться в буфере блоков FEC, связанном с текущим/предшествующим кадром в каждом физическом канале. В этом случае указатель частоты указывает информацию частоты, соответствующую каналу РЧ.

Информация уровня-1 (L1) может включать в себя различную информацию в связи с отдельными временными интервалами. Например, информация уровня-1 (L1) включает в себя число кадров, связанных с услугой, начальный адрес временного интервала с точностью несущей OFDM, содержащейся в символе OFDM, длину временного интервала, временные интервалы, соответствующие несущей OFDM, количество битов дополнения в последней несущей OFDM, служебную информацию модуляции, служебную информацию скорости передачи режима и информацию о схеме (MIMO) с многими входами и многими выходами.

Информация уровня-1 (L1) может включать в себя идентификатор (ID) сотовой ячейки, флаг для услуги, подобной услуге уведомляющих сообщений (например, аварийное сообщение), количество текущих кадров и количество дополнительных битов для будущего использования. В этом случае ID сотовой ячейки указывает область вещания, передаваемого широковещательным передатчиком.

Второй пилот-сигнал P2 приспособлен для выполнения оценки канала, чтобы декодировать символ, содержащийся в сигнале P2. Второй пилот-сигнал P2 может использоваться в качестве начального значения оценки канала для следующего символа данных. Второй пилот-сигнал P2 может также передавать информацию уровня-2 (L2). Например, второй пилот-сигнал способен описывать информацию, связанную с услугой передачи в информации уровня-2 (L2). Устройство передачи сигнала декодирует второй пилот-сигнал, так что оно может извлекать служебную информацию, содержащуюся в кадре частотно-временного квантования (TFS), и может эффективно выполнять сканирование канала. Между тем, эта информация уровня-2 (L2) может быть включена в специальный PLP кадра TFS. В соответствии с другим примером информация L2 может быть включена в специальный PLP, и информация описания услуги также может передаваться в конкретном PLP.

Например, второй пилот-сигнал может включать в себя два символа OFDM для режима FFT размером 8 кбайт. В целом второй пилот-сигнал может быть любым одним из: одиночного символа OFDM режима FFT размером 32K, одиночного символа OFDM режима FFT 16K, двух символов OFDM режима FFT 8K, четырех символов OFDM режима FFT 4K и восьми символов OFDM режима FFT 2K.

Другими словами, во втором пилот-сигнале P2 могут содержаться одиночный символ OFDM, имеющий размер большого FFT, или несколько символов OFDM, каждый из которых имеет размер малого FFT, так чтобы характеристика объема, допускающего передачу пилот-сигнала, могла поддерживаться.

Если информация, подлежащая передаче во втором пилот-сигнале, превышает емкость символа OFDM для второго пилот-сигнала, могут дополнительно использоваться символы OFDM после второго пилот-сигнала. Информация L1 (Уровень 1) и L2 (Уровень 2), содержащаяся во втором пилот-сигнале, является кодированной с исправлением ошибок и затем подвергнутой перемежению, так что восстановление данных выполняется, даже если имеет место импульсная помеха.

Как описано выше, информация L2 может также включаться в специальный PLP, передающий информацию описания услуги.

На Фиг.3 показано окно сигнализации в соответствии с настоящим изобретением. Кадр частотно-временного квантования (TFS) показывает принцип смещения информации сигнализации. Информация уровня-1 (L1), содержащаяся во втором пилот-сигнале, включает в себя информацию структуры кадра и информацию физического уровня, требуемую устройством приема сигнала, декодирующим символ данных. Следовательно, если информация последующих символов данных, расположенных после второго пилот-сигнала, содержится во втором пилот-сигнале, а передается результирующий второй пилот-сигнал, устройство приема сигнала может быть неспособным немедленно декодировать вышеупомянутые последующие символы данных из-за времени декодирования второго пилот-сигнала.

Следовательно, как показано на Фиг.3, информация L1, содержащаяся во втором пилот-сигнале (P2), включает в себя информацию о размере одного кадра частотно-временного квантования (TFS) и включает в себя информацию, содержащуюся в окне сигнализации в позиции, отстоящей от второго пилот-сигнала на величину смещения окна сигнализации.

Между тем, чтобы выполнять оценку канала для символа данных, составляющего услугу, символ данных может включать в себя пилот-сигнал «с отражением» и непрерывный пилот-сигнал.

Далее будет описана система передачи/приема сигнала, способная передавать/принимать кадры сигнала, показанные на Фиг.1-3. Отдельные услуги могут передаваться и приниматься по нескольким каналам РЧ. Канал для передачи каждой из услуг или потока, передаваемого посредством этого канала, называется PLP. PLP может распределяться между временными интервалами с временным разделением в нескольких каналах РЧ или единственной полосе РЧ. Этот кадр сигнала может передавать PLP с временным разделением, по меньшей мере, в одном канале РЧ. Другими словами, один PLP может передаваться, по меньшей мере, посредством одного канала РЧ с разделенными по времени диапазонами. Ниже в документе будут раскрыты системы передачи/приема сигнала, передающие/принимающие кадр сигнала, по меньшей мере, посредством одной полосы РЧ.

На Фиг.4 показана блок-схема, иллюстрирующая устройство для передачи сигнала в соответствии с одним вариантом осуществления настоящего изобретения. Согласно Фиг.4 устройство передачи сигнала включает в себя процессор 110 ввода, модуль 120 кодирования и модуляции, формирователь кадра 130, MIMO/MISO кодер 140, множество модуляторов (150a, …, 150r) для MIMO/MISO кодера 140 и множество аналоговых процессоров (160a, …, 160r).

Процессор 110 ввода принимает потоки, укомплектованные несколькими услугами, создает p кадров основной полосы (p является натуральным числом), которые включают в себя информацию модуляции и кодирования, соответствующую каналам передачи отдельных услуг, и выводит p кадров основной полосы.

Модуль 120 кодирования и модуляции принимает кадры основной полосы от процессора 110 ввода, выполняет канальное кодирование и перемежение относительно каждого из кадров основной полосы и выводит результат канального кодирования и перемежения.

Формирователь 130 кадра формирует кадры, которые переносят кадры основной полосы, содержащиеся в p каналах PLP, на R каналов РЧ (где R является натуральным числом), расщепляет сформированные кадры и выводит расщепленные кадры в каналы, соответствующие (числу) R каналов РЧ. В отдельном канале РЧ несколько услуг могут мультиплексироваться по времени. Кадры сигнала, сформированные формирователем 140 кадра, могут включать в себя структуру частотно-временного квантования (TFS), при этом услуга является мультиплексированной в частотно-временной области.

MIMO/MISO кодер 140 кодирует сигналы, подлежащие передаче на R каналов(ах) РЧ, и выводит кодированные сигналы в тракты, соответствующие числу А антенн (где А является натуральным числом). MIMO/MISO кодер 140 выводит кодированный сигнал, в котором единица, подлежащая передаче на единичном канале РЧ, кодируется для А антенн, так что сигнал передается/принимается на/от структуры MIMO (с многими входами и многими выходами) или структуру MISO (с многими входами и одним выходом).

Модуляторы (150a, …, 150r) модулируют сигналы частотной области, вошедшие через тракт, соответствующий каждому каналу РЧ, в сигналы временной области. Модуляторы (150a, …, 150r) модулируют входные сигналы в соответствии со схемой мультиплексирования с ортогональным частотным разделением (OFDM) и выводят модулированные сигналы.

Аналоговые процессоры (160a, …, 160r) преобразуют входные сигналы в сигналы РЧ, так что сигналы РЧ могут выводиться в каналы РЧ.

Устройство передачи сигнала в соответствии с этим вариантом осуществления может включать в себя заранее установленное число модуляторов (150a, …150r), соответствующее числу каналов РЧ, и заранее установленное число аналоговых процессоров (160a, …, 160r), соответствующее числу каналов РЧ. Однако в случае использования схемы MIMO число аналоговых процессоров должно быть равно произведению R (то есть числа каналов РЧ) и А (то есть числа антенн).

На Фиг.5 показана блок-схема, иллюстрирующая процессор 110 ввода в соответствии с настоящим изобретением. Согласно Фиг.5 процессор 110 ввода включает в себя первый мультиплексор 111a потока, первый расщепитель 113a услуги, и множество формирователей кадра (115a, …, 115m) первой основной полосы (BB). Процессор 110 ввода включает в себя второй мультиплексор 111b потока, второй расщепитель 113b услуги и множество формирователей (115n, …, 115p) кадра второй основной полосы (BB).

Например, первый мультиплексор 111a потока принимает несколько транспортных потоков (TS) формата MPEG-2 (стандарт Экспертной группы по вопросам движущегося изображения), мультиплексирует принятые TS-потоки MPEG-2 и выводит мультиплексированные TS-потоки MPEG-2. Первый расщепитель 113a услуги принимает мультиплексированные потоки, расщепляет входные потоки отдельных услуг и выводит расщепленные потоки. Как описано выше, при условии что услуга, передаваемая посредством тракта физического канала, называется PLP, первый расщепитель услуги 113a расщепляет услугу, подлежащую передаче в каждом PLP, и выводит расщепленную услугу.

Формирователи (115a, …, 115m) кадра первой BB формируют данные, содержащиеся в услуге, подлежащие передаче в каждом PLP, в форме конкретного кадра и выводят отформатированные для конкретного кадра данные. Формирователи кадра (115a, …, 115m) первой BB создают кадр, включающий в себя заголовок и полезную нагрузку, снабженную данными услуги. Заголовок каждого кадра может включать в себя информацию режима на основе модуляции и кодирования данных услуги и значения счетчика-таймера на основе тактовой частоты модулятора, чтобы синхронизировать входные потоки.

Второй мультиплексор 111b потока принимает несколько потоков, мультиплексирует входные потоки и выводит мультиплексированные потоки. Например, второй мультиплексор 111b потока может мультиплексировать потоки, передаваемые по протоколу Internet (IP) вместо TS-потоков MPEG-2. Эти потоки могут быть инкапсулированы согласно схеме общего оформления пакета потока (GSE). Потоки, мультиплексированные вторым мультиплексором 111b потока, могут быть любыми из потоков. Следовательно, вышеупомянутые потоки, отличающиеся от TS-потоков MPEG-2, называются потоками общего назначения (GS-потоками).

Второй расщепитель 113b услуги принимает мультиплексированные общие потоки, расщепляет принятые общие потоки в соответствии с отдельным услугами (то есть типами PLP) и выводит расщепленные GS потоки.

Формирователи (115n, …, 115p) кадра второй BB формируют данные услуги, подлежащие передаче в отдельных PLP в форме особого кадра, используемого в качестве единицы обработки сигналов, и выводят результирующие данные услуги. Формат кадра, формируемого формирователями (115n, …, 115p) кадра второй BB, может быть соответствующим таковому для формирователей (115a, …, 115m) кадра первой BB, если это необходимо. Если требуется, может также предлагаться другое осуществление. В другом варианте осуществления формат кадра, формируемый формирователями (115n, …, 115p) кадра второй BB, может отличаться от такового для формирователей (115a, …, 115m) кадра первой BB. Заголовок для TS MPEG-2 дополнительно включает в себя слово Packet Sync (синхронизация пакета), которое не содержится в потоке GS, что влечет появление различных заголовков.

На Фиг.6 показана блок-схема, иллюстрирующая модуль кодирования и модуляции в соответствии с настоящим изобретением. Модуль кодирования и модуляции включает в себя первый перемежитель 123, второй кодер 125 и второй перемежитель 127.

Первый кодер 121 действует в качестве внешнего кодера входного кадра основной полосы и способен выполнять кодирование с исправлением ошибок. Первый кодер 121 выполняет кодирование с исправлением ошибок входного кадра основной полосы, используя схему Боуза - Чоудхури - Хоквенгема (BCH). Первый перемежитель 123 выполняет перемежение кодированных данных, так что он предотвращает образование пакетных ошибок в сигнале передачи. Первый перемежитель 123 может не содержаться в вышеупомянутом варианте осуществления.

Второй кодер 125 действует в качестве внутреннего кодера либо выводимых данных первого кодера 121, либо выводимых данных первого перемежителя 123 и способен выполнять кодирование с исправлением ошибок. В качестве схемы кодирования с исправлением ошибок может использоваться схема с низкой плотностью битов контроля четности (LDPC). Второй перемежитель 127 смешивает кодированные с исправлением ошибок данные, сформированные вторым кодером 125, и выводит смешанные данные. Первый перемежитель 123 и второй перемежитель 127 способны выполнять перемежение данных в единицах битов.

Модуль 120 кодирования и модуляции имеет отношение к одиночному потоку PLP. Поток PLP кодируется с исправлением ошибок, модулируется посредством модуля 120 кодирования и модуляции и затем передается на формирователь 130 кадра.

На Фиг.7 показана блок-схема, иллюстрирующая формирователь кадра в соответствии с настоящим изобретением. Согласно Фиг.7 формирователь 130 кадра принимает потоки нескольких каналов от модуля 120 кодирования и модуляции и размещает принятые потоки в одном кадре сигнала. Например, формирователь кадра может включать в себя первый модуль 131a отображения и первый временной перемежитель 132a в первом тракте и может включать в себя второй модуль 131b отображения и второй временной перемежитель 132b во втором тракте. Количество входных каналов равно числу PLP для передачи услуги или числу потоков, передаваемых посредством каждого PLP.

Первый модуль 131a отображения выполняет отображение данных, содержащихся во входном потоке, в соответствии с первой схемой отображения символа. Например, первый модуль 131a отображения может выполнять отображение входных данных, используя схему квадратурной амплитудной модуляции (КАМ, QAM) (например, 16-позиционную QAM, 64-позиционную QAM и 256-позиционную QAM).

Если первый модуль 131a отображения выполняет отображение символа, входные данные могут быть отображены в несколько видов символов в соответствии с несколькими схемами отображения символа. Например, первый модуль 131a отображения классифицирует входные данные на блоки кадра основной полосы и подблоки кадра основной полосы. Отдельные классифицированные данные могут быть гибридно отображенным символом, по меньшей мере, посредством двух схем QAM (например, 16 QAM и 64 QAM). Следовательно, данные, содержащиеся в одной услуге, могут отображаться в символы на основе различных схем отображения символа в отдельных интервалах.

Первый временной перемежитель l32a принимает последовательность символов, отображенную посредством первого модуля 131a преобразования и способен выполнять перемежение во временной области. Первый модуль 131a отображения отображает в символы данные, которые содержатся в единице кадра с исправленными ошибками, принятой от модуля 120 кодирования и модуляции. Первый временной перемежитель 132a принимает последовательность символов, отображенную посредством первого модуля 131a преобразования, и перемежает принятую последовательность символов в единицах кадра с исправленными ошибками.

Таким образом, p-й модуль 131p отображения или p-й временной перемежитель 132p принимают данные услуги, подлежащие передаче в p-м PLP, и отображают данные услуги в символы в соответствии с p-й схемой отображения символа. Отображенные символы могут перемежаться во временной области. Следует отметить, что эта схема отображения символа и эта схема перемежения соответствуют таковым для первого временного перемежителя 132a и первого модуля 131a отображения.

Схема отображения символа первого модуля 131a отображения может быть соответствующей таковой для p-го модуля 131p отображения или отличной от нее. Первый модуль 131a отображения и p-й модуль 131p отображения способны отображать входные данные в отдельные символы, используя те же или отличающиеся схемы гибридного отображения символа.

Данные временных перемежителей, расположенных на отдельных трактах (то есть данные услуги, перемеженные посредством первого временного перемежителя 132a, и данные услуги, подлежащие передаче на R каналах РЧ посредством p-го временного перемежителя 132p), являются перемеженными, так что физический канал позволяет, чтобы вышеупомянутые данные были перемеженными по нескольким каналам РЧ.

В связи с потоками, принимаемыми в таком же числе каналов, каково число PLP, формирователь 133 кадров TFS формирует кадр сигнала TFS, например, как вышеупомянутый кадр сигнала, таким образом, что услуга является сдвинутой по времени в соответствии с каналами РЧ. Формирователь 133 кадров TFS расщепляет данные услуги, принятые в любом из каналов, и выводит данные услуги, расщепленные на данные для R полос РЧ в соответствии со схемой планирования сигнала.

Формирователь 133 кадров TFS принимает первый пилот-сигнал и второй пилот-сигнал от модуля 135 информации сигнализации (обозначенного «сигнал опорный/PL»), размещает первый и второй пилот-сигналы в кадре сигнала и вставляет сигнал сигнализации (L1 и L2) вышеупомянутого физического уровня во второй пилот-сигнал. В этом случае первый и второй пилот-сигналы используются в качестве начальных сигналов для кадра сигнала, содержащегося в каждом канале РЧ, из числа кадров сигнала TFS, принятых от модуля 135 информации сигнализации (сигнал опорный/PL). Как показано на Фиг.2, первый пилот-сигнал может включать в себя тип передачи и основные параметры передачи, и второй пилот-сигнал может включать в себя информацию физического параметра и структуры кадра. К тому же, второй пилот-сигнал включает в себя сигнал сигнализации L1 (Уровень 1) и сигнал сигнализации L2 (Уровень 2).

R частотных перемежителях (137a, …, 137r) перемежают данные услуги, подлежащие передаче на соответствующих каналах РЧ для кадра сигнала TFS, в частотной области. Частотные перемежители (137a, …, 137r) могут перемежать данные услуги на уровне ячеек данных, содержащихся в символе OFDM.

Следовательно, данные услуги, подлежащие передаче на каждом канале РЧ в кадре сигнала TFS, являются обработанными на частотно-избирательное замирание, так что не могут быть потеряны в конкретной частотной области.

На Фиг.8 показан вид первого примера отношения символов, когда модули 131a и 131b отображения выполняют гибридное отображение символа. На этой фигуре показано число битов, передаваемых одной поднесущей (ячейкой), если кодирование с исправлением ошибок выполняется блоком кодирования и модуляции в нормальном режиме (длина кодированного с исправлением ошибок кода составляет 64800 битов) для режима LDPC кодирования с исправлением ошибок.

Например, если модули 131a и 131b отображения выполняют отображение символа, используя 256QAM, то 64800 битов отображаются в 8100 символов. Если модули 131a и 131b отображения выполняют гибридное отображение символа (Hyb 128-QAM) с использованием 256QAM и 64QAM с соотношением 3:2, число символов, отображаемых посредством 256QAM, составляет 4860 и число символов, отображаемых посредством 64QAM, составляет 4320. Число переданных битов на одну несущую (ячейку) составляет 7,0588.

Если используется способ отображения символа 64QAM, входные данные могут отображаться на 10800 символов и могут передаваться шесть битов на одну ячейку. Если данные отображаются на символы способом гибридного отображения символа 64QAM и 16QAM (64QAM:16QAM=3:2, Hyb32-QAM), то пять битов могут передаваться посредством одной поднесущей (ячейки).

Если данные отображаются на символы способом 16QAM, то данные отображаются на 16200 символов, каждый из которых используется для передачи четырех битов.

Подобным образом, если данные отображаются на символы способом гибридного отображения символа 16QAM и QPSK (16QAM:QPSK=2:3, Hyb8-QAM), три бита могут передаваться одной поднесущей (ячейкой).

Если данные отображаются на символы способом QPSK, данные могут отображаться на 32400 символов, каждый из которых используется для передачи двух битов.

На Фиг.9 показаны способы отображения символа для данных с исправленными ошибками, кодированных способом LDPC кодирования с исправлением ошибок для «короткого» режима (длина кодированного с исправлением ошибок кода составляет 16200 битов), которые соответствуют способам отображения символа по Фиг.8 и числам битов на одну несущую в соответствии со способами отображения символа.

Число битов, передаваемых поднесущей, является соответствующим таковому для нормального режима (64800 битов) в соответствии со способами отображения символа, такими как 256QAM, Hyb 128-QAM, 64-QAM, Hyb 32-QAM, 16QAM, Hyb8-QAM и QPSK (квадратурная фазовая манипуляция, КФМн), но общие числа передаваемых символов отличаются от таковых для нормального режима. Например, 16200 битов передаются посредством 2025 символов в 256QAM, 16200 битов передаются посредством 1215 символов в соответствии с 256QAM, и 1080 символов передаются в соответствии с 64QAM (общее число 2295 символов) в Hyb 128-QAM.

Соответственно, скорость передачи данных на одну поднесущую (ячейку) для каждого PLP может регулироваться в соответствии со способом гибридного отображения символа или способом одиночного отображения символа.

На Фиг.10 показан примерный вид каждого из модулей 131a и 131b отображения символа, показанных на Фиг.7. Каждый из модулей 131a и 131b отображения символа включает в себя модуль 1315a отображения первого порядка, модуль 131b отображения второго порядка, модуль 1317 объединения символов и объединитель 1318 модулей с исправлением ошибок.

Анализатор 1311 битового потока принимает поток услуги PLP от модуля кодирования и модуляции и расщепляет принятый поток услуги.

Соответствующий первому порядку модуль 1315a отображения символа отображает на символы биты потока услуги, расщепленного посредством способа отображения символа более высокого порядка. Соответствующий второму порядку модуль 1315b отображения символа отображает на символы биты потока услуги, расщепленного способом отображения символа более низкого порядка. Например, в вышеупомянутом примере модуль 1315a отображения символа первого порядка может отображать битовый поток в символы в соответствии с 256QAM, и модуль 1315b отображения символа второго порядка может отображать битовый поток в символы в соответствии с 64QAM.

Модуль 1317 объединения символов объединяет символы, выводимые от модулей 1315a и 1315b отображения символа, в один поток символов и выводит поток символов. Модуль 1317 объединения символов может выводить поток символов, включаемый в один PLP.

Объединитель 1318 модулей с исправлением ошибок может выводить один поток символов, объединенный блоком 1317 объединения символов, в единицу блока кодированного с исправлением ошибок кода. Объединитель 1318 блоков с исправлением ошибок может выводить блок символов так, что кодированные с исправлением ошибок блоки кода равномерно распределены, по меньшей мере, по одной полосе РЧ для кадра сигнала TFS. Объединитель 1318 блоков с исправлением ошибок может выводить блок символов так, чтобы длина блока символов для кодированного с исправлением ошибок блока в нормальном режиме была равна таковой для блока символов для кодированного с исправлением ошибок блока в коротком режиме. Например, блоки из четырех символов кодированного с исправлением ошибок блока для короткого режима могут быть объединены в один блок символов.

Объединитель 1318 блоков с исправлением ошибок может расщеплять поток символов в соответствии с общим кратным числа полос РЧ, так что формирователь кадра сигнала равномерно размещает символы на полосы РЧ. Если максимальным числом полос РЧ в кадре сигнала является 6, объединитель 1318 блоков с исправлением ошибок выводит блок символа так, чтобы общее число символов могло делиться на 60, которое является общим кратным для 1, 2, 3, 4, 5 и 6.

Символы, включаемые в выводимый блок символов, могут быть организованы так, чтобы они были равномерно распределенными по отношению к шести полосам РЧ. Соответственно хотя режим с исправлением ошибок в соответствии с кодовой скоростью и способ отображения символа являются объединенными, символы, задающие конфигурацию PLP, равномерно распределяются для полос РЧ.

На Фиг.11 показан вид другого варианта осуществления модуля отображения символа. В варианте осуществления по этой фигуре модуль отображения символов включает в себя второй кодер 125 и второй перемежитель 127, включенные в модуль кодирования и модуляции. То есть если используется этот вариант осуществления, модуль кодирования и модуляции может включать в себя только первый кодер 121, первый перемежитель 123 и второй кодер 125.

Вариант осуществления модуля отображения символа включает в себя анализатор 1311 битового потока, битовый перемежитель 1312a первого порядка, битовый перемежитель 1312b второго порядка, демультиплексор 1313a первого порядка, демультиплексор 1313b второго порядка, модуль 1315a отображения символа первого порядка, модуль 1315b отображения символа второго порядка и объединитель 1317 символов.

При выполнении вторым кодером 125 LDPC-кодирования с исправлением ошибок длина кодированного с исправлением ошибок блока (например, длина 64800 битов и длина 16200 битов) может изменяться в соответствии с режимом LDPC. Если биты, включенные в кодированный с исправлением ошибок блок, отображаются в символы, возможности исправления ошибок для битов, включенных в слово ячейки, определяющее конфигурацию символа, могут изменяться в соответствии с позициями битов. Например, слово ячейки, которое является символом, может определяться в соответствии с кодовой скоростью кодирования с исправлением ошибок и способом отображения символа (является ли способ отображения символа способом отображения символа более высокого порядка или способом отображения символа более низкого порядка). Если кодом с исправлением ошибок является LDPC, возможности исправления ошибок битов изменяются в соответствии с позициями битов в кодированном с исправлением ошибок блоке. Например, надежности для битов, кодированных в соответствии с характеристиками H-матрицы (гибридных параметров), используемой в способе неравномерного LDPC кодирования с исправлением ошибок, могут изменяться в соответствии с позициями битов. Соответственно порядок битов, конфигурирующих слово ячейки, отображенное на символ, изменяется так, что возможности исправления ошибок для битов, которые являются слабыми в сравнении с исправлением ошибок в кодированном с исправлением ошибок блоке, регулируются и, таким образом, устойчивость к ошибке в битовом уровне может регулироваться.

Сначала второй кодер 125, например, выполняет кодирование с исправлением ошибок по отношению к потоку, включенному в один PLP, посредством способа LDPC кодирования с исправлением ошибок.

Анализатор 1311 битового потока принимает поток услуги в соответствии с PLP и расщепляет принятый поток услуги.

Битовый перемежитель 1312a первого порядка перемежает биты, включенные в первый битовый поток расщепленных потоков услуги. Подобным образом битовый перемежитель 1312b второго порядка перемежает биты, включенные во второй битовый поток расщепленных потоков услуги.

Битовый перемежитель 1312a первого порядка и битовый перемежитель 1312b второго порядка могут соответствовать второму перемежителю 127, используемому в качестве внутреннего перемежителя. Способ перемежения для битового перемежителя 1312a первого порядка и битового перемежителя 1312b второго порядка будет описан далее.

Демультиплексор 1313a первого порядка и демультиплексор 1313b второго порядка демультиплексируют биты битовых потоков, перемеженных битовым перемежителем 1312a первого порядка и битовым перемежителем 1312b второго порядка. Демультиплексоры 1313a и 1313b делят входной битовый поток на подпотоки битов, которые будут отображаться на вещественную ось и мнимую ось совокупности (конкатенации), и выводят подпотоки битов. Модули 1315a и 1315b отображения символа отображают на соответствующие символы подпотоки битов, демультиплексированные демультиплексорами 1313a и 1313b.

Перемежители битов 1312a и 1312b и демультиплексоры 1313a и 1313b могут комбинировать характеристики кодового слова LDPC и характеристики надежности совокупности для отображения символа в соответствии с совокупностью. Подробное осуществление демультиплексоров 1313a и 1313b первого порядка будет описано далее.

Модуль 1315a отображения символа первого порядка выполняет соответствующее первому порядку отображение символа, например отображение символа более высокого порядка, и модуль 1315b отображения символа второго порядка выполняет соответствующее второму порядку отображение символа, например отображение символа более низкого порядка. Модуль 1315a отображения символа первого порядка отображает в символы подпотоки битов, выводимые из демультиплексора 1313 первого порядка, и модуль 1315b отображения символа второго порядка отображает в символы подпотоки битов, выводимые из демультиплексора 1313b второго порядка.

Объединитель 1317 символов объединяет символы, отображенные блоком 1315a отображения символа первого порядка и блоком 1315b отображения символа второго порядка, в один поток символов и выводит поток символов.

Как описано выше, в LDPC возможности исправления ошибок для битов могут быть изменены в соответствии с позициями битов в кодированном с исправлением ошибок блоке. Соответственно если перемежитель битов и демультиплексор являются управляемыми в соответствии с характеристиками LDPC кодера 125, чтобы изменять порядок битов, задающих конфигурацию слова ячейки, возможность исправления ошибок на уровне битов может быть максимизирована.

На Фиг.12 показано представление принципа перемежения битов перемежителями 1312a и 1312b битов по Фиг.11.

Например, входные биты хранятся в имеющей заранее установленное число строк и столбцов матричного вида машинной памяти и считываются из нее. При сохранении входных битов сначала сохраняются биты в первом столбце в направлении по строке, и если первый столбец заполнен, сохраняются биты в другом столбце в направлении по строке. При считывании хранимых битов биты считываются в направлении столбца, и если считываются все биты, хранимые в первой строке, считываются биты из другой строки в направлении столбца. Другими словами, при сохранении битов биты сохраняются построчно, так что столбцы заполняются последовательно. И когда хранимые биты считываются, хранимые биты считываются по столбцам от первой строки до последней строки последовательно. На этой фигуре MSB означает «старший значащий бит», и LSB означает «младший значащий бит».

Для того чтобы отображать LDPC-кодированные с исправлением ошибок биты на символы с той же длиной единицы блока исправления ошибок с различными кодовыми скоростями, битовые перемежители 1312a и 1312b могут изменять число строк и столбцов машинной памяти в соответствии с типам модулей 1315a и 1315b отображения символа.

На Фиг.13 показан вид примера ряда строк и столбцов машинной памяти для битовых перемежителей 1312a и 1312b в соответствии с типами модулей отображения символа 1315a и 1315b, если режимом LDPC является нормальный режим.

Например, если модуль 1315a отображения символа отображает биты на символы 256QAM, перемежитель 1312a первого порядка перемежает биты с помощью машинной памяти, имеющей 8100 строк и 8 столбцов. Если символы отображаются согласно 64QAM, то перемежитель 1312a первого порядка перемежает биты с помощью машинной памяти, имеющей 10800 строк и 6 столбцов. Если символы отображаются согласно 16QAM, перемежитель 1312a первого порядка перемежает биты машинной памяти, имеющей 16200 строк и 4 столбца.

Например, если модули 1315a и 1315b отображения символа отображают биты на символы Hyb128-QAM, перемежитель 1312a первого порядка перемежает биты, используя машинную память, имеющую 4860 строк и 8 столбцов, и перемежитель 1312b второго порядка перемежает биты, используя машинную память, имеющую 4320 строк и 6 столбцов.

Подобным образом, если модули 1315a и 1315b отображения символа отображают символы Hyb32-QAM, перемежитель 1312a первого порядка перемежает биты, используя машинную память, имеющую 6480 строк и 6 столбцов, и перемежитель 1312b второго порядка перемежает биты, используя машинную память, имеющую 6480 строк и 4 столбца.

На Фиг.14 показан вид примера ряда строк и столбцов машинной памяти для битовых перемежителей 1312a и 1312b в соответствии с типами модулей 1315a и 1315b отображения символа, если режимом LDPC является короткий режим.

Например, если модуль 1315a отображения символа отображает биты на символы 256QAM, перемежитель 1312a первого порядка перемежает биты посредством машинной памяти, имеющей 2025 строк и 8 столбцов. Если модули 1315a и 1315b отображения символа отображают символы Hyb128-QAM, перемежитель 1312a первого порядка перемежает биты, используя машинную память, имеющую 1215 строк и 8 столбцов, и перемежитель 1312b второго порядка перемежает биты, используя машинную память, имеющую 1080 строк и 6 столбцов.

Если перемежение битов выполняется по отношению к кодированному с исправлением ошибок блоку, позиции битов в кодированном с исправлением ошибок блоке могут быть изменены.

На Фиг.15 показано представление принципа мультиплексирования входных битов для демультиплексоров 1313a и 1313b.

Перемежители 1312a и 1312b битов перемежают входные биты x0, x1 и xn-1 и выводят перемеженные биты. Способ перемежения уже описан выше.

Демультиплексоры 1313a и 1313b демультиплексируют перемеженные потоки битов. Способ демультиплексирования может изменяться в соответствии с кодовой скоростью способа кодирования с исправлением ошибок и способа отображения символа в блоке отображения символа. Если способом отображения символа в блоке отображения символа является QPSK, входные биты, например, перемежаются в два подпотока и модуль отображения символа отображает два подпотока в символы так, чтобы они соответствовали вещественной оси и мнимой оси совокупности. Например, первый бит y0 демультиплексированного первого подпотока соответствует вещественной оси, и первый бит y1 демультиплексированного второго подпотока соответствует мнимой оси.

Если способом отображения символа модуля отображения символа является 16QAM, входные биты, например, демультиплексируются в четыре подкадра. Модуль отображения символа выбирает биты, включенные в четыре подпотока, и отображает выбранные биты на символы с тем, чтобы они соответствовали вещественной оси и мнимой оси совокупности.

Например, биты y0 и y2 демультиплексированного первого и третьего подпотоков соответствуют вещественной оси, и биты yl и y3 демультиплексированного второго и четвертого подпотоков соответствуют мнимой оси.

Подобным образом, если способом символа в блоке отображения символа является 64QAM, входные биты могут быть демультиплексированы в шесть битовых потоков. Модуль отображения символа отображает шесть подпотоков на символы с тем, чтобы они соответствовали вещественной оси и мнимой оси совокупности. Например, демультиплексированные первый, третий и пятый подпотоки битов y0, y2 и y4 соответствуют вещественной оси, и демультиплексированные второй, четвертый и шестой подпотоки битов y1, y3 и y6 соответствуют мнимой оси.

Подобным образом, если способом символа в блоке отображения символа является 256QAM, входные биты могут быть демультиплексированы на восемь битовых потоков. Модуль отображения символа отображает эти восемь подпотоков на символы с тем, чтобы они соответствовали вещественной оси и мнимой оси совокупности. Например, сначала демультиплексированные первый, третий, пятый и седьмой биты подпотоков y0, y2, y4 и y6 соответствуют вещественной оси, и демультиплексированные второй, четвертый, шестой и восьмой биты подпотоков y1, y3, y6 и y7 соответствуют мнимой оси.

Если модуль отображения символа отображает символы, демультиплексированные демультиплексором, подпотоки могут отображаться в потоки битов вещественной оси и мнимой оси совокупности.

Вышеописанные способ перемежения битов, способ демультиплексирования и способ отображения символа являются иллюстративными, и могут использоваться различные способы в качестве способа выбора битов в подпотоках с тем, чтобы демультиплексированные демультиплексором подпотоки могли соответствовать вещественной оси и мнимой оси совокупности.

Отображенное в символы слово ячейки может изменяться в соответствии с любым из исправленных ошибкой битовых потоков в соответствии с кодовой скоростью, способом перемежения битовых потоков, способом демультиплексирования и способом отображения символа. MSB в слове ячейки выше LSB в слове ячейки по надежности декодирования с исправлением ошибок. Хотя надежность бита в конкретной позиции кодированного с исправлением ошибок блока является низкой, надежность бита может быть повышена посредством процесса обратного отображения символа, если бит слова ячейки расположен в MSB или близко к MSB.

Соответственно хотя надежность бита, кодированного в соответствии с характеристикам H-матрицы, используемой в способе неравномерного LDPC кодирования с исправлением ошибок, изменяется, бит может устойчиво передаваться/приниматься с помощью процесса отображения символа и обратного отображения и рабочая характеристика системы может настраиваться.

На Фиг.16 показан вид варианта осуществления демультиплексирования входного потока демультиплексором.

Если способом отображения символа является QPSK, два бита отображаются в один символ и два бита одной единицы символа демультиплексируются в очередности индексов битов (индексы 0 и 1 для b).

Если способом отображения символа является 16QAM, 4 бита отображаются в один символ и четыре бита одной единицы символа демультиплексируются в соответствии с результатом вычисления по модулю 4 для индексов битов (индексы 0, 1, 2 и 3 для b).

Если способом отображения символа является 64QAM, 6 битов отображаются в один символ и шесть битов одной единицы символа демультиплексируются в соответствии с результатом вычисления по модулю 6 для индексов битов (индексы 0, 1, 2, 3, 4 и 5 для b).

Если способом отображения символа является 256QAM, 8 битов отображаются в один символ и восемь битов одной единицы символа демультиплексируются в соответствии с результатом вычисления по модулю 8 для индексов битов (индексы 0, 1, 2, 3, 4, 5, 6 и 7 для b).

Порядок демультиплексирования подпотоков является иллюстративным и может быть изменен.

На Фиг.17 показан вид примера типа демультиплексирования в соответствии со способом отображения символа. Способ отображения символа включает в себя QPSK, 16QAM, 64QAM и 256QAM, и тип демультиплексирования включает в себя тип от первого до шестого.

Первый тип является примером, в котором входные биты последовательно соответствуют индексам с четными номерами (0, 2, 4, 8,) (или вещественная ось совокупности) и последовательно соответствуют индексам с нечетными номерами (1, 3, 5, 7,) (или мнимая ось совокупности). В дальнейшем битовое демультиплексирование первого типа может быть представлено идентификатором демультиплексирования «10» (двоичное число 1010; позиция 1 - позиция MSB, соответствующая вещественной оси и мнимой оси совокупности).

Второй тип является примером, в котором демультиплексирование выполняется в обратном порядке относительно первого типа, то есть LSB входных битов последовательно соответствует четным индексам (6, 4, 2, 0) (или вещественная ось совокупности) и нечетным индексам (1, 3, 5, 7,) (или мнимая ось совокупности). В дальнейшем битовое демультиплексирование второго типа может быть представлено идентификатором демультиплексирования «5» (двоичное число 0101).

Третий тип является примером, в котором входные биты организованы так, что битами обоих концов кодового слова становятся MSB. Входные биты переставляются, чтобы заполнять кодовое слово с обоих концов кодового слова. Ниже в документе, битовое демультиплексирование третьего типа может быть представлено идентификатором демультиплексирования «9» (двоичное число 1001).

Четвертый тип является примером, в котором входные биты организованы так, что средним битом кодового слова становится MSB. Битом входных битов является первый заполненный в средней позиции кодового слова, и оставшиеся биты затем переставляются в направлении обоих концов кодового слова в очередности входных битов. Ниже в документе битовое демультиплексирование четвертого типа может быть представлено идентификатором демультиплексирования «6» (двоичное число 0110).

Пятый тип является примером, в котором биты являются демультиплексированными так, что последним битом кодового слова становится MSB и его первым битом становится LSB, и шестой тип является примером, в котором биты переставляются так, что первым битом кодового слова становится MSB и его последним битом становится LSB. Ниже в документе битовое демультиплексирование пятого типа может быть представлено идентификатором демультиплексирования «3» (двоичное число 0011), и битовое демультиплексирование шестого типа может быть представлено идентификатором демультиплексирования «12» (двоичное число 1100).

Как описано выше, тип демультиплексирования может изменяться в соответствии со способом отображения символа или кодовой скоростью способа кодирования с исправлением ошибок. То есть может использоваться другой тип демультиплексирования, если изменяется способ отображения символа или кодовая скорость.

На Фиг.18 показан вид варианта осуществления демультиплексирования входного битового потока в соответствии с типом демультиплексирования. В этом варианте осуществления в схему могут включаться перемежители битов 1312a и 1312b, демультиплексоры 1313a и 1313b и модули 1315a и 1315b преобразования.

Битовые перемежители 1312a и 1312b перемежают кодированные с исправлением ошибок PLP-сервисные потоки. Например, перемежители битов 1312a и 1312b могут выполнять битовое перемежение в единицах кодирования с исправлением ошибок в соответствии с режимом кодирования с исправлением ошибок. Способ побитового перемежения уже был описан выше.

Демультиплексоры 1313a и 1313b могут включать в себя демультиплексоры 1313a1 и 1313b1 первого типа и демультиплексоры 1313a2 и 1313b2 n-го типа. Здесь n является целым числом. Способы демультиплексирования битов посредством демультиплексоров n типов следуют типам, показанным на Фиг.17. Например, демультиплексоры первого типа могут соответствовать битовому демультиплексированию первого типа (1100), и демультиплексор второго типа (не показано) может соответствовать битовому демультиплексированию второго типа (0011). Демультиплексор 1313b n-го типа демультиплексирует входной битовый поток в соответствии с битовым мультиплексированием n-го типа (например, идентификатор 1100 демультиплексирования) и выводит демультиплексированный битовый поток. Селекторы 1313a3 и 1313b3 принимают сигнал выбора демультиплексора относительно типа демультиплексирования, подходящего для входных битов, и выводят демультиплексированные потоки битов в соответствии с любым типом от первого типа до n-го типа и сигналом выбора демультиплексора. Сигнал выбора демультиплексора может изменяться в соответствии с кодовой скоростью кодирования с исправлением ошибок и способа отображения символа совокупности. Соответственно тип демультиплексирования может быть определен в соответствии с кодовой скоростью способа кодирования с исправлением ошибок или/и способом отображения символа для совокупности. Далее будет описан подробный пример в соответствии с символами, отображенными на совокупности или/и кодовой скоростью кодирования с исправлением ошибок в соответствии с сигналом выбора демультиплексора.

Модули 1315a и 1315b отображения могут отображать демультиплексированные подпотоки битов на символы в соответствии с сигналом выбора демультиплексора и выводить отображенные символы.

На Фиг.19 показано представление типа демультиплексирования, который определен в соответствии с кодовой скоростью кодирования с исправлением ошибок и способом отображения символа.

В способе 4QAM отображения символа, даже если кодовая скорость «cr» способа LDPC кодирования с исправлением ошибок является любой из 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10, битовый поток может быть демультиплексирован в соответствии со всеми типами демультиплексирования (обозначено «все»).

В способе 16QAM отображения символа, если кодовой скоростью способа LDPC кодирования с исправлением ошибок является 1/4, 1/3, 2/5 и 1/2, символы могут отображаться без выполнения битового перемежения и битового демультиплексирования (обозначено No-Int и No-Demux). Если кодовой скоростью кодирования с исправлением ошибок является 3/5, бит может демультиплексироваться в соответствии с любым из идентификаторов 9, 10 и 12 демультиплексирования. Если кодовой скоростью кодирования с исправлением ошибок является 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10, входной битовый поток может демультиплексироваться в соответствии с идентификатором «6» демультиплексирования.

В способе 64QAM отображения символа, если кодовой скоростью LDPC кодирования с исправлением ошибок является 1/4, 1/3, 2/5 и 1/2, символы могут быть отображены без выполнения битового перемежения и битового демультиплексирования. Если кодовой скоростью является 3/5, биты могут быть демультиплексированы в соответствии с любым из идентификаторов «9» и «10» демультиплексирования. Если кодовой скоростью является 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10, биты могут быть демультиплексированы в соответствии с идентификатором 6 демультиплексирования.

В способе отображения символа 256QAM, если кодовой скоростью LDPC кодирования с исправлением ошибок является 1/4, 1/3, 2/5 и 1/2, символы могут быть отображены без выполнения битового перемежения и битового демультиплексирования. Если кодовой скоростью является 3/5, биты могут быть демультиплексированы в соответствии с идентификатором демультиплексирования «9». Если кодовой скоростью является 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10, биты могут быть демультиплексированы в соответствии с идентификатором демультиплексирования «6».

Как описано выше, тип битового демультиплексирования может изменяться в соответствии с кодовой скоростью, используемой для кодирования с исправлением ошибок, и способом отображения символа. Соответственно возможность исправления ошибок для бита, расположенного в конкретной позиции кодированного с исправлением ошибок блока, может настраиваться путем отображения демультиплексированных подпотоков на символы. Соответственно является возможным оптимизировать устойчивость (к ошибкам) на уровне битов.

На Фиг.20 показан вид примера выражения способа демультиплексирования посредством уравнения. Например, если способом отображения символа является QPSK, входные биты (xi, xN/2+i) соответствуют демультиплексированным битам y0 и y1. Если способом отображения символа является 16QAM, входные биты ( ) соответствуют демультиплексированным битам y0, y1, y2 и y3.

) соответствуют демультиплексированным битам y0, y1, y2 и y3.

Если способом отображения символа является 64QAM, входные биты ( ) соответствуют демультиплексированным битам y0, y1, y2, y3, y4 и y5. Если способом отображения символа является 256QAM, входные биты (

) соответствуют демультиплексированным битам y0, y1, y2, y3, y4 и y5. Если способом отображения символа является 256QAM, входные биты ( ) соответствуют демультиплексированным битам y0, y1, y2, y3, y4, y5, y6 и y7.

) соответствуют демультиплексированным битам y0, y1, y2, y3, y4, y5, y6 и y7.

Здесь N обозначает число битов, отображенных в символы, по отношению к входным битам перемежителя.

На Фиг.21 показан вид примера отображения символа посредством модуля отображения символа. Например, в способе QPSK отображения символа символы на созвездии соответствуют значению бита y0 демультиплексированного первого подпотока и значению бита y1 демультиплексированного второго подпотока.

В 16QAM вещественная ось символов в созвездии соответствует битам демультиплексированного первого и третьего подпотоков (биты, отделенные от позиции MSB на 0 и 2), и мнимая ось таковой соответствует битам демультиплексированного второго и четвертого подпотоков (биты, отделенные от позиции MSB на 1 и 3).

В 64QAM вещественная ось символов в совокупности соответствует битам демультиплексированного первого, третьего и пятого подпотоков (биты, отделенные от позиции MSB на 0, 2 и 4), и мнимая ось таковой соответствует битам демультиплексированных второго, четвертого и шестого подпотоков (биты, отделенные от позиции MSB на 1, 3 и 5).

Соответственно биты, определяющие конфигурацию символа, могут отображаться на слово ячейки в очередности демультиплексирования. Если биты, определяющие конфигурацию слова ячейки, демультиплексируются, MSB и LSB в слове ячейки изменяются и устойчивость к ошибкам битов может регулироваться, хотя надежность LDPC-кодированных с исправлением ошибок битов изменяется в соответствии с позициями.

На Фиг.22 показана блок-схема, иллюстрирующая MIMO/MISO кодер в соответствии с настоящим изобретением. Согласно Фиг.22 MIMO/MISO кодер кодирует входные данные, используя схему MIMO/MISO кодирования, и выводит кодированные данные по нескольким каналам. Если приемная сторона сигнала принимает сигнал, переданный по этим нескольким каналам, из одного или нескольких каналов, является возможным получить выгоду (также называемую усилением при разнесенном приеме, повышением полезной нагрузки или повышением степени мультиплексирования).

MIMO/MISO кодер 140 кодирует данные услуги для каждого канала, сформированного формирователем кадра 130, и выводит кодированные данные в А каналов, соответствующих числу выходных антенн.

На Фиг.23 показана блок-схема, иллюстрирующая модулятор в соответствии с настоящим изобретением. Согласно Фиг.23 модулятор включает в себя первый контроллер 151 мощности (PAPR Reduce1), модуль 153 преобразования во временную область (IFFT), второй контроллер 157 мощности (PAPR Reduce2) и модуль 159 вставки защитного интервала.

Первый контроллер 151 мощности уменьшает PAPR (отношение пиковой мощности к средней) для данных, передаваемых в число R каналов сигнала в частотной области.

Модуль 153 преобразования во временную область (IFFT) преобразует принимаемые сигналы частотной области в сигналы временной области. Например, сигналы частотной области могут быть преобразованы в сигналы временной области в соответствии с алгоритмом обратного быстрого преобразования Фурье (IFFT). Следовательно, данные частотной области могут модулироваться в соответствии со схемой OFDM.

Второй контроллер 157 мощности (PAPR Reduce2) уменьшает PAPR (отношение пиковой мощности к средней) данных канала, передаваемых в число R каналов сигнала во временной области. В этом случае могут использоваться схема сохранения тона и схема расширения активной совокупности (ACE) для расширения совокупности (констелляции) символа.

Модуль 159 вставки защитного интервала вставляет защитный интервал в выводимый символ OFDM и выводит результат этого вставления. Как описано выше, вышеупомянутый вариант осуществления может выполняться в каждом сигнале R каналов.

На Фиг.24 показана блок-схема, иллюстрирующая аналоговый процессор 160 в соответствии с настоящим изобретением. Согласно Фиг.24 аналоговый процессор 160 включает в себя цифроаналоговый преобразователь (ЦАП, DAC) 161, модуль 163 преобразования с повышением частоты и аналоговый фильтр 165.

DAC 161 преобразовывает входные данные в аналоговый сигнал и выводит аналоговый сигнал. Модуль 163 преобразования с повышением частоты преобразует частотную область аналогового сигнала в область РЧ. Аналоговый фильтр 165 фильтрует сигнал РЧ-области и выводит отфильтрованный сигнал РЧ.

На Фиг.25 показана блок-схема, иллюстрирующая устройство для приема сигнала в соответствии с настоящим изобретением. Согласно Фиг.25 устройство приема сигнала включает в себя первый приемник 210a сигнала, n-й приемник 210n сигнала, первый демодулятор 220a, n-й демодулятор 220n, декодер 230 MIMO/MISO, анализатор 240 кадра, декодирующий демодулятор 250 и процессор 260 вывода.

В случае сигнала приема, соответствующего структуре кадра сигнала TFS, несколько услуг мультиплексируются в R каналов и затем сдвигаются по времени, так что передается сдвинутый по времени результат.

Приемник может включать в себя, по меньшей мере, один приемник сигнала, чтобы принимать услугу, передаваемую, по меньшей мере, по одному каналу РЧ. Кадр сигнала TFS, передаваемый в число R (где R является натуральным числом) каналов РЧ, может передаваться по многолучевому распространению через А антенн. «А» антенн используются для R каналов РЧ, так что общее число антенн равно R×A.

Первый приемник 210a сигнала способен принимать данные услуги, передаваемые посредством, по меньшей мере, одного канала, из числа полных данных услуги, передаваемых посредством нескольких каналов РЧ. Например, первый приемник 210a сигнала может принимать сигнал передачи, обработанный в соответствии со схемой MIMO/MISO, через несколько каналов.

Первый приемник 210a сигнала и n-й приемник 210n сигнала могут принимать несколько единиц данных услуги, передаваемых по n каналам РЧ из числа нескольких каналов РЧ, в виде одного PLP. А именно, этот вариант осуществления показывает устройство приема сигнала, способное одновременно принимать данные от R каналов РЧ. Следовательно, если в этой реализации принимается один канал РЧ, является необходимым только первый приемник 210a.

Первый демодулятор 220a и n-й демодулятор 220n демодулируют сигналы, принятые в первом и n-м приемниках 210a и 210n сигнала в соответствии со схемой OFDM, и выводят демодулированные сигналы.

MIMO/MISO декодер 230 декодирует данные услуги, принятые через несколько каналов передачи, в соответствии со схемой декодирования MIMO/MISO, и выводит декодированные данные услуги в отдельный канал передачи. Если принято R передаваемых услуг по нескольким каналам передачи, MIMO/MISO декодер 230 может выводить данные услуги одного PLP, содержащиеся в каждой из R услуг, соответствующих числу R каналов. Если p услуг передаются посредством R каналов РЧ и сигналы отдельных каналов РЧ принимаются через А антенн, приемник декодирует p услуг, используя общее число (R×A) приемных антенн.

Модуль 240 анализа кадра осуществляет анализ кадра сигнала TFS, включающего в себя несколько услуг, и выводит извлеченные данные услуги.

Декодирующий демодулятор 250 выполняет декодирование с исправлением ошибок относительно данных услуги, содержащихся в извлеченном кадре, выполняет обратное отображение декодированных данных символа в битовые данные и выводит результат обработанного обратного отображения.

Процессор 260 вывода декодирует поток, включающий в себя обратно отображенные битовые данные, и выводит декодированный поток.

В вышеупомянутом описании каждый компонент из модуля 240 анализа кадра, декодирующего демодулятора 250 и процессора 260 вывода принимает столько единиц данных услуги, каково число PLP, и выполняет обработку сигналов над принятыми данными услуги.

На Фиг.26 показана блок-схема, иллюстрирующая приемник сигнала в соответствии с настоящим изобретением. Согласно Фиг.26 приемник сигнала может включать в себя тюнер 211, преобразователь с понижением частоты 213, и аналого-цифровой преобразователь (АЦП, ADC) 215.

Тюнер 211 выполняет скачкообразную перестройку некоторых каналов РЧ, способных передавать выбранные пользователем услуги во всех каналах РЧ, если PLP включен в состав нескольких каналов РЧ, и выводит результат перестройки. Тюнер 211 выполняет скачкообразную перестройку каналов РЧ, содержащихся в кадре сигнала TFS, в соответствии с входными центральными частотами РЧ и в то же время настраивает соответствующие частотные сигналы таким образом, что он выводит настроенные сигналы. Если сигнал передается в А каналов многолучевого распространения, тюнер 211 выполняет настройку на соответствующий канал РЧ и принимает сигналы приема через А антенн.

Преобразователь 213 с понижением частоты выполняет преобразование с понижением частоты РЧ сигнала, настроенного тюнером 211, и выводит результат преобразования с понижением частоты. АЦП 215 преобразовывает аналоговый сигнал в цифровой сигнал.

На Фиг.27 показана блок-схема, иллюстрирующая демодулятор в соответствии с настоящим изобретением. Согласно Фиг.27 демодулятор включает в себя детектор кадра 221, модуль 222 синхронизации кадра, модуль 223 удаления защитного интервала, модуль 224 преобразования в частотную область (FFT), модуль 225 оценки канала, канальный эквалайзер 226 и модуль 227 извлечения информации сигнализации.

Если демодулятор получает данные услуги, переданные в потоке одного PLP, будет выполняться нижеследующая демодуляция сигнала. Подробное описание этого процесса будет представлено ниже.

Детектор 221 кадра идентифицирует систему доставки сигнала приема. Например, детектор 221 кадра определяет, является ли сигнал приема сигналом DVB-TS (цифрового телевидения) или не является. И детектор 221 кадра может также определять, является ли сигнал приема кадром сигнала TFS или не является. Модуль 222 синхронизации кадра извлекает синхронизацию временной и частотной области из кадра сигнала TFS.

Контроллер 223 защитного интервала удаляет из временной области защитный интервал, находящийся между символами OFDM. Преобразователь 224 в частотную область (FFT) преобразовывает сигнал приема в сигнал частотной области, используя алгоритм FFT, таким образом, что он извлекает соответствующие частотной области данные символа.

Модуль оценки 225 канала выполняет оценку канала относительно канала приема, используя символ пилот-сигнала, содержащийся в данных символа, соответствующих частотной области. Канальный эквалайзер 226 выполняет частотную коррекцию канала для данных приема, используя информацию оценки канала, определенную блоком 225 оценки канала.

Модуль 227 извлечения информации сигнализации может извлекать информацию сигнализации относительно физического уровня, установленного в первом и втором пилот-сигналах, содержащихся в данных приема частотно скорректированного канала.

На Фиг.28 показана блок-схема, иллюстрирующая MIMO/MISO декодер в соответствии с настоящим изобретением. Приемник сигнала и демодулятор предназначены для обработки сигнала, принимаемого в отдельном канале. Если приемник сигнала и демодулятор принимают данные услуги PLP, обеспечивающие одну услугу посредством нескольких каналов нескольких антенн, и демодулируют данные услуги PLP, MIMO/MISO декодер 230 выводит сигнал, принимаемый в нескольких каналах, в виде данных услуги, передаваемых в одном PLP. Следовательно, MIMO/MISO декодер 230 может получать выгоду разнесенного приема и выгоду мультиплексирования от данных услуг, принимаемых в соответствующих PLP.

MIMO/MISO декодер 230 принимает сигнал передачи многолучевого распространения от нескольких антенн и способен декодировать сигнал, используя схему MIMO, способную восстанавливать каждый сигнал приема в форме одного сигнала. Иначе, MIMO/MISO декодер 230 способен восстанавливать сигнал, используя схему MIMO, которая принимает сигнал многолучевой передачи от одиночной антенны и восстанавливает принятый сигнал многолучевой передачи.

Следовательно, если сигнал передается через R каналов РЧ (где R является натуральным числом), MIMO/MISO декодер 230 может декодировать сигналы, принятые через А антенн отдельных каналов РЧ. Если значение А равно "1", сигналы могут декодироваться в соответствии со схемой MISO. Если значение А выше "1", сигналы могут декодироваться в соответствии со схемой MIMO.

На Фиг.29 показана блок-схема, иллюстрирующая анализатор кадра в соответствии с настоящим изобретением. Согласно Фиг.29 анализатор кадра включает в себя первый частотный обратный перемежитель 241a, r-й частотный обратный перемежитель 241r, анализатор кадра 243, первый временной обратный перемежитель 245a, p-й временной обратный перемежитель 245p, первый модуль 247a обратного отображения и p-й модуль 247p обратного отображения. Значение "r" может определяться числом каналов РЧ, и значение "p" может быть определено согласно числу потоков, передающих данные услуги PLP, сформированные блоком анализа кадра 243.

Следовательно, если p услуг передаются в p потоков PLP по R каналам РЧ, то анализатор кадра включает в себя r частотных обратных перемежителей, p временных обратных перемежителей и p модулей обратного отображения символа.

В связи с первым каналом РЧ первый частотный перемежитель 241a выполняет обратное перемежение входных данных частотной области и выводит результат обратного перемежения.

Анализатор кадра 243 осуществляет анализ (парсинг) кадра сигнала TFS, передаваемого в несколько каналов РЧ, используя информацию планирования кадра сигнала TFS, и осуществляет анализ данных услуги PLP, содержащихся во временном интервале конкретного канала РЧ, включающего в себя требующуюся услугу. Анализатор кадра 243 осуществляет анализ кадра сигнала TFS, чтобы принимать данные конкретной услуги, распределенные в несколько каналов РЧ, в соответствии со структурой кадра сигнала TFS, и выводит данные услуги PLP первого тракта.