Предлагаемое изобретение относится к телевизионной технике и преимущественно может быть использовано для анализа интерферограмм оптических изделий, выполняемого в телевизионных системах, где в качестве датчиков видеосигнала применены матрицы приборов с зарядовой связью (матрицы ПЗС).

Известно устройство формирования сигнала изображения интерферограмм [1], содержащее оптически связанные светоделитель, светорегулирующую ячейку и матрицу ПЗС, состоящую из связанных зарядовой связью первой секции накопления, второй секции накопления, секции хранения и выходного регистра, а также блок управления, первый выход которого соединен с управляющими входами первой и второй секций накопления, второй выход - с управляющим входом секции хранения, третий выход - с управляющим входом выходного регистра, четвертый и пятый выходы - соответственно с первым и вторым управляющими входами усилителя-формирователя, информационный вход которого подключен к выходу выходного регистра матрицы ПЗС (Для упрощения изложения в формуле изобретения данного устройства не упоминается входящий в матрицу ПЗС блок преобразования заряда в напряжение (БПЗН)), а выход является выходом устройства, при этом светорегулирующая ячейка выполнена в виде электрохромного прибора, а ее управляющий вход подключен к источнику регулируемого напряжения постоянного тока, причем светоделитель оптически связан с первой секцией накопления матрицы ПЗС непосредственно, а со второй секцией накопления матрицы ПЗС - через светорегулирующую ячейку.

В данном устройстве путем рекурсивной фильтрации видеосигнала выполняется усреднение случайных колебаний оптического изображения объектов, вызванных, например, вибрациями. Интервал накопления задержанной составляющей выходного сигнала изображения однозвенного рекурсивного фильтра фиксирован и равен интервалу накопления прямой составляющей видеосигнала на выходе рекурсивного фильтра. Регулировка же степени фильтрации достигается только за счет управления размахом этой составляющей сигнала с коэффициентом K, который определяется коэффициентом ослабления освещенности для первой мишени матрицы ПЗС.

Недостатком аналога [1] является ограниченная точность выполнения операции рекурсивной фильтрации выходного видеосигнала.

Известно другое устройство [2], которое по отношению к предлагаемому решению обладает большим числом сходных существенных признаков, а поэтому является другим аналогом. Оно содержит последовательно расположенные и оптически связанные объектив и мишень датчика телевизионного сигнала, а также RS-триггер, селектор синхроимпульсов, счетчик-делитель, коммутатор, блок задержки на кадр, состоящий из последовательно соединенных аналого-цифрового преобразователя (АЦП), оперативно-запоминающего устройства (ОЗУ) и цифроаналогового преобразователя (ЦАП), причем выход «Видео» датчика подключен к входу блока задержки на кадр и соответственно к входу селектора синхроимпульсов, выход которого подключен к тактовому входу RS-триггера и соответственно к входу последовательно соединенных счетчика-делителя и коммутатора, управляющий вход которого соединен с первым управляющим входом датчика и подключен к прямому выходу RS-триггера, второй управляющий вход датчика подключен к выходу коммутатора, S-вход RS-триггера является входом «Пуск», а R-вход RS-триггера - входом «Стоп» устройства.

Недостатком второго аналога является отсутствие выполнения операции рекурсивной фильтрации и высокий уровень собственных шумов матрицы ПЗС, вносимых в выходной сигнал изображения устройства. Это определяется тем, что в фотоприемнике используется единственный блок преобразования заряда в напряжение» (БПЗН), который выполнен по критерию максимальной управляющей способности зарядового преобразования.

Наиболее близким по числу сходных существенных признаков, характеризующих заявляемое изобретение, следует считать устройство [3], содержащее последовательно расположенные и оптически связанные объектив и матрицу ПЗС, состоящую из последовательно связанных зарядовой связью фотоприемной секции, первого горизонтального регистра, первого БПЗН, разделительного электрода, секции памяти, второго горизонтального регистра и второго БПЗН; генератор управляющих импульсов, состоящий из последовательно соединенных временного контроллера (ВК) и первого преобразователя уровней (ПУ) и содержащий в своем составе второй ПУ; сигнальный процессор, содержащий первый и второй видеоусилители; первый блок задержки на кадр (БЗК); второй БЗК, а также содержащее в составе формирователя комбинированного изображения RS-триггер, последовательно соединенные счетчик-делитель и коммутатор, элемент «И» и коммутатор-смеситель, при этом управляющие входы фотоприемной секции и секции памяти матрицы ПЗС подключены к первому выходу первого ПУ, второй выход которого подключен к управляющим входам первого и второго горизонтальных регистров матрицы ПЗС, а выход второго ПУ подключен к управляющему входу разделительного электрода матрицы ПЗС, выход первого БПЗН которой подключен через первый видеоусилитель сигнального процессора соответственно к входу первого БЗК и к первому информационному входу коммутатора-смесителя, а выход второго БПЗН матрицы ПЗС подключен через второй видеоусилитель сигнального процессора соответственно к входу второго БЗК и ко второму информационному входу коммутатора-смесителя, третий информационный вход которого подключен к выходу первого БЗК, а четвертый информационный вход коммутатора-смесителя - к выходу второго БЗК; прямой выход RS-триггера подключен соответственно к первому управляющему входу ВК, к управляющему входу коммутатора и первому входу элемента «И», а тактовый вход RS-триггера, объединенный с входом счетчика-делителя, - ко второму выходу ВК, второй вход элемента «И» подключен к выходу счетчика-делителя, а выход элемента «И» - соответственно к входу второго ПУ и к первому управляющему входу коммутатора-смесителя, причем S-вход RS-триггера является входом «Пуск» устройства, а R-вход RS-триггера - входом «Стоп» устройства.

В матрице ПЗС прототипа имеют место и дополнительные существенные признаки, а именно: площадь затвора S1 полевого транзистора, выполняющего сбор зарядовых носителей в первом БПЗН, выполнена по критерию минимального внесения в сигнал изображения собственных шумов, а площадь затвора S2 аналогичного полевого транзистора во втором БПЗН - по критерию максимальной управляющей способности зарядового преобразования, при этом S1<S2.

Недостатком прототипа является отсутствие выполнения операции рекурсивной фильтрации.

Задача изобретения - повышение точности рекурсивной фильтрации в результате повышения отношения сигнал/шум выходного сигнала изображения путем дополнительного управления временем накопления задержанной составляющей этого видеосигнала и снижения уровня вносимых шумов.

Поставленная задача в заявляемом устройстве формирования сигнала изображения интерферограмм решается тем, что в устройство прототипа, содержащее последовательно расположенные и оптически связанные объектив и матрицу ПЗС, состоящую из последовательно связанных зарядовой связью фотоприемной секции, первого горизонтального регистра, первого БПЗН, разделительного электрода, секции памяти, второго горизонтального регистра и второго БПЗН; генератор управляющих импульсов, состоящий из последовательно соединенных ВК и первого ПУ и содержащий в своем составе второй ПУ; сигнальный процессор, содержащий первый и второй видеоусилители; первый БЗК; второй БЗК, а также RS-триггер, последовательно соединенные счетчик-делитель и коммутатор, элемент «И» и коммутатор-смеситель, при этом управляющие входы фотоприемной секции и секции памяти матрицы ПЗС подключены к первому выходу первого ПУ, второй выход которого подключен к управляющим входам первого и второго горизонтальных регистров матрицы ПЗС, а выход второго ПУ подключен к управляющему входу разделительного электрода матрицы ПЗС, выход первого БПЗН которой подключен через первый видеоусилитель сигнального процессора соответственно к входу первого БЗК и к первому информационному входу коммутатора-смесителя, а выход второго БПЗН матрицы ПЗС подключен через второй видеоусилитель сигнального процессора соответственно к входу второго БЗК и ко второму информационному входу коммутатора-смесителя, третий информационный вход которого подключен к выходу первого БЗК, а четвертый информационный вход коммутатора-смесителя - к выходу второго БЗК; прямой выход RS-триггера подключен соответственно к первому управляющему входу ВК, к управляющему входу коммутатора и первому входу элемента «И», а тактовый вход RS-триггера, объединенный с входом счетчика-делителя, - ко второму выходу ВК, второй вход элемента «И» подключен к выходу счетчика-делителя, а выход элемента «И» - соответственно к входу второго ПУ и к первому управляющему входу коммутатора-смесителя, причем S-вход RS-триггера является входом «Пуск» устройства, а R-вход RS-триггера - входом «Стоп» устройства прототипа, введены последовательно соединенные аналоговый ключ и взвешивающий сумматор, второй вход которого подключен к первому выходу коммутатора-смесителя, второй выход которого подключен к информационному входу аналогового ключа, управляющий вход которого подключен к прямому выходу RS-триггера, а выход «Видео» взвешивающего сумматора является выходом заявляемого устройства, причем площадь затвора S1 полевого транзистора, выполняющего сбор зарядовых носителей в первом БПЗН матрицы ПЗС, выполнена по критерию максимальной управляющей способности зарядового преобразования, а площадь затвора S2 аналогичного полевого транзистора во втором БПЗН - по критерию минимального внесения в сигнал изображения собственных шумов, при этом S1>S2,

Сопоставительный анализ с прототипом [3] показывает, что заявляемое устройство отличается наличием новых признаков, в том числе:

- новыми конструктивными элементами (блоками), которыми являются аналоговый ключ и взвешивающий сумматор;

- электрическими связями новых блоков в составе устройства;

- взаимным расположением на общем кристалле матрицы ПЗС первого и второго БПЗН.

Совокупность известных и новых признаков заявляемого устройства не известна из уровня техники, поэтому предлагаемое техническое решение соответствует критерию новизны.

В заявляемом решении интервалы накопления смежных кадров (полукадров) в матрице ПЗС не совпадают и разнесены по времени, что увеличивает возможность регулировки степени рекурсивной фильтрации видеосигнала интерферограмм, повышая качество воспроизводимого их изображения на экране видеомонитора за счет роста полезной составляющей видеосигнала. Кроме этого оптимизирован уровень собственных шумов матрицы ПЗС, вносимых в выходной сигнал изображения, благодаря чему дополнительно повышено отношение сигнал/шум.

Следовательно, по техническому результату и методу его достижения предлагаемое решение соответствует критерию о наличии изобретательского уровня.

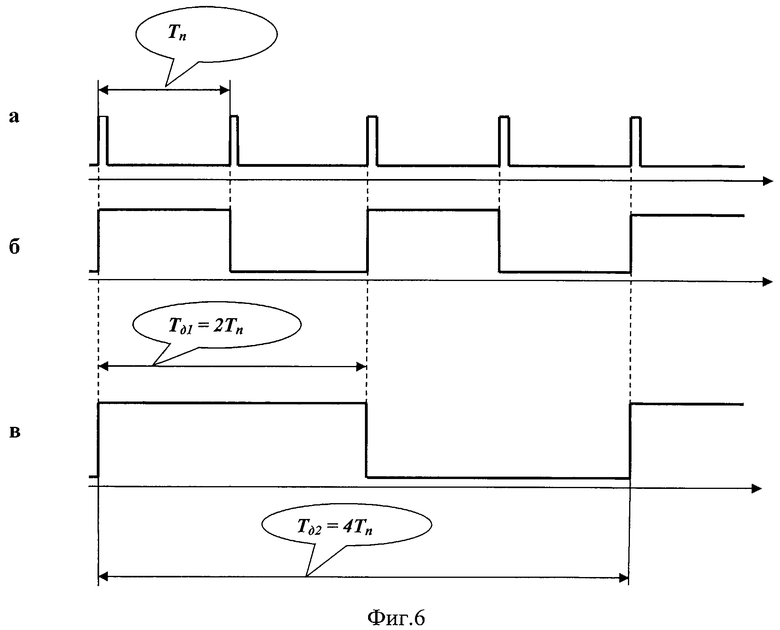

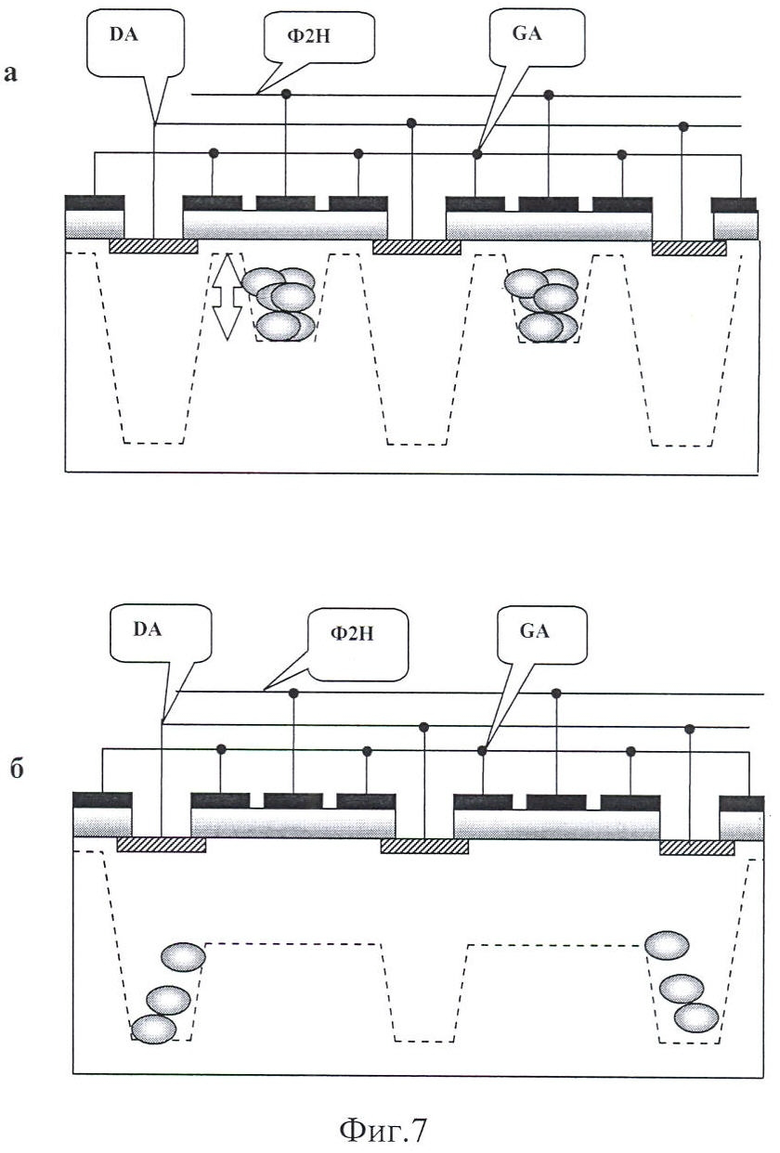

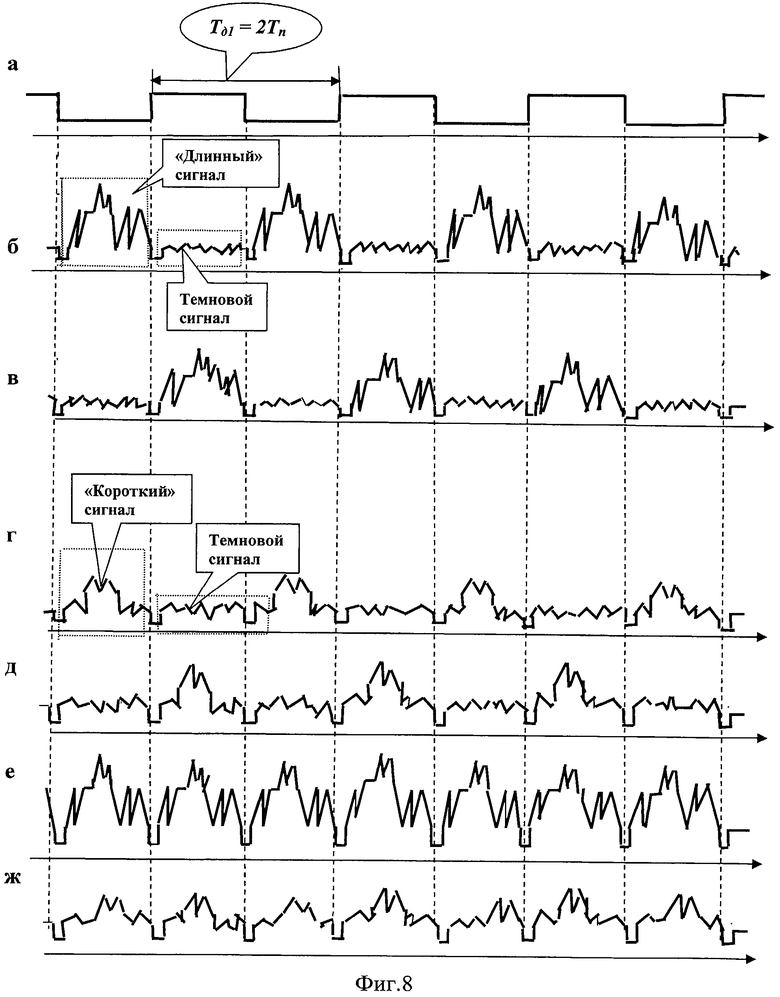

На фиг.1 изображена структурная схема заявляемого устройства; на фиг.2 приведена функциональная схема технологической организации матрицы ПЗС; на фиг.3 показан пример выполнения электрической схемы коммутатора; на фиг.4 - один из возможных вариантов выполнения электрической схемы коммутатора-смесителя; на фиг.5 схематически представлено взаимное расположение интервалов накопления матрицей ПЗС в смежных кадрах (полукадрах); на фиг.6 представлена временная диаграмма, поясняющая работу счетчика делителя; на фиг.7 приведена иллюстрация процесса антиблюмингового стока в матрице ПЗС, на фиг.8 представлена временная диаграмма, поясняющая работу коммутатора-смесителя.

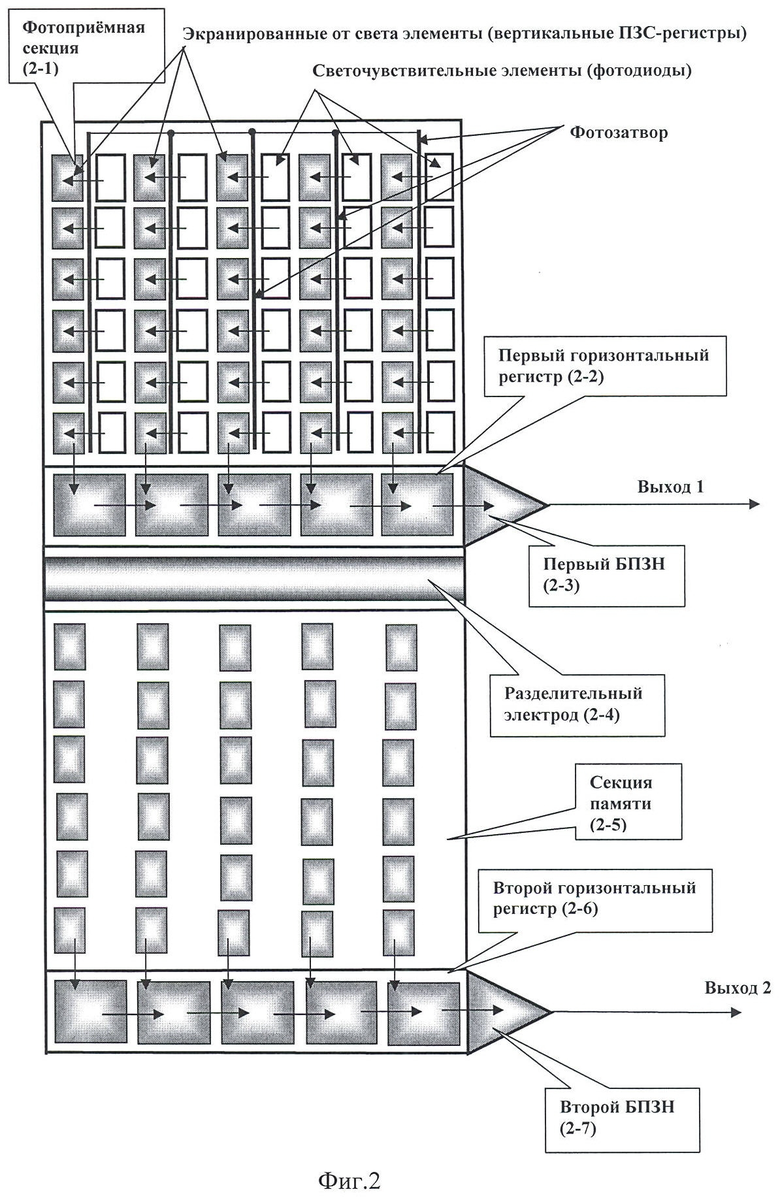

Заявляемое устройство формирования сигнала изображения интерферограмм, см. фиг.1, содержит последовательно расположенные и оптически связанные объектив 1 и матрицу 2 ПЗС, состоящую из последовательно связанных зарядовой связью фотоприемной секции 2-1, первого горизонтального регистра 2-2, первого БПЗН 2-3, разделительного электрода 2-4, секции памяти 2-5, второго горизонтального регистра 2-6 и второго БПЗН 2-7; генератор 3 управляющих импульсов, состоящий из последовательно соединенных ВК 3-1 и первого ПУ 3-2 и содержащий в своем составе второй ПУ 3-3; сигнальный процессор 4, содержащий первый видеоусилитель 4-1 и второй видеоусилители 4-2; а также RS-триггер 5; последовательно соединенные счетчик-делитель 6 и коммутатор 7; первый БЗК 8; второй БЗК 9, коммутатор-смеситель 10; элемент «И» 11; последовательно соединенные аналоговый ключ 12 и взвешивающий сумматор 13, при этом первый выход ПУ 3-2 подключен соответственно к управляющим входам секции 2-1 и секции 2-5, второй выход ПУ 3-2 - соответственно к управляющим входам горизонтального регистра 2-2 и горизонтального регистра 2-6, а выход ПУ 3-3 - к управляющему входу разделительного электрода 2-4; выход БПЗН 2-3 подключен через видеоусилитель 4-1 соответственно к первому информационному входу коммутатора смесителя 10 и к входу БЗК 8, а выход БПЗН 2-7 подключен через видеоусилитель 4-4 соответственно ко второму информационному входу коммутатора-смесителя 10 и к входу БЗК 9; выход БЗК 8 подключен к третьему информационному входу коммутатора-смесителя 10, а выход БЗК 9 - к четвертому информационному входу коммутатора-смесителя 10, прямой выход RS-триггера 5 подключен соответственно к первому управляющему входу ВК 3-1, к управляющему входу коммутатора 7, первому входу элемента «И» 11 и к управляющему входу аналогового ключа 12, а тактовый вход RS-триггера 5, объединенный с входом счетчика-делителя 6, - ко второму выходу ВК 3-1; второй вход элемента «И» 11 подключен к выходу счетчика-делителя 6, а выход элемента «И» 11 - соответственно к входу второго ПУ 3-3 и к управляющему входу коммутатора-смесителя 10, первый выход которого подключен ко второму входу взвешивающего сумматора 13, а второй выход коммутатора-смесителя - к информационному входу аналогового ключа, при этом выход «Видео» взвешивающего сумматора 13 является выходом заявляемого устройства.

Видеосигнал с выхода взвешивающего сумматора 13, как показано на фиг.1, может быть подан на вход видеомонитора 14.

Матрица 2 ПЗС является сенсором видеосигнала в заявляемом устройстве, а по схемотехническому исполнению (см. фиг.2) полностью соответствует прототипу. Фотоприемная секция 2-1 матрицы ПЗС имеет типовую конструкцию для матриц ПЗС с организацией «строчный перенос». Она обеспечивает накопление зарядовых пакетов в светочувствительных элементах, в качестве которых используются фотодиоды, организованные в столбцы. В непосредственной близости от каждого столбца фотодиодов находится нечувствительный к свету вертикальный ПЗС-регистр, отделенный от фотодиодов фотозатвором. Во время накопления зарядовых пакетов в фотодиодах на фотозатвор подается низкий уровень напряжения, обеспечивающий потенциальный барьер между фотодиодами и вертикальным ПЗС-регистром. По окончании накопления на фотозатвор кратковременно подается высокий уровень напряжения, разрешающий перенос зарядовых пакетов из фотодиодов в потенциальные ямы, образованные в вертикальных ПЗС-регистрах.

Фотоприемная секция 2-1 снабжена электронным затвором, выполняющим электронную регулировку чувствительности путем управления временем накопления зарядовых носителей в течение кадрового периода. По сути, электронный затвор является затвором антиблюминговой (стоковой) области GA, технологически выполненной в фотоприемной секции матрицы ПЗС, как показано на фиг.7.

Если на затвор GA подается высокий уровень импульсного смещения, потенциальный барьер снимается, затвор открывается, а на фотомишени исключается процесс накопления фотоэлектронов. Носители зарядов, не задерживаясь в потенциальных ямах под фазными электродами, например под шинами Ф2Н при трехфазной организации переноса, устремляются в более глубокие ямы, создаваемые потенциалом DA стоковой области, а далее рекомбинируют в подложку фотоприемника (см. фиг.7б). Когда на затвор GA матрицы ПЗС подается нижний уровень импульсного смещения, закрывая его, реализуется режим накопления с сокращенным внутри кадра временем сбора носителей (см. фиг.7а).

Зарядовые пакеты из вертикальных ПЗС-регистров секции 2-1 построчно переносятся в горизонтальный регистр 2-2, из которого поэлементно считываются через БПЗН 2-3. Горизонтальный регистр 2-2 и БПЗН 2-3 также являются типовыми представителями матрицы ПЗС со строчным переносом.

На общий кристалл матрицы ПЗС, как и в прототипе, дополнительно введены: разделительный электрод 2-4, секция памяти 2-5, второй горизонтальный регистр 2-6 и второй БПЗН 2-7. Данная функциональная схема технологической организации матрицы ПЗС (см. фиг.2) близка к концепции фотоприемника со строчно-кадровым переносом [4, с.137], отличаясь от нее наличием горизонтального регистра 2-2, разделительного электрода 2-4 и БПЗН 2-3. Разделительный электрод 2-4 разрешает построчный перенос зарядов из вертикальных регистров секции 2-1 сквозь регистр 2-2 в секцию памяти 2-5 или изолирует секцию 2-5 от такого переноса. Число элементов в каждом столбце секции 2-5 равно числу элементов вертикального регистра секции 2-1. Под секцией 2-5 расположен горизонтальный регистр 2-6, который организован точно так же, как и регистр 2-2, а заканчивается БПЗН 2-7.

Блок 2-7, как и блок 2-3, предназначен для осуществления преобразования зарядового сигнала изображения в напряжение видеосигнала. Принципиальным их отличием является различный уровень зарядовых пакетов на входе, который учитывается при конструктивном исполнении полевого транзистора в части емкости его затвора. Для БПЗН 2-3 ожидается высокий уровень зарядового сигнала, поэтому необходимо увеличить управляющую способность блока путем увеличения площади затвора (S1). Напротив, для БПЗН 2-7 предполагается низкий уровень зарядового сигнала, поэтому емкость затвора должна быть предельно малой, что достигается выбором геометрии его размеров, обеспечивающей малую площадь (S2). Так что обязательным при конструировании нагрузочных транзисторов является условие: S1>S2.

Генератор 3 управляющих импульсов предназначен для осуществления развертки в матрице 2 ПЗС и формирования служебных импульсов для сигнального процессора 4. Входящий в его состав ВК 3-1 может быть выполнен в виде большой интегральной схемы (БИС), например микросхемы CXD2463R фирмы Sony [5]. Остальные блоки генератора 3 управляющих импульсов, а именно: ПУ 3-2 и ПУ 3-3, которые предназначены для преобразования уровней логических сигналов в уровни сигналов, необходимые для работы матрицы ПЗС, могут быть реализованы в виде второй БИС необходимого комплекта.

Как и в прототипе, особенностью ВК 3-1 в заявляемом решении является наличие первого и второго управляющих входов.

Применительно к микросхеме CXD2463R первым управляющим входом является вывод 20. Если необходимо включить автоматическую регулировку времени накопления (АРВН) в телекамере, нужно подать на этот вывод логический «0», для переключения в режим ручного управления временем накопления - логическую «1» в уровнях ТТЛ.

Второй управляющий вход микросхемы CXD2463R образуют выводы 11, 12, 13. Для работы телекамеры в режиме АРВН эти выводы должны «висеть в воздухе», т.к. на них с помощью высокоомных резистивных делителей поданы соответствующие потенциалы в диапазоне 1,3-3,5 вольт. Если необходимо переключение восьми значений фиксированных экспозиций в диапазоне от 10 мкс до 10 мс, то на них должны быть поданы кодовые комбинации из нулей («0») и единиц («1»), указанные в приведенной ниже табл.1.

В настоящем решении используются шесть кодовых комбинаций: «000» - 10 мкс; «100» - 100 мкс; «011» - 200 мкс; «110» - 500 мкс; «001» - 1000 мкс; «111» - 10000 мкс.

Отметим, что комбинация «000» определяет самую короткую длительность накопления, а комбинация «111» - самую длинную. Установка всех этих кодовых комбинаций выполняется в коммутаторе 7.

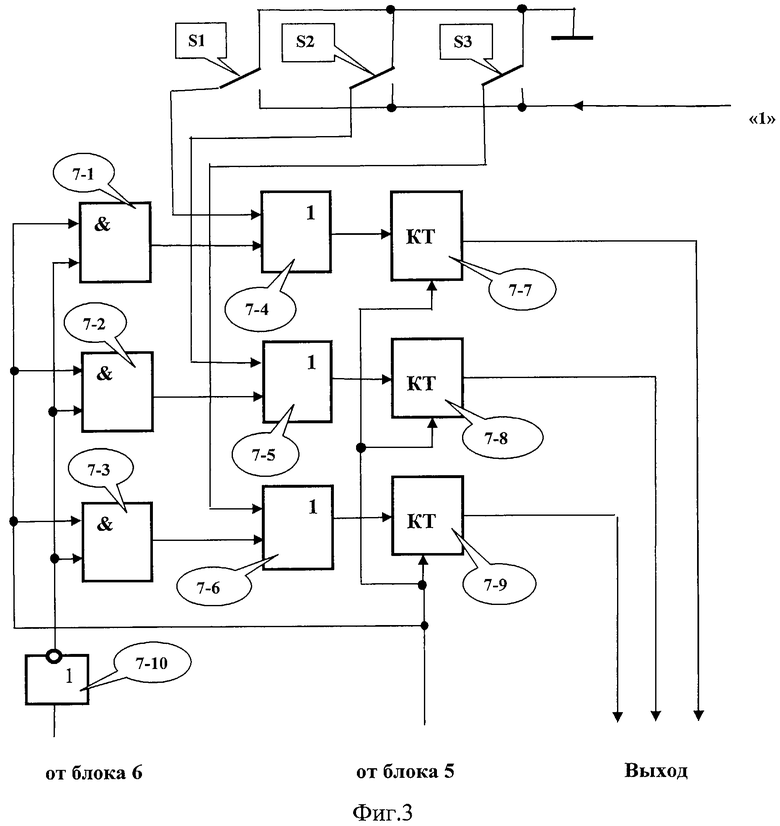

Возможная электрическая схема этого блока (см. фиг.3) содержит первый элемент «И» 7-1, второй элемент «И» 7-2, третий элемент «И» 7-3, первый элемент «ИЛИ» 7-4, второй элемент «ИЛИ» 7-5, третий элемент «ИЛИ» 7-6, первый коммутатор 7-7, второй коммутатор 7-8, третий коммутатор 7-9, инвертор 7-10, а также первый переключатель S1, второй переключатель S2 и третий переключатель S3.

Допустим, что переключатели S1…S3 находятся в исходном (отжатом) положении. Тогда при подаче высокого логического уровня сигнала от блока 5 на входы разрешения коммутаторов 7-7, 7-8, 7-9 и низкого логического уровня сигнала от блока 6 на инвертор 7-10 на выходе коммутатора 7 формируется логическая комбинация «111».

Когда же в исходном положении переключателей S1…S3 и наличии на входах разрешения коммутаторов логической «1» на инвертор 7-10 от блока 6 будет подана тоже «1», на выходе блока 7 установится комбинация «000».

При подаче уровня логической «1» от блока 5 и сохранении уровня логической «1», поступающей от блока 6, могут быть получены четыре дополнительных кодовых комбинаций в зависимости от положения переключателей S1…S3, как представлено в табл.2.

Очевидно, что выбор положения переключателей S1…S3 позволяет осуществить регулировку «короткого» времени накопления в матрице 2 ПЗС от 10 до 1000 мкс.

Если на входы разрешения коммутаторов 7-7, 7-8, 7-9 будет подан низкий логический уровень, тогда, независимо от состояния на входах элементов «И» 7-1,

7-2, 7-3 и положения переключателей S1…S3, выходы коммутаторов будут изолированы от входов.

Сигнальный процессор 4 при помощи первого 4-1 и второго 4-2 видеоусилителей выполняет двухканальное усиление и обработку сигналов изображения с выходов матрицы ПЗС и формирование на первом и втором выходах полных телевизионных сигналов (композитных видеосигналов). Сигнальный процессор 4 может быть выполнен в виде одной БИС или двух микросхем CXA1310AQ фирмы Sony [6]. Следует отметить, что для работы в режиме прототипа в видеоусилителе 4-1 (см. фиг.1) вырабатывается управляющий сигнал на ВК 3-1, который необходим для реализации автоматической регулировки времени накопления (АРВН) фотоприемника.

Первый БЗК 8 и второй БЗК 9 предназначены для выполнения задержки входного видеосигнала на длительность одного кадра. Если в устройстве использована прогрессивная развертка с частотой кадров 50 Гц, то длительность задержки составляет 20 мс. При организации в устройстве стандартной чересстрочной развертки длительность требуемой задержки будет составлять два полукадра, т.е. 40 мс. Техническая реализация блоков 8 и 9 не отличается от выполнения аналогичных блоков прототипа и может быть осуществлена путем последовательного соединения аналого-цифрового преобразователя (АЦП), оперативно-запоминающего устройства (ОЗУ) и цифроаналогового устройства (ЦАП).

Счетчик-делитель 6 предназначен для выполнения деления частоты импульсов КСИ на два (с 50 Гц до 25 Гц) при прогрессивной развертке и соответственно на четыре (с 50 Гц до 12,5 Гц) при чересстрочной развертке видеосигнала. Работа счетчика-делителя 6 в режиме прогрессивной развертки иллюстрируется на фиг.6, где на эпюре 6а показаны импульсы КСИ с периодом Тn, на эпюре 6б - выходные импульсы, следующие с периодом 2Тn.

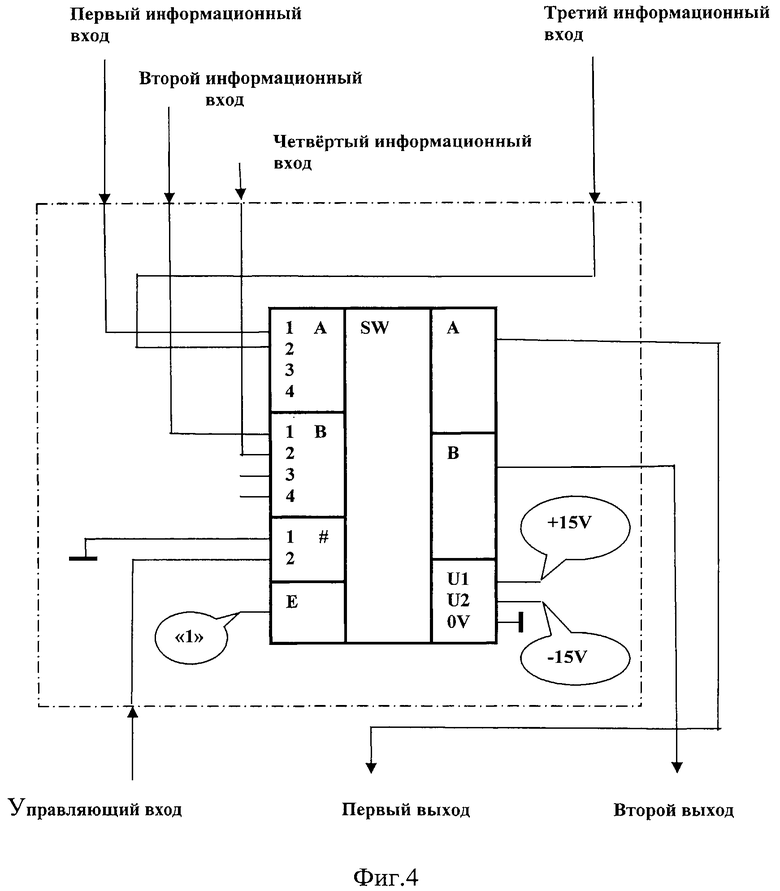

Коммутатор-смеситель 10 предназначен для промежуточного синтеза видеосигнала устройства. Электрическая схема блока 10 может быть выполнена на базе микросхемы КР590КН3 [7, с.450-451], как предложено на фиг.4.

В зависимости от уровней логических сигналов, подаваемых на управляющий вход #2, при условии подключения входа #1 к логическому нулю, а входа Е к логической «1», в соответствии с табл.3 истинности открываются два из четырех каналов, а именно: 1А и 1В или 2А и 2В.

Временная диаграмма, иллюстрирующая работу коммутатора-смесителя 10, показана на фиг.8, где на эпюре 8а представлен сигнал, подаваемый на управляющий вход блока 10. На эпюре 8б показан видеосигнал, поступающий на первый информационный вход блока 10, на эпюре 8г - на второй информационный вход, на эпюре 8в - на третий информационный вход, а на эпюре 8д - на четвертый информационный вход. В результате на первом выходе блока 10 формируется видеосигнал, изображенный на эпюре 8е, а на втором выходе - видеосигнал, показанный на эпюре 8ж.

Объектив 1, RS-триггер 5, счетчик-делитель 6 и элемент «И» 11 по схемотехническому выполнению не отличаются от аналогичных блоков прототипа. Добавим, что RS-триггер 5 является тактируемым триггерным устройством RS-типа с высоким активным уровнем на входах управления.

Аналоговый ключ 12 может быть выполнен на базе одного из четырех управляемых ключей с нормально разомкнутыми контактами отечественной микросхемы КР590КН2 [7].

Взвешивающий сумматор 13 предназначен для выполнения операции сложения двух входных видеосигналов с весовыми (масштабными) коэффициентами и может быть выполнен по рекомендациям монографии [8]. Для видеосигнала, поступающего на его первый вход, весовой коэффициент К является регулируемым, который выбирается из неравенства 0<К<1.

Для видеосигнала, поступающего на его второй вход, весовой коэффициент должен быть равен единице (K=1).

Заявляемое устройство формирования сигнала изображения интерферограмм (см. фиг.1) работает следующим образом.

Предположим, что расположенная в поле зрения устройства интерфенционная картина объекта находится в идеально статическом положении, не испытывая случайных колебаний за счет вибрации и других регулярных механических воздействий низкой частоты. При этом допустим, что само устройство работает в режиме прогрессивной развертки, а освещенность объекта контроля позволяет установить рабочую освещенность на мишени матрицы ПЗС, необходимую для получения видеосигнала с максимальным отношением сигнал/шум.

В исходном положении на первом управляющем входе ВК 3-1 присутствует низкий логический уровень. Такой же уровень сигнала устанавливается на выходе элемента «И» 11, на выходе ПУ 3-3, на разделительном электроде 2-4 матрицы 2 ПЗС и на управляющем входе коммутатора-смесителя 10. Аналоговый ключ 12 находится в состоянии «разомкнуто».

Автоматическая регулировка времени накопления (АРВН) матрицы 2 ПЗС установит максимальную величину текущей экспозиции, т.е. длительность накопления информационных зарядов составит 10000 мкс. Разделительный электрод 2-4 «изолирует» регистр 2-2 от секции 2-5, поэтому сигнал изображения будет считываться из него поэлементно в БПЗН 2-3. Сформированный далее на выходе видеоусилителя

4-1 композитный видеосигнал будет воспроизводиться на экране видеомонитора 14.

При этом на втором выходе ВК 3-1 формируются кадровые синхроимпульсы (КСИ) с периодом Тn (см. фиг.6а), а счетчик-делитель 6 выполняет деление входной частоты на два, формируя на выходе меандр с периодом Т∂1=2Тn (см. фиг.6б).

Пусть на объекте контроля возникает низкочастотное механическое воздействие. Тогда в формируемом видеосигнале неизбежно появляется смаз, а в наблюдаемом с экрана видеомонитора 14 изображении заметно ухудшается его качество за счет снижения отношения сигнал/шум.

Для выполнения задачи изобретения на вход «Пуск» устройства подается импульс положительной полярности. В момент совпадения на «S»-входе RS-триггера 5 высокого уровня этого импульса с высоким уровнем КСИ на его тактовом входе состояние триггера изменяется. На прямом выходе триггера 5 устанавливается сигнал логической «1».

Последний подается соответственно на управляющий вход блока 7, на первый управляющий вход ВК 3-1, на первый вход элемента «И» 11 и на управляющий вход аналогового ключа 8. Поэтому схема АРВН в матрице 2 ПЗС отключается, второй управляющий вход ВК 3-1 оказывается подключенным к выходу блока 7, а на управляющий вход коммутатора-смесителя 10 поступает с выхода блока 6 импульсный меандр с периодом Т∂1=2Тn. Одновременно аналоговый ключ 12 устанавливается в состояние «замкнуто», соединяя второй выход блока 10 со вторым информационным входом блока 13.

При подключении второго управляющего входа ВК 3-1 к выходу коммутатора 7 на этом входе на время низкого уровня меандра импульсов с выхода блока 6 устанавливается логическая комбинация «111», обеспечивающая длительность кадрового накопления зарядов в фотоприемнике, равной 10000 мкс -  (см. табл.1).

(см. табл.1).

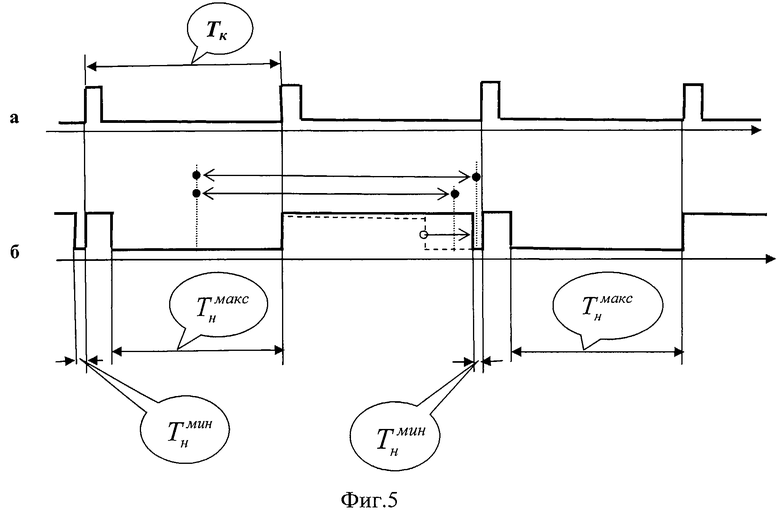

По отношению к кадровому бланку, показанному на фиг.5а, импульсный сигнал, подаваемый на электронный затвор GA матрицы ПЗС в этой ситуации, представлен на фиг.5б.

Низкий уровень меандра с выхода блока 6 означает и такой же уровень на выходе элемента «И» 11, а также на разделительном электроде 2-4. Поэтому для секции 2-1 на это время будет продолжаться «изоляция» от секции 2-5, а считывание накопленных зарядовых пакетов осуществляется построчно в регистр 2-2, а из него - поэлементно в БПЗН 2-3. Обозначим условно этот видеосигнал, снимаемый с первого выхода матрицы 2 ПЗС, «длинным» сигналом из-за прямой зависимости его уровня от длительного (10000 мкс) накопления зарядового кадра.

Когда же с выхода блока 6 будет подан высокий уровень меандра импульсов, тогда на это время на втором управляющем входе ВК 3-1 устанавливается логическая комбинация «000», гарантирующая длительность кадрового накопления зарядов в фотоприемнике, равной 10 мкс -  (см. табл.1). Если же дополнительно «уйти» от исходного положения «Отжато» для переключателей S1…S3 коммутатора 7 (см. фиг.3), то можно установить на втором управляющем входе другие четыре логические комбинации «100», «010», «110» и «001» (см. табл.2), которые обеспечат длительность кадрового накопления матрицы 2 ПЗС соответственно 100, 200, 500 и 1000 мкс.

(см. табл.1). Если же дополнительно «уйти» от исходного положения «Отжато» для переключателей S1…S3 коммутатора 7 (см. фиг.3), то можно установить на втором управляющем входе другие четыре логические комбинации «100», «010», «110» и «001» (см. табл.2), которые обеспечат длительность кадрового накопления матрицы 2 ПЗС соответственно 100, 200, 500 и 1000 мкс.

Отметим, что во время действия высокого уровня меандра на разделительном электроде 2-4 тоже устанавливается высокий уровень. Поэтому он разрешает для зарядовых пакетов накопленного кадра построчный их перенос из секции 2-1 сквозь регистр 2-2 в секцию 2-5 и хранение зарядов в ней до момента наступления очередного промежутка Тn «изоляции».

В последующем интервале Тn выполняется построчный перенос каждой строки этого зарядового кадра в регистр 2-6 и считывание каждого элемента строки в БПЗН 2-7. Обозначим условно этот видеосигнал, снимаемый со второго выхода матрицы 2 ПЗС, «коротким» сигналом из-за прямой зависимости его уровня от кратковременного накопления зарядового кадра.

Необходимо отметить, что «длинный» сигнал на первом выходе матрицы 2 ПЗС (см. фиг.8б) и «короткий» сигнал на ее втором выходе (см. фиг.8г) следуют с периодом 2Тn, а в течение паузы (интервала Тn) регистры 2-3 и 2-6 матрицы ПЗС параллельно осуществляют считывание темнового сигнала и удаляют паразитную информацию из фотоприемника, но создают пропуски информативного сигнала.

Видеосигнал с первого выхода матрицы 2 ПЗС поступает на вход видеоусилителя

4-1 сигнального процессора 4, а с его выхода - на первый информационный вход коммутатора-смесителя 10 и на вход первого БЗК 8. Одновременно видеосигнал со второго выхода матрицы 2 ПЗС подается на вход видеоусилителя 4-2, а с выхода - на второй информационный вход коммутатора-смесителя 10 и на вход второго БЗК 9 соответственно.

Задержанный на кадр видеосигнал (см. фиг.8в) с выхода БЗК 8 поступает на третий информационный вход коммутатора-смесителя 10, а задержанный на кадр видеосигнал (см. фиг.8д) с выхода БЗК 9 - на четвертый информационный вход блока 10.

Не имеющий информативных пропусков «длинный» видеосигнал (см. фиг.8е) формируется на первом выходе коммутатора-смесителя 10 и поступает на второй вход взвешивающего сумматора 13. Аналогично, «короткий» видеосигнал без пропусков (см. фиг.8ж) вырабатывается на втором выходе блока 10, а подается далее на первый вход блока 13.

В блоке 13 осуществляется синтез выходного сигнала изображения заявляемого устройства путем выполнения операции суммирования входных видеосигналов с необходимыми весовыми коэффициентами. Предусмотренная по первому входу блока 13 регулировка весового коэффициента К в пределах 0<K<1 позволяет изменить степень рекурсивности реализуемой фильтрации видеосигнала.

С учетом того, что считывание «короткого» видеосигнала выполняется через БПЗН 2-7, выполненный по критерию минимального внесения в сигнал изображения собственных шумов матрицы ПЗС, будем иметь выигрыш в отношении сигнал/шум. Теоретически среднеквадратичное отклонение (СКО) шума считывания может быть снижено на порядок, см. [9, с.52].

С другой стороны, в заявляемом решении суммируемые видеосигналы фиксируют различные состояния процесса накопления информационных зарядов во времени. Своеобразной иллюстрацией этого процесса для предлагаемого решения является временная диаграмма на фиг.5б. Временные «центры тяжести» суммируемых видеосигналов (они помечены на фиг.5 кружками с заливкой) могут регулироваться относительно друг друга за счет управления длительностью накопления «короткого» видеосигнала.

Поэтому, выбирая при помощи переключателей S1…S3 в коммутаторе 7 длительность накопления  , можно дополнительно регулировать степень рекурсивности фильтруемого выходного изображения, реализуя имеющийся резерв повышения отношения сигнал/шум за счет роста самого видеосигнала.

, можно дополнительно регулировать степень рекурсивности фильтруемого выходного изображения, реализуя имеющийся резерв повышения отношения сигнал/шум за счет роста самого видеосигнала.

Предположим, что устройство работает в режиме чересстрочной развертки. Тогда на втором выходе ВК 3-1 формируются импульсы с периодом полукадров Тn. Счетчик-делитель 6 выполняет деление входной частоты на четыре, т.е. период выходных импульсов будет составлять: Т∂2=4Тn (см. фиг.6в). В течение действия низкого уровня этого меандра в матрице 2 ПЗС будет выполняться не один, а два цикла экспонирования с «длинным» зарядовым накоплением по  для каждого. Аналогично, в течение действия высокого уровня меандра в ПЗС будет совершаться не один, а два цикла экспонирования с «коротким» зарядовым накоплением по

для каждого. Аналогично, в течение действия высокого уровня меандра в ПЗС будет совершаться не один, а два цикла экспонирования с «коротким» зарядовым накоплением по  .

.

При этом БЗК 8 и БЗК 9 осуществляют задержку входного видеосигнала на два полукадра, т.е. по длительности на два Тn.

В остальном работа устройства не отличается от ее функционирования в режиме прогрессивной развертки.

При необходимости возвращения устройства в исходный режим работы следует подать импульс положительной полярности на вход «Стоп». В момент совпадения на «R»-входе RS-триггера 5 высокого уровня этого импульса с высоким уровнем тактовых импульсов (КСИ) состояние триггера изменяется. На прямом выходе RS-триггера 5 установится сигнал логического «0», а в матрице 2 ПЗС будет восстановлено функционирование схемы АРВН. Одновременно будет восстановлено состояние «разомкнуто» для аналогового ключа 12, благодаря подаче сигнала логического «0» на его управляющий вход. На первом входе взвешивающего сумматора 13 видеосигнал будет отсутствовать, поэтому на его выход будет передаваться только видеосигнал со второго входа с единичным весовым коэффициентом.

По сравнению с аналогом [1], предлагаемое устройство формирования сигнала изображения интерферограмм исключает необходимость разделения входного светового потока по двум направлениям. Поэтому принципиально устраняется возможная неточность рекурсивной фильтрации видеосигнала из-за ошибки оптического рассовмещения смежных кадров при накоплении информационных зарядов.

В настоящее время все элементы структурной схемы устройства формирования сигнала изображения интерферограмм освоены или могут быть освоены отечественной промышленностью. Поэтому следует считать предлагаемое изобретение соответствующим требованию о промышленной применимости.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Патент №2068624 РФ. МПК H04N 5/225, 7/18. Устройство формирования сигнала изображения интерферограмм / В.М.Смелков // Б.И. - 1996. - №30.

2. Патент №2362275 РФ. МПК H04N 5/225. Телевизионная камера для наблюдения в условиях сложной освещенности и/или сложной яркости объектов / В.М.Смелков // Б.И. - 2009. - №20.

3. Решение о выдаче патента РФ на изобретение по заявке №2009145587 (064988) от 30.11.2010. МПК H04N 5/225. Телевизионная камера для наблюдения в условиях сложной освещенности и/или сложной яркости объектов / В.М.Смелков.

4. Владо Дамьяновски. CCTV. Библия видеонаблюдения. Цифровые и сетевые технологии / Перевод с англ. - М.: ООО «Ай-Эс-Эс Пресс», 2006.

5. Микросхема CXD2463R фирмы Sony. Timing Controller for CCD Camera. Инструкция для пользователя на английском языке, с.1-12.

6. Микросхема CXA1310AQ фирмы Sony. Single Chip Processing for CCD Camera. Инструкция для пользователя на английском языке, с.1-14.

7. Цифровые и аналоговые интегральные микросхемы: Справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. - М.: «Радио и связь», 1990.

8. Фолкенберри Л. Применение операционных усилителей и линейных ИС: Перевод с англ. - М.: «Мир», 1985.

9. Никитин В.В., Цыцулин А.К. Телевидение в системах физической защиты. С-Пб.: СПбГЭТУ «ЛЭТИ», 2001.

Изобретение относится к телевизионной технике и преимущественно может быть использовано для анализа интерферограмм оптических изделий, выполняемого в телевизионных системах. Техническим результатом является повышение точности рекурсивной фильтрации в результате повышения отношения сигнал/шум выходного сигнала изображения путем дополнительного управления временем накопления задержанной составляющей этого видеосигнала и снижения уровня вносимых шумов. Результат достигается тем, что в устройство прототипа введены последовательно соединенные аналоговый ключ и взвешивающий сумматор, второй вход которого подключен к первому выходу коммутатора-смесителя, второй выход которого подключен к информационному входу аналогового ключа, управляющий вход которого подключен к прямому выходу RS-триггера, а выход «Видео» взвешивающего сумматора является выходом заявляемого устройства, причем в коммутаторе реализованы дополнительные отсчеты интервала накопления информационных зарядов в матрице ПЗС, площадь затвора S1 полевого транзистора, выполняющего сбор зарядовых носителей в первом БПЗН матрицы ПЗС, выполнена по критерию максимальной управляющей способности зарядового преобразования, а площадь затвора S2 аналогичного полевого транзистора во втором БПЗН - по критерию минимального внесения в сигнал изображения собственных шумов, при этом S1>S2. 1 з.п. ф-лы, 8 ил, 3 табл.

1. Устройство формирования сигнала изображения интерферограмм, содержащее последовательно расположенные и оптически связанные объектив и матрицу приборов с зарядовой связью (матрицу ПЗС), состоящую из последовательно связанных зарядовой связью фотоприемной секции, первого горизонтального регистра, первого блока преобразования заряда в напряжение (БПЗН), разделительного электрода, секции памяти, второго горизонтального регистра и второго БПЗН, генератор управляющих импульсов, состоящий из последовательно соединенных временного контроллера (ВК) и первого преобразователя уровней (ПУ) и содержащий в своем составе второй ПУ, сигнальный процессор, содержащий первый и второй видеоусилители, первый блок задержки на кадр (БЗК), второй БЗК, а также RS-триггер, последовательно соединенные счетчик-делитель и коммутатор, элемент «И» и коммутатор-смеситель, при этом управляющие входы фотоприемной секции и секции памяти матрицы ПЗС подключены к первому выходу первого ПУ, второй выход которого подключен к управляющим входам первого и второго горизонтальных регистров матрицы ПЗС, а выход второго ПУ подключен к управляющему входу разделительного электрода матрицы ПЗС, выход первого БПЗН которой подключен через первый видеоусилитель сигнального процессора соответственно к входу первого БЗК и к первому информационному входу коммутатора-смесителя, а выход второго БПЗН матрицы ПЗС подключен через второй видеоусилитель сигнального процессора соответственно к входу второго БЗК и ко второму информационному входу коммутатора-смесителя, третий информационный вход которого подключен к выходу первого БЗК, а четвертый информационный вход коммутатора-смесителя - к выходу второго БЗК; прямой выход RS-триггера подключен соответственно к первому управляющему входу ВК, к управляющему входу коммутатора и первому входу элемента «И», а тактовый вход RS-триггера, объединенный с входом счетчика-делителя, - ко второму выходу ВК, второй вход элемента «И» подключен к выходу счетчика-делителя, а выход элемента «И» - соответственно к входу второго ПУ и к первому управляющему входу коммутатора-смесителя, причем S-вход RS-триггера является входом «Пуск» устройства, а R-вход RS-триггера - входом «Стоп» устройства прототипа, отличающееся тем, что в него введены последовательно соединенные аналоговый ключ и взвешивающий сумматор, второй вход которого подключен к первому выходу коммутатора-смесителя, второй выход которого подключен к информационному входу аналогового ключа, управляющий вход которого подключен к прямому выходу RS-триггера, а выход «Видео» взвешивающего сумматора является выходом заявляемого устройства, причем в коммутаторе реализованы дополнительные отсчеты интервала накопления информационных зарядов в матрице ПЗС, площадь затвора S1 полевого транзистора, выполняющего сбор зарядовых носителей в первом БПЗН матрицы ПЗС, выполнена по критерию максимальной управляющей способности зарядового преобразования, а площадь затвора S2 аналогичного полевого транзистора во втором БПЗН - по критерию минимального внесения в сигнал изображения собственных шумов, при этом S1>S2.

2. Устройство по п.1, отличающееся тем, что счетчик-делитель в режиме прогрессивной развертки сигнала изображения является делителем входной частоты на два, а в режиме чересстрочной развертки - делителем на четыре, при этом в режиме прогрессивной развертки первый и второй БЗК являются блоками задержки на кадр, а в режиме чересстрочной развертки - блоками задержки на два полукадра.

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ ИНТЕРФЕРОГРАММ | 1992 |

|

RU2068624C1 |

| JP 2009217231 А, 2009.09.24 | |||

| US 4523846 А, 1985.06.18 | |||

| ИНТЕРФЕРОМЕТР | 2002 |

|

RU2239157C2 |

| US 5465147 А, 1995.11.07. | |||

Авторы

Даты

2012-03-27—Публикация

2011-03-29—Подача