Область техники, к которой относится изобретение

Настоящее изобретения относится к системам связи, использующим коды с низкой плотностью проверок на четность (LDPC).

Уровень техники

В беспроводных системах связи производительность линии связи значительно снижается вследствие наличия различных шумов в каналах, затухания, и межсимвольной интерференции (ISI). Таким образом, для реализации высокоскоростных цифровых систем связи, требующих высокой пропускной способности и надежности, например, мобильных систем связи следующего поколения, цифрового вещания и мобильного интернета, необходимо разработать технологию, решающую проблему шумов, затухания и ISI. Недавно были выполнены обширные исследования в отношении использования кода с коррекцией ошибок для увеличения надежности связи путем эффективного восстановления искаженной информации.

Код LDPC, который впервые был рассмотрен Галагером (Gallager) в 60-х годах, использовался недостаточно широко из-за его сложной реализации, которая не могла быть осуществлена на том технологическом уровне. Однако турбокод, который был открыт К.Берроу (C.Berrou), А.Главье (A.Glavieux) и П.Ситимашимой (P. Thitimajshima) в 1993, обеспечивал производительность, приближающуюся к пределу Шеннона для канала. Таким образом, были выполнены исследования по итеративному декодированию и кодированию канала на основе графов, а также анализ производительности и характеристик турбокода. В результате этих исследований код LDPC был повторно изучен в начале 90-х, что показало, что код LDPC имеет производительность, приближающуюся к пределу Шеннона для канала, если декодирование выполняется с использованием итеративного декодирования, основанного на алгоритме “сумма-произведение” на графе Таннера (специальный случай фактор-графа), соответствующего коду LDPC.

Код LDPC обычно представляют с использованием методики представления графов, и многие их характеристики могут быть проанализированы с помощью методов, основанных на теории графов, алгебре и теории относительности. В общем случае, граф-модель кодов канала является удобной для описания кодов. С помощью отображения информации кодированных битов на вершины графа и отображения отношений между битами на ребра графа возможно рассмотреть сеть связи, в которой вершины обмениваются заранее заданными сообщениями через ребра. Это позволяет разработать естественный алгоритм декодирования. Например, алгоритм декодирования, разработанный на основе решетки, которую можно рассматривать как частный случай графа, может включать в себя хорошо известный алгоритм Витерби и алгоритм BCJR (Bahl - Cocke - Jelinek - Raviv).

Код LDPC обычно определяют с помощью матрицы проверки четности и может быть переставлен в виде двудольного графа, называемого графом Таннера. В двудольном графе вершины, составляющие граф, относятся к двум различным типам, и код LDPC представляется двухкомпонентном графом, составленным из вершин, некоторые из которых называются узлами переменных, а остальные называются проверочными узлами. Узлы переменных однозначно отображаются на кодируемые биты.

Ниже со ссылками на фиг.1 и 2 приводится описание способа представления через граф кода LDPC.

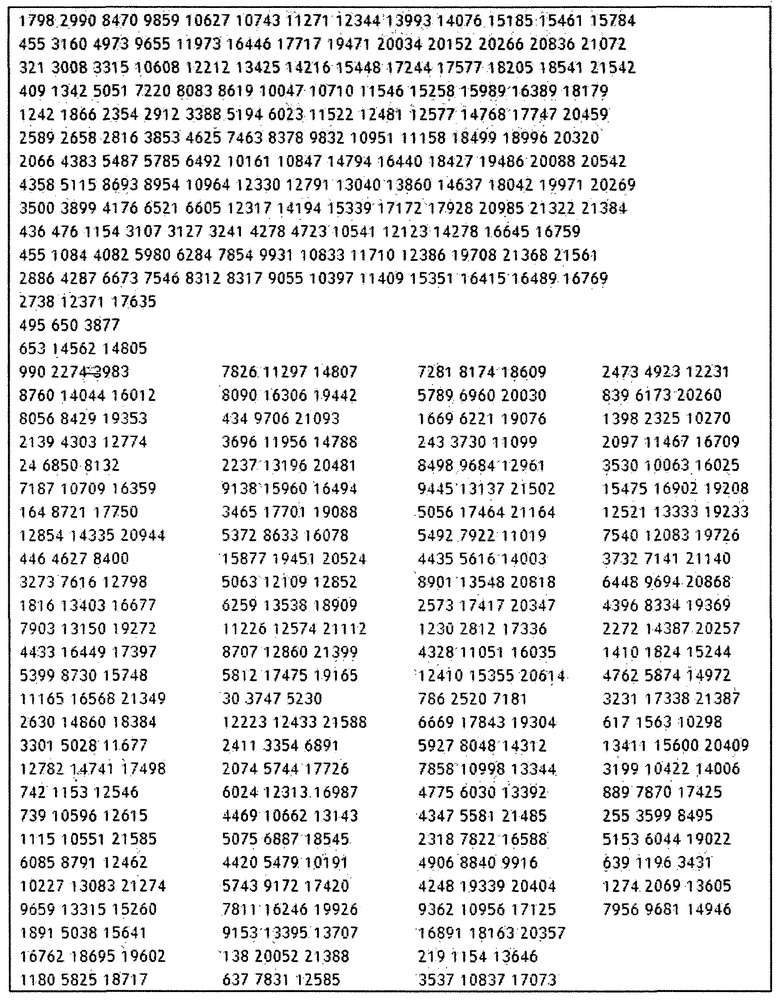

На фиг.1 показан пример матрицы H1 проверки четности кода LDPC, содержащей 4 строки и 8 столбцов. Как видно из фиг.1, поскольку количество столбцов равно 8, код LDPC генерирует кодовое слово длины 8, и столбцы отображаются в 8 кодированных битов.

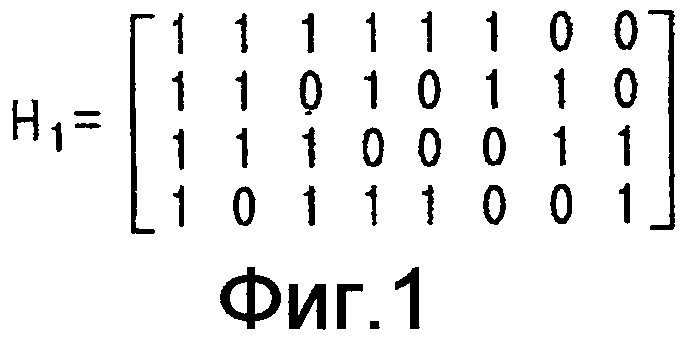

На фиг.2 показана диаграмма, иллюстрирующая граф Таннера, соответствующий H1 по фиг.1.

Как показано на фиг.2, граф Таннера кода LDPC содержит 8 узлов переменных x, (202), x2 (204), x3 (206), x4 (208), x5 (210), x6 (212), x7 (214) и x8 (216), и 4 проверочных узла 218, 220, 222 and 224. i-й столбец и j-я строка в матрице H1 проверки четности отображаются соответственно на узел xi переменной и j-й проверочный узел. Помимо этого, значение 1, т.е. ненулевое значение, в точке, где пересекаются i-й столбец и j-я строка в матрице H1 проверки четности кода LDPC, указывает, что существует ребро между узлом xi переменной и j-м проверочным узлом в графе Таннера, как показано на фиг.2.

В графе Таннера кода LDPC степень узла переменной и проверочного узла определяют как количество ребер, входящих в каждый соответствующий узел, и эта степень равна количеству ненулевых значений в столбце или строке, соответствующих ассоциированному узлу в матрице проверки четности кода LDPC. Например, на Фиг.1 степени узлов переменных x1 (202), x2 (204), x3 (206), x4 (208), x5 (210), x6 (212), x7 (214) и x8 (216) составляют соответственно 4, 3, 3, 3, 2, 2, 2 и 2, а степени проверочных узлов 218, 220, 222 и 224 составляют соответственно 6, 5, 5 и 5. Помимо этого, количество ненулевых значений в столбцах матрице H1 проверки четности по фиг.1, которые соответствуют узлам переменных по фиг.2, равно их степеням 4, 3, 3, 3, 2, 2, 2 и 2. Количество ненулевых значений в сторках матрице H1 проверки четности по фиг.1, которые соответствуют проверочным узлам по Фиг.2, равно их степеням 6, 5, 5 и 5.

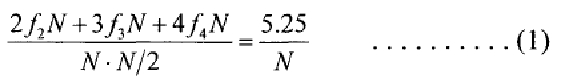

Для того чтобы выразить распределение степеней для узлов кода LDPC, отношение количества узлов переменных степени degree-i к полному количеству узлов переменных определяют как fi, а отношение количества проверочных узлов степени degree-j к полному количеству проверочных узлов определяют как gj. Например, для кода LDPC, соответствующего фиг.1 и 2, f2=4/8, f3=3/8, f4=l/8, и fi =0 для i≠2, 3, 4; и g5=3/4, g6=l/4, и gj=0 для j≠5, 6. Если длина кода LDPC, т.е. количество столбцов, определена как N, а количество строк определено как N/2, плотность ненулевых значений в матрице проверки четности, имеющей приведенное выше распределение степеней, вычисляют по Уравнению (1).

В Уравнении (1) при увеличении N количество единиц в матрице проверки четности уменьшается. В общем случае для кода LDPC, поскольку длина N кода обратно пропорциональна плотности ненулевых значений, код LDPC с большим N имеет очень низкую плотность ненулевых значений. Наличие выражения “низкая плотность” в названии кода LDPC основано на описанном выше соотношении.

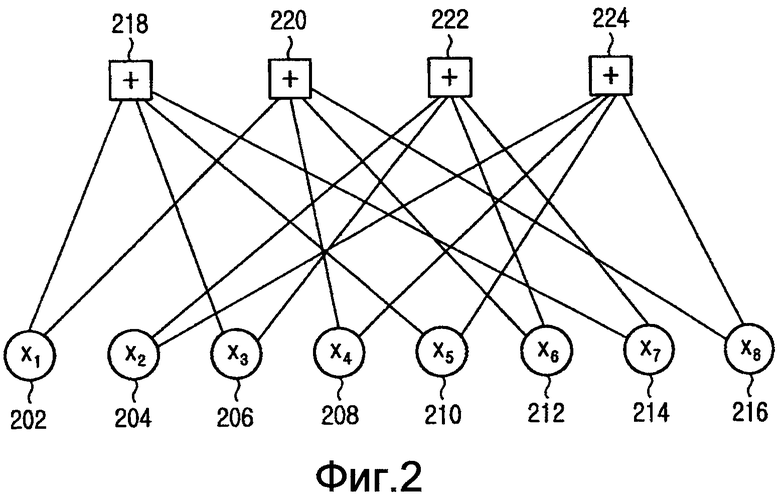

Далее, со ссылками на фиг.3, приводится описание характеристик матрицы проверки четности структурированного кода LDPC, используемой в настоящем изобретении. На фиг.3 схематически проиллюстрирован код LDPC, принятый в качестве стандартного решения в DVB-S2 (стандарт цифрового спутникового видеовещания второго поколения), являющимся одним из принятых в Европе стандартов цифрового вещания.

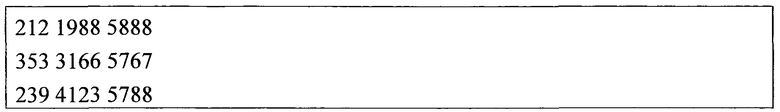

На фиг.3, N1 обозначает длину кодового слова LDPC, K1 дает длину информационного слова, а (N1-K1) дает длину сегмента проверки четности. Далее, целые M1 и q определены таким образом, что выполняется соотношение q=(N1-K1)/M1. Предпочтительно, K1/M1 также является целым.

Как показано на фиг.3, структура относящейся к проверке четности части, т.е. столбцов с K1 по (N1-1), в матрице проверки четности имеет вид двойной диагонали. Таким образом, что касается распределения степеней по столбцам, соответствующим относящейся к проверке четности части матрицы, все столбцы имеют степень 2, за исключением последнего столбца, имеющего степень 1.

В матрице проверки четности структуру информационной части, т.е. столбцов с 0 по (K1-1), разрабатывают с учетом следующих правил.

Правило 1: Все K1/M1 групп столбцов генерируются путем группировки K1 столбцов, соответствующих информационному слову в матрице проверки четности, в множество групп, каждая из которых содержит M1 столбцов. Способ формирования столбцов, принадлежащих каждой группе столбцов основан на Правиле 2.

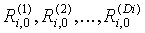

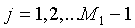

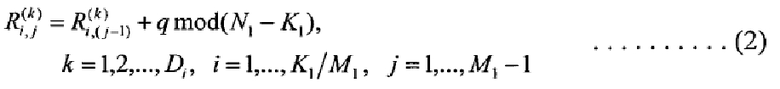

Правило 2: Сначала определяют позиции единиц '1' в каждом нулевом столбце в i-й группе столбцов (где i=1,…, K1/M1). Если степень нулевого столбца в каждой i-й группе столбцов обозначается как Di и позиции строк с единицами составляют  , позиции

, позиции  строк с единицами в j-м столбце (где

строк с единицами в j-м столбце (где  ) i-й группы столбцов даются Уравнением (2).

) i-й группы столбцов даются Уравнением (2).

В соответствии с приведенными выше правилами, можно утверждать, что степени всех столбцов, принадлежащих i-й группе столбцов (где i=1,…, K1/M1), равны Di. Для лучшего понимания структуры кода DVB-S2 LDPC, в котором информация хранится в матрице проверки четности в соответствии с описанными выше правилами, ниже приведен подробный пример.

В качестве подробного примера, для N1=30, K1=15, M1=5 и q=3, три последовательности для информации в положениях строк с единицами для 3 группы столбцов могут быть выражены следующим образом. Здесь для удобства эти последовательности упоминаются как “последовательности позиции вес-1”.

В отношении последовательности позиции вес-1 для 0-х столбцов в каждой группе столбцов только соответствующие последовательности позиций могут быть выражены, как указано ниже, для каждой группы столбцов. Например:

Другими словами, i-я последовательность позиции вес-1 на i-й строчке последовательно представляет информацию в позициях строк с единицами в i-й группе столбцов.

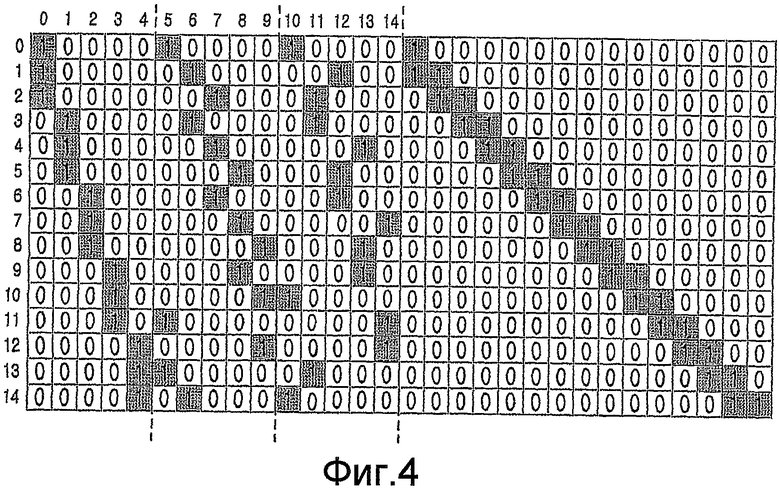

Существует возможность сгенерировать код LDPC с использованием подходов, аналогичным применяемым в коде DVB-S2 LDPC по фиг.4, путем формирования матрицы проверки четности с использованием информации, соответствующей рассмотренному подробному примеру и Правил 1 и 2.

Известно, что для кода DVB-S2 LDPC, разработанного в соответствии с Правилами 1 и 2, может быть эффективно выполнено кодирование с использованием структурной формы. Соответствующие этапы процесса выполнения кодирования LDPC с использованием основанной на DVB-S2 матрице проверки четности описаны ниже в качестве примера.

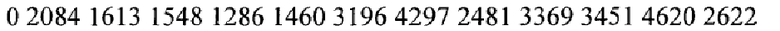

В приведенном ниже подробном примере рассматривается процесс кодирования для кода DVB-S2 LDPC с N1=16200, K1=10800, M1=360 и q=15. Для удобства, информационные биты, имеющие длину K1, представлены как (i0, i1,…, iK1-1), а биты четности, имеющие длину (N1-K1), выражены как (p0, p1,…, pN1-K1-1).

Этап 1: Кодер LDPC инициализирует биты четности следующим образом:

p0=p1=…=pN1-K1-1=0

Этап 2: Кодер LDPC считывает информацию о строке, где единица расположена в группе столбцов из нулевой последовательности позиции вес-1, из сохраненных последовательностей, характеризующих матрицу проверки четности.

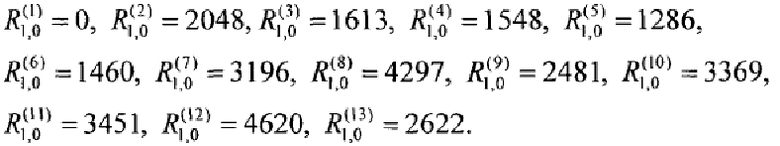

Кодер LDPC обновляет конкретные биты px в соответствии с Уравнением (3), используя считанную информацию и первый информационный бит i0. Здесь х обозначает значение  для k=1,2,…,13.

для k=1,2,…,13.

В Уравнении (3), px=px⊕i0 также может быть выражен следующим образом: px←px⊕i0, и ⊕ обозначает бинарное сложение.

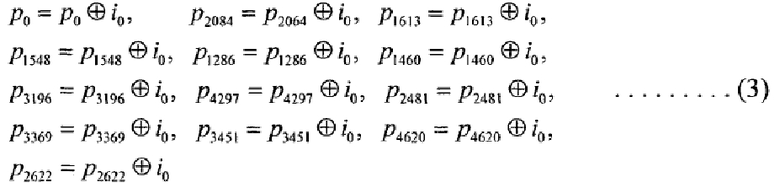

Этап 3: Кодер LDPC сначала находит значение Уравнения (4) для следующих 359 битов информации im (где m=1,2,…,359) после i0.

В Уравнении (4), х обозначает значение  для k=1,2,…,13. Следует отметить, что Уравнение (4) следует той же концепции, что и Уравнению (2).

для k=1,2,…,13. Следует отметить, что Уравнение (4) следует той же концепции, что и Уравнению (2).

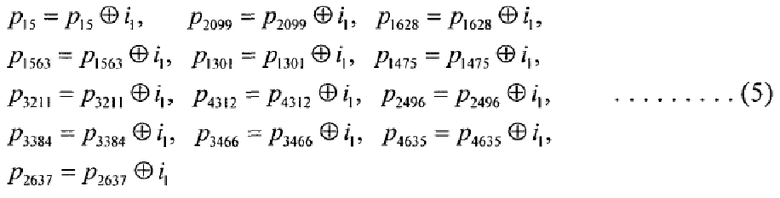

Затем кодер LDPC выполняет операцию, аналогичную Уравнению (3), используя значение, найденное в Уравнении (4). Другими словами, кодер LDPC обновляет p{x+(m modM1)×q}mod(N1-K1) для im. Например, для m=1, т.е. для i1, кодер LDPC обновляет биты четности p{x+q}mod(N1-K1), как описано в Уравнении (5).

Следует отметить, что в Уравнении (5) q=15. Кодер LDPC выполняет вышеописанный процесс для m=1,2,…,359, подобно тому, как показано выше.

Этап 4: Как и на этапе 2, кодер LDPC считывает информацию о первой последовательности позиции вес-1  (k=1,2,…,13) для 361 информационного бита i360 и обновляет конкретный px, где х обозначает

(k=1,2,…,13) для 361 информационного бита i360 и обновляет конкретный px, где х обозначает  . Кодер LDPC обновляет p{x+(m modM1)×q}mod(N1-K1), m=361,362,…,719 путем аналогичного применения Уравнения (4) к следующим 359 информационным битам i360,i360,,i360 после i360.

. Кодер LDPC обновляет p{x+(m modM1)×q}mod(N1-K1), m=361,362,…,719 путем аналогичного применения Уравнения (4) к следующим 359 информационным битам i360,i360,,i360 после i360.

Этап 5: Кодер LDPC повторяет этапы 2, 3 и 4 для всех групп, причем каждая группа имеет 360 информационных битов.

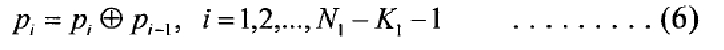

Этап 6: В завершение, кодер LDPC определяет биты четности, используя Уравнение (6)

Биты четности pi по Уравнению (6) представляют собой биты четности, которые были подвергнуты LDPC кодированию.

Как описывалось выше, в DVB-S2, кодер LDPC выполняет LDPC кодирование, выполняя процесс, содержащий этапы 1-6.

Хорошо известно, что производительность кода LDPC тесно соотносится с характеристиками циклов в графе Таннера. В частности, из экспериментальных исследований хорошо известно, что большое количество коротких циклов в графе Танера может привести к деградации производительности. Таким образом, для разработки LDPC кодов, имеющих высокую производительность, должна приниматься во внимание характеристика циклов графа Таннера.

Однако еще не был предложен способ разработки кодов DVB-S2 LDPC, имеющих хорошие характеристики циклов. Для кода DVB-S2 LDPC в области высоких отношений сигнал/шум наблюдается феномен более медленного уменьшения вероятности ошибки при увеличении отношения сигнал/шум, если не проводится оптимизация характеристик циклов в графе Таннера. Поэтому существует потребность в способе, обеспечивающем возможность эффективного улучшения характеристик циклов при разработке кодов LDPC, имеющих структуру DVB-S2.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Настоящее изобретение выполнено с целью преодоления по меньшей мере описанных выше проблем и для обеспечения по меньшей мере преимуществ, описанных ниже. Соответственно, один из аспектов настоящего изобретения обеспечивает устройство и способ кодирования/декодирования канала для разработки матрицы проверки четности квазициклического кода LDPC, разработанного на базе матрицы циклических перестановок, для разработки кода DVB-S2 LDPC в системе связи, использующей коды LDPC.

Другой аспект настоящего изобретения обеспечивает устройство и способ кодирования/декодирования канала для разработки матрицы проверки четности такого же кода LDPC, что и код DVB-S2 LDPC, имеющий хорошую характеристику графа Таннера в системе связи, использующей коды LDPC.

Согласно одному из аспектов настоящего изобретения, обеспечивается способ генерации матрицы проверки четности кода с низкой плотностью проверок четности (LDPC). Определяют параметры для кода LDPC. Первая матрица проверки четности кода LDPC формируется согласно определенным параметрам. Вторая матрица проверки четности создается с помощью удаления заранее заданной доли части, относящейся к проверке четности, в первой матрице проверки четности. Третья матрица проверки четности создается путем переупорядочивания второй матрицы проверки четности.

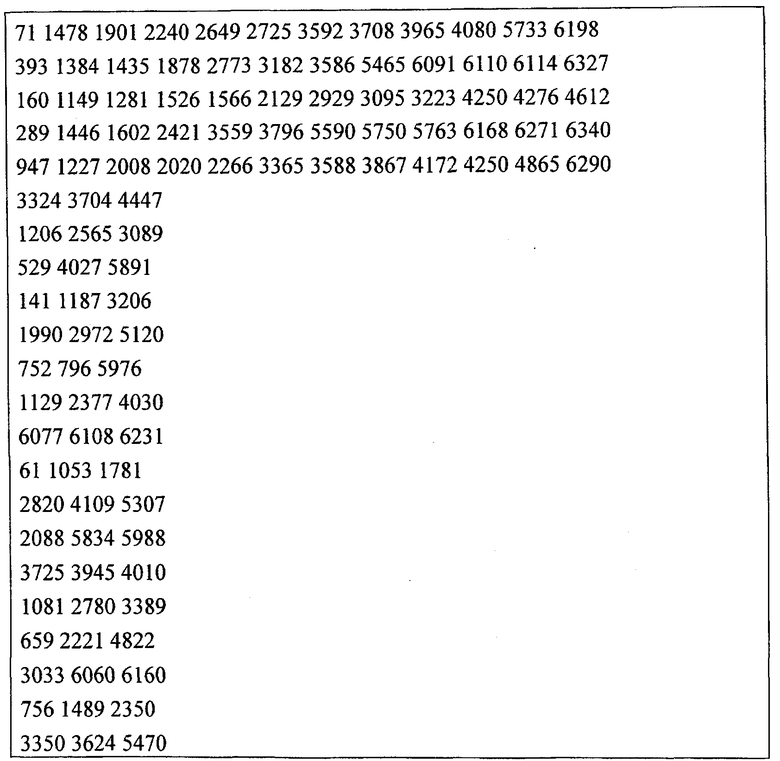

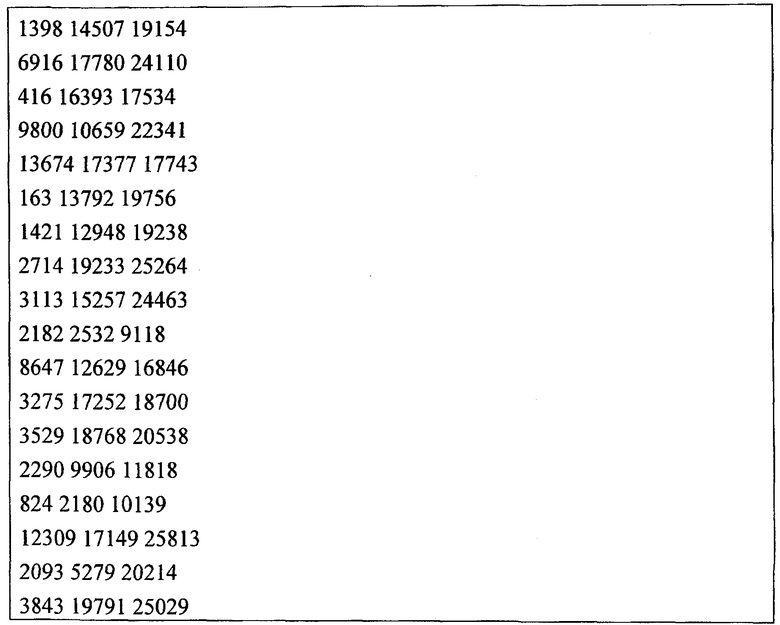

Согласно еще одному аспекту настоящего изобретения, обеспечивается способ кодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC). Считывают сохраненную матрицу проверки четности. Выполняют LDPC кодирование принятого сигнала, используя сохраненную матрицу проверки четности. Матрицу проверки четности разделяют на информационное слово и четность. Если кодовая скорость составляет 3/5 и длина кодового слова составляет 16200, матрицу проверки четности формируют, как указано в нижеследующей таблице:

Согласно другому варианту осуществления, обеспечивается способ декодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC). Извлекают матрицу проверки четности для кода LDPC. Выполняют LDPC декодирование, используя извлеченную матрицу проверки четности. Извлеченную матрицу проверки четности разделяют на информационное слово и четность. Если кодовая скорость составляет 3/5 и длина кодового слова составляет 16200, матрицу проверки четности формируют, как указано в нижеследующей таблице:

Согласно дополнительному аспекту настоящего изобретения, обеспечивают устройство кодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC). Устройство извлечения матрицы проверки четности кода LDPC считывает сохраненную матрицу проверки четности. Кодер LDPC выполняет LDPC кодирование принятого сигнала, используя сохраненную матрицу проверки четности. Матрицу проверки четности разделяют на четность и информационное слово. Если кодовая скорость составляет 3/5 и длина кодового слова составляет 16200, матрицу проверки четности формируют, как указано в нижеследующей таблице:

Согласно другому дополнительному аспекту настоящего изобретения, обеспечивают устройство декодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC). Устройство извлечения матрицы проверки четности кода LDPC считывает сохраненную матрицу проверки четности. Декодер LDPC выполняет LDPC декодирование принятого сигнала, используя сохраненную матрицу проверки четности. Считанную матрицу проверки четности разделяют на четность и информационное слово. Если кодовая скорость составляет 3/5 и длина кодового слова составляет 16200, матрицу проверки четности формируют, как указано в нижеследующей таблице:

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Перечисленные выше и другие аспекты, признаки и преимущества, обеспечиваемые настоящим изобретением, станут более понятными из нижеследующего подробного описания, рассматриваемого совместно с чертежами, на которых:

Фиг.1 представляет собой диаграмму, иллюстрирующую матрицу проверки четности кода LDPC с длиной 8;

Фиг.2 представляет собой диаграмму, иллюстрирующую граф Таннера матрицы проверки четности кода LDPC с длиной 8;

Фиг.3 представляет собой диаграмму, иллюстрирующую схематическую структуру кода LDPC DVB-S2;

Фиг.4 представляет собой диаграмму, иллюстрирующую матрицу проверки четности кода LDPC DVB-S2;

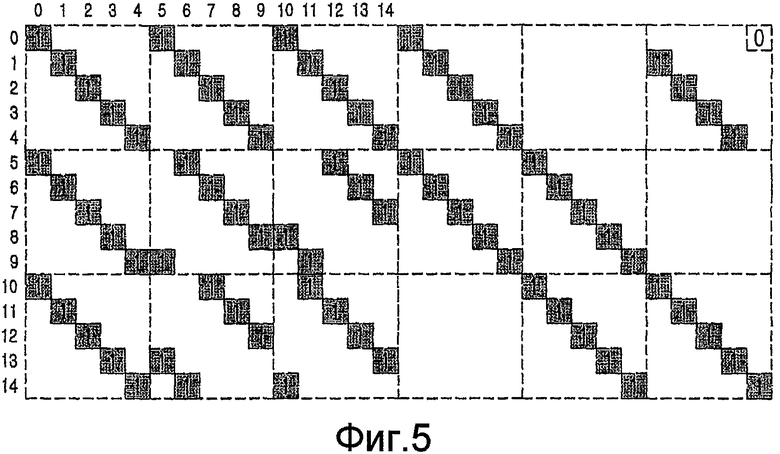

Фиг.5 представляет собой диаграмму, иллюстрирующую матрицу проверки четности, генерируемую с помощью переупорядочивания столбцов и строк матрицы проверки четности кода LDPC DVB-S2 по фиг.4 в соответствии с заранее определенными правилами, в соответствии с одним из вариантов осуществления настоящего изобретения;

Фиг.6 представляет собой диаграмму, иллюстрирующую матрицу проверки четности квазициклического кода LDPC, необходимую для разработки кода LDPC DVB-S2, в соответствии с одним из вариантов осуществления настоящего изобретения;

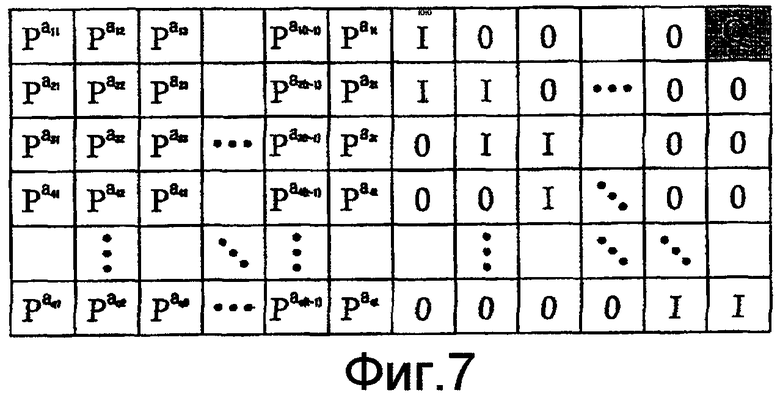

Фиг.7 представляет собой диаграмму, иллюстрирующую результат, полученный путем преобразования матрицы проверки четности квазициклического кода LDPC, необходимую для разработки кода LDPC DVB-S2, в соответствии с одним из вариантов осуществления настоящего изобретения;

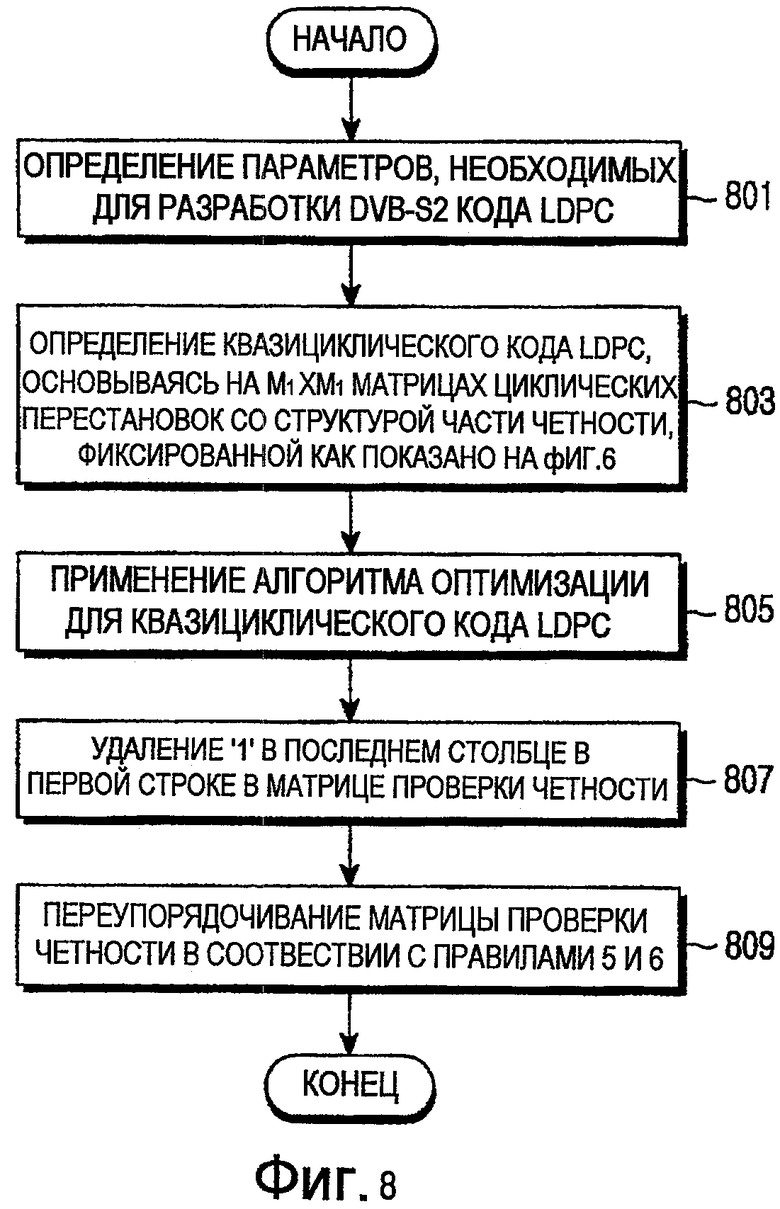

Фиг.8 представляет собой блок-схему последовательности операций, иллюстрирующую процесс разработки кода LDPC DVB-S2, в соответствии с одним из вариантов осуществления настоящего изобретения;

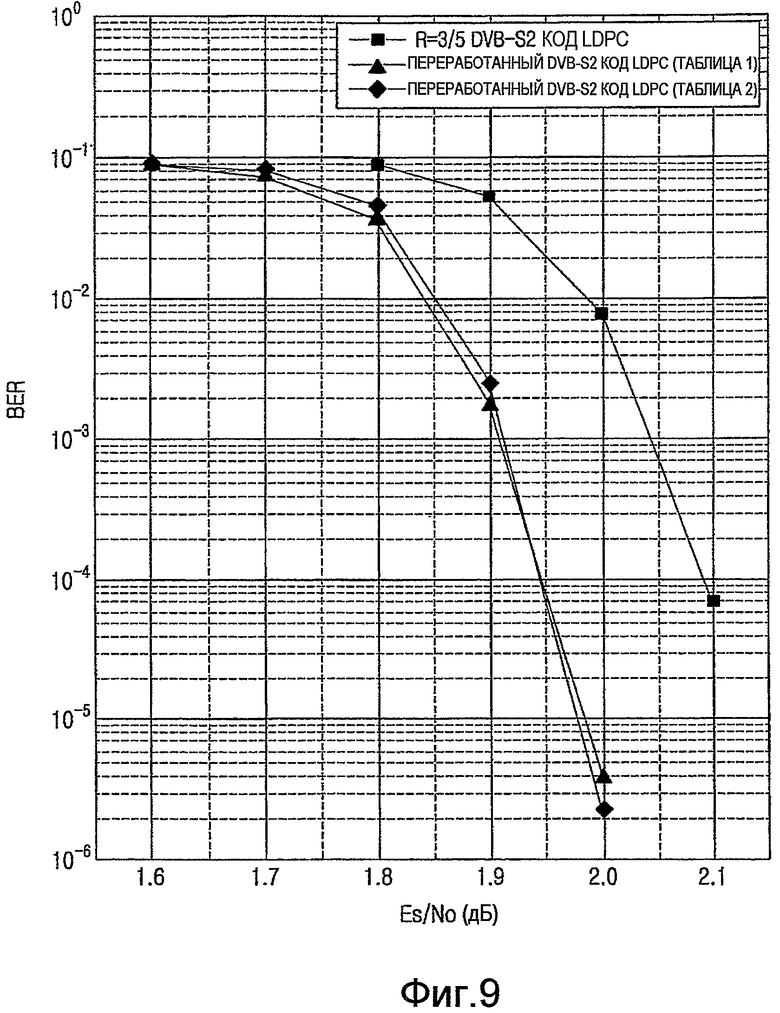

Фиг.9 представляет собой блок-схему, иллюстрирующую результат компьютерного моделирования кода LDPC DVB-S2, в соответствии с одним из вариантов осуществления настоящего изобретения;

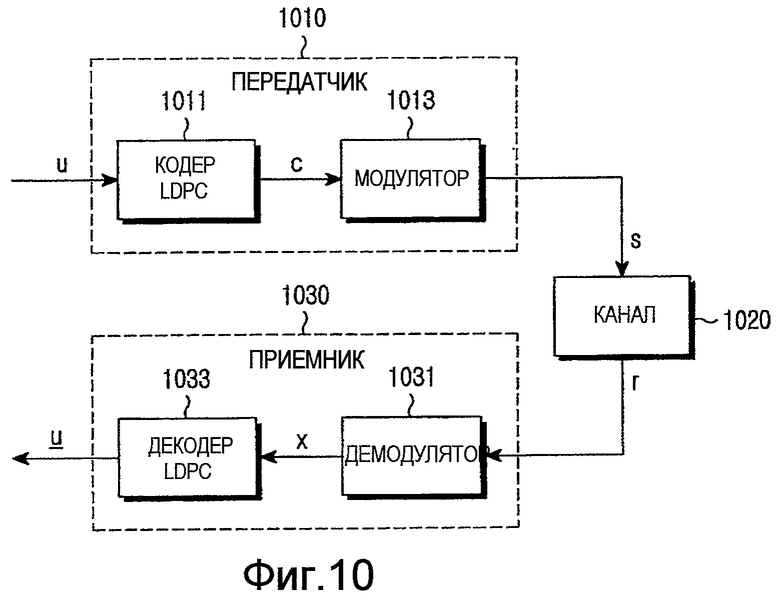

Фиг.10 представляет собой блок-схему, иллюстрирующую структуру приемопередатчика в системе связи, использующего переработанный код LDPC DVB-S2, в соответствии с одним из вариантов осуществления настоящего изобретения;

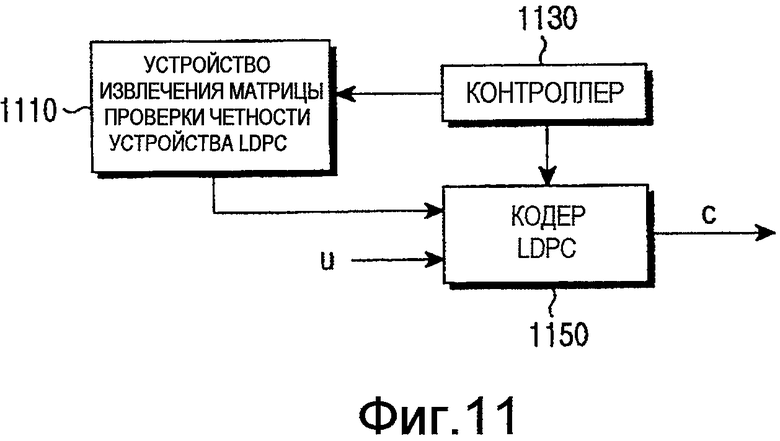

Фиг.11 представляет собой блок-схему, иллюстрирующую структуру передающего устройства, использующего код LDPC, в соответствии с одним из вариантов осуществления настоящего изобретения;

Фиг.12 представляет собой блок-схему, иллюстрирующую структуру приемного устройства, использующего код LDPC, в соответствии с одним из вариантов осуществления настоящего изобретения;

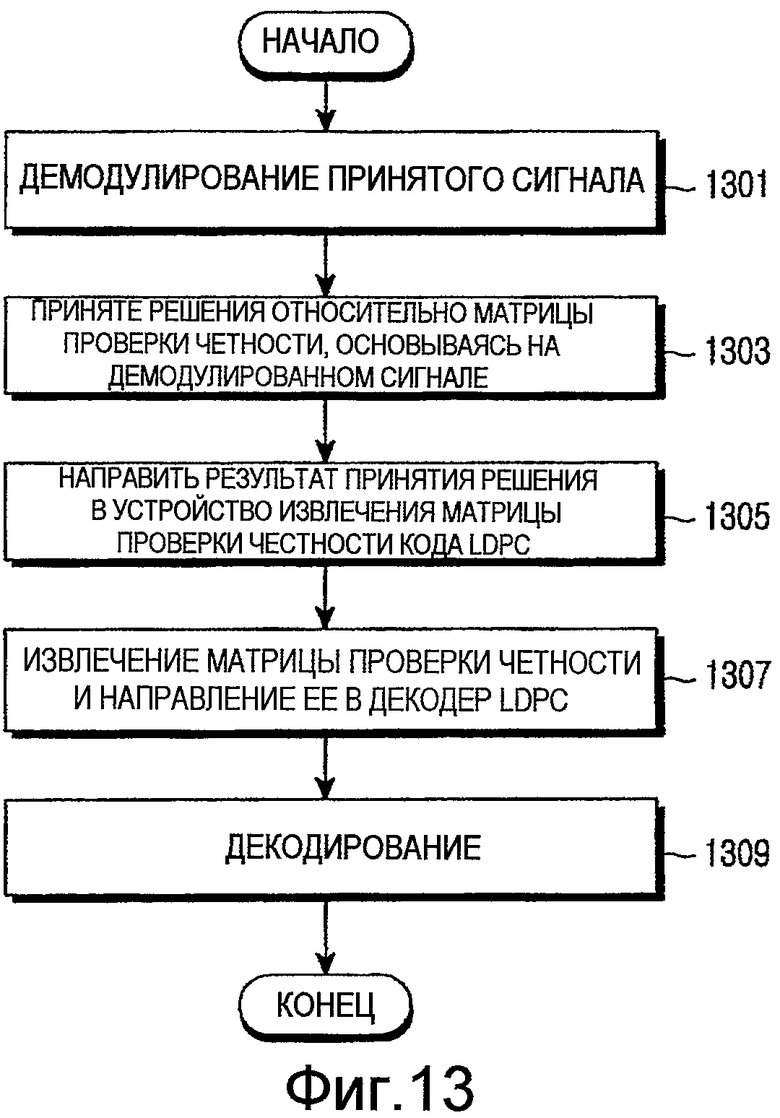

Фиг.13 представляет собой блок-схему последовательности операций, иллюстрирующую процесс приема в приемном устройстве, использующем код LDPC, в соответствии с одним из вариантов осуществления настоящего изобретения;

ПОДРОБНОЕ ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНЫХ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

Предпочтительные варианты осуществления настоящего изобретения описаны со ссылками на прилагаемые чертежи. Одинаковые или подобные компоненты обозначены одинаковыми или подобными ссылочными позициями, не смотря на то, что они изображены на разных чертежах. Подробное описание конструкций или процессов, известных из уровня техники, может быть опущено с тем, чтобы избежать неясности при описании объекта настоящего изобретения.

Настоящее изобретения обеспечивает способ для разработки кода LDPC DVB-S2, имеющего хорошую характеристику графа Таннера. Дополнительно, настоящее изобретение обеспечивает способ и устройство для генерации кодового слова LDPC с использованием матрицы проверки четности упомянутого выше кода LDPC.

Структурные характеристики кода LDPC DVB-S2 описаны ниже с использованием матрицы проверки четности кода LDPC DVB-S2, показанной на фиг.4. Для матрицы проверки четности, показанной на фиг.4, N1=30, K1=15, M1=5 и q=3, последовательности позиции вес-1 строк для нулевых столбцов в трех группах столбцов являются следующими:

Здесь i-я последовательность позиции вес-1 в i-й строчке последовательно представляет информацию на позициях строк с единицами в i-й группе столбцов.

Матрица проверки четности по фиг.4 преобразуется в соответствии со следующими правилами. Фиг.4 представляет собой диаграмму, иллюстрирующую матрицу проверки четности кода LDPC DVB-S2.

Правило 3: Строки с нулевой по (N1-K1-1)-ю переупорядочены таким образом, что (q·i+j)-я строка располагается на месте (M1·j+i)-й строки, причем 0≤i≤M1 и 0≤j≤q.

Правило 4: Столбцы с нулевого по (K1-1)-й не меняются, столбцы с K1-го по (N1-1)-й переупорядочены таким образом, что (K1+q·i+j)-й столбец располагается на месте (K1+M1·j+i)-го столбца.

Матрица проверки четности, имеющая форму, показанную на фиг.5, получена путем реконструкции матрицы проверки четности по фиг.4 в соответствии с Правилами 3 и 4. На фиг.5 проиллюстрирована матрица проверки четности, сгенерированная путем переупорядочивания столбцов и строк в матрице проверки четности кода LDPC DVB-S2 по фиг.4, в соответствии с заранее заданными правилами, в соответствии с одним из вариантов осуществления изобретения.

Если исходить из допущения, что на фиг.5 единицы присутствуют в (N1-1)-м столбце на нулевой строке, то матрица проверки четности по фиг.5 может рассматриваться как соответствующая некоторому виду квазициклического кода LDPC, состоящего из матрицы циклических перестановок размера M1×M1, т.е. 5×5. 'Матрица циклических перестановок' определена как вид матрицы перестановок, созданной путем циклических сдвигов вправо, одна за одной, строк в единичной матрице. Помимо этого, 'квазициклический код LDPC' определен как разновидность кода LDPC, созданная путем разделения матрицы проверки четности на несколько блоков с одинаковыми размерами и отображения матриц циклических перестановок или нулевых матриц в эти блоки.

Таким образом, матрица проверки четности, аналогичная квазициклическому LDPC коду, может быть получена путем реконструкции матрицы проверки четности кода LDPC DVB-S2, применяя Правила 3 и 4. Помимо этого, ожидается, что код LDPC DVB-S2 может быть сгенерирован из квазициклического LDPC кода путем обращения процесса, определяемого Правилами 3 и 4.

Хотя результаты исследований кода LDPC DVB-S2 неизвестны, существует множество известных способов разработки квазициклического LDPC кода. Способы разработки квазициклического LDPC кода включают хорошо известные способы оптимизации характеристик циклов в графе Таннера.

В одном из вариантов осуществления настоящего изобретения предложен способ разработки кода LDPC DVB-S2 с использованием хорошо известного способа улучшения характеристик циклов в графе Таннера квазициклического кода LDPC. Однако, поскольку способ улучшения характеристик циклов в графе Таннера квазициклического кода LDPC только косвенно относится к настоящему изобретению, его подробное описание опушено для упрощения изложения.

Ниже представлено описание способа разработки кода LDPC DVB-S2 с использованием квазициклического кода LDPC. Код LDPC DVB-S2 имеет кодовое слово длины N1, информационную длину K1 и длину четности (N1-K1), при этом q=(N1-K1)/M1.

Матрица проверки четности квазициклического кода LDPC показана на фиг.6. Фиг.6 представляет собой диаграмму, иллюстрирующую матрицу проверки четности квазициклического кода LDPC, необходимую для разработки кода LDPC DVB-S2 согласно одному из вариантов осуществления настоящего изобретения. Показанная на фиг.6 матрица проверки четности имеет (N1-K1) строк и N1 столбцов и разделена на отдельные блоки M1×M1. Для удобства, если t=K1/M1, информационная часть и часть четности в матрице проверки четности по фиг.6 состоят соответственно из t блоков столбцов и q блоков столбцов и имеют в целом q блоков строк. При этом N1/M1 = t+q.

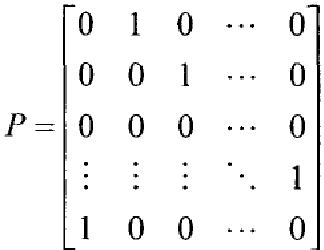

Соответствующие частичные блоки, составляющие матрицу проверки четности по фиг.6, соответствуют матрицам циклических перестановок или нулевым матрицам. При этом матрица циклических перестановок имеет размер M1×M1 и создана на основе матрицы Р циклических перестановок, которая определена следующим образом:

На фиг.6 aij представляют целые от 0 до M1-1 или значения ∝, Р0 определено как единичная матрица I, и Р∝ определяет нулевую матрицу M1×M1. Помимо этого, цифры 0 в части четности определяют нулевые матрицы M1×M1.

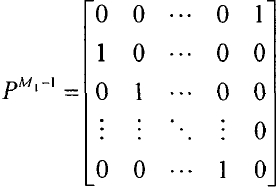

Матрица проверки четности по фиг.6 характеризуется тем, что блок столбцов, соответствующий четности, содержит единичную матрицу I и матрицу циклической перестановки PM1-1, как показано на чертеже. Другими словами, блок столбцов, соответствующий четности, имеет жестко определенную структуру, показанную на фиг.6. Матрица PM1-1 циклических перестановок определяется следующим образом:

Квазициклический код LDPC показан на фиг.16 в той части, которая осталась неизменной в процессе оптимизации циклов квазициклического кода LDPC вследствие того, что структуры блоков столбцов, соответствующих части четности, являются фиксированными. Другими словами, поскольку блоки столбцов, соответствующих части четности, являются фиксированными в матрице проверки четности по фиг.6, соединения между узлами переменных, соответствующие четности, определены в графе Таннера, так что для оптимизации циклов в графе Таннера необходимо только оптимизировать соединения между узлами переменных, соответствующих информационной части.

Как описывалось выше, существует много способов оптимизации характеристики циклов графа Таннера квазициклического кода LDPC. Поскольку способ разработки квазициклического кода LDPC с графом Таннера, имеющим оптимизированные характеристики циклов только косвенно относится к настоящему изобретению, его подробное описание опущено.

Предполагается, что с помощью способа разработки квазициклического кода LDPC определяют распределение степеней, демонстрирующее хорошую производительность в состоянии, где структура части четности является фиксированной в квазициклической матрице проверки четности по фиг.6. Позиции матрицы циклических перестановок и нулевых матриц определяют в блоках столбцов, соответствующих информационной части, в соответствии распределению степеней. Характеристики циклов графа Таннера оптимизируются.

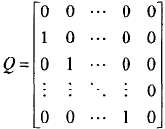

Форма, показанная на фиг.7, например, может быть получена петем удаления единиц в последнем столбце первой строки в матрице PM1-1 циклических перестановок, соответствующей последнему (N1/M1)-му или (i+q)-му блоку столбцов в первом блоке строк в матрице проверки четности по фиг.6. Фиг.7 представляет собой диаграмму, иллюстрирующую результат, полученный путем преобразования матрицы проверки четности квазициклического кода LDPC, необходимой для разработки кода LDPC DVB-S2, в соответствии с вариантом осуществления настоящего изобретения.

Следует отметить, что матрица PM1-1 циклических перестановок преобразуется в матрицу Q, показанную на фиг.7.

Описанные ниже Правила 5 и 6 определяют процесс, обратный процессу, определяемому Правилами 3 и 4.

Правило 5: Столбцы с нулевого по (K1-1)-й сохраняются неизменными, столбцы с K1-го по (N1-1)-й переупорядочиваются таким образом, что (K1+M1·j+i)-й столбец располагается на месте (K1+q·i+j)-го столбца, где 0≤i≤M1 и 0≤j≤q.

Правило 6: строки с нулевую по (N1-K1-1)-ю переупорядочиваются таким образом, что (M1·j+i)-я строка располагается на месте (q·i+j)-й строки.

Матрица проверки четности кода LDPC, сгенерированная из квазициклического кода LDPC по фиг.6 с помощью описанного выше процесса, путем применения Правил 5 и 6 превращается в матрицу проверки четности, например, имеющую форму кода LDPC DVB-S2, показанного на фиг.3. Описанный выше способ разработки матрицы проверки четности DVB-S2, в которой длины кортового слова, информации и четности составляют соответственно N1, K1 и (N1-K1) при q=(N1-K1)/M1, может быть представлен в виде следующего процесса.

ПРОЦЕСС РАЗРАБОТКИ КОДА LDPC DVB-S2

Фиг.8 представляет собой блок-схему последовательности операций для разработки кода LDPC DVB-S2, согласно одному из вариантов настоящего изобретения.

Как показано на фиг.8, параметры, необходимые для разработки требуемого кода LDPC DVB-S2, определяют на этапе 801. В настоящем документе полагается, что параметры, такие как длина кодового слова и длина информации, а также хорошее распределение степеней для разработки кода LDPC DVB-S2, определены заранее.

Затем, на этапе 803, в соответствии с параметрами, определенными на этапе 801, формируют матрицу проверки четности квазициклического кода LDPC, состоящую из M1×M1 матриц циклических перестановок и нулевых матриц, как показано на фиг.6. На фиг.6 блоки столбцов, соответствующие части четности, всегда имеют фиксированную форму.

На этапе 805 определяют матрицы циклических перестановок блоков столбцов, соответствующих информационной части на Фиг.6 путем применения алгоритма улучшения характеристик циклов графа Таннера квазициклического кода LDPC. При этом может использоваться любой известный алгоритм улучшения характеристик циклов.

На этапе 807 получают матрицу проверки четности, например, показанную на фиг.7, путем удаления единиц в последнем столбце первой строке матрицы проверки четности по фиг.6, которая была установлена на этапе 805.

На этапе 809 переупорядочивают столбцы и строки матрицы проверки четности по фиг.7 путем применения Правил 5 и 6 к матрице проверки четности по фиг.7. Полученная в результате матрица проверки четности может представлять, например, код LDPC DVB-S2, показанный на фиг.3.

Кодовое слово может быть получено путем описанного выше процесса кодирования LDPC DVB-S2 к коду LDPC, полученному в результате выполнения описанных выше этапов.

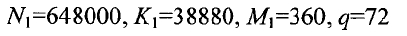

Для анализа производительности кода LDPC DVB-S2 был разработан код LDPC DVB-S2, имеющий следующие параметры:

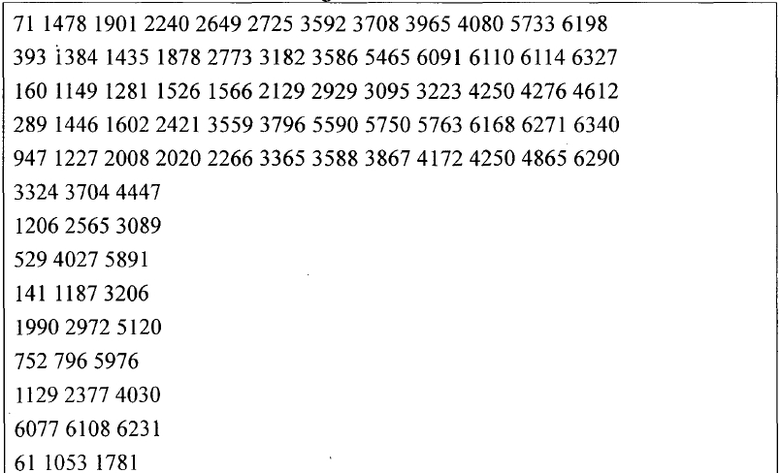

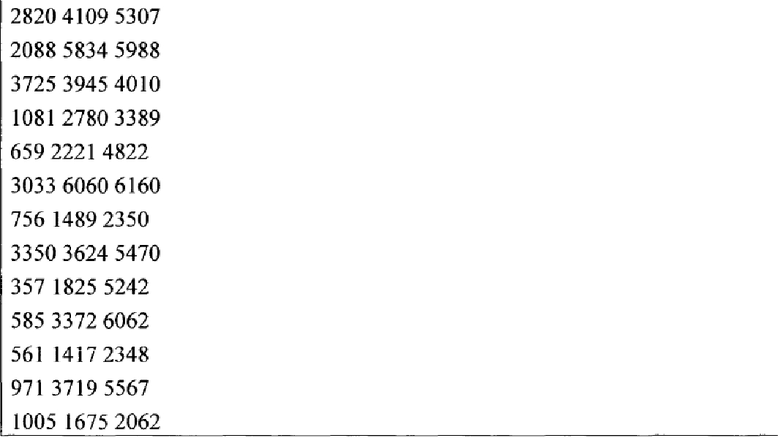

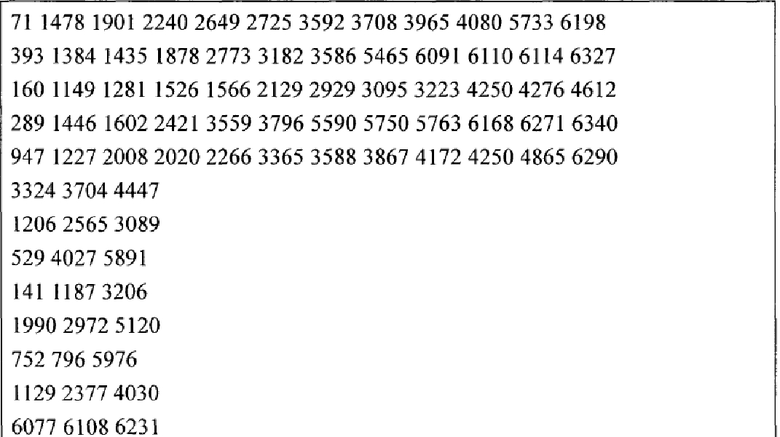

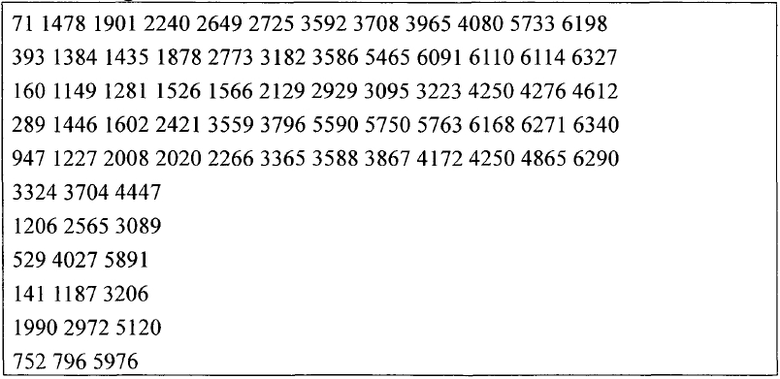

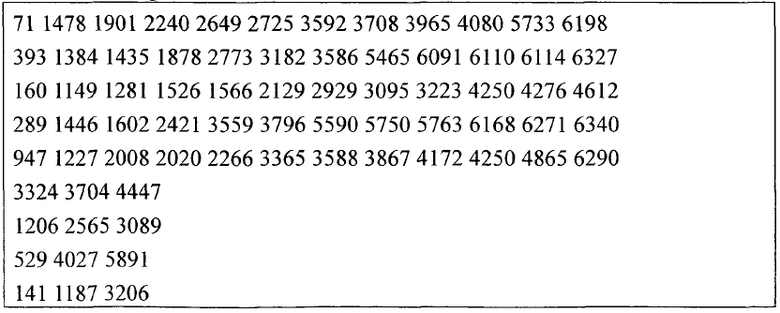

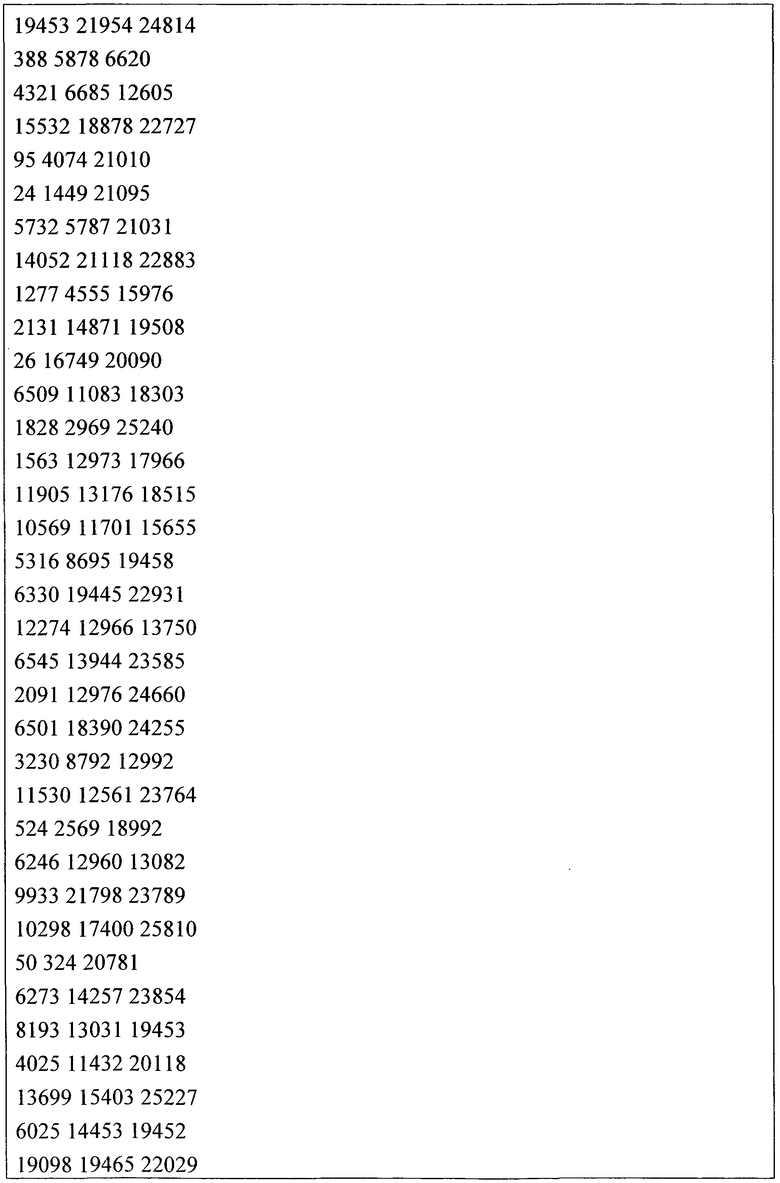

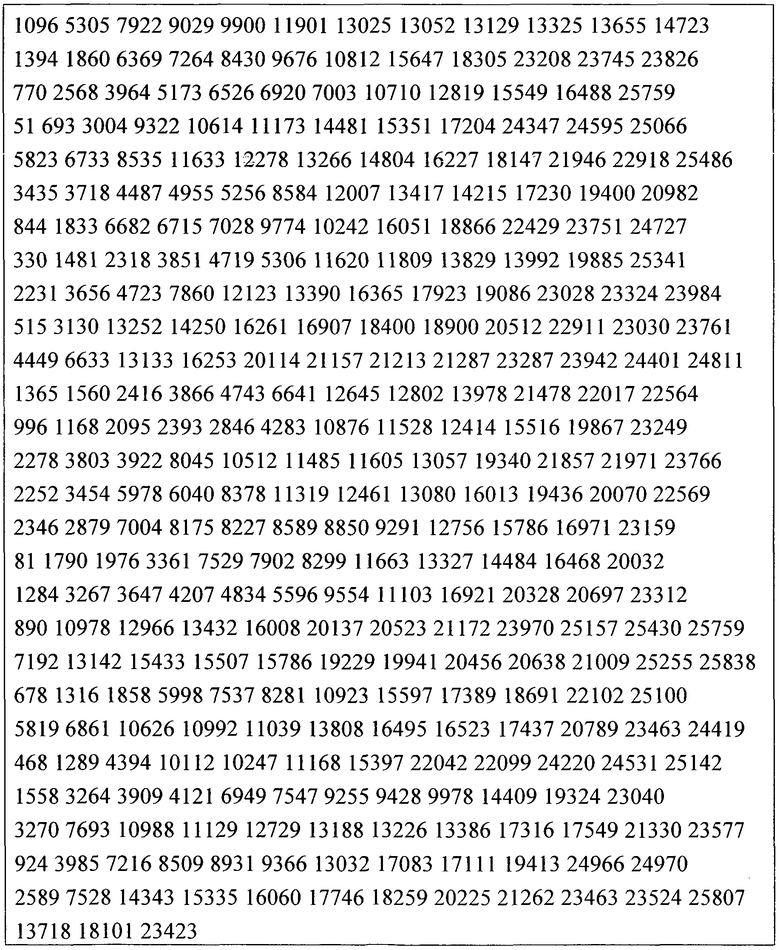

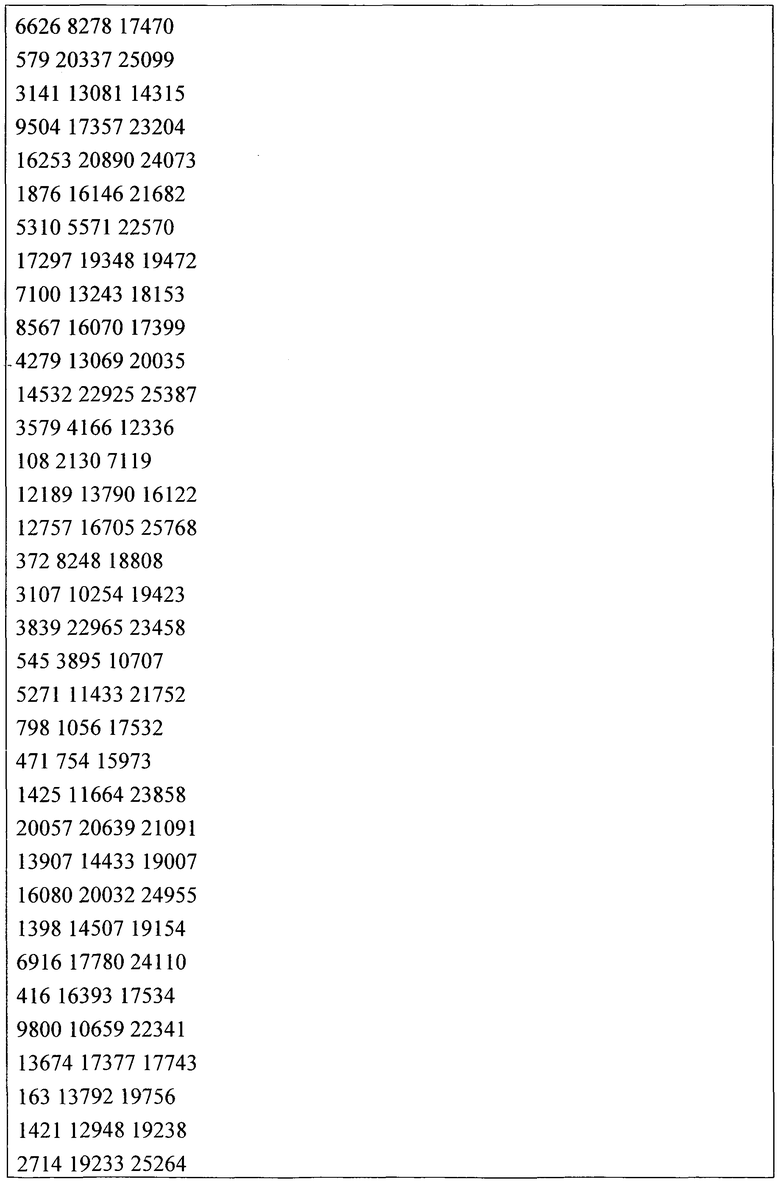

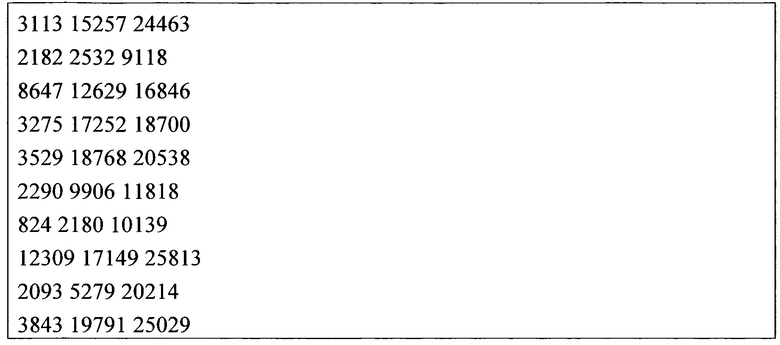

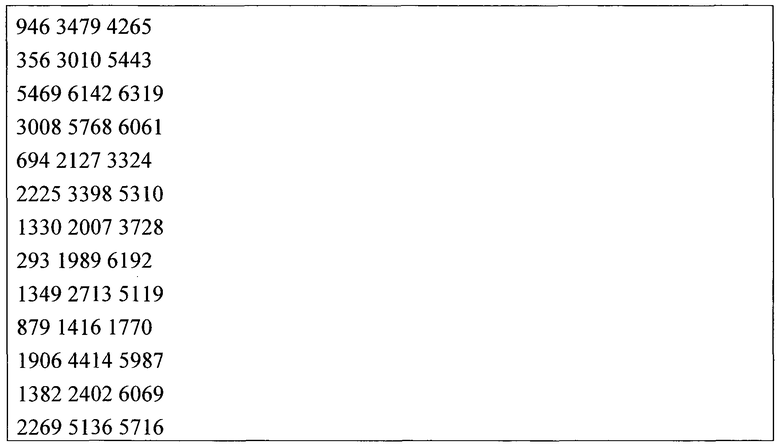

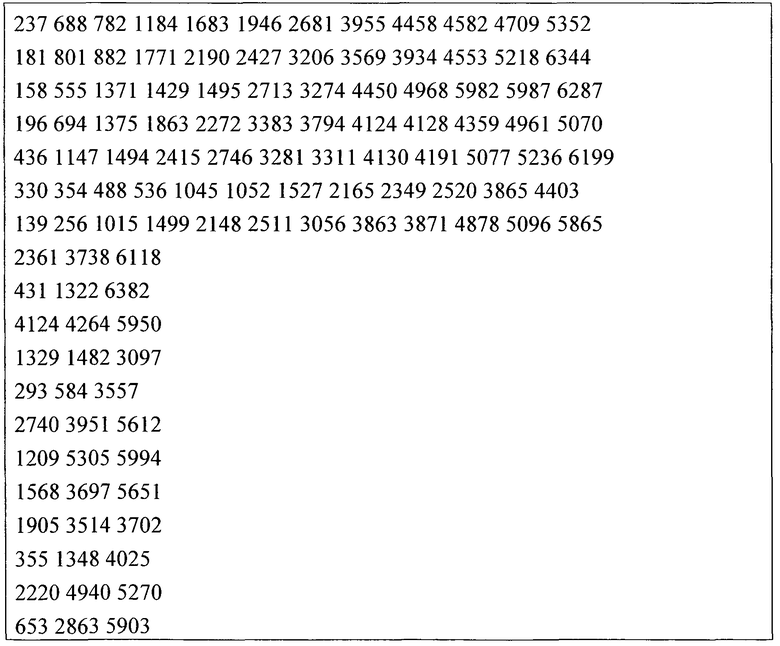

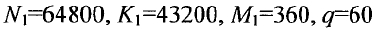

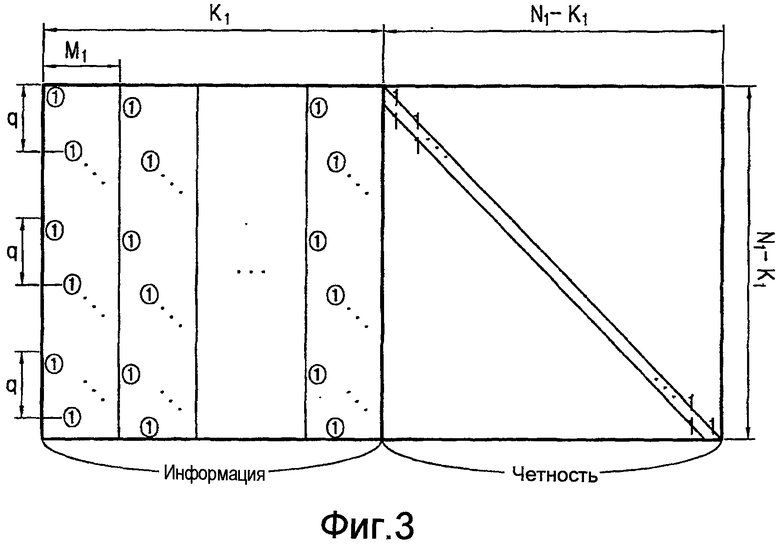

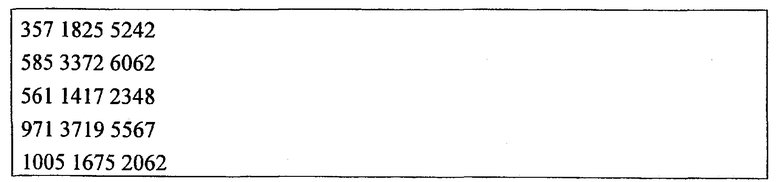

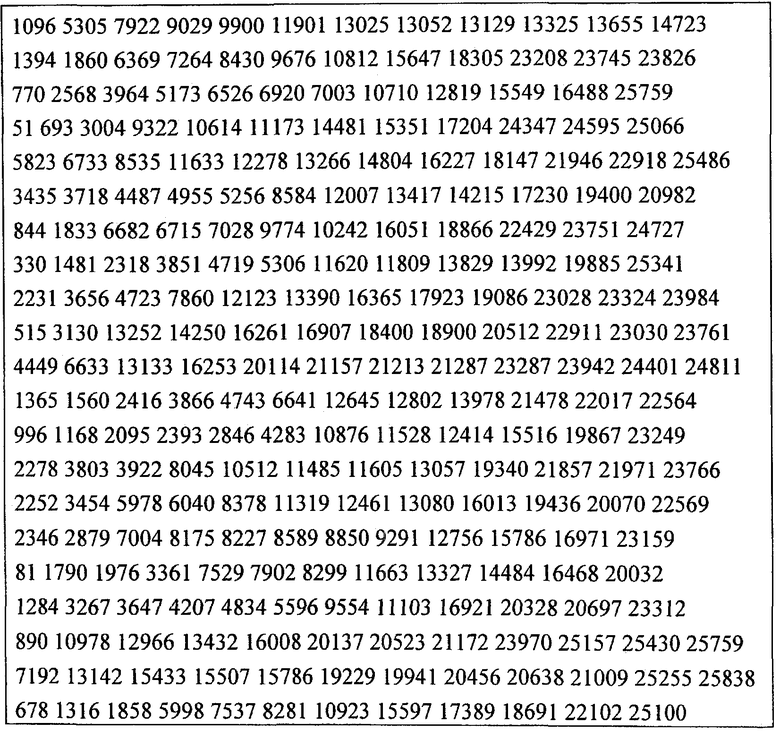

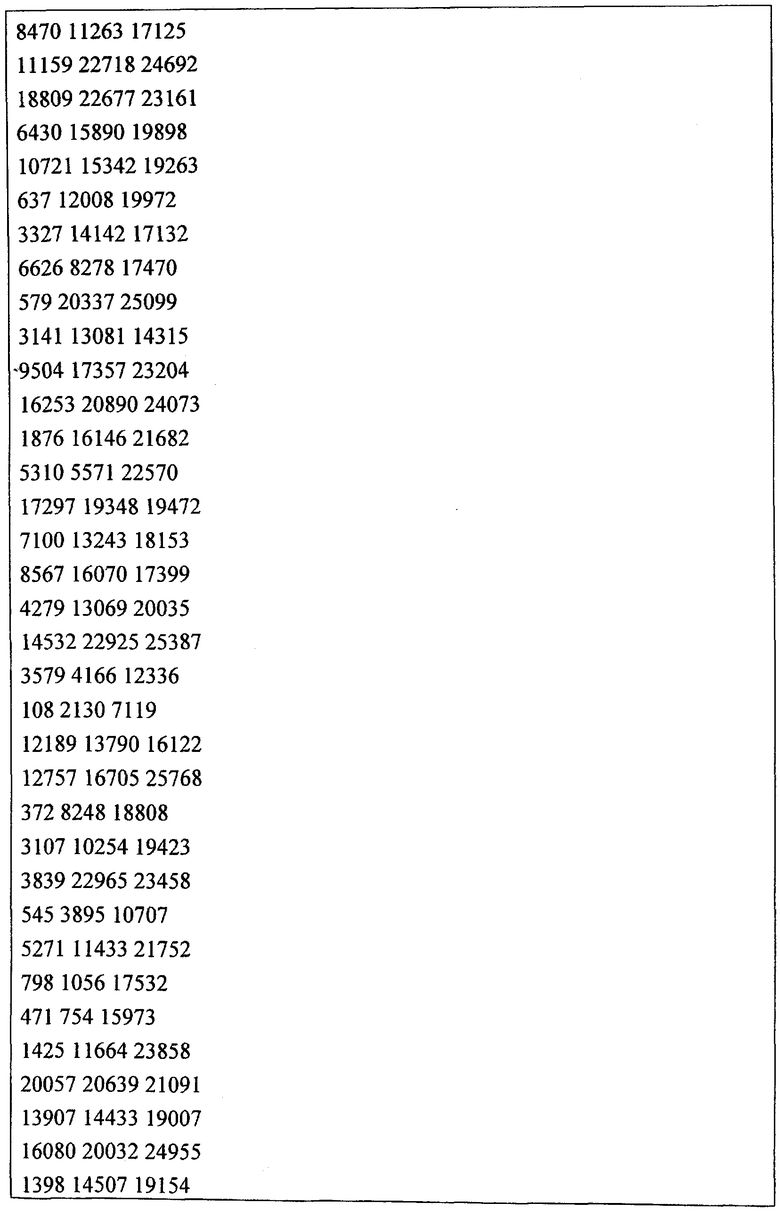

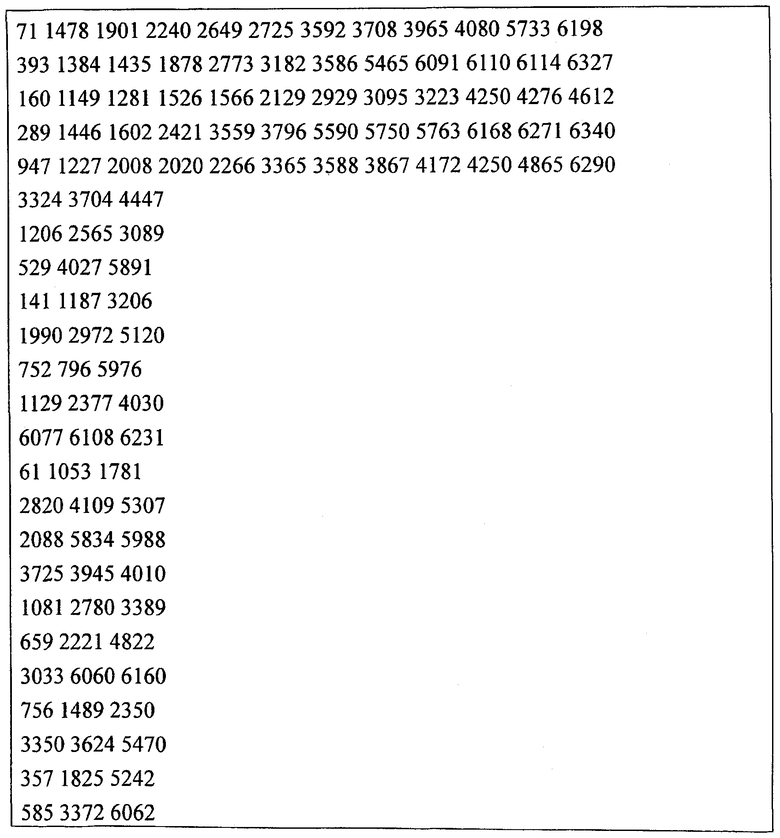

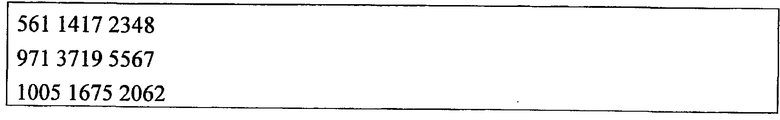

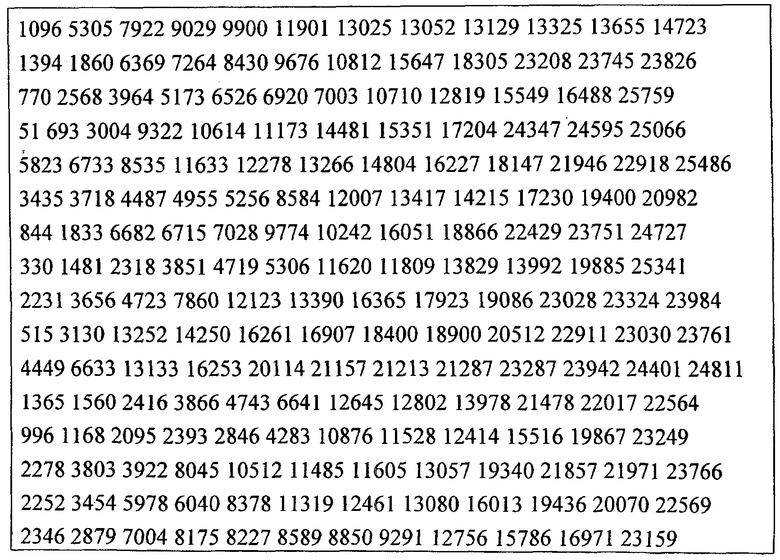

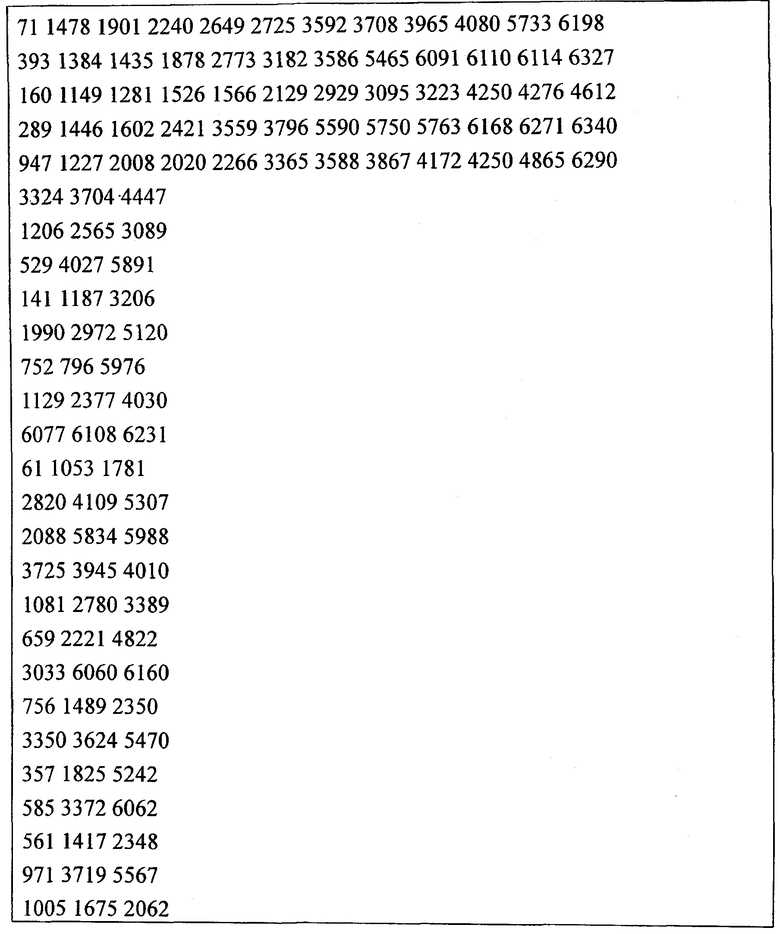

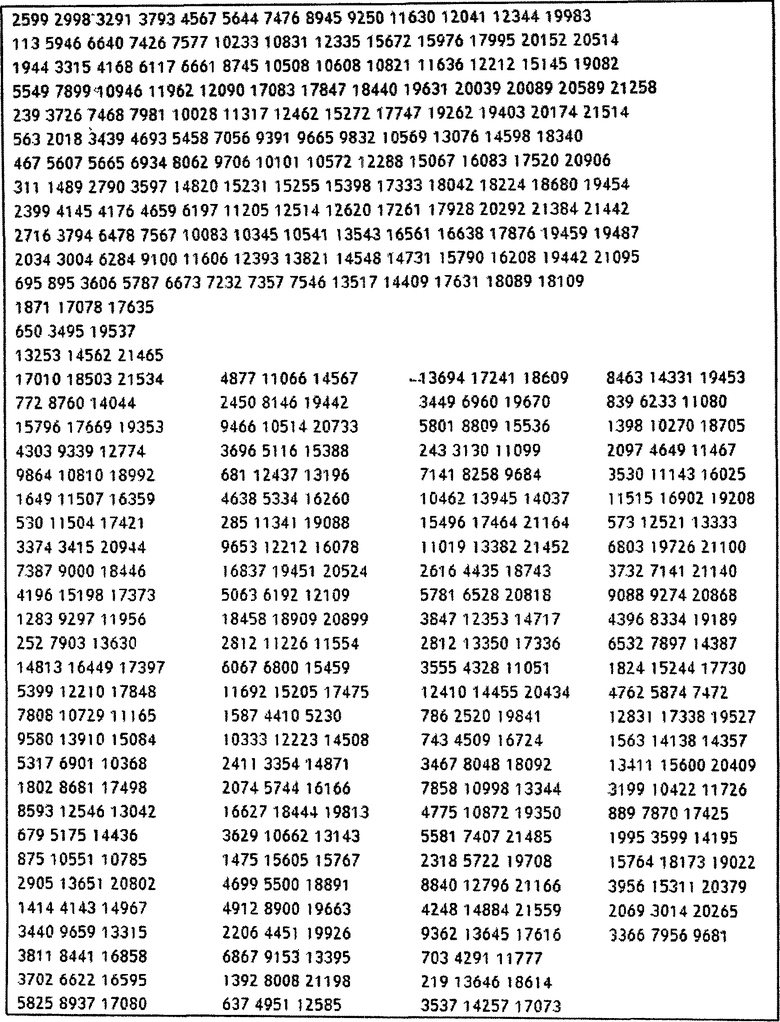

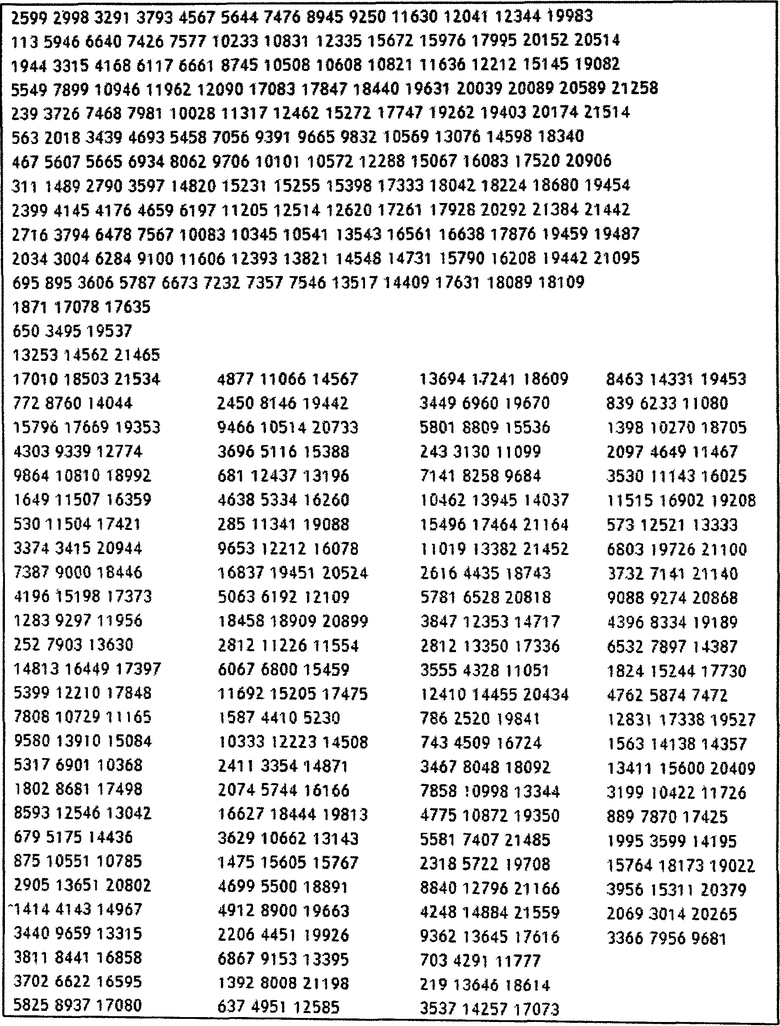

Для разработки кодов LDPC DVB-S2 с кодовой скоростью 3/5 и имеющих указанные выше параметры, из квазициклического кода LDPC, имеющего в целом N1/M1=180 блоков столбцов и q=(N1-K1)/M1=72 блоков строк, может быть получена матрица проверки четности, показанная в Таблице 1 и Таблице 2, путем применения процесса разработки кода LDPC DVB-S2. i-я последовательность позиции вес-1 в i-м столбце последовательно представляет информацию на позициях строк с единицами в i-й группе столбцов.

Таблица 1

Таблица 2

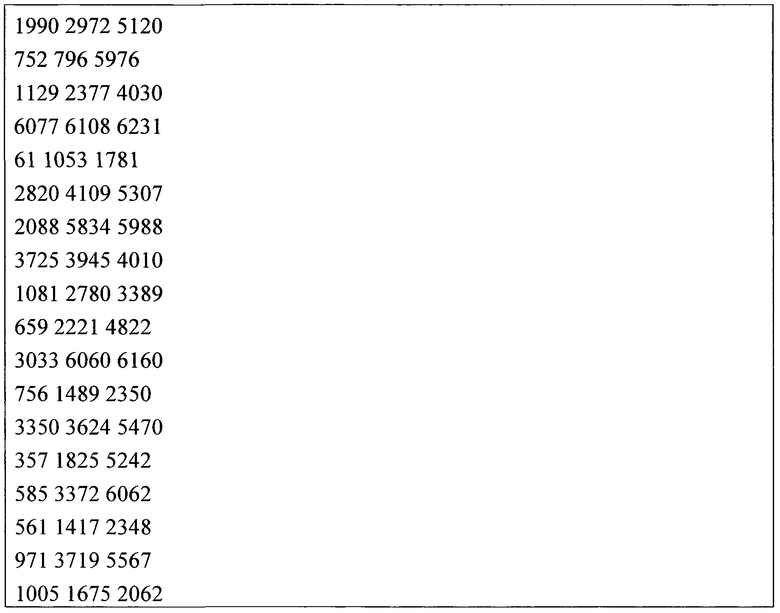

Дополнительно был разработан код LDPC DVB-S2, имеющий следующие параметры:

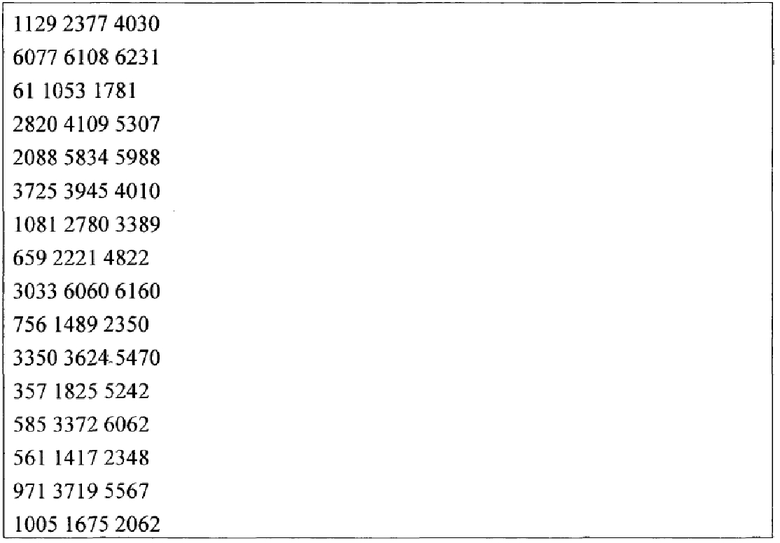

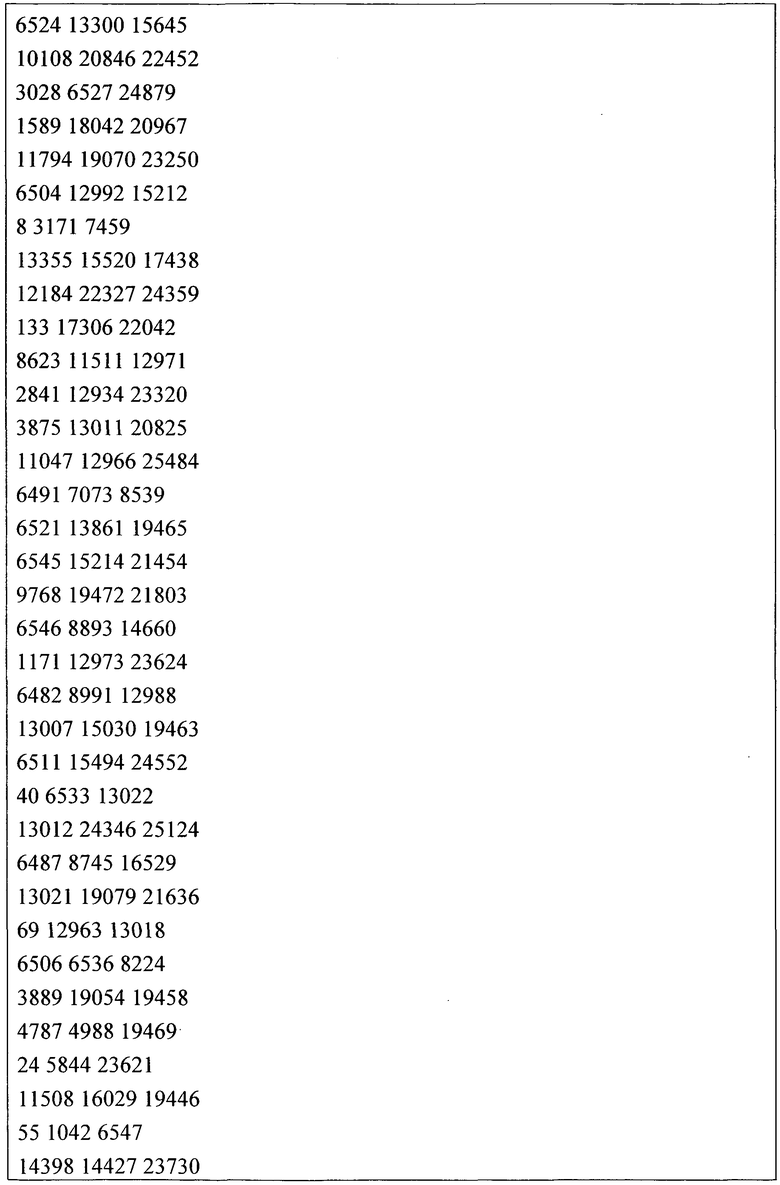

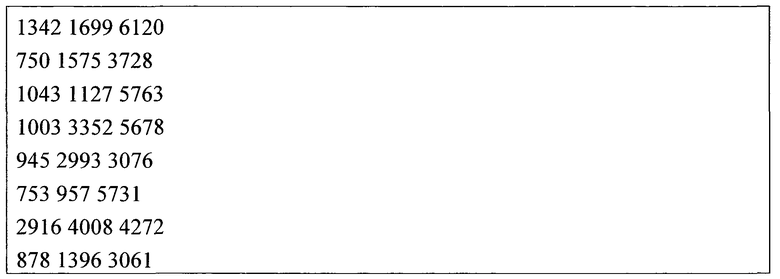

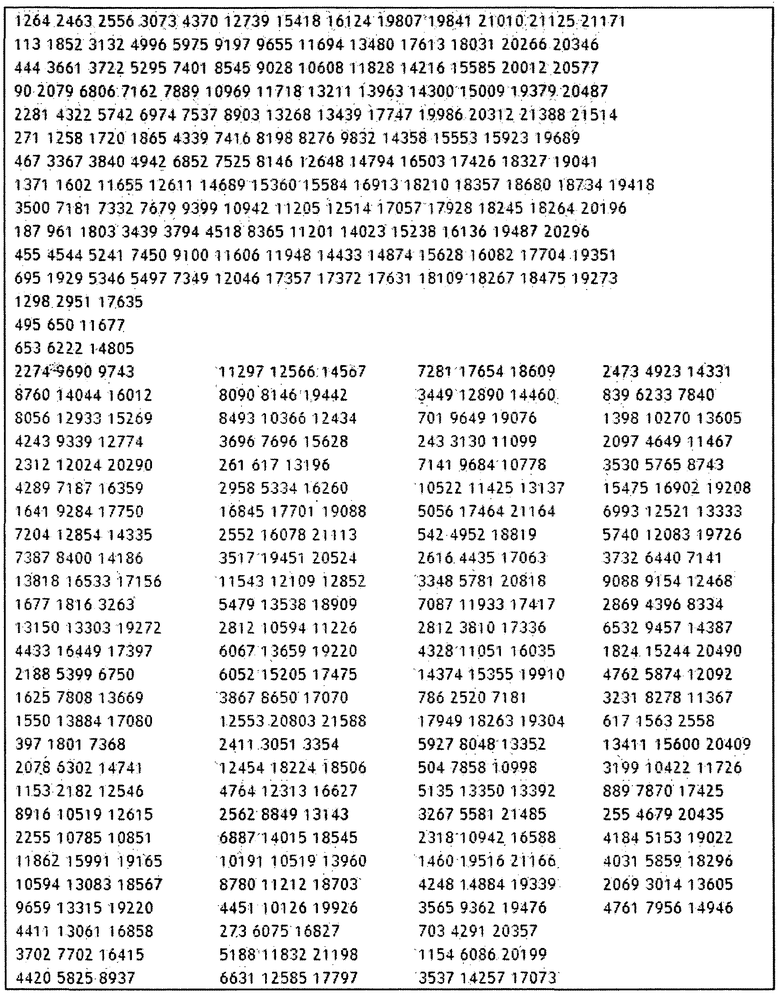

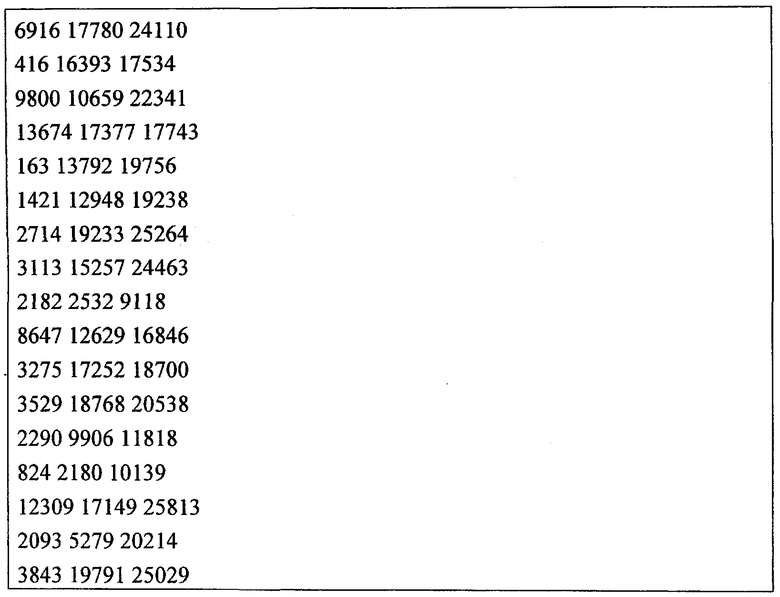

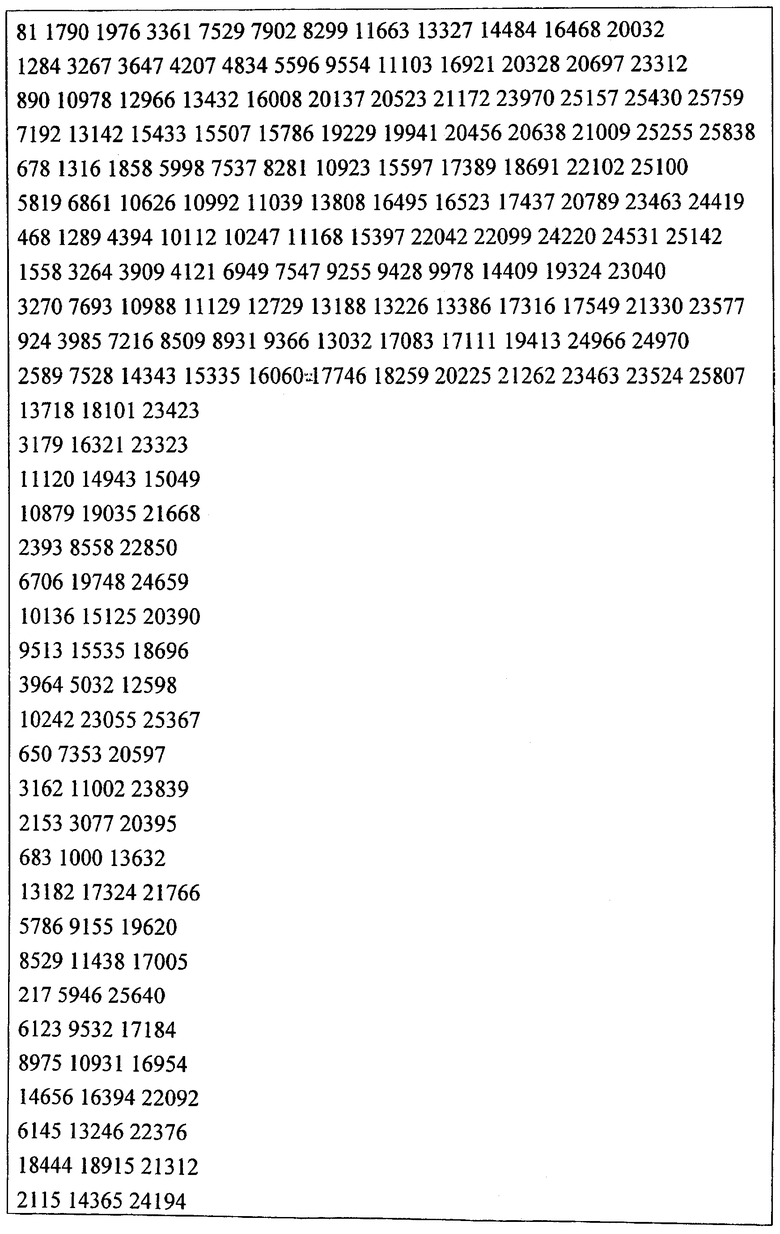

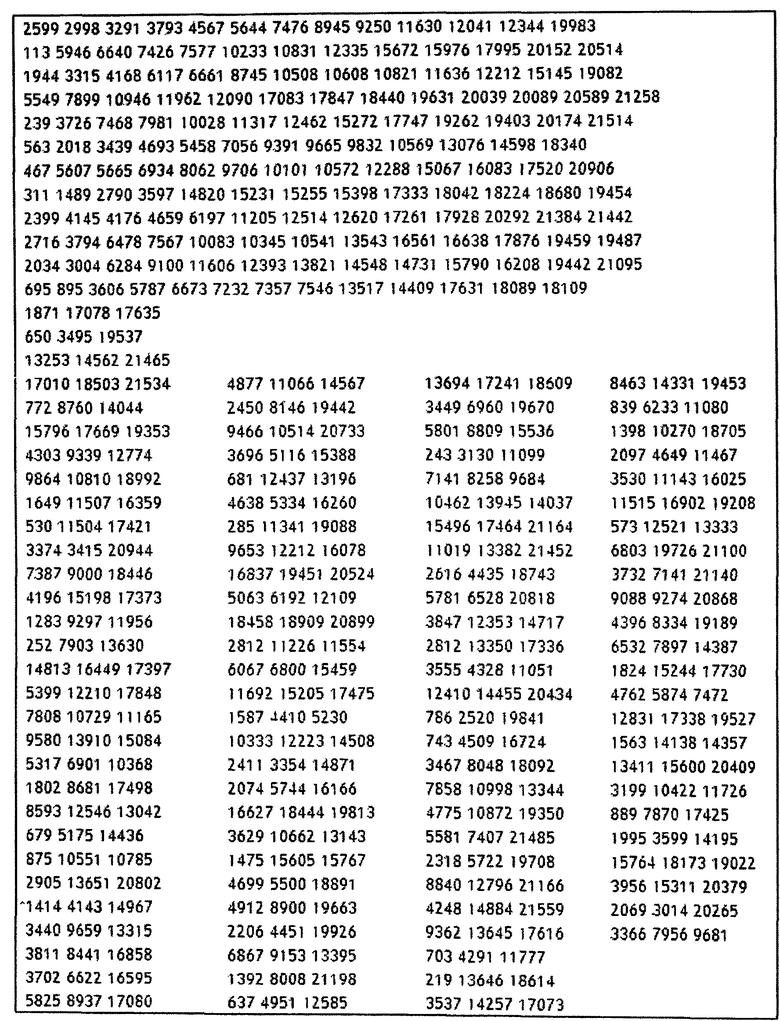

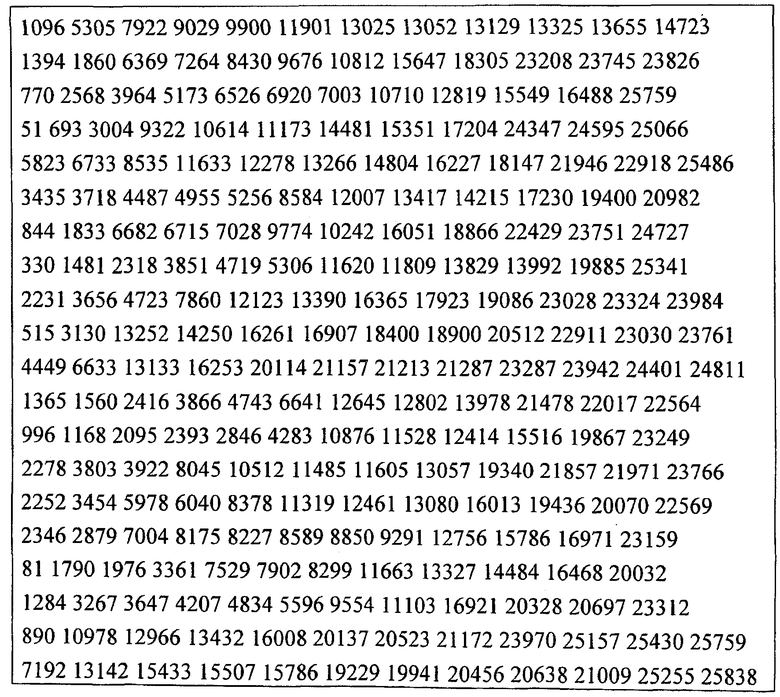

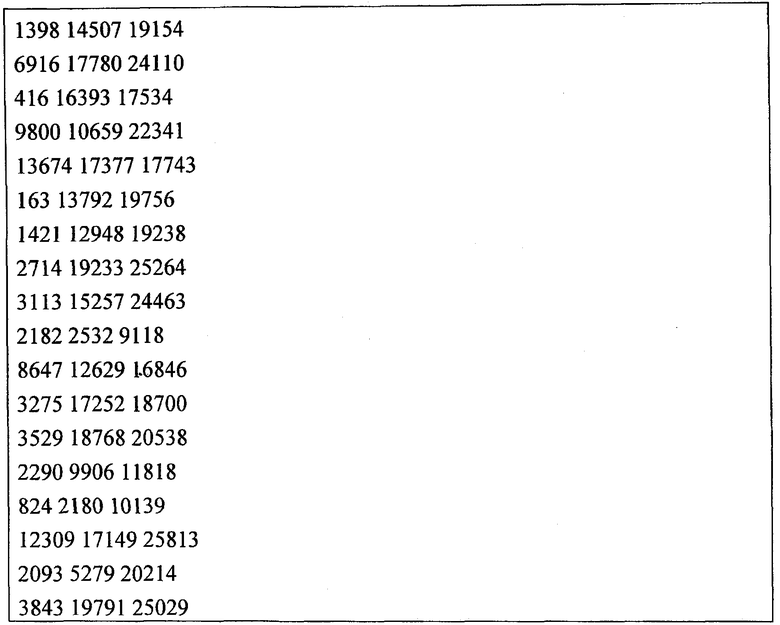

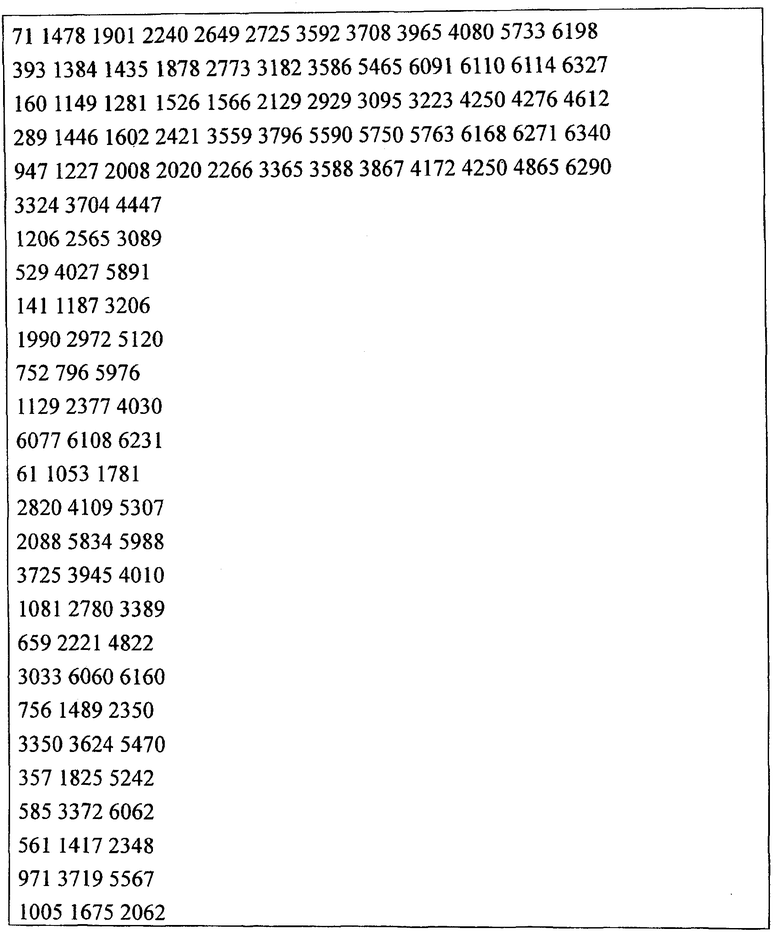

Для разработки кодов LDPC DVB-S2 с кодовой скоростью 3/5 и имеющих указанные выше параметры, из квазициклического кода LDPC, имеющего в целом N1/M1=45 блоков столбцов и q=(N1-K1)/M1=18 блоков строк, может быть получена матрица проверки четности, показанная в Таблицах 3-6, путем применения процесса разработки кода LDPC DVB-S2. i-я последовательность позиции вес-1 в i-м столбце последовательно представляет информацию на позициях строк с единицами в i-й группе столбцов.

Таблица 3

Таблица 4

Таблица 5

Таблица 6

Сравнение производительности между разработанным кодом LDPC DVB-S2 и существующим кодом LDPC DVB-S2 показано на фиг.9. Фиг.9 представляет собой диаграмму, иллюстрирующую результаты компьютерного моделирования кода LDPC DVB-S2 в соответствии с одним из вариантов осуществления настоящего изобретения.

Очевидно, что если канал с аддитивным гауссовским белым шумом (AWGN) использует в качестве схемы модуляции двухпозиционную фазовую манипуляцию (BPSK), улучшение производительности примерно 0,15 дБ происходит при BER=10-4. Улучшение производительности кода LDPC DVB-S2 с кодовой скоростью 3/5 может быть достигнуто путем простого изменения информации о матрице проверки четности, как показано в Таблицах 1-6.

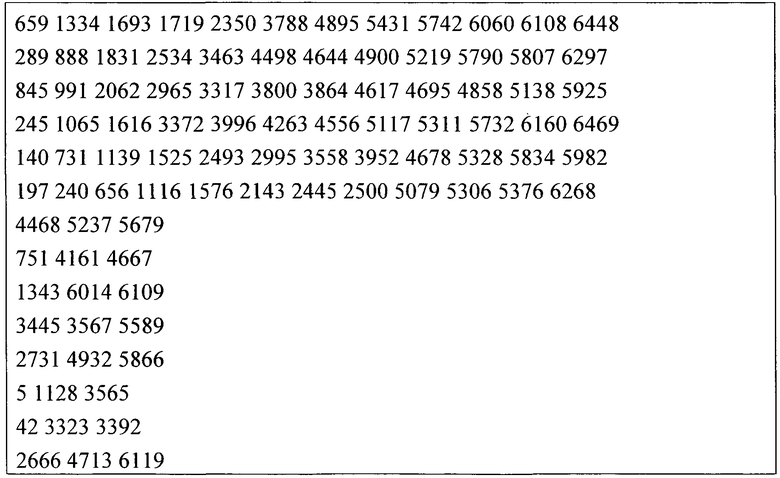

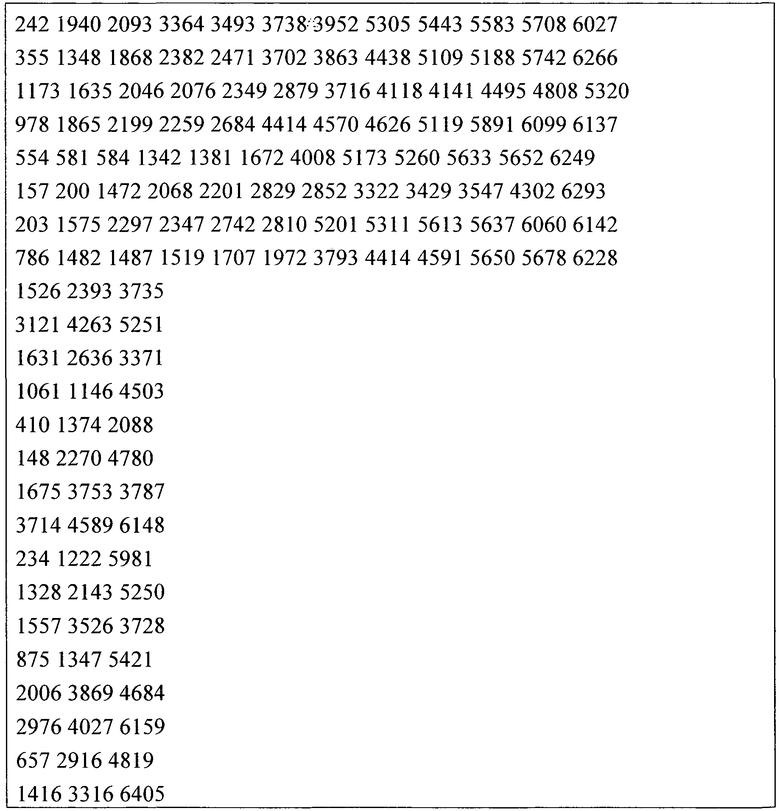

Процесс разработки кода LDPC DVB-S2, описанный со ссылками на фиг.8, может быть использован не только для кодовой скорости 3/5, но и для других кодовых скоростей. Код LDPC DVB-S2, имеющий приведенные ниже параметры был разработан в качестве примера разработки кода LDPC DVB-S2, имеющего другую кодовую скорость.

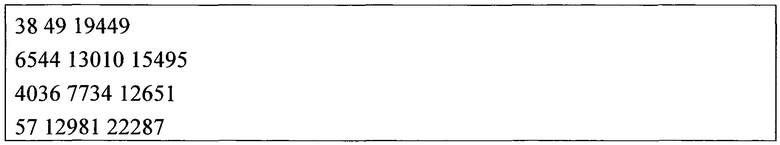

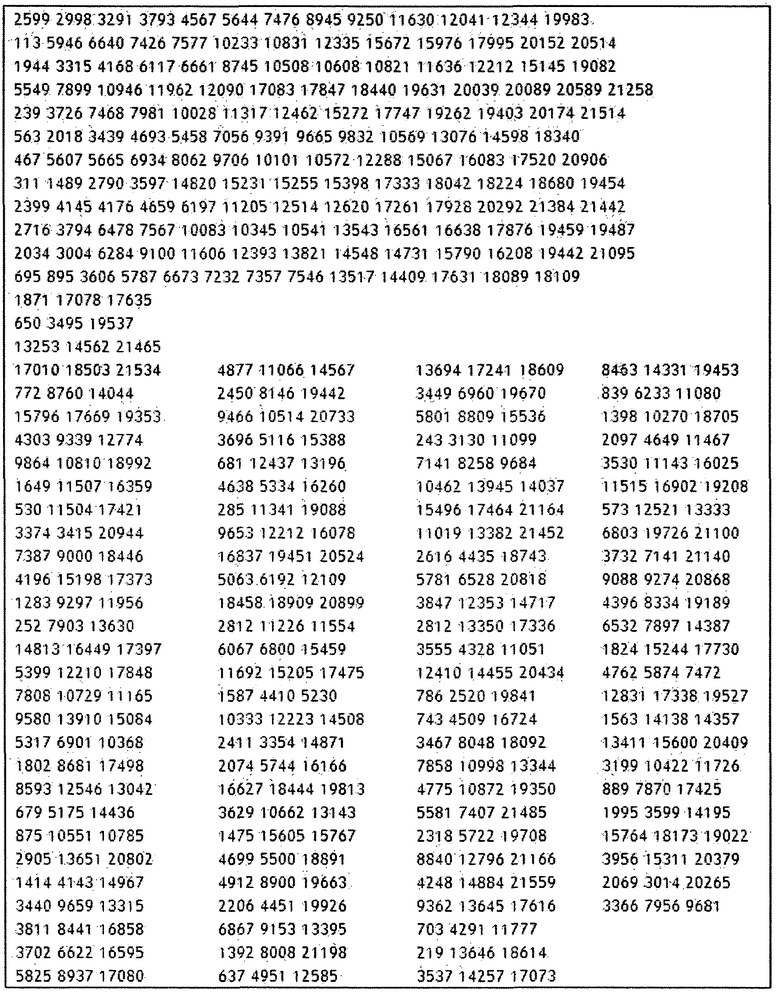

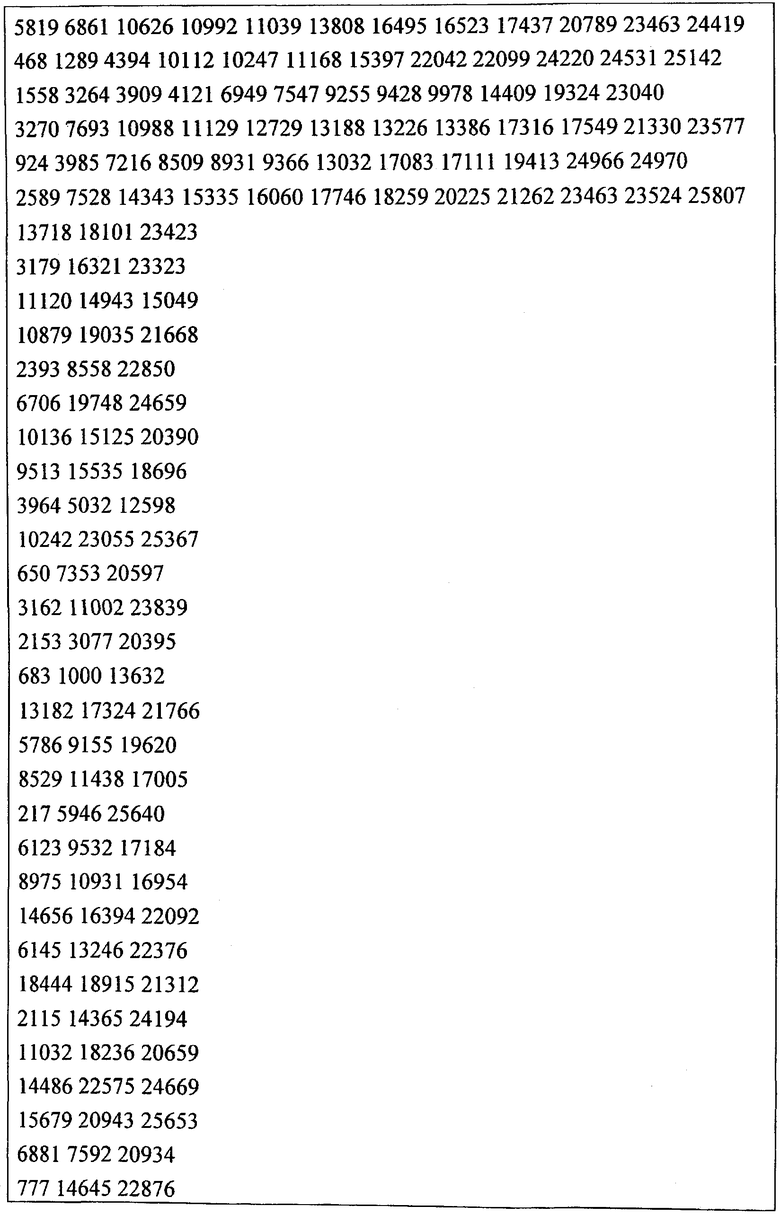

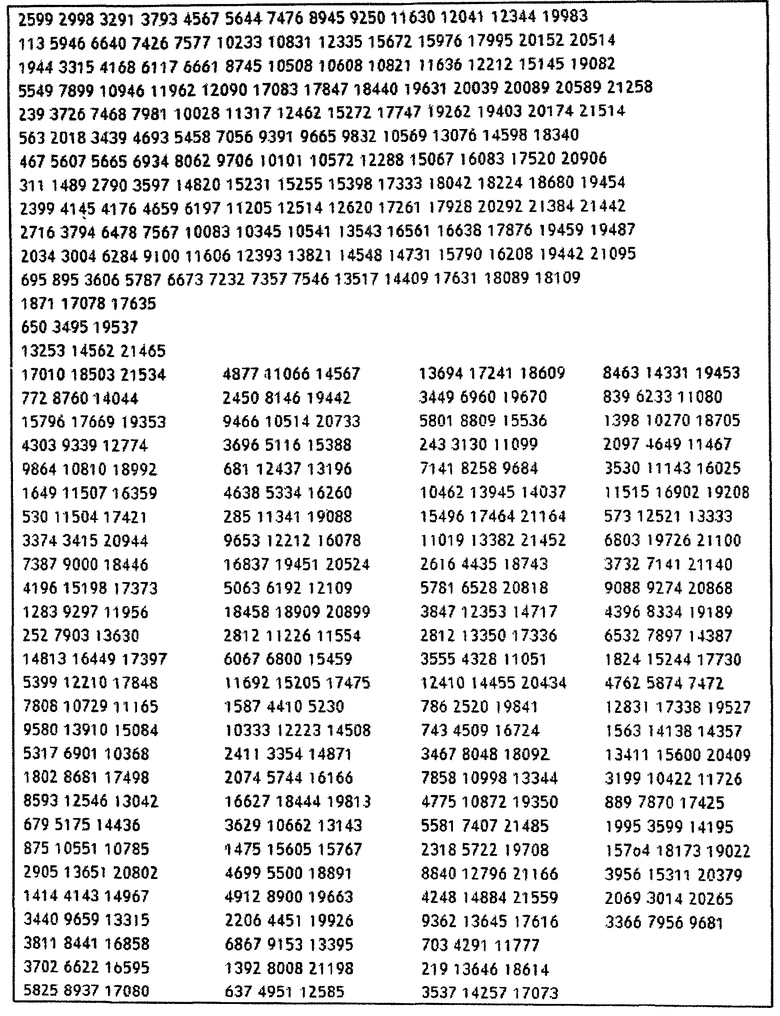

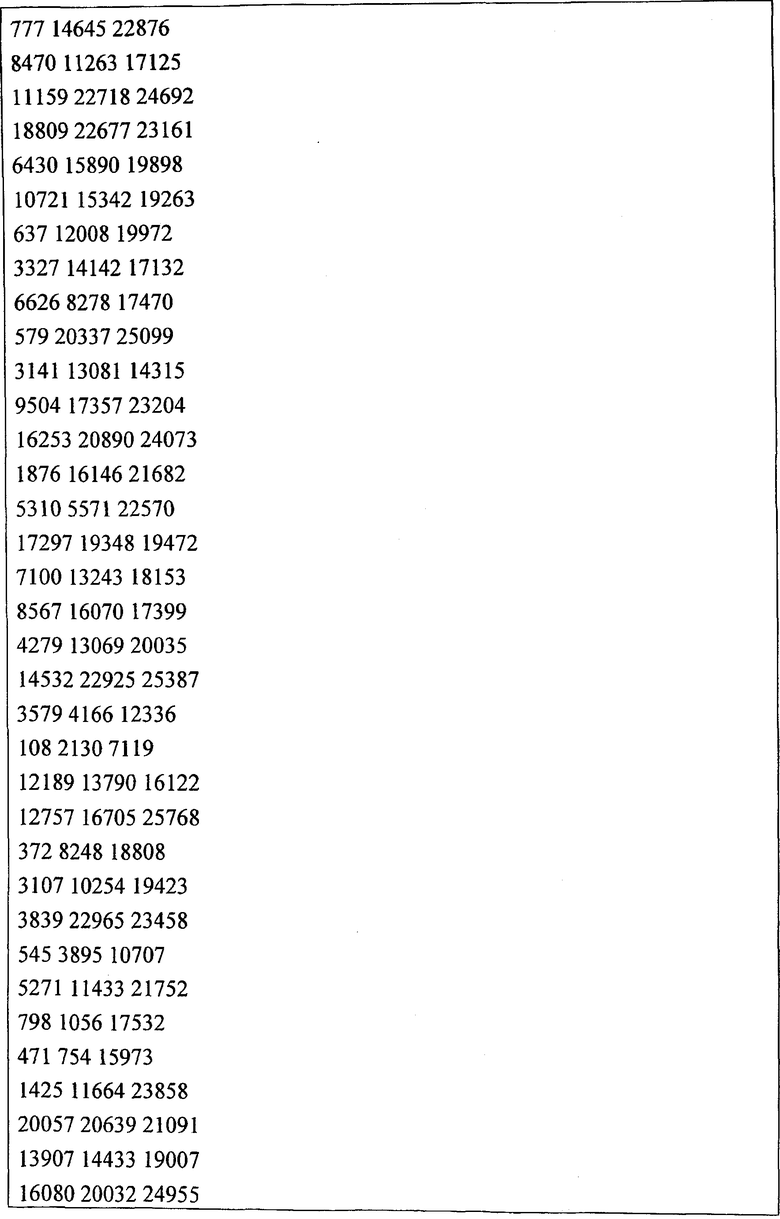

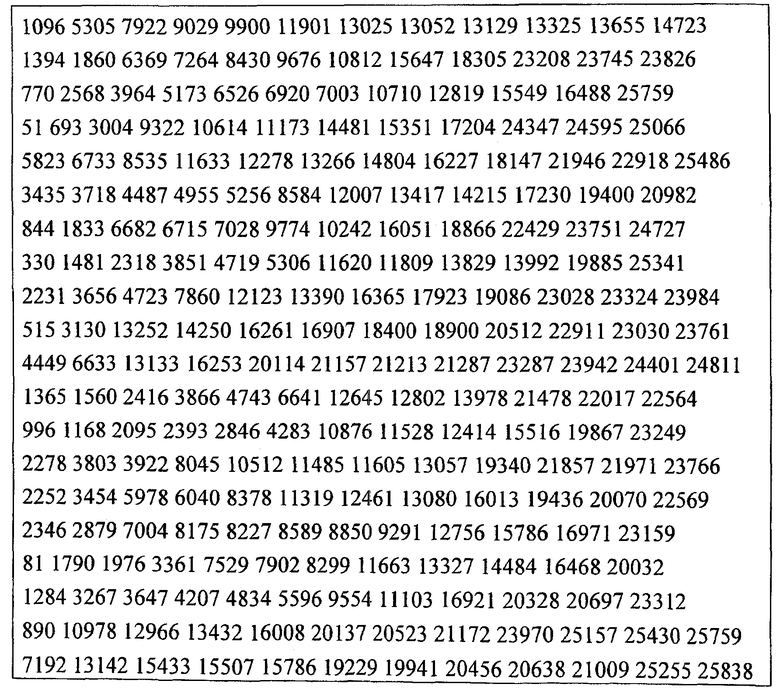

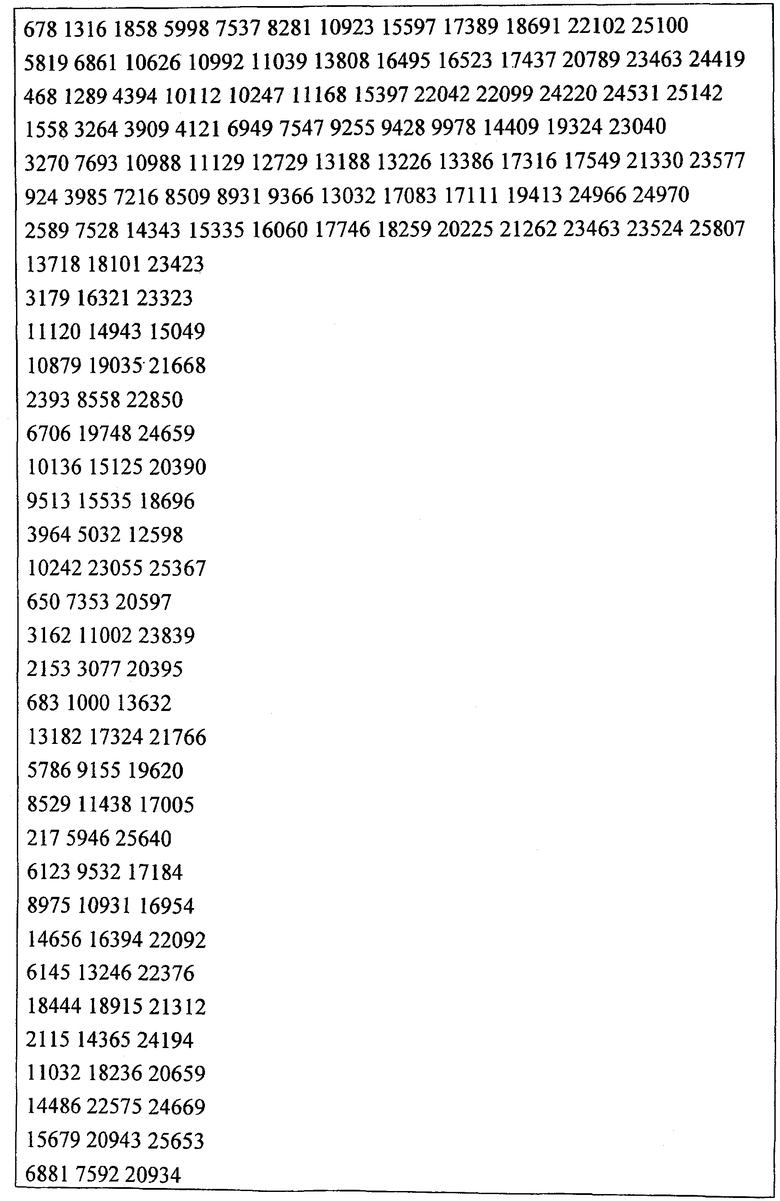

Для разработки кодов LDPC DVB-S2 с кодовой скоростью 2/3 и имеющих указанные выше параметры, из квазициклического кода LDPC, имеющего в целом N1/M1=180 блоков столбцов и q=60 блоков строк, может быть получена матрица проверки четности, показанная в Таблицах 7-10, путем применения процесса разработки кода LDPC DVB-S2 по фиг.8.

Таблица 7

Таблица 8

Таблица 9

Таблица 10

Как показано на фиг.10, сообщение u вводят в кодер 1011 LDPC в передатчике 1010 перед передачей в приемник 1030. Затем кодер 1011 LDPC кодирует введенное сообщение u предоставляет закодированный сигнал c в модулятор 1013. Модулятор 1013 модулирует кодированный сигнал и передает модулированный сигнал s в приемник 1030 через беспроводной канал 1020. Затем демодулятор 1031 в приемнике 1030 демодулирует сигнал r, переданный передатчиком 1010, и выдает демодулированный сигнал x в декодер 1033 LDPC. Затем декодер 1033 LDPC вычисляет оценку u сообщения из данных, принятых по беспроводному каналу.

Подробная структура передающего устройства в системе связи, использующей переработанный код LDPC DVB-S2, показан на фиг.11. фиг.11 представляет собой блок-схему, иллюстрирующую структуру передающего устройства, использующего переработанный код LDPC DVB-S2, в соответствии с одним из вариантов осуществления настоящего изобретения.

Передающее устройство включает в себя контроллер 1130, устройство 1110 извлечения матрицы проверки четности кода LDPC и кодер 1150 LDPC.

Устройство 1110 извлечения матрицы проверки четности кода LDPC извлекает матрицы проверки четности кода LDPC в соответствии с требованиями системы. Матрица проверки четности кода LDPC может быть извлечена из информации последовательностей в Таблицах 1-10, может быть извлечена из памяти, в которой хранится матрица проверки четности, может быть предоставлена в передающее устройство или может быть сгенерирована в передающем устройстве.

Контроллер 1130 выполнен с возможностью определения необходимой матрицы проверки четности в соответствии с кодовой скоростью, длины кодового слова, или информационной длины, таким образом, чтобы удовлетворить требованиям системы.

Кодер 1150 LDPC выполняет кодирование, основываясь на информации о матрице проверки четности кода LDPC, считанной контроллером 1130 и устройством 1110 извлечения матрицы проверки четности кода LDPC.

Фиг.12 представляет собой блок-схему, иллюстрирующую структуру приемного устройства в соответствии с одним из вариантов осуществления настоящего изобретения.

На фиг.12 проиллюстрировано приемное устройство для приема сигнала, переданного из системы связи, использующее переработанный код LDPC DVB-S2 и восстанавливающее необходимые пользователю данные из принятого сигнала.

Приемное устройство включает в себя контроллер 1250, устройство 1230 принятие решения по матрице проверки четности, устройство 1270 извлечения матрицы проверки четности кода LDPC, демодулятор 1210 и декодер 1290 LDPC.

Демодулятор 1210 демодулирует принятый код LDPC и направляет демодулированный сигнал в устройство 1230 принятие решения по матрице проверки четности и декодер 1290 LDPC.

Устройство 1230 принятия решения по матрице проверки четности кода LDPC, под управлением контроллера 1250, основываясь на демодулированном сигнале, принимает решение о матрице проверки четности кода LDPC, используемой в системе.

Контроллер 1250 направляет результат принятия решения из устройства 1230 принятие решения по матрице проверки четности в устройство 1270 извлечения матрицы проверки четности кода LDPC и декодер 1290 LDPC.

Устройство 1270 извлечения матрицы проверки четности кода LDPC, под управлением контроллера 1250, извлекает матрицу проверки четности кода LDPC, требуемую системой, и направляет извлеченную матрицу проверки четности в декодер 1290 LDPC. Как уже указывалось выше, матрица проверки четности кода LDPC может быть извлечена из информации последовательностей в Таблицах 1-10, может быть извлечена из памяти, в которой хранится матрица проверки четности, может быть предоставлена в передающее устройство или может быть сгенерирована в передающем устройстве.

Декодер 1290 LDPC, под управлением контроллера 1250, выполняет декодирование, основываясь на принятом сигнале, направленном из демодулятора 1210 и информации о матрице проверки четности кода LDPC, направленной из устройства 1270 извлечения матрицы проверки четности кода LDPC.

На фиг.13 показана блок-схема последовательности операций для приемного устройства по фиг.12.

На этапе 1301 демодулятор 1210 принимает сигнал, переданный из системы связи, использующей переработанный код LDPC DVB-S2, и демодулирует принятый сигнал. После этого, на этапе 1303, устройство 1230 принятия решения по матрице проверки четности кода LDPC, основываясь на демодулированном сигнале, принимает решение в отношении матрицы проверки четности кода LDPC, используемой в системе.

На этапе 1305 результат принятия решения из устройства 1230 принятия решения по матрице проверки четности направляется в устройство 1270 извлечения матрицы проверки четности кода LDPC. На этапе 1307 устройство 1270 извлечения матрицы проверки четности кода LDPC извлекает извлечения матрицу проверки четности кода LDPC, требуемую системой, направляет ее в декодер 1290 LDPC.

Как уже указывалось выше, матрица проверки четности кода LDPC может быть извлечена из информации последовательностей в Таблицах 1-10, может быть извлечена из памяти, в которой хранится матрица проверки четности, может быть предоставлена в передающее устройство или может быть сгенерирована в передающем устройстве.

После этого, на этапе 1309, декодер 1290 LDPC выполняет декодирование, основываясь на информации о матрице проверки четности кода LDPC, направленной из устройства 1270 извлечения матрицы проверки четности кода LDPC.

Как следует из приведенного описания, настоящее изобретение оптимизирует характеристики графа Таннера при разработке кода LDPC DVB-S2, тем самым оптимизируя производительность системы связи, использующей код LDPC.

Хотя изобретение было описано на примере определенного предпочтительного варианта осуществления, специалист в данной области техники может выполнить различные изменения и модификации без отхода от сущности и объема изобретения, определенных в прилагаемой формуле изобретения.

Изобретение относится к системам связи, использующим коды с низкой плотностью проверок на четность. Раскрыты устройство и способ кодирования канала в системе связи, использующий код с низкой плотностью проверок четности (LDPC). Определяют параметры для разработки кода LDPC и формируют первую матрицу проверки четности квазициклического кода LDPC в соответствии с упомянутыми определенными параметрами. Создают вторую матрицу проверки четности посредством удаления заранее заданной доли части четности в первой матрице проверки четности и создают третью матрицу проверки четности посредством переупорядочивания второй матрицы проверки четности. Технический результат - обеспечение эффективного улучшения характеристик циклов при разработке кодов LDPC, имеющих структуру DVB-S2. 12 н. и 4 з.п. ф-лы, 13 ил., 13 табл.

1. Способ кодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащий этапы, на которых:

считывают сохраненную матрицу проверки четности; и

выполняют LDPC кодирование сигнала, используя сохраненную матрицу проверки четности,

причем кодовая скорость составляет 3/5, длина кодового слова составляет 16200, и матрицу проверки четности формируют, как определено в нижеследующей таблице:

2. Способ по п.1, в котором матрица проверки четности имеет множество групп столбцов, полученных с помощью группировки столбцов, соответствующих информационному слову, причем каждая группа столбцов имеет заранее заданное количество столбцов; и

каждая строка в упомянутой таблице включает информацию последовательности, указывающую на позиции строк, в которых '1' расположена в соответствующей группе столбцов матрицы проверки четности.

3. Способ кодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащий этапы, на которых:

считывают сохраненную матрицу проверки четности; и

выполняют LDPC кодирование сигнала, используя сохраненную матрицу проверки четности,

причем кодовая скорость составляет 3/5, длина кодового слова составляет 64800, и матрицу проверки четности формируют, как определено в нижеследующей таблице:

4. Способ кодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащий этапы, на которых:

считывают сохраненную матрицу проверки четности; и

выполняют LDPC кодирование сигнала, используя сохраненную матрицу проверки четности,

причем кодовая скорость составляет 2/3, длина кодового слова составляет 64800, и матрицу проверки четности формируют, как определено в нижеследующей таблице:

5. Способ декодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащий этапы, на которых:

извлекают матрицу проверки четности кода LDPC; и

выполняют LDPC декодирование, используя извлеченную матрицу проверки четности,

причем кодовая скорость составляет 3/5, длина кодового слова составляет 16200, и матрицу проверки четности формируют, как определено в нижеследующей таблице:

6. Способ по п.5, в котором матрица проверки четности имеет множество групп столбцов, полученных с помощью группировки столбцов, соответствующих информационному слову, причем каждая группа столбцов имеет заранее заданное количество столбцов; и

каждая строка в упомянутой таблице включает информацию последовательности, указывающую на позиции строк, в которых '1' расположена в соответствующей группе столбцов матрицы проверки четности.

7. Способ декодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащий этапы, на которых:

извлекают матрицу проверки четности кода LDPC; и

выполняют LDPC декодирование, используя извлеченную матрицу проверки четности,

причем кодовая скорость составляет 3/5, длина кодового слова составляет 64800, и матрицу проверки четности формируют, как определено в нижеследующей таблице:

8. Способ декодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащий этапы, на которых:

извлекают матрицу проверки четности кода LDPC; и

выполняют LDPC декодирование, используя извлеченную матрицу проверки четности,

причем кодовая скорость составляет 2/3, длина кодового слова составляет 64800, и матрицу проверки четности формируют, как определено в нижеследующей таблице:

9. Устройство кодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащее:

блок извлечения матрицы проверки четности кода LDPC для считывания сохраненной матрицы проверки четности;

кодер LDPC для выполнения LDPC кодирования полученного сигнала, с использованием сохраненной матрицы проверки четности,

причем кодовая скорость составляет 3/5, длина кодового слова составляет 16200, и матрицу проверки четности формируют, как определено в нижеследующей таблице:

10. Устройство по п.9, в котором матрица проверки четности имеет множество групп столбцов, полученных с помощью группировки столбцов, соответствующих информационному слову, причем каждая группа столбцов имеет заранее заданное количество столбцов; и

каждая строка в упомянутой таблице включает информацию последовательности, указывающую на позиции строк, в которых '1' расположена в соответствующей группе столбцов матрицы проверки четности.

11. Устройство кодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащее:

устройство извлечения матрицы проверки четности кода LDPC для считывания сохраненной матрицы проверки четности;

кодер LDPC для выполнения LDPC кодирования полученного сигнала, с использованием сохраненной матрицы проверки четности,

причем кодовая скорость составляет 3/5, длина кодового слова составляет 64800, и матрицу проверки четности формируют, как определено в нижеследующей таблице:

12. Устройство кодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащее:

блок извлечения матрицы проверки четности кода LDPC для считывания сохраненной матрицы проверки четности;

кодер LDPC для выполнения LDPC кодирования полученного сигнала, с использованием сохраненной матрицы проверки четности,

причем кодовая скорость составляет 2/3, длина кодового слова составляет 64800, и матрицу проверки четности формируют, как определено в нижеследующей таблице:

13. Устройство декодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащее:

блок извлечения матрицы проверки четности кода LDPC для считывания сохраненной матрицы проверки четности;

декодер LDPC для выполнения LDPC декодирования, с использованием считанной матрицы проверки четности,

причем кодовая скорость составляет 3/5, длина кодового слова составляет 16200, и упомянутую считанную матрицу проверки четности формируют, как определено в нижеследующей таблице:

14. Устройство по п.13, в котором матрица проверки четности имеет множество групп столбцов, полученных с помощью группировки столбцов, соответствующих информационному слову, причем каждая группа столбцов имеет заранее заданное количество столбцов; и

каждая строка в упомянутой таблице включает информацию последовательности, указывающую на позиции строк, в которых '1' расположена в соответствующей группе столбцов матрицы проверки четности.

15. Устройство декодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащее:

блок извлечения матрицы проверки четности кода LDPC для считывания сохраненной матрицы проверки четности;

декодер LDPC для выполнения LDPC декодирования, с использованием считанной матрицы проверки четности,

причем кодовая скорость составляет 3/5, длина кодового слова составляет 64800, и упомянутую считанную матрицу проверки четности формируют, как определено в нижеследующей таблице:

16. Устройство декодирования канала в системе связи, использующей код с низкой плотностью проверок четности (LDPC), содержащее:

блок извлечения матрицы проверки четности кода LDPC для считывания сохраненной матрицы проверки четности;

декодер LDPC для выполнения LDPC декодирования, с использованием считанной матрицы проверки четности,

причем кодовая скорость составляет 2/3, длина кодового слова составляет 64800, и упомянутую считанную матрицу проверки четности формируют, как определено в нижеследующей таблице:

| KR 20070054088 A, 28.05.2007 | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| RU 2006112205 A, 10.11.2007 | |||

| EP 1653629 A, 03.05.2006 | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| US 2005283708 A1, 22.12.2005. | |||

Авторы

Даты

2012-05-10—Публикация

2009-02-18—Подача