Изобретение относится к области силовой электроники и может использоваться в синхронных системах управления силовыми вентильными преобразователями (ВП), например в тиристорных выпрямителях.

Известно устройство синхронизации (УС) прямого действия (Информационные цепи преобразователей тиристорных электроприводов / С.С.Крылов, Е.В.Мельников, Л.И.Конышев. - М.: Энергоатомиздат, 1984. - 160 с.), содержащее компаратор на операционном усилителе с резисторами цепи положительной обратной связи, подключенный к напряжению сети через разделительный понижающий трансформатор и осуществляющий выделение с помощью выходного сигнала логической «1» моментов времени перехода напряжением сети через нулевой уровень.

Недостатком известного технического решения является его низкая помехоустойчивость к импульсным помехам со стороны напряжения синхронизации, а также погрешность работы при изменениях амплитуды сигнала синхронизации.

Известно устройство синхронизации, содержащее усилитель с резисторами положительной обратной связи (регенеративный компаратор), синхронизирующий трансформатор с выпрямительными диодами и согласующий выходной транзистор (SU 1798869 СССР, Н02М 1/08. Система импульсно-фазового управления трехфазным тиристорным преобразователем / Маурер В.Г., Рахматулин P.M., Цытович Л.И. и др. - №4778744/07, заявлено 05.01.90; Опубл. 28.02.93, Бюл. №8).

Отличие УС состоит в том, что питание компаратора осуществляется от двух трехфазных нулевых схем, формирующих нестабилизированное напряжение для усилителя. При этом пороги переключения компаратора изменяются по закону выпрямленного напряжения сети. Переключение УС производится напряжением соответствующей фазы на вторичной стороне трансформатора. В результате длительность выходного импульса компаратора соответствует заданному диапазону изменения угла управления тиристорами даже для случая значительной нестабильности напряжения сети фаз А, В, С.

Недостатком известного УС является то, что высокая точность поддержания заданного диапазона регулирования тиристорами происходит только при синхронном и идентичном по уровню изменении амплитуд всех фаз напряжения сети одновременно.

Известно УС интегрирующего типа, содержащее сумматоры, интеграторы, усилители постоянного тока (релейные элементы), формирователи импульсов управления и вентильные каскады (SU 873374 СССР, Н02Р 13/16. Устройство для импульсно-фазового управления вентильным преобразователем / Гафиятуллин Р.Х., Суворов Г.В., Цытович Л.И и др. - №2680999/07; заявлено 02.11.78; Опубл. 15.10.81, Бюл. №38).

Последовательно соединенные блоки сумматора, интегратора и релейного элемента образуют развертывающий преобразователь (РП). Для перевода РП в режим внешней синхронизации необходимо, чтобы амплитуда синхронизирующего воздействия превышала амплитуду выходных импульсов релейного элемента не менее чем в 2,0 раза. В этом случае между напряжением синхронизации и выходными импульсами релейного блока устанавливается фазовый сдвиг -90 эл. град.

Недостатком известного технического решения является то, что между сигналом синхронизации и выходом релейного элемента присутствует фазовый сдвиг -90 эл. град, что ограничивает область применения подобных каналов синхронизации в целом ряде вентильных преобразователей (ВП), например в реверсивных тиристорных преобразователях с раздельным управлением. Причина заключается в том, что при сдвиге сигнала синхронизации на - 90 эл. град относительно соответствующей фазы напряжения сети ограничивается диапазон регулирования угла силовыми вентилями. В результате на вход РП необходимо подавать сигнал смещения для установки фронтов его выходных импульсов в требуемое положение. Учитывая, что под действием входного сигнала смещения изменяется положение во времени как переднего, так и заднего фронта выходного импульса РП, практически не удается при таком методе синхронизации обеспечить полный диапазон регулирования угла управления тиристорами в реверсивных преобразователях.

Наиболее близким к предлагаемому техническому решению является устройство синхронизации (RU 2383985 Российская Федерация, МПК7 Н02М 1/08. Устройство синхронизации / Л.И.Цытович, М.М.Дудкин, А.В.Качалов, P.M.Рахматулин. - №2008142655/09; заявл. 27.10.08; опубл. 10.03.10, Бюл. №7).

Устройство-прототип содержит два развертывающих преобразователя, каждый из которых состоит из последовательно соединенных сумматора, интегратора и релейного элемента, выход которого подключен к первому входу сумматора. Одновременно выход первого развертывающего преобразователя соединен с входом второго РП через последовательно включенные амплитудный модулятор и пропорционально-дифференцирующее звено, второй вход сумматора первого РП является «входом» УС, а выход релейного элемента второго РП - «выходом» УС. Вход УС подключен также к входу демодулятора, на выходе которого включен сглаживающий фильтр, выход которого соединен со вторым входом амплитудного модулятора.

Первый РП синхронизируется с напряжением сети, а второй - с выходным сигналом амплитудного модулятора. При этом амплитуда импульсов с выхода амплитудного модулятора зависит от амплитуды напряжения сети. В результате устройство-прототип представляет собой апериодическое звено второго порядка с постоянными времени, зависящими от параметров (амплитуды и частоты) напряжения сети.

Недостатком устройства-прототипа является повышенный температурный дрейф «нуля», обусловленный дрейфовыми параметрами амплитудного модулятора, приводящими к колебаниям амплитуды сигнала синхронизации второго РП. Кроме того, УС имеет ограниченные функциональные возможности, так как с его помощью можно синхронизировать лишь определенный тип вентильных преобразователей, например однофазные управляемые выпрямители.

Таким образом, устройство-прототип характеризуется низкой точностью, ограниченными функциональными возможностями и, следовательно, областью применения.

В основу изобретения положена техническая задача, направленная на повышение точности работы и расширение функциональных возможностей устройства синхронизации.

Указанная техническая задача решается тем, что в устройство синхронизации, содержащее первый блок синхронизации, в состав которого входят первый сумматор, первый интегратор, первый релейный элемент, второй сумматор, второй интегратор и второй релейный элемент, причем вход первого блока синхронизации соединен с шиной фазы А напряжения сети, согласно изобретению введены второй и третий блоки синхронизации, первый и второй двоично-десятичные дешифраторы и три логических блока, каждый из которых содержит шесть элементов функции «2И» и один элемент «6ИЛИ», входы последнего подключены к выходам элементов «2И», а выход элемента «6ИЛИ» является одним из «выходов» устройства синхронизации, при этом входы второго и третьего блоков синхронизации соединены с шинами фаз В и С соответственно, первый выход каждого из блоков синхронизации подключен к входам первого двоично-десятичного дешифратора с весом 20, 21 и 22 соответственно, второй выход каждого из блоков синхронизации подключен к входам второго двоично-десятичного дешифратора с весом 20, 21 и 22 соответственно, вход первого и второго двоично-десятичного дешифратора, имеющий вес 23, подключен к шине нулевого потенциала, входы элементов «2И» первого, второго и третьего логических блоков соединены с соответствующими выходными шинами первого и второго двоично-десятичных дешифраторов, при этом каждый из блоков синхронизации содержит последовательно включенные первый пропорциональный четырехполюсник, первый сумматор, первый интегратор, первый релейный элемент, второй пропорциональный четырехполюсник, второй сумматор, второй интегратор, второй релейный элемент, причем выход первого релейного элемента через третий пропорциональный четырехполюсник подключен ко второму входу первого сумматора и через первый инвертирующий ключ соединен с первым выходом блока синхронизации, а выход второго релейного элемента через четвертый пропорциональный четырехполюсник подключен ко второму входу второго сумматора и через второй инвертирующий ключ соединен со вторым выходом блока синхронизации, вход первого пропорционального четырехполюсника является «входом» блока синхронизации.

В результате поставленная техническая задача достигается за счет того, что в устройство введены второй и третий блоки синхронизации, первый и второй двоично-десятичные дешифраторы и три логических блока, каждый из которых содержит шесть элементов функции «2И» и один элемент «6ИЛИ». При этом выходные сигналы блоков синхронизации рассматриваются в качестве двоично-десятичного кода, когда требуемому интервалу коммутации в 30 эл. град соответствует вполне определенное сочетание двоично-десятичных чисел. Затем эти числа объединяются по функции «ИЛИ», что позволяет сформировать сигнал синхронизации любой продолжительности для любых схем управляемых выпрямителей постоянного тока как однофазных, так и трехфазных. Кроме этого, предлагаемое устройство синхронизации обладает возможностью диагностирования вентильного преобразователя (ВП), например от неправильного чередования фаз А, В, С напряжения сети, а также позволяет производить защиту ВП от перехода какого-либо канала синхронизации в результате своей неисправности в статическое состояние (логический «0» или «1»), а также в случае срыва режима внешней синхронизации в блоках синхронизации и их перехода в состояние автоколебаний. Последние обстоятельства однозначно свидетельствуют о расширении функциональных возможностей предлагаемого устройства.

Повышенная точность предлагаемого устройства объясняется тем, что в его блоках синхронизации отсутствует амплитудный модулятор, приводящий к колебаниям амплитуды сигнала синхронизации второго развертывающего преобразователя из-за его повышенного температурного дрейфа «нуля».

Таким образом, предлагаемое устройство обладает повышенной точностью в работе и расширенными функциональными возможностями при построении систем импульсно-фазового управления как однофазными, так и трехфазными вентильными преобразователями.

Изобретение поясняется чертежами

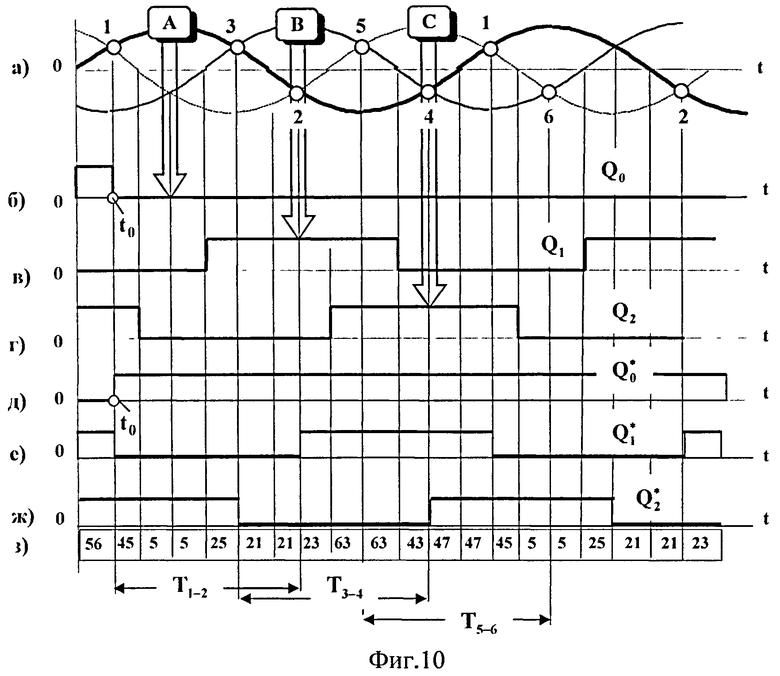

Фиг.1 - функциональная схема каскадного интервало-кодового двоично-десятичного устройства синхронизации.

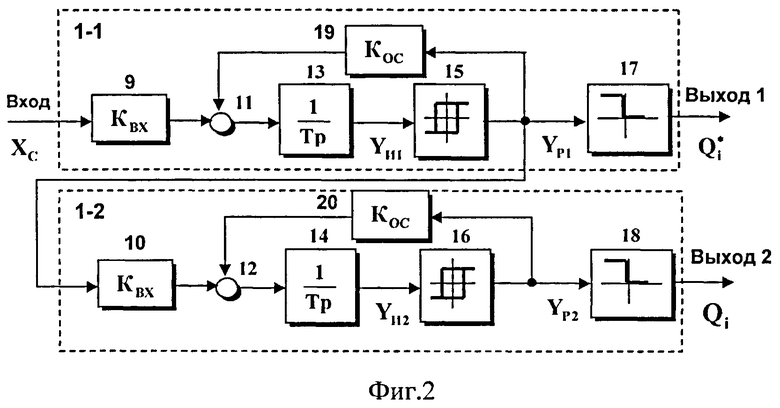

Фиг.2 - функциональная схема блока синхронизации, например, фазы А.

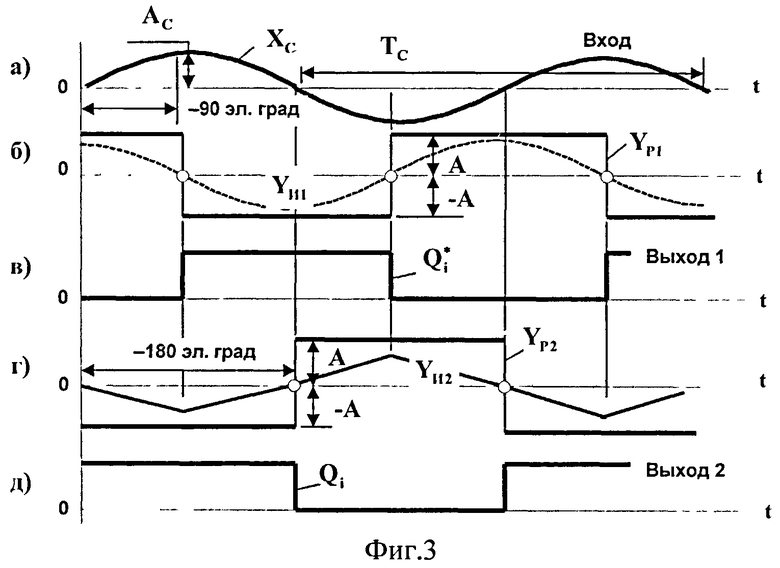

Фиг.3а, б, в, г, д - временные диаграммы сигналов блока синхронизации, например, фазы А.

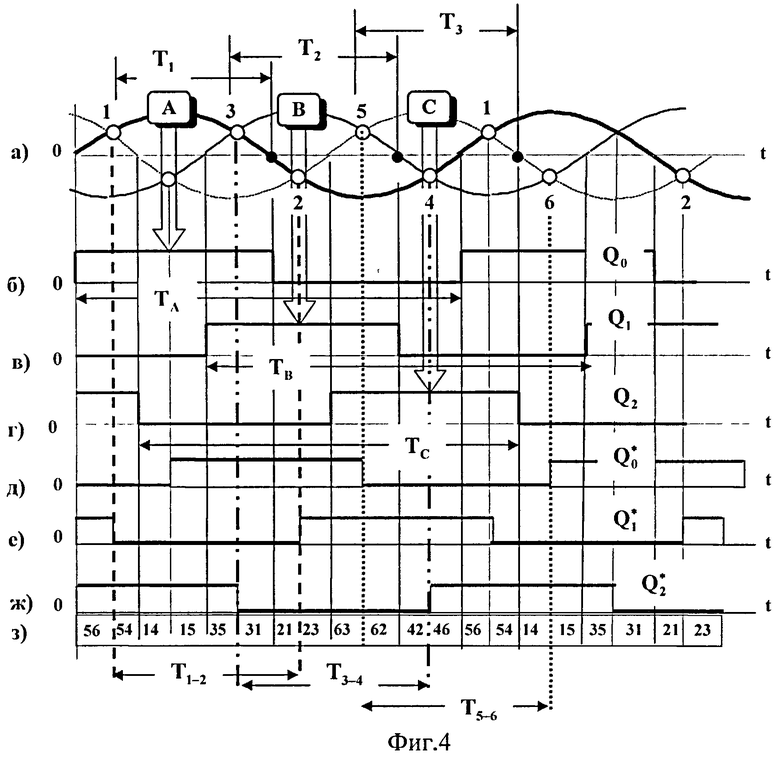

Фиг.4а, б, в, г, д, е, ж, з - временные диаграммы сигналов каскадного интервало-кодового двоично-десятичного устройства синхронизации.

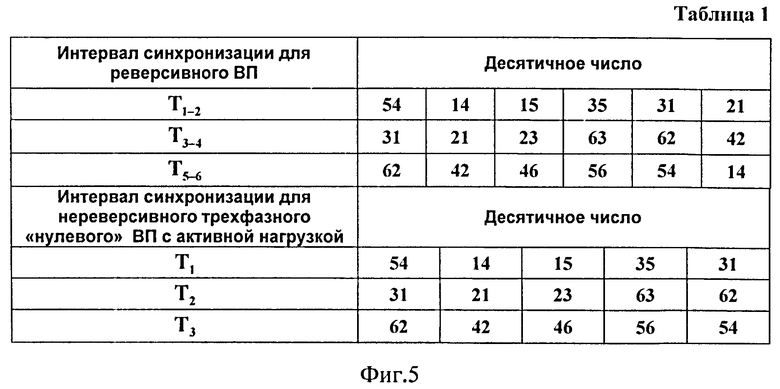

Фиг.5 - таблица 1 кодовых состояний фиг.4.

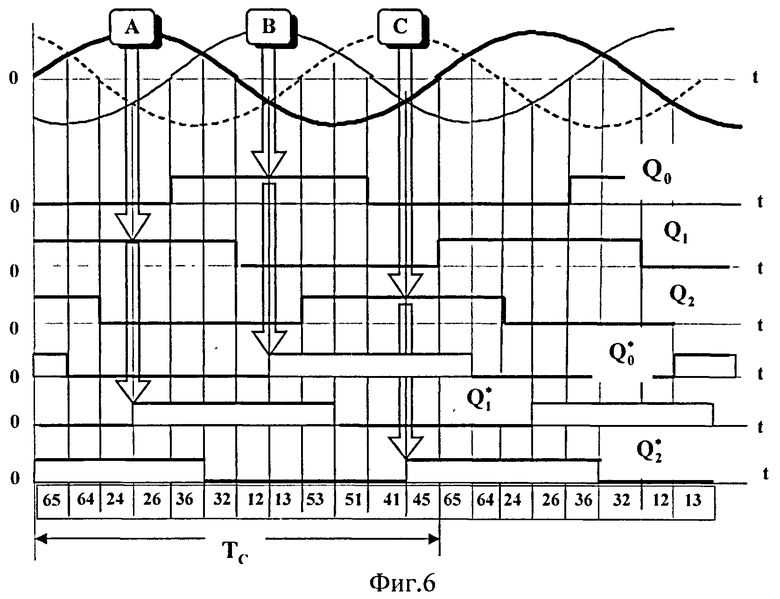

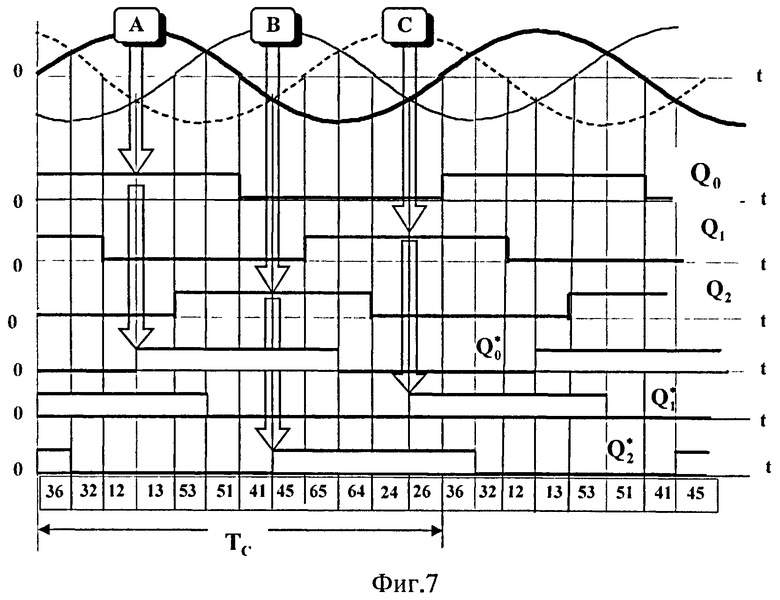

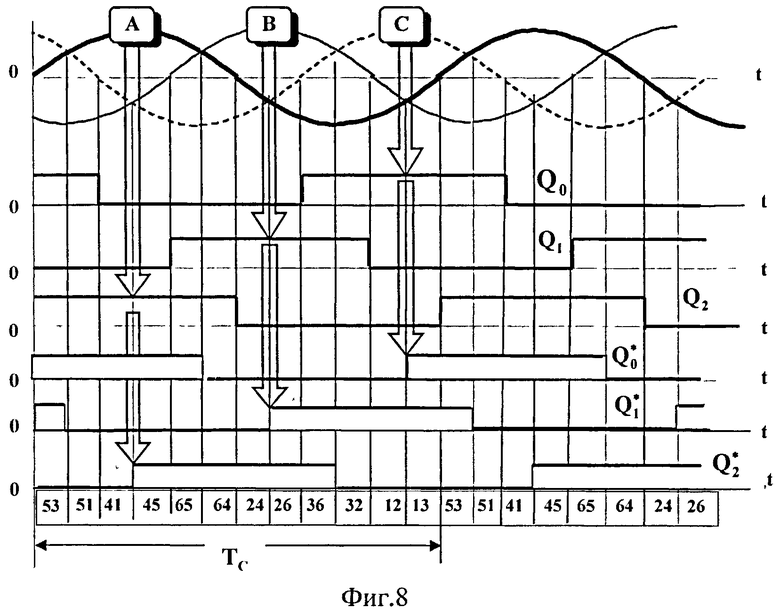

Фиг.6, 7, 8 - временные диаграммы сигналов каскадного интервало-кодового двоично-десятичного устройства синхронизации при неправильном чередовании фаз напряжения сети.

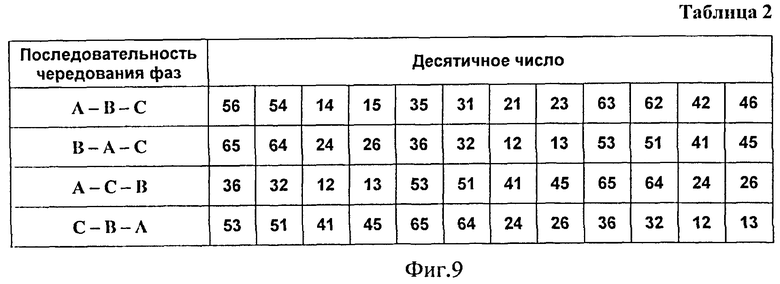

Фиг.9 - таблица 2 кодовых состояний к фиг.6, 7, 8.

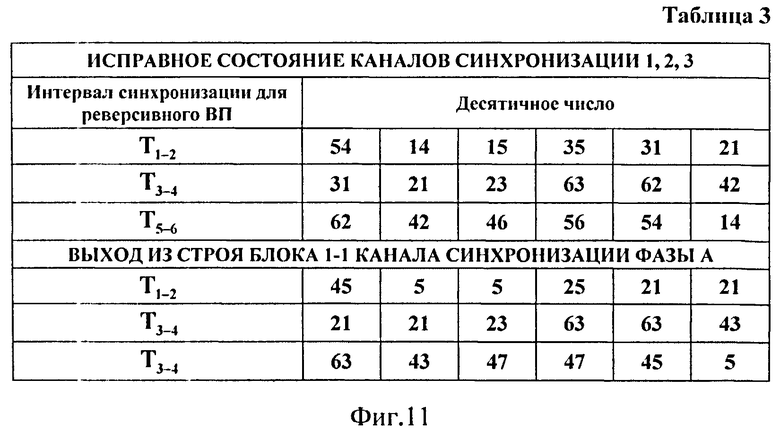

Фиг.10а, б, в, г, д, е, ж, з - временные диаграммы сигналов каскадного интервало-кодового двоично-десятичного устройства синхронизации при катастрофическом отказе релейного элемента.

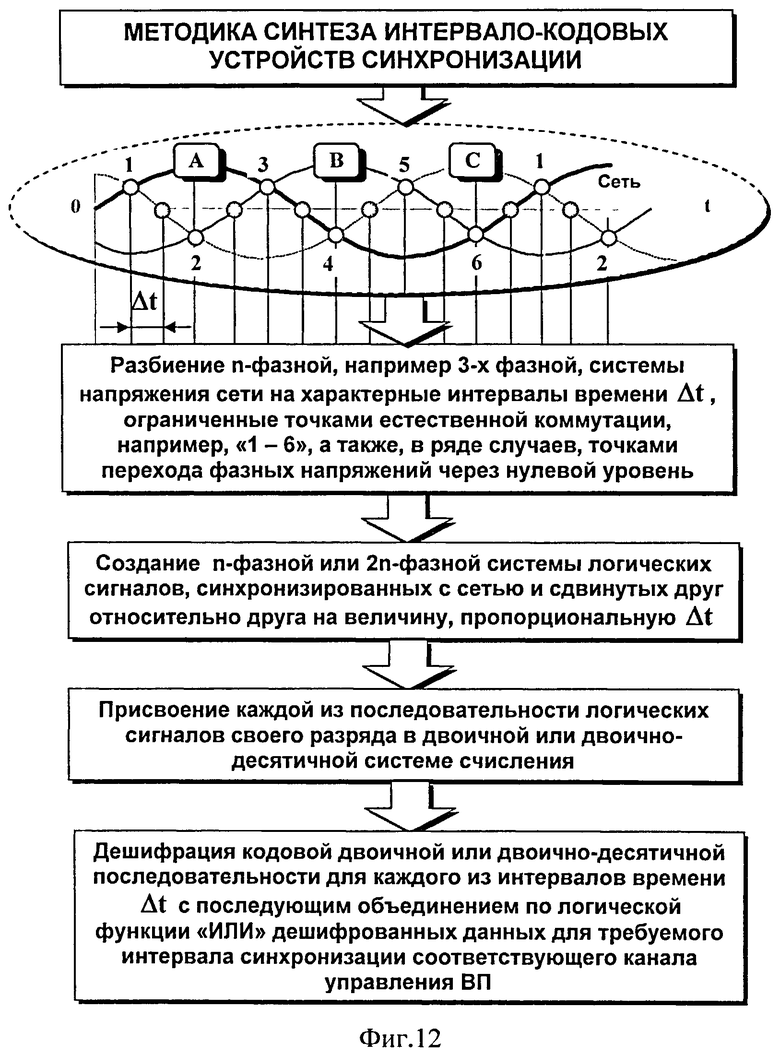

Фиг.11 - таблица 3 кодовых состояний фиг.10.

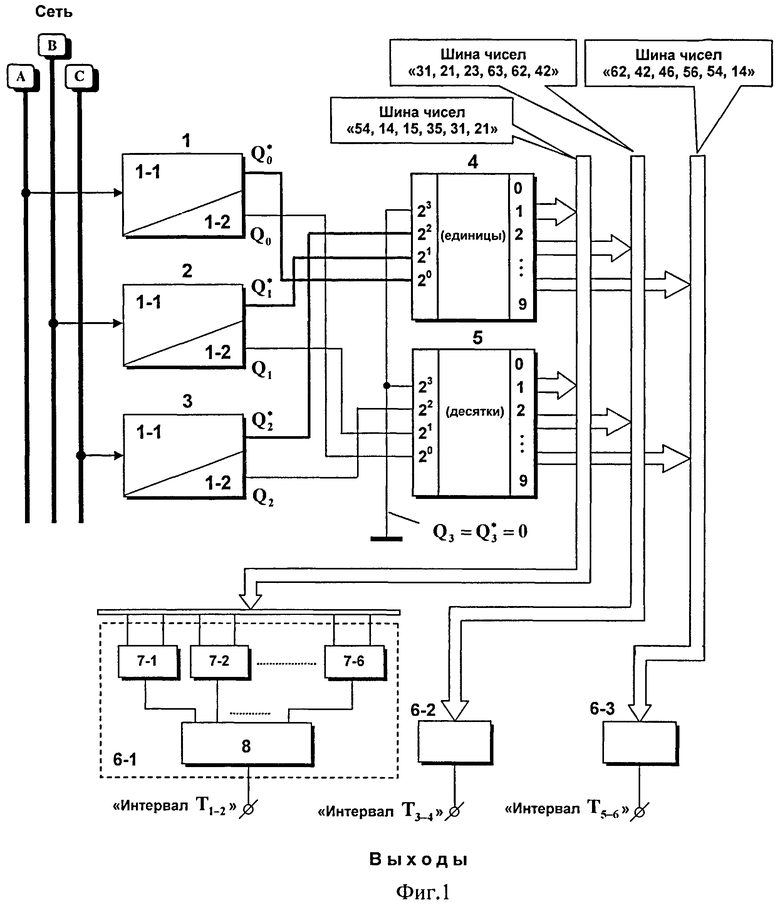

Фиг.12 - блок-схема методики синтеза интервало-кодовых устройств синхронизации.

В состав устройства синхронизации (фиг.1) входят первый 1, второй 2 и третий 3 блоки синхронизации, каждый из которых состоит из первого 1-1 и второго 1-2 развертывающих преобразователей, а также входят первый 4 и второй 5 двоично-десятичные дешифраторы, первый 6-1, второй 6-2 и третий 6-3 логические блоки, каждый из которых содержит шесть элементов 7-1, 7-2, … 7-6 функции «2И» и один элемент 8 функции «6ИЛИ», входы которого подключены к выходам элементов 7-1, 7-2, … 7-6 функции «2И», а выход элемента 8 функции «6ИЛИ» является одним из «выходов» каскадного интервало-кодового двоично-десятичного устройства синхронизации. При этом вход первого 1, второго 2 и третьего 3 блоков синхронизации соединен с шиной фаз А, В, С напряжения сети соответственно, первый выход каждого из блоков синхронизации 1, 2, 3 подключен к входам первого двоично-десятичного дешифратора 4 с весом 20, 21 и 22 соответственно, второй выход каждого из блоков синхронизации 1, 2, 3 подключен к входам второго двоично-десятичного дешифратора 5 с весом 20, 21 и 22 соответственно, вход первого 4 и второго 5 двоично-десятичного дешифратора, имеющий вес 23, подключен к шине нулевого потенциала, входы элементов 7-1, 7-2, … 7-6 функции «2И» первого 6-1, второго 6-2 и третьего 6-3 логических блоков соединены с соответствующими выходными шинами первого 4 и второго 5 двоично-десятичных дешифраторов.

Каждый из развертывающих преобразователей 1-1 и 1-2 (фиг.2) соответственно состоит из последовательно соединенных первого 9 и второго 10 пропорциональных четырехполюсников, первого 11 и второго 12 сумматоров, первого 13 и второго 14 интеграторов, первого 15 и второго 16 релейных элементов, первого 17 и второго 18 инвертирующих ключей, выходы которых являются первыми и вторыми выходами блоков синхронизации 1, 2, 3 (фиг.1). При этом выходы первого 15 и второго 16 релейных элементов соответственно соединены с входами третьего 19 и четвертого 20 пропорциональных четырехполюсников, выходы которых подключены ко вторым входам первого 11 и второго 12 сумматоров. Одновременно выход первого релейного элемента 15 соединен с входом второго пропорционального четырехполюсника 10, а вход первого пропорционального четырехполюсника 9 является «входом» одного из блоков синхронизации 1, 2, 3 (фиг.1).

Звенья устройства синхронизации имеют следующие характеристики.

Двоично-десятичные дешифраторы 4, 5 преобразуют входной двоичный код в десятичное число. Вес входных разрядов и вес выходных разрядов обозначены десятичными числами «внутри» условно-графического изображения дешифраторов.

Элементы 7-1, 7-2, … 7-6 функции «2И» переключаются в состояние логической «1», если все входные переменные равны логической «1».

Элемент 8 функции «6ИЛИ» переключается в состояние логической «1», если хотя бы одна из шести входных переменных равна логической «1».

В каждом из РП 1-1, 1-2 (фиг.2) сумматоры 11, 12 имеют единичный коэффициент передачи по каждому из входов. Интеграторы 13, 14 имеют передаточную функцию W(p)=1/Tp, где Т - постоянная времени интегрирования. При дискретном изменении входного воздействия выходной сигнал интеграторов 13, 14 изменяется по линейному закону со знаком, обратным по отношению к знаку сигнала на его входе. Релейные элементы 15, 16 имеют симметричную относительно «нуля» петлю гистерезиса. Его выходной сигнал меняется дискретно в пределах ±А. Инвертирующие ключи 17, 18 преобразуют биполярные выходные импульсы релейных элементов 15, 16 в однополярные для последующего согласования РП с цифровыми элементами. Инвертирующие ключи 17, 18 имеют нулевое значение порогов включения/выключения и инвертирующую характеристику «вход-выход».

На фиг.1-11 введены следующие обозначения:

KВХ и KОС - коэффициенты пропорционального усиления четырехполюсников 9, 10, 19, 20;

YИ1, YИ2 - выходные сигналы интеграторов 13 и 14 соответственно;

YР1, YР2 - выходные сигналы релейных элементов 15 и 16 соответственно, имеющих амплитуду выходных импульсов ±А;

, Qi - выходные сигналы инвертирующих ключей 17, 18, соответствующие разрядам младшей (единицы) и старшей (десятки) тетрад двоично-десятичного кода 8-4-2-1 соответственно;

, Qi - выходные сигналы инвертирующих ключей 17, 18, соответствующие разрядам младшей (единицы) и старшей (десятки) тетрад двоично-десятичного кода 8-4-2-1 соответственно;

А, В, С - напряжение сети фаз А, В, С соответственно;

XC - сигнал синхронизации одной из фаз А, В, С напряжения сети;

TC - период гармонического сигнала синхронизации;

AC - амплитуда сигнала синхронизации;

TA, TB, TC - периоды напряжения фаз А, В, С соответственно;

Т1-2, Т3-4, Т5-6 - интервалы синхронизации для реверсивного ВП;

T1, Т2, Т3 - интервалы синхронизации для нереверсивного трехфазного «нулевого» ВП с активной нагрузкой.

Принцип работы устройства следующий.

Развертывающие преобразователи 1-1 и 1-2 (фиг.2) блоков синхронизации 1, 2, 3 (фиг.1) представляют собой автоколебательные звенья, которые работают в режиме внешней синхронизации с частотой сигнала, подаваемого на их информационный вход.

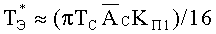

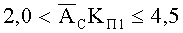

Первый РП 1-1 (фиг.2) имеет передаточную функцию апериодического звена первого порядка с эквивалентной постоянной времени  и полностью адаптирован к изменениям частоты (TC)-1 и амплитуды AC синхронизирующего гармонического воздействия (Цытович Л.И. Реверсивный тиристорный преобразователь для систем управления с питанием от сети с нестационарными параметрами / Л.И.Цытович, P.M.Рахматулин, М.М.Дудкин, А.В.Качалов // Практическая силовая электроника. - 2009. - №2 (34). - С.35-41). При этом «глубина» синхронизации РП 1-1 выбирается в диапазоне

и полностью адаптирован к изменениям частоты (TC)-1 и амплитуды AC синхронизирующего гармонического воздействия (Цытович Л.И. Реверсивный тиристорный преобразователь для систем управления с питанием от сети с нестационарными параметрами / Л.И.Цытович, P.M.Рахматулин, М.М.Дудкин, А.В.Качалов // Практическая силовая электроника. - 2009. - №2 (34). - С.35-41). При этом «глубина» синхронизации РП 1-1 выбирается в диапазоне  , где

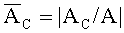

, где  - нормированное значение амплитуды AC сигнала синхронизации; ±А - амплитуда выходных импульсов релейных элементов 15, 16.

- нормированное значение амплитуды AC сигнала синхронизации; ±А - амплитуда выходных импульсов релейных элементов 15, 16.

Второй РП 1-2 (фиг.2) обладает частичной адаптацией, так как его эквивалентная постоянная времени ТЭ≈(πTCKП2)/16 зависит только от частоты напряжения сети, подаваемого на вход одного из блоков синхронизации 1, 2, 3 (фиг.1). Коэффициенты усиления KП1, KП2 развертывающих преобразователей 1-1 и 1-2 (фиг.2) определяются соотношением параметров KВХ и KОС звеньев 9, 10 и 19, 20 на входе и в цепи обратной связи РП.

Учитывая, что амплитуды выходных импульсов релейных элементов 15, 16 равны между собой, для перевода РП 1-2 в режим внешней синхронизации прямоугольными выходными импульсами РП 1-1 необходимо выполнение условия КП2>1,0.

Выходные инверторы 17, 18 (фиг.2) служат для преобразования биполярных выходных импульсов YР1, YР2 релейных элементов 15, 16 (фиг.3б, г) в однополярный сигнал  , Qi (фиг.3в, д) для последующего согласования выходов блоков 17, 18 со схемами цифровой обработки данных. Каждый из развертывающих преобразователей 1-1 и 1-2 обеспечивают фазовый сдвиг выходных импульсов YP1, YP2 по отношению к сигналу синхронизации XC на -90 эл. град (фиг.3а, б, г). Результирующий фазовый сдвиг между сигналом синхронизации XC на входе одного из блоков синхронизации 1, 2, 3 и сигналом на выходе Qi равен -180 эл. град (фиг.3а, д).

, Qi (фиг.3в, д) для последующего согласования выходов блоков 17, 18 со схемами цифровой обработки данных. Каждый из развертывающих преобразователей 1-1 и 1-2 обеспечивают фазовый сдвиг выходных импульсов YP1, YP2 по отношению к сигналу синхронизации XC на -90 эл. град (фиг.3а, б, г). Результирующий фазовый сдвиг между сигналом синхронизации XC на входе одного из блоков синхронизации 1, 2, 3 и сигналом на выходе Qi равен -180 эл. град (фиг.3а, д).

Для последующего рассмотрения принципа действия каскадного интервало-кодового двоично-десятичного УС считаем, что выходные импульсы развертывающего преобразователя 1-2 (фиг.2, 3д) блоков синхронизации 1, 2, 3 (фиг.1) формируют значения Qi (логический «0» или «1») соответствующего разряда старшей тетрады (десятки) двоично-десятичного кода 8-4-2-1, а сигнал на выходе РП 1-1 (фиг.2, 3в) блоков синхронизации 1, 2, 3 представляет собой соответствующий разряд  младшей (единицы) тетрады кода 8-4-2-1.

младшей (единицы) тетрады кода 8-4-2-1.

Рассмотрим работу УС на примере построения каналов синхронизации реверсивного тиристорного преобразователя с раздельным управлением (фиг.4).

В этом случае система содержит три идентичных канала синхронизации 1, 2, 3, подключенные к фазам А, В, С напряжения сети (фиг.1). Каждый из блоков синхронизации 1, 2, 3 выполнен по схеме на фиг.2 и имеет по два выхода  (выход 1) и Qi (выход 2). В дальнейшем считаем, что блок синхронизации 1 формирует данные с весом 20 для младшего разряда Q0 и

(выход 1) и Qi (выход 2). В дальнейшем считаем, что блок синхронизации 1 формирует данные с весом 20 для младшего разряда Q0 и  соответственно первой и второй тетрад кода 8-4-2-1, а блок синхронизации 3 - для третьего разряда Q2,

соответственно первой и второй тетрад кода 8-4-2-1, а блок синхронизации 3 - для третьего разряда Q2,  этих же тетрад с весовым коэффициентом 22. Значение четвертого разряда кода 8-4-2-1 принимаем постоянным и равным

этих же тетрад с весовым коэффициентом 22. Значение четвертого разряда кода 8-4-2-1 принимаем постоянным и равным  (фиг.1).

(фиг.1).

Сигналы Qi со вторых выходов блоков синхронизации 1, 2, 3 (фиг.4б-г), образующие «старшую» тетраду кода 8-4-2-1, имеют уровень логической «1» в течение времени формирования «положительных» полуволн напряжений фаз А, В, С (фиг.4а). Выходные импульсы  «младшей» тетрады (фиг.4д-ж) сдвинуты относительно сигналов Qi (фиг.4б-г) на -90 эл. град.

«младшей» тетрады (фиг.4д-ж) сдвинуты относительно сигналов Qi (фиг.4б-г) на -90 эл. град.

В результате каждый участок трехфазной системы напряжений фаз А, В, С продолжительностью в 30 эл. град характеризуется своей кодовой комбинацией, десятичное значение которой показано на фиг.4з.

При этом, например, для интервалов синхронизации Т1-2, Т3-4, Т5-6 реверсивного преобразователя постоянного тока между точками естественной коммутации «1-2», «3-4» и «5-6» (фиг.4а) присутствуют вполне определенные кодовые комбинации (фиг.5), которые декодируются двоично-десятичными дешифраторами 4 и 5, и затем объединяются с помощью логических блоков 6-1, 6-2, 6-3 (фиг.1), формируя сигнал синхронизации соответствующих каналов системы импульсно-фазового управления. Каждый из блоков 6-1, 6-2, 6-3 содержит шесть элементов 7-1, 7-2, 7-3, 7-4, 7-5, 7-6 функции «2И» и один логический элемент 8 функции «6ИЛИ». Один из входов блоков 6-1, 6-2, 6-3 подключается к двоично-десятичному дешифратору 4, второй вход - к двоично-десятичному дешифратору 5. Например, считаем, что блок 7-1 (фиг.1) выделяет число «54» путем формирования на своем выходе сигнала логической «1». Для этого первый вход блока 7-1 подключается к выходной шине числа «4» двоично-десятичного дешифратора 4, а второй вход соединяется с выходной шиной числа «5» двоично-десятичного дешифратора 5. В результате при появлении числа «54» блок 7-1 переключается в состояние логической «1», которая передается через блок 8 функции «6ИЛИ» на один из выходов УС.

Обладая высокой степенью помехоустойчивости, обусловленной последовательным включением интегрирующих РП 1-1 и 1-2 (фиг.2), данный интервало-кодовый принцип синхронизации характеризуется также широкими функциональными возможностями.

Так, например, для вентильного преобразователя с трехфазной «нулевой» схемой силовых ключей достаточно для каждого из требуемых интервалов синхронизации (фиг.4а, интервалы Т1, T2, Т3) выделить пять кодовых комбинаций, показанных на фиг.5. При работе с однофазным преобразователем могут использоваться сигналы Q, (фиг.4б-г) либо соответствующая последовательность из шести чисел (фиг.4а, з).

Это позволяет использовать данный класс устройств синхронизации также в качестве магистрального, когда объект, например взаимосвязанные технологической последовательностью электроприводы, работающие с различными по конфигурации силового блока ВП, синхронизируются от единого устройства синхронизации.

Кроме способности формировать сигнал синхронизации для различных схем ВП, интервало-кодовые УС обладают также возможностью производить с их помощью ряд операций диагностирования ВП.

На фиг.6, 7, 8 приведены диаграммы сигналов каскадного интервало-кодового двоично-десятичного УС для различных случаев неправильного чередования фаз А, В, С напряжения сети.

Первое, что обращает на себя внимание, так это то, что полностью меняются значения числовых последовательностей (фиг.6-9) по сравнению с первоначальной для последовательности «А-В-С» (фиг.4з).

Во-вторых, «внутри» каждого из случаев «В-А-С», «А-С-В» и «С-В-А» (фиг.6-8) существует один и тот же массив чисел, отличающийся друг от друга лишь последовательностью их расположения.

Таким образом, с помощью интервало-кодового УС обеспечивается не только синхронизация каналов управления ВП, но и абсолютная достоверность процесса определения (диагностики) правильности чередования фаз напряжения сети, подключаемого к системе импульсно-фазового управления. Для этого можно использовать как весь набор из 12 чисел (фиг.9), так и одно число, например «36» (фиг.9).

Способность каскадного интервало-кодового двоично-десятичного УС определять чередование фаз напряжения сети в принципе позволяет по получаемому массиву чисел производить автоматическое демультиплексирование его выходов, когда независимо от порядка подключения системы импульсно-фазового управления к сети каждый из ее каналов будет синхронизирован с требуемой фазой сетевого напряжения.

Интервало-кодовый принцип синхронизации позволяет также производить защиту ВП от перехода какого-либо канала синхронизации в результате своей неисправности в статическое состояние (логический «0» или «1»), а также в случае срыва режима внешней синхронизации в блоках синхронизации 1, 2, 3 и их перехода в состояние автоколебаний.

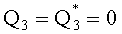

Рассмотрим сказанное на примере диаграмм сигналов (фиг.10) для случая выхода из строя РП 1-1 (фиг.2) блока синхронизации 1 (фиг.1) фазы А, когда, например, в результате катастрофического отказа его релейного элемента 15 в момент времени t0 РП 1-1 переходит в неуправляемое состояние - А, что вызывает появление статического состояния  (фиг.10д). Так как РП 1-2 имеет всегда коэффициент передачи больше единицы, то появление на его входе статического сигнала - А приведет к срыву режима синхронизации и принудительно переведет его в статическое положение + А, когда

(фиг.10д). Так как РП 1-2 имеет всегда коэффициент передачи больше единицы, то появление на его входе статического сигнала - А приведет к срыву режима синхронизации и принудительно переведет его в статическое положение + А, когда  (фиг.10б).

(фиг.10б).

Тогда при исправном состоянии блоков синхронизации 2, 3 (фиг.10в, г, е, ж) на выходе двоично-десятичных дешифраторов 4, 5 будет формироваться последовательность десятичных чисел (фиг.10з, фиг.11), которая отличается от той, которая имеет место в устройстве синхронизации при работоспособности всех его звеньев (фиг.11). Так, например, для интервала синхронизации Т1-2 отличие будет в пяти случаях из шести. В то же время для интервала Т3-4 массив чисел отличается только в одном случае, а именно числом «43». Что касается интервала синхронизации Т3-4, то здесь вся комбинация отлична от той, которая присутствует при исправном состоянии всех каналов устройства синхронизации (фиг.11).

Очевидно, что другие возможные варианты неисправности элементов устройства приведут к новым кодовым последовательностям, отличающимся от базовой на фиг.5.

В общем случае методика синтеза интервало-кодового УС сводится к следующему (фиг.12). Любая система напряжений от однофазной до многофазной имеет характерные точки с периодом повторения, кратным ее частоте. Для однофазных сетей такими точками являются точки перехода синусоидальным напряжением через нулевой уровень. В n-фазных сетях к этим точкам добавляются точки естественной коммутации, например, в трехфазных сетях следующих друг за другом с интервалом 60 эл. град. В результате каждому характерному для данной системы напряжений интервалу времени можно присвоить свое значение, например, в двоичной или двоично-десятичной системах счисления. Для этого необходимо создать дополнительную систему логических сигналов, сдвинутых относительно друг друга таким образом, чтобы каждый из характерных интервалов времени Δt (фиг.12) имел бы свою только для него характерную кодовую комбинацию, которая затем преобразуется в десятичное число с помощью элементов декодирования (дешифраторов). После этого с помощью логической функции «ИЛИ» суммируются те значения десятичного числа, которые характеризуют заданный интервал синхронизации системы управления ВП.

Промышленная применимость

Рассмотренное устройство будет использоваться в системе управления вентильными преобразователями испытательного стенда электротехнических изделий в электроцехе ОАО «Челябинский трубопрокатный завод».

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2011 |

|

RU2461948C1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2011 |

|

RU2449456C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2552147C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2496228C1 |

| ФИЛЬТР С ДИСКРЕТНО ПЕРЕСТРАИВАЕМЫМИ ХАРАКТЕРИСТИКАМИ | 2006 |

|

RU2317636C1 |

| ТРЕХФАЗНЫЙ РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ С ЗАЩИТОЙ | 2012 |

|

RU2499347C1 |

| МНОГОЗОННЫЙ РАЗВЕРТЫВАЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ПЕРЕДАЧИ ЛОГИЧЕСКИХ ДАННЫХ ПО ОДНОПРОВОДНОЙ ЛИНИИ СВЯЗИ | 2001 |

|

RU2206922C2 |

| СПОСОБ ИНТЕГРИРУЮЩЕГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2014 |

|

RU2571549C1 |

| МНОГОЗОННЫЙ ИНТЕГРИРУЮЩИЙ РЕГУЛЯТОР | 2014 |

|

RU2546084C1 |

| АДАПТИВНОЕ ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2013 |

|

RU2531530C1 |

Изобретение относится к области силовой электроники. Технический результат заключается в повышении точности работы и расширении функциональных возможностей устройства. Для этого устройство синхронизации представляет собой интегрирующую развертывающую систему, где выделение требуемой длительности импульса синхронизации для силового вентильного преобразователя осуществляется на основе интервало-кодового алгоритма обработки данных. Заявленное устройство содержит (фиг.1) первый 1, второй 2 и третий 3 блоки синхронизации, каждый из которых состоит из первого 1-1 и второго 1-2 развертывающих преобразователей, первый 4 и второй 5 двоично-десятичные дешифраторы, первый 6-1, второй 6-2 и третий 6-3 логические блоки, каждый из которых содержит шесть элементов 7-1, 7-2, … 7-6 функции «2И» и один элемент 8 функции «6ИЛИ». Каждый из развертывающих преобразователей 1-1 и 1-2 (фиг.2) состоит соответственно из первого 9 и второго 10 пропорциональных четырехполюсников, первого 11 и второго 12 сумматоров, первого 13 и второго 14 интеграторов, первого 15 и второго 16 релейных элементов, первого 17 и второго 18 инвертирующих ключей, третьего 19 и четвертого 20 пропорциональных четырехполюсников. Введение в устройство синхронизации второго 2 и третьего 3 блоков синхронизации, первого 4 и второго 5 двоично-десятичных дешифраторов и трех логических блоков 6-1, 6-2, 6-3 позволяет выделить требуемую длительность импульса синхронизации на основе интервало-кодового алгоритма обработки данных с выходов блоков синхронизации. 12 ил.

Устройство синхронизации, содержащее первый блок синхронизации, в состав которого входят первый сумматор, первый интегратор, первый релейный элемент, второй сумматор, второй интегратор и второй релейный элемент, причем вход первого блока синхронизации соединен с шиной фазы А напряжения сети, отличающееся тем, что в него введены второй и третий блоки синхронизации, первый и второй двоично-десятичные дешифраторы и три логических блока, каждый из которых содержит шесть элементов функции «2И» и один элемент «6ИЛИ», входы последнего подключены к выходам элементов «2И», а выход элемента «6ИЛИ» является одним из «выходов» устройства синхронизации, при этом входы второго и третьего блока синхронизации соединены с шинами фаз В и С соответственно, первый выход каждого из блоков синхронизации подключен к входам первого двоично-десятичного дешифратора с весом 20, 21 и 22 соответственно, второй выход каждого из блоков синхронизации подключен к входам второго двоично-десятичного дешифратора с весом 20, 21 и 22 соответственно, вход первого и второго двоично-десятичного дешифратора, имеющий вес 23, подключен к шине нулевого потенциала, входы элементов «2И» первого, второго и третьего логических блоков соединены с соответствующими выходными шинами первого и второго двоично-десятичных дешифраторов, при этом каждый из блоков синхронизации содержит последовательно включенные первый пропорциональный четырехполюсник, первый сумматор, первый интегратор, первый релейный элемент, второй пропорциональный четырехполюсник, второй сумматор, второй интегратор, второй релейный элемент, причем выход первого релейного элемента через третий пропорциональный четырехполюсник подключен ко второму входу первого сумматора и через первый инвертирующий ключ соединен с первым выходом блока синхронизации, а выход второго релейного элемента через четвертый пропорциональный четырехполюсник подключен ко второму входу второго сумматора и через второй инвертирующий ключ соединен со вторым выходом блока синхронизации, вход первого пропорционального четырехполюсника является «входом» блока синхронизации.

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2008 |

|

RU2383985C1 |

| СИСТЕМА ИМПУЛЬСНО-ФАЗОВОГО УПРАВЛЕНИЯ | 2003 |

|

RU2248659C2 |

| Система импульсно-фазового управления трехфазным тиристорным преобразователем | 1990 |

|

SU1798869A1 |

| Устройство для импульсно-фазового управления вентильным преобразователем | 1978 |

|

SU873374A1 |

| Устройство для синхронизации с напряжением сети | 1981 |

|

SU970590A1 |

Авторы

Даты

2012-10-27—Публикация

2011-10-12—Подача