Область техники, к которой относится изобретение

[1] Аспекты настоящего изобретения относятся к автоматическому запросу на повторение (ARQ) в беспроводной системе связи. Более конкретно, аспекты настоящего изобретения относятся к способу и устройству для продвинутого управления буфером ARQ в беспроводной системе связи.

Предшествующий уровень техники

[2] В соответствии с состоянием канала радиоресурса, беспроводная система связи может сталкиваться с ошибкой в передаваемых и принимаемых данных. В связи с этим данная беспроводная система связи может осуществлять управление или исправлять ошибку в данных с использованием схемы автоматического запроса на повторение (ARQ) с целью повышения надежности передачи.

[3] При использовании схемы ARQ приемник ARQ информирует передатчик ARQ о том, является ли блок данных ARQ (далее в настоящем документе рассматриваемый как блок ARQ) успешно принятым от передатчика ARQ. Например, когда блок ARQ, принятый от передатчика ARQ, не содержит ошибки, приемник ARQ передает подтверждение (ACK) на передатчик ARQ. Когда блок ARQ, принятый от передатчика ARQ, является поврежденным, приемник ARQ передает отрицательное подтверждение ACK (NACK) на передатчик ARQ. В настоящем документе последовательность операций приемника ARQ для передачи успеха или неуспеха приема блока ARQ на передатчик ARQ рассматривается как обратная передача ARQ.

[4] В соответствии с этим передатчик ARQ может получать состояние приема блока ARQ, переданного на приемник ARQ, на основе ACK/NACK, принятого от приемника ARQ. При приеме ACK от приемника ARQ передатчик ARQ передает на приемник ARQ новый блок ARQ. В противоположность этому при приеме информации NACK от приемника ARQ передатчик ARQ повторно передает на приемник ARQ блок ARQ, соответствующий NACK.

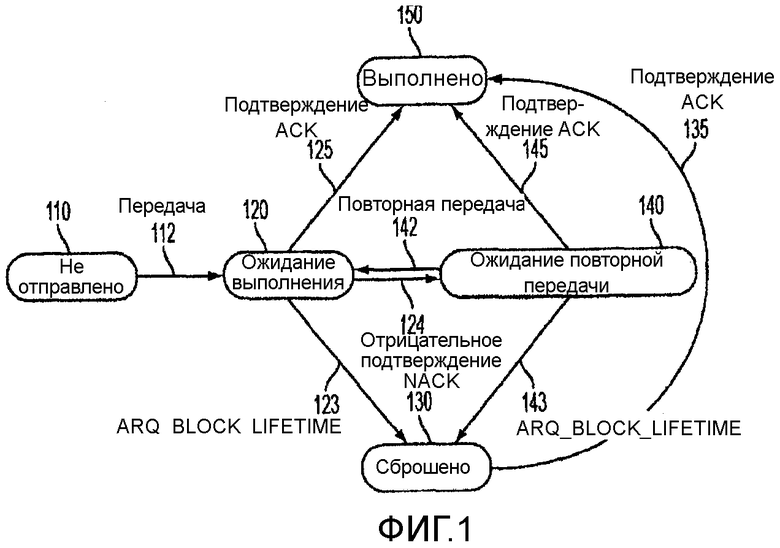

[5] Схема ARQ может осуществляться различным образом для различных стандартов беспроводной связи. Ниже со ссылкой на фиг.1 описывается пример схемы передачи ARQ, используемой в стандартах Института инженеров по электротехнике и электронике (IEEE) 802.16e и IEEE 802.16m.

[6] Фиг.1 иллюстрирует машину состояний передатчика ARQ для блока ARQ в соответствии с предшествующим уровнем техники.

[7] Касательно фиг.1 связь блока ARQ может находиться в одном из пяти состояний, а именно в состоянии 110 «Не отправлено», в состоянии 120 «Ожидание выполнения», в состоянии 130 «Сброшено», в состоянии 140 «Ожидание повторной передачи» и в состоянии 150 «Выполнено». Каждое задействованное соединение ARQ имеет независимую машину состояний ARQ. Минимальным блоком перехода состояний ARQ является блок ARQ. Блок ARQ начинается в состоянии 110 «Не отправлено» до того, как данный блок ARQ изначально передается.

[8] Когда блок ARQ передается, для блока ARQ инициируется таймер ARQ_BLOCK_LIFETIME (ВРЕМЕНИ_ЖИЗНИ_БЛОКА_ARQ), и состояние блока ARQ переходит от состояния 110 «Не отправлено» к состоянию 120 «Ожидание выполнения» на этапе 112. Когда это происходит, параметр ARQ_TX_NEXT_SN (СЛЕДУЮЩЕГО_SN_ПЕРЕДАЧИ_ARQ) приращивается на единицу.

[9] В то время как блок ARQ находится в состоянии 120 «Ожидание выполнения», передатчик ARQ ожидает одно из: подтверждения ACK и отрицательного подтверждения NACK от соответствующего приемника ARQ. Если приходит ACK, состояние блока ARQ переходит к состоянию 150 «Выполнено» на этапе 125. Если приходит NACK, состояние блока ARQ переходит к состоянию 140 «Ожидание повторной передачи» на этапе 124. После того как период ARQ_BLOCK_LIFETIME истекает, состояние блока ARQ переходит к состоянию 130 «Сброшено» на этапе 123.

[10] В то время как блок ARQ находится в состоянии 140 «Ожидание повторной передачи», передатчик ARQ подготавливается для повторной передачи данных ARQ, соответствующих блоку ARQ. Если приходит ACK, состояние блока ARQ переходит к состоянию 150 «Выполнено» на этапе 145. Если данные ARQ, соответствующие блоку ARQ, передаются повторно, состояние блока ARQ переходит обратно к состоянию 120 «Ожидание выполнения» на этапе 142. После того как таймер ARQ_BLOCK_LIFETIME истекает, состояние блока ARQ переходит к состоянию 130 «Сброшено» на этапе 143 без осуществления повторной передачи.

[11] В то время как блок ARQ находится в состоянии 130 «Сброшено», передатчик ARQ отправляет сообщение сброса и ожидает ACK от приемника ARQ. Если приходит ACK для сообщения сброса или блок ARQ, состояние блока ARQ переходит к состоянию 150 «Выполнено» на этапе l35.

[12] Когда блок ARQ находится в состоянии 150 «Выполнено», передатчик ARQ завершает работу ARQ посредством стирания всех таймеров и переменных состояний ARQ, относящихся к блоку ARQ.

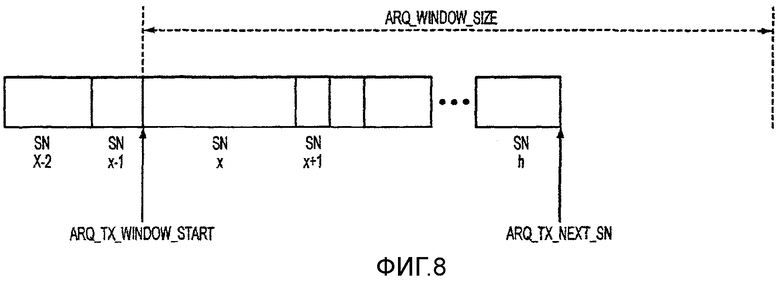

[13] Каждый передатчик ARQ поддерживает окно передачи ARQ с помощью двух параметров, а именно параметра ARQ_TX_WINDOW_START (НАЧАЛА_ОКНА_ПЕРЕДАЧИ_ARQ) и параметра ARQ_TX_NEXT_SN. Машина состояний ARQ рассматривает все блоки ARQ вплоть до ARQ_TX_WINDOW_START - 1 как подтверждающиеся соответствующим приемником ARQ. Параметр ARQ_TX_WINDOW_START представляет нижнюю границу окна ARQ в передатчике ARQ. Когда соответствующий блок ARQ параметра ARQ_TX_WINDOW_START в машине состояний ARQ переходит к состоянию 150 «Выполнено», параметр ARQ_TX_WINDOW_START перемещается к следующему наиболее низкому порядковому номеру (SN) ARQ, не подтвержденному приемником ARQ. Параметр ARQ_TX_NEXT_SN соответствует наиболее низкому SN, представляющему собой следующий блок ARQ, назначенный к отправке посредством передатчика ARQ. Параметр ARQ_TX_NEXT_SN будет находиться в пределах интервала от ARQ_TX_WINDOW_START до ARQ_TX_WINDOW_START + ARQ_WINDOW_SIZE (РАЗМЕР_ОКНА_ARQ).

[14] Каждый приемник ARQ поддерживает окно приема ARQ с помощью двух параметров, а именно параметра ARQ_RX_WINDOW_START (НАЧАЛА_ОКНА_ПРИЕМА_ARQ) и параметра ARQ_RX_HIGHEST_SN (НАИБОЛЕЕ_ВЫСОКОГО_SN_ПРИЕМА_ARQ). Машина состояний ARQ рассматривает все блоки ARQ вплоть до ARQ_RX_WINDOW_START - 1 как принимающиеся. Параметр ARQ_RX_WINDOW_START представляет нижнюю границу окна ARQ в приемнике ARQ. Когда соответствующий блок ARQ_RX_WINDOW_START принимается правильно или после истечения таймера ARQ_RX_PURGE_TIMEOUT (ВРЕМЕНИ_ОЖИДАНИЯ_СБРОСА_ПРИЕМА_ARQ), ARQ_RX_WINDOW_START перемещается к следующему наиболее низкому SN ARQ, не являющемуся принятым.

[15] Параметр ARQ_RX_HIGHEST_SN соответствует наиболее высокому SN ARQ принятого блока ARQ, плюс один. Параметр ARQ_RX_HIGHEST_SN будет находиться в пределах интервала от ARQ_RX_WINDOW_START до ARQ_RX_WINDOW_START + ARQ_WINDOW_SIZE.

[16] Ниже со ссылкой на фиг.2 описывается пример схемы приема ARQ, используемой в стандартах IEEE 802.16e и IEEE 802.16m.

[17] Фиг.2 иллюстрирует блок-схему последовательности операций для приема блока ARQ в соответствии с предшествующим уровнем техники.

[18] Касательно фиг.2, когда на этапе 202 принимают блок пакетных данных (PDU) управления доступом к среде (MAC), приемник ARQ проверяет расширенный заголовок фрагментации и упаковывания (FPEH) и получает информацию блока ARQ для приема ARQ. После того как приемник ARQ знает SN ARQ и соответствующий блок ARQ, машина состояний приемника ARQ на этапе 204 добавляет данный SN к списку номеров SN, назначенных к подтверждению. Машина состояний приемника ARQ проверяет допустимость SN посредством определения на этапе 206, попадает ли SN в пределы диапазона окна приемника ARQ (то есть от ARQ_RX_WINDOW_START до ARQ_RX_WINDOW_START + ARQ_WINDOW_SIZE). Если блок ARQ не является допустимым (то есть блок ARQ не находится в пределах диапазона окна приемника ARQ), на этапе 208 приемник сбрасывает блок ARQ.

[19] Если SN ARQ является допустимым (то есть блок ARQ находится в пределах диапазона окна приемника ARQ), на этапе 210 определяют, является ли соответствующий блок ARQ уже принятым. Если определяется, что блок ARQ является уже принятым, машина состояний приемника ARQ на этапе 212 повторно устанавливает таймер ARQ_RX_PURGE_TIMEOUT и на этапе 208 сбрасывает блок ARQ. В данном случае соответствующий блок ARQ сбрасывается, поскольку он является дублирующим блоком, который не должен сохраняться в буфере. Однако если определяется, что блок ARQ не является дублированным, машина состояний приемника ARQ начинает процедуру с целью обновления переменных состояний ARQ и соответствующих таймеров на этапах 214-224 и сохранения блока ARQ в буфере на этапе 226.

[20] Более конкретно, если определяется, что блок ARQ не является дублированным, на этапе 214 определяется, является ли SN большим, чем или равным ARQ_RX_HIGHEST_SN. Если определяется, что SN является меньшим, чем ARQ_RX_HIGHEST_SN, процедура переходит к этапу 218. Однако если определяется, что SN является большим, чем или равным ARQ_RX_HIGHEST_SN, приемник ARQ на этапе 216 обновляет ARQ_RX_HIGHEST_SN как SN+1 и переходит к этапу 218.

[21] На этапе 218 определяется, является ли SN равным ARQ_RX_WINDOW_START. Если определяется, что SN является равным ARQ_RX_WINDOW_START, на этапе 220 ARQ_RX_WINDOW_START продвигается к следующему блоку ARQ с наиболее низким номером, который не был принят, на этапе 222 повторно устанавливается ARQ_SYNC_LOSS_TIMEOUT (ВРЕМЯ_ОЖИДАНИЯ_ПОТЕРИ_СИНХРОНИЗАЦИИ_ARQ), и на этапе 226 блок ARQ сохраняется. Однако если определяется, что SN не является равным ARQ_RX_WINDOW_START, приемник ARQ маркирует блок как принятый и повторно устанавливает таймер ARQ_RX_PURGE_TIMEOUT для этого SN на этапе 224. Блок ARQ затем сохраняется на этапе 226.

[22] Приемник ARQ осуществляет обратную передачу ARQ с использованием элемента информации (IE) обратной передачи ARQ с целью обновления состояния приема блока ARQ, когда от передатчика ARQ принимается опрос обратной передачи ARQ, или когда блок ARQ отсутствует в течение количества времени, соответствующего DELIVERY_IN_ORDER_TIMEROUT (ВРЕМНИ_ОЖИДАНИЯ_УПОРЯДОЧЕННОЙ_ДОСТАВКИ).

[23] Когда передатчик ARQ принимает IE обратной передачи ARQ, не включающий в себя селективную карту ACK, передатчик ARQ рассматривает все блоки ARQ в интервале ARQ_TX_WINDOW_START до SN (включительно) как подтвержденные и устанавливает ARQ_TX_WINDOW_START на SN+1. Когда IE обратной передачи ARQ включает в себя селективную карту ACK, передатчик ARQ рассматривает все блоки ARQ в интервале ARQ_TX_WINDOW_START до SN (не включая) как подтвержденные и устанавливает ARQ_TX_WINDOW_START на SN. Старший бит (MSB) селективной карты ACK обозначает SN в IE обратной передачи ARQ, который будет начинаться с NACK, а смежные биты в селективной карте ACK могут маркироваться как ACK или NACK. Передатчик ARQ рассматривает только допустимые подтверждения ACK в пределах окна ARQ (то есть ARQ_TX_WINDOW_START + ARQ_WINDOW_SIZE). Подтверждения ACK вне окна ARQ передатчиком ARQ игнорируются.

[24] Когда от передатчика ARQ принимается сообщение сброса, приемник ARQ отправляет ACK на передатчик ARQ и сбрасывает соответствующие блоки в сообщении сброса. ARQ_RX_WINDOW_START передвигается к следующему наиболее низкому SN блока ARQ, еще не принятому в пределах окна приема ARQ.

[25] Сервисные блоки данных (SDU) MAC реконструируются из блоков ARQ в последовательности. Когда принимается новый блок ARQ, приемник ARQ проверяет, может ли быть реконструирован полный SDU. Если полный SDU может быть реконструирован, он затем передается на верхний уровень, в противном случае блок ARQ буферизируется, и приемник ARQ ожидает другие блоки ARQ с тем, чтобы осуществить реконструкцию SDU. Когда блок ARQ пропускается, блоки ARQ, относящиеся к реконструкции SDU, очищаются из буфера.

[26] Как IEEE 802.16e, так и IEEE 802.16m при формировании PDU поддерживают упаковывание блоков SDU, а также фрагментацию и повторную сборку. В данном случае стандартом IEEE 802.16e и стандартом IEEE 802.16m поддерживаются как блоки SDU переменной длины, так и блоки SDU фиксированной длины. Более конкретно, стандарт IEEE 802.16e определяет подзаголовок фрагментации (Fragmentation SubHeader, FSH) и подзаголовок упаковывания (Packing SubHeader, PSH) для поддержания блоков SDU переменной длины, примеры форматов которых продемонстрированы ниже в соответственно Таблице 1 и Таблице 2.

[27] Таблица 1

[28] Таблица 2

[29] Касательно Таблицы 1 и Таблицы 2 FSH является по существу таким же самым, как PSH, кроме того, что 11-битовое поле «Length» заменяется 3-битовым полем «Reserved». FSH используется, когда полезная нагрузка в блоке PDU MAC включает в себя только однофрагментный блок SDU. Это происходит постольку, поскольку отсутствует необходимость наличия поля «Length», поскольку основной заголовок MAC уже имеет поле длины. Ниже со ссылкой на фиг.3 описывается пример блоков SDU переменной длины, упакованных в блоки PDU MAC, включающих в себя подзаголовки FSH и подзаголовки PSH на основе стандарта IEEE 802.16e.

[30] FIG. 3 иллюстрирует блоки SDU переменной длины, упакованные в блоки PDU MAC, включающие в себя подзаголовки FSH и подзаголовки PSH в соответствии с предшествующим уровнем техники.

[31] Касательно фиг.3 продемонстрировано r блоков SDU 302 MAC, s-r+1 блоков PDU 304 MAC, а также t блоков SDU 306 MAC. Каждый из s-r+1 блоков PDU 304 MAC имеет только один фрагмент SDU, и, таким образом, каждый SDU начинается одним FSH. В противоположность этому r блоков SDU 302 MAC и t блоков SDU 306 MAC каждый являются включенными в один блок PDU MAC, включающий в себя нефрагментированные блоки SDU и фрагменты SDU, и вследствие этого каждый SDU или фрагмент SDU начинается с PSH.

[32] Приемник ARQ собирает блоки PDU MAC в порядке FSN и использует 2-битовое поле управления фрагментами (FC) для разделения блоков PDU на группы и формирования блоков SDU. Блок SDU может быть сформирован из только одного сегмента данных с FC «00». В противном случае блок SDU формируется, начиная с одного фрагмента с FC «10», с нулевым или большим количеством фрагментов с FC «11», и заканчиваясь одним фрагментом с FC «01».

[33] Ниже со ссылкой на фиг.4 описывается пример упаковывания блоков SDU фиксированной длины в блок PDU MAC на основе стандарта IEEE 802.16e.

[34] FIG. 4 иллюстрирует блоки SDU MAC фиксированной длины, упакованные в один блок PDU MAC в соответствии с предшествующим уровнем техники.

[35] Касательно фиг.4 k блоков SDU MAC фиксированной длины упаковываются в один блок PDU MAC, где один после другого упаковывается целое число блоков SDU. Учитывая длину всего блока PDU MAC, число упакованных блоков SDU является равным длине блока PDU MAC минус заголовок MAC, разделенной на предварительно определенную длину SDU.

[36] Еще одна другая схема ARQ в соответствии с предшествующим уровнем техники обнаруживается в сети наземного радиодоступа (E-UTRAN) усовершенствованной универсальной системы мобильной связи (UMTS) проекта партнерства третьего поколения (3GPP), известной также под названием «Долгосрочное развитие» (LTE). Ниже со ссылкой на фиг.5 описывается пример структуры блока PDU управления радиоканалами (RLC).

[37] FIG. 5 иллюстрирует структуру PDU RLC в соответствии с предшествующим уровнем техники.

[38] Касательно фиг. 5 продемонстрированы блоки SDU переменной длины, из которых формируются блоки PDU переменной длины. Блок PDU LTE (например, блок PDU k RLC) может состоять из нулевого количества или одного из последнего фрагмента предыдущего SDU (n), нулевого или большего количества отдельных SDU (например, n+1 и n+2) и нулевого количества или одного из первого фрагмента следующего SDU (например, n+3). В качестве альтернативы блок PDU (например, блок PDU RLC) может состоять из только одного фрагмента в середине блока SDU (например, n+3).

[39] В данном случае вместо использования одного поля FC для каждого PSH, как это используется стандартами IEEE 802.16e и IEEE 802.16m, протокол RLC, используемый стандартом LTE, использует поле информации формирования кадров (FI). Если все блоки PDU приходят на приемник ARQ успешно, приемник ARQ может организовывать данные блоки PDU в порядке SN и находить начальную и конечную точки каждого SDU посредством проверки полей FI. Поле FI представляет собой 2-битовое поле, обозначающее, является ли блок SDU RLC сегментированным в начале и/или в конце поля данных. Более конкретно, поле FI обозначает, соответствует ли первый байт поля данных первому байту блока SDU RLC и соответствует ли последний байт поля данных последнему байту блока SDU RLC. Интерпретация поля FI приведена ниже в Таблице 3.

[40] Таблица 3

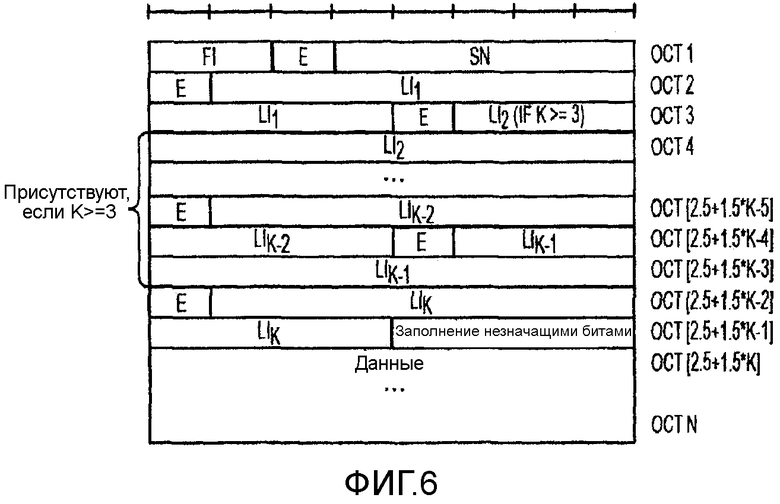

[41] Ниже со ссылкой на фиг.6 описывается пример данных в режиме без подтверждения (UMD).

[42] Фиг.6 иллюстрирует блок PDU UMD в соответствии с предшествующим уровнем техники.

[43] Касательно фиг. 6 продемонстрирован блок PDU UMD с 5-битовым SN. В данном случае блок PDU UMD имеет нечетное число полей индикатора длины (LI) (то есть K=1, 3, 5, и так далее). Поля LI обозначают длину в байтах соответствующего элемента поля данных, присутствующего в блоке PDU данных RLC, доставляемого/принимаемого посредством модуля в режиме без подтверждения (UM) или модуля RLC в режиме с подтверждением (AM). Первый LI, присутствующий в заголовке блока PDU данных RLC, соответствует первому элементу поля данных, присутствующему в поле данных блока PDU данных RLC, второй LI, присутствующий в заголовке блока PDU данных RLC, соответствует второму элементу поля данных, присутствующему в поле данных блока PDU данных RLC, и так далее. Значение 0 для поля LI является зарезервированным.

[44] Поле SN составляет 10 битов для блока PDU данных в режиме с подтверждением (AMD), сегментов блока PDU AMD и блоков PDU состояния и составляет 5 битов или 10 битов (является конфигурируемым) для блока PDU UMD. Поле SN обозначает порядковый номер соответствующего блока PDU UMD или блока PDU AMD. Для сегмента блока PDU AMD поле SN обозначает порядковый номер исходного блока PDU AMD, из которого был сконструирован сегмент блока PDU AMD.

[45] Поле бита расширения (E) представляет собой однобитовое поле. Поле E обозначает, следует ли далее поле данных или далее следует набор из поля E и поля LI.

[46] Операция ARQ, используемая стандартом LTE, известная как режим AM с подтверждением (AM), использует параметры, отличные от тех, которые используются стандартами IEEE 802.16e и IEEE 802.16m. Более конкретно, передатчик ARQ использует окно передачи, имеющее три параметра, а именно VT(A), VT(MS) и VT(S).

[47] VT(A) представляет собой переменную состояния, которая удерживает значение SN следующего блока PDU AMD, для которого последовательно должно быть получено подтверждение ACK, и которая служит в качестве нижней границы окна передачи. VT(A) обновляется каждый раз, когда модуль RLC в режиме AM принимает подтверждение ACK для блока PDU AMD с SN=VT(A).

[48] VT(MS) представляет собой переменную состояния, равную VT(A) + AM_Window_Size (Размер_Окна_AM) и служащую в качестве верхней границы окна передачи.

[49] VT(S) представляет собой переменную состояния, удерживающую значение SN, которое должно быть назначено для следующего вновь сгенерированного блока PDU AMD. VT(S) обновляется каждый раз, когда модуль RLC в режиме AM доставляет блок PDU AMD с SN=VT(S).

[50] Приемник ARQ использует окно приема, имеющее пять параметров, а именно VR(R), VR(MR), VR(H), VR(MS), и VR(X).

[51] VR(R) представляет собой переменную состояния, которая удерживает значение SN, следующее за последним последовательно и полностью принятым блоком PDU AMD, и которая служит в качестве нижней границы окна приема. VR(R) обновляется каждый раз, когда модуль RLC в режиме AM принимает блок PDU AMD с SN=VR(R).

[52] VR(MR) представляет собой переменную состояния, равную VR(R) + AM_Window_Size, удерживающую значение SN первого блока PDU AMD сверх окна приема и служащую в качестве верхней границы окна приема.

[53] VR(H) представляет собой переменную состояния, которая удерживает значение SN, следующее за SN блока PDU данных RLC с наиболее высоким SN среди принятых блоков PDU данных RLC.

[54] VR(MS) представляет собой переменную состояния, удерживающую наиболее высокое возможное значение SN, которое может быть обозначено посредством «ACK_SN», когда необходимо конструирование блока PDU статуса.

[55] VR(X) представляет собой переменную состояния, которая удерживает значение SN, следующее за SN блока PDU данных RLC, инициировавшего T_reordering (Повторное_упорядочение_T).

[56] Резюмируя, стандарты IEEE 802.16e, IEEE 802.16m и LTE предоставляют передатчику ARQ возможность фрагментации пакетов, поступающих из более высокого уровня, с целью формирования блока SDU. Фрагментация обозначается посредством поля «FC» в стандартах IEEE 802.16e и IEEE 802.16m (см. Таблицы 1 и 2), а также поля «FI» в стандарте LTE (см. Таблицу 3). Вследствие этого, когда приемник ARQ принял блок ARQ с SN, равным нижней границе окна приема ARQ (то есть ARQ_RX_WINDOW_START в IEEE 802.16e и IEEE 802.16m, и VR(R) в LTE), приемник ARQ осуществит продвижение окна приема и передачу ACK на передатчик ARQ. Однако это не обязательно означает, что приемник ARQ может удалить этот блок ARQ из буфера приема и доставить его на более высокий уровень, поскольку сначала должен быть сформирован полный блок SDU.

[57] Например, рассмотрим сценарий на фиг.5. Здесь блок PDU k-1 RLC не может быть удален из буфера приема до тех пор, пока также не прибыл блок PDU k RLC, поскольку блок SDU n RLC не может быть реконструирован посредством самого блока PDU k-1 RLC. Аналогичным образом блок PDU k+1 RLC не может быть удален из буфера приема до тех пор, пока также не прибыли оба блока PDU k RLC и PDU k+2 RLC, поскольку блок SDU n+3 RLC не может быть реконструирован посредством самого блока PDU k+1 RLC. Таким образом, блок PDU k+1 RLC будет вынужден ожидать большего количества блоков PDU RLC прежде, чем быть удаленным из буфера приема ARQ и быть доставленным на более высокий уровень, в зависимости от того, как был фрагментирован блок SDU n+3 RLC.

[58] В соответствии с этим при использовании ARQ важным является управление потоком, так чтобы передатчик ARQ не переполнял буфер в приемнике ARQ. Эта проблема представляет особую важность для беспроводных систем связи, где мобильная станция (MS) обычно имеет ограниченный буфер. В данном случае в целях решения проблемы переполнения буфера в приемнике ARQ в уровне техники используется управление буфером. Ниже описывается управление буфером в соответствии с предшествующим уровнем техники.

[59] В целях облегчения управления буфером приемник ARQ информирует передатчик ARQ о максимальном размере буфера ARQ (ARQ_MAX_BUFFER_SIZE) во время согласования функциональных возможностей. ARQ_MAX_BUFFER_SIZE представляет собой максимальный размер буфера ARQ (в байтах), который приемник ARQ способен назначать для всех соединений ARQ. Когда для заданного приемника ARQ в наличии имеются один или более потоков с задействованием ARQ, передатчик ARQ поддерживает состояние ARQ_BUFFER_USED (ИСПОЛЬЗОВАНИЕ_БУФЕРА_ARQ), представляющее собой полное использование буфера ARQ для всех потоков с задействованием ARQ на приемнике ARQ, в добавление к другим состояниям ARQ на поток. ARQ_BUFFER_USED учитывает все блоки ARQ и подблоки, которые еще не были подтверждены по порядку приемником ARQ. Например, если передатчик ARQ отправил блоки 0-10, а приемник ARQ подтверждает блоки 1-10, ARQ_BUFFER_USED будет рассматривать блоки PDU с номерами с 0 по 10 как заполняющие буфер приемника ARQ. Когда блок 0 также подтверждается, ARQ_BUFFER_USED обновляется с целью обозначения того, что блоки с 0 по 10 были очищены из буфера приемника ARQ. Передатчик ARQ обеспечивает, чтобы передача или повторная передача блоков ARQ не превышала ARQ_MAX_BUFFER_SIZE - ARQ_BUFFER_USED.

Раскрытие изобретения

Техническая проблема

[60] Однако один недостаток касательно управления буфером в предшествующем уровне техники состоит в том, что передатчик ARQ может тем не менее переполнять буфер ARQ в приемнике ARQ, поскольку он предполагает, что все блоки ARQ (например, блоки с 0 по 10), которые были совокупно подтверждены приемником ARQ, были доставлены на более высокий уровень и, таким образом, больше не находятся в буфере приема ARQ. Однако это не обязательно является таковым. В действительности, блок ARQ, представляющий собой фрагмент блока SDU MAC, не может быть доставлен на более высокий уровень до тех пор, пока на приемник ARQ не прибыли все фрагменты. Другими словами, блок ARQ может все еще находиться в буфере приема ARQ, даже если он является подтвержденным приемником ARQ и окно приема ARQ передвинулось сверх этого блока ARQ. Таким образом, управление буфером в предшествующем уровне техники не учитывает проблему реконструкции SDU, и, таким образом, передатчик может переполнять буфер ARQ в приемнике ARQ.

Решение проблемы

[61] Вследствие этого существует необходимость в способе и устройстве для продвинутого управления буфером ARQ в беспроводной системе связи.

[62] Одним аспектом настоящего изобретения является решение, по меньшей мере, вышеуказанных проблем и/или недостатков и обеспечение, по меньшей мере, описанных ниже преимуществ. В соответствии с этим одним аспектом настоящего изобретения является обеспечение способа и устройства для продвинутого управления буфером автоматического запроса на повторение (ARQ) в беспроводной системе связи.

[63] В соответствии с одним аспектом настоящего изобретения обеспечивается способ для управления передатчиком ARQ в беспроводной системе связи. Данный способ включает в себя этапы, на которых определяют неиспользованную емкость буфера приемника ARQ в приемнике ARQ, определяют, может ли буфер приемника ARQ поддерживать назначенный к передаче блок ARQ на основе данной определенной неиспользованной емкости буфера приемника ARQ, и, если определено, что буфер приемника ARQ может поддерживать блок ARQ, назначенный к передаче, передают блок ARQ на приемник ARQ.

[64] В соответствии с одним другим аспектом настоящего изобретения обеспечивается устройство передатчика ARQ для использования в беспроводной системе связи. Данное устройство включает в себя приемник для приема сигналов от по меньшей мере одного приемника ARQ, передатчик для передачи сигналов на по меньшей мере один приемник ARQ, и контроллер.

[65] Данный контроллер осуществляет управление приемником и передатчиком, а также определяет неиспользованную емкость буфера приемника ARQ в приемнике ARQ, определяет, может ли буфер приемника ARQ поддерживать блок ARQ, назначенный к передаче, на основе данной определенной неиспользованной емкости буфера приемника ARQ, и, если определено, что буфер приемника ARQ может поддерживать блок ARQ, назначенный к передаче, осуществляет управление с целью передачи блока ARQ на приемник ARQ.

Полезные эффекты изобретения

[66] Представлен способ для точного определения неиспользованной емкости буфера приемника ARQ в приемнике ARQ.

[67] Вследствие этого с помощью более эффективного управления ARQ через посредство определения неиспользованной емкости буфера приемника ARQ в приемнике ARQ может быть предотвращено переполнение буфера ARQ.

[68] Другие аспекты, преимущества, а также отличительные признаки настоящего изобретения станут очевидны для специалистов в данной области техники из нижеследующего описания, которое, будучи взятым в соединении с прилагаемыми чертежами, раскрывает иллюстративные варианты осуществления настоящего изобретения.

Краткое описание чертежей

[69] Вышеуказанные и другие аспекты, признаки и преимущества определенных иллюстративных вариантов осуществления настоящего изобретения будут более очевидны из нижеследующего описания, взятого в соединении с сопроводительными чертежами, на которых:

[70] фиг.1 иллюстрирует машину состояний передатчика автоматического запроса на повторение (ARQ) для блока ARQ в соответствии с предшествующим уровнем техники;

[71] фиг.2 иллюстрирует блок-схему последовательности операций для приема блока ARQ в соответствии с предшествующим уровнем техники;

[72] фиг.3 иллюстрирует сервисные блоки данных (SDU) переменной длины, упакованные в блоки пакетных данных (PDU) управления доступом к среде (MAC), включающие в себя подзаголовки фрагментации (FSH) и подзаголовки упаковывания (PSH) в соответствии с предшествующим уровнем техники;

[73] фиг.4 иллюстрирует блоки SDU фиксированной длины, упакованные в один блок PDU MAC в соответствии с предшествующим уровнем техники;

[74] фиг.5 иллюстрирует структуру блока PDU управления радиоканалами (RLC) в соответствии с предшествующим уровнем техники;

[75] фиг.6 иллюстрирует блок PDU данных в режиме без подтверждения (UMD) в соответствии с предшествующим уровнем техники;

[76] фиг.7 иллюстрирует заполнение буфера и вычисление доступного пространства буфера в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения;

[77] фиг.8 иллюстрирует управление буфером для соединения ARQ в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения;

[78] фиг.9 иллюстрирует блок-схему последовательности операций для определения того, включать ли блок ARQ в ARQ_BUFFER_USED с использованием поля FI, в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения;

[79] фиг.10 иллюстрирует блок-схему последовательности операций для определения того, включать ли блок ARQ в ARQ_BUFFER_USED с использованием поля FC, в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения;

[80] фиг.11 иллюстрирует структурную диаграмму для приемника ARQ в беспроводной системе связи в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения; и

[81] фиг.12 иллюстрирует структурную диаграмму для передатчика ARQ в беспроводной системе связи в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

[82] На всех чертежах схожие опорные обозначения будут пониматься как относящиеся к схожим частям, компонентам и структурам.

Подробное описание вариантов осуществления изобретения

[83] Нижеследующее описание со ссылкой на сопроводительные чертежи обеспечивается с целью содействия в исчерпывающем понимании иллюстративных вариантов осуществления настоящего изобретения, как обозначено посредством формулы изобретения и ее эквивалентов. Оно включает в себя различные конкретные детали с целью содействия в данном понимании, но они должны рассматриваться только в качестве иллюстративных. В соответствии с этим обычные специалисты в данной области техники распознают, что, не выходя за пределы сущности и объема настоящего изобретения, могут быть сделаны различные изменения и модификации вариантов осуществления, описанных в настоящем документе. В дополнение к этому, описания хорошо известных функций и конструкций опускаются для ясности и краткости.

[84] Термины и слова, используемые в нижеследующем описании и формуле изобретения, не ограничиваются до библиографических значений, но используются изобретателем только с целью обеспечения ясного и стройного понимания настоящего изобретения. В соответствии с этим для специалиста в данной области техники должно быть очевидным, что нижеследующее описание иллюстративных вариантов осуществления настоящего изобретения обеспечивается лишь в целях иллюстрации, а не в целях ограничения изобретения, как определено посредством прилагаемой формулы изобретения и ее эквивалентов.

[85] Необходимо понимать, что значение форм единственного числа включает в себя и множественное число определяемых объектов, если только контекст ясно не указывает на обратное. Таким образом, например, ссылка на «поверхность компонента» включает в себя ссылку на одну или более таких поверхностей.

[86] Посредством термина «по существу» обозначается, что перечисляемая характеристика, параметр или значение не обязательно должны быть точно получены, но что в объемах, не препятствующих эффекту, который была назначена обеспечить данная характеристика, могут иметь место отклонения или вариации, включающие в себя, например, допуски, ошибку измерения, ограничения в точности измерения и другие факторы, известные специалистам в области техники.

[87] Иллюстративные варианты осуществления настоящего изобретения, описанные ниже, относятся к способу и устройству для автоматического запроса на повторение (ARQ) в беспроводной системе связи. Более конкретно, иллюстративные варианты осуществления настоящего изобретения, описанные ниже, относятся к способу и устройству для продвинутого управления буфером ARQ в беспроводной системе связи.

[88] Следует понимать, что, только для простоты объяснения, нижеследующее описание может относиться к терминам, используемым в различных стандартах. Например, нижеследующее описание может относиться к терминам, используемым в стандарте 802.16e Института инженеров по электротехнике и электронике (IEEE), в стандарте IEEE 802.16m или в стандарте долгосрочного развития (LTE) проекта партнерства третьего поколения (3GPP). Однако данное описание не должно интерпретироваться как ограничивающееся до стандартов IEEE 802.16e, IEEE 802.16m или LTE 3GPP. Независимо от механизма, используемого для ARQ, предпочтительным является осуществление продвинутого управления буфером, и оно является выгодным за свою способность согласовываться со стандартизированным механизмом.

[89] Первый иллюстративный вариант осуществления

[90] Первый иллюстративный вариант осуществления настоящего изобретения включает в себя способ для передатчика ARQ точного определения объема использования буфера приема ARQ, так чтобы передатчик ARQ не передавал больше, чем приемник ARQ мог бы поддерживать. Параметр ARQ_MAX_BUFFER_SIZE представляет собой параметр согласования между передатчиком ARQ, таким как базовая станция (BS), и приемником ARQ, таким как мобильная станция (MS). ARQ_MAX_BUFFER_SIZE представляет собой максимальный размер буфера ARQ (в байтах), который приемник ARQ способен назначать для всех соединений ARQ. Приемник ARQ информирует передатчик ARQ о максимальном размере буфера ARQ во время согласования функциональных возможностей. Передатчик ARQ обеспечивает, чтобы новая передача блока ARQ не превышала ARQ_MAX_BUFFER_SIZE - ARQ_BUFFER_USED. ARQ_BUFFER_USED обозначает полное использование буфера ARQ для всех потоков с задействованием ARQ на приемнике ARQ. Другими словами, ARQ_BUFFER_USED обозначает сумму ARQ_BUFFER_USED на поток для всех потоков с задействованием ARQ на приемнике ARQ. ARQ_BUFFER_USED на поток вычисляется как заполненный размер буфера окна передатчика ARQ (от ARQ_TX_WINDOW_START до ARQ_TX_NEXT_SN-1 (включительно)). В данном случае, если блоки ARQ, с порядковым номером (SN), меньшим, чем ARQ_TX_WINDOW_START, являются частью того же самого сервисного блока данных (SDU) управления доступом к среде (MAC), что и первый блок ARQ в окне передатчика ARQ, тогда эти блоки ARQ должны быть включены в вычисление ARQ_BUFFER_USED на поток. Другими словами, при определении объема использования буфера приема ARQ, передатчик ARQ также учитывает блоки ARQ на приемнике ARQ как ARQ_BUFFER_USED, если они имеют SN меньший, чем ARQ_TX_WINDOW_START, и все еще находятся в ожидании полной реконструкции блока SDU, прежде чем быть доставленными на более высокий уровень. Ниже со ссылкой на фиг.7 описываются: пример заполнения буфера, а также вычисление доступного пространства буфера.

[91] Фиг.7 иллюстрирует заполнение буфера и вычисление доступного пространства буфера в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

[92] Касательно фиг.7 продемонстрированы три соединения ARQ, включающие в себя соединение 1 701 ARQ, соединение 2 702 ARQ и соединение 3 703 ARQ, совместно использующие буфер ARQ на приемнике ARQ. Передатчик ARQ информируется о ARQ_MAX_BUFFER_SIZE, символизирующимся посредством всего пространства внутри квадрата 700. Передатчик ARQ определяет заполнение буфера ARQ_BUFFER_USED для каждого соединения ARQ, учитывая все блоки ARQ, сохраненные в буфере приема ARQ. Доступное пространство 710 буфера ARQ определяется следующим образом:

[93] ARQ_MAX_BUFFER_SIZE - ARQ_BUFFER_USED_CONNECTION_1 - ARQ_BUFFER_USED_CONNECTION_2 - ARQ_BUFFER_USED_CONNECTION_3.

[94] Пример управления буфером для соединения ARQ будет описан ниже со ссылкой на фиг.8.

[95] Фиг.8 иллюстрирует управление буфером для соединения ARQ в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

[96] Касательно фиг.8 продемонстрировано соединение ARQ. В данном случае предполагается, что нижняя граница окна приема ARQ указывает на SN=x. Получив подтверждение ACK, передатчик ARQ передвигает нижнюю границу окна передачи ARQ на SN=x. Однако передатчик ARQ должен включить блоки ARQ с SN=x-1 и SN=x-2 при вычислении ARQ_BUFFER_USED_CONNECTION_i, поскольку оба блока ARQ все еще находятся в буфере приема ARQ в ожидании большего количества данных в целях реконструкции блока SDU. В данном случае ARQ_BUFFER_USED_CONNECTION_i=сумме(Size_of_ARQ_SN_k), где k=x-2, x-1, x, x+1,..., h.

[97] Второй иллюстративный вариант осуществления

[98] Второй иллюстративный вариант осуществления настоящего изобретения включает в себя способ для выведения, был ли блок ARQ удален из буфера приема ARQ. Передатчик ARQ знает контекст фрагментации для каждого переданного пакета. Таким образом, когда блок ARQ находится вне окна передачи ARQ (также вне окна приема ARQ), передатчик ARQ определяет, включать ли блок ARQ в вычисляемый ARQ_BUFFER_USED.

[99] Передатчик ARQ определяет, включать ли блок ARQ в вычисляемый ARQ_BUFFER_USED, посредством определения, соответствует ли последний бит блока ARQ последнему биту блока SDU. Если определяется, что последний бит блока ARQ соответствует последнему биту блока SDU, все блоки ARQ, вплоть до данного блока ARQ включительно, могут быть доставлены на более высокий уровень, и, таким образом, в ARQ_BUFFER_USED необходимо включить нулевое количество блоков ARQ.

[100] В противном случае, если определяется, что первый бит блока ARQ соответствует первому биту блока SDU, все блоки ARQ, вплоть до данного блока ARQ не включительно, могут быть доставлены на более высокий уровень, и, таким образом, в ARQ_BUFFER_USED необходимо включить нулевое количество блоков ARQ, вплоть до данного блока ARQ включительно.

[101] Определение того, включать ли блок ARQ в вычисляемый ARQ_BUFFER_USED с использованием поля FI, более детально описано ниже со ссылкой на фиг.9.

[102] Фиг.9 иллюстрирует блок-схему последовательности операций для определения того, включать ли блок ARQ в ARQ_BUFFER_USED с использованием поля FI в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

[103] Касательно фиг.9 иллюстрируемая процедура выработки решения повторяется в обратном направлении, если текущий блок ARQ представляет собой непрерывный фрагмент до тех пор, пока не будет удовлетворено одно из условий, описанных выше, и передатчик ARQ не определит, какие блоки ARQ могут быть удалены из буфера приема ARQ, и какие блоки ARQ должны все еще быть включенными в ARQ_BUFFER_USED, даже если они находятся вне окна передачи ARQ и окна приема ARQ. В нижеследующем примере предполагается, что передатчик ARQ определяет, что из окна приема ARQ удаляются все блоки ARQ, вплоть до, но не включая, SN=x-1. На этапе 902 передатчик ARQ принимает подтверждение ACK от приемника ARQ, что предоставляет передатчику ARQ возможность продвижения окна передачи ARQ от предыдущей нижней границы SN=x до SN=y+1. На этапе 904 передатчик ARQ осуществляет оценку текущего блока (то есть блока ARQ с SN=y).

[104] На этапе 906 определяется, соответствует ли последний бит блока ARQ последнему биту блока SDU. Последний бит блока ARQ может быть определен как соответствующий последнему биту блока SDU, если FI=00, или если FI=10.

[105] Если определяется, что последний бит блока ARQ соответствует последнему биту блока SDU, все блоки ARQ, вплоть до оцененного блока ARQ включительно (то есть блока ARQ с SN=y), могут быть доставлены на более высокий уровень на этапе 908 и, таким образом, могут быть исключены из ARQ_BUFFER_USED.

[106] Если определяется, что последний бит блока ARQ не соответствует последнему биту блока SDU, на этапе 910 определяется, соответствует ли первый бит блока ARQ первому биту блока SDU. Первый бит блока ARQ может быть определен как соответствующий первому биту блока SDU, если FI=01.

[107] Если определяется, что первый бит блока ARQ соответствует первому биту блока SDU, все блоки ARQ, вплоть до, но не включая оцененный блок ARQ (то есть блок ARQ с SN=y), могут быть доставлены на более высокий уровень на этапе 912 и, таким образом, могут быть исключены из ARQ_BUFFER_USED.

[108] В противоположность этому, если определяется, что первый бит блока ARQ не соответствует первому биту блока SDU, передатчик ARQ на этапе 914 осуществляет оценку предыдущего блока ARQ (то есть блока ARQ с SN=y-1). После этого процесс возвращается к этапу 906.

[109] Процедура продолжается до тех пор, пока она не закончит оценку блока ARQ с SN=x, если брать предельный случай. В данном случае все блоки ARQ от SN=x-1 до SN=y остаются ожидающими в буфере приема ARQ, даже хотя они находятся вне окна приема ARQ.

[110] В качестве альтернативы определение того, включать ли блок ARQ в вычисляемый ARQ_BUFFER_USED, может использовать поле FC. Определение того, включать ли блок ARQ в вычисляемый ARQ_BUFFER_USED с использованием поля FC, более детально описано ниже со ссылкой на фиг.10.

[111] Фиг.10 иллюстрирует блок-схему последовательности операций для определения того, включать ли блок ARQ в ARQ_BUFFER_USED с использованием поля FC в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

[112] Касательно фиг.10 иллюстрируемая процедура выработки решения повторяется в обратном направлении, если текущий блок ARQ представляет собой непрерывный фрагмент, до тех пор, пока не будет удовлетворено одно из условий, описанных выше, и передатчик ARQ не определит, какие блоки ARQ могут быть удалены из буфера приема ARQ и какие блоки ARQ должны все еще быть включенными в ARQ_BUFFER_USED, даже если они находятся вне окна передачи ARQ и окна приема ARQ. В нижеследующем примере предполагается, что передатчик ARQ определяет, что из окна приема ARQ удаляются все блоки ARQ, вплоть до, но не включая, SN=x-1. На этапе 1002 передатчик ARQ принимает подтверждение ACK от приемника ARQ, что предоставляет передатчику ARQ возможность продвижения окна передачи ARQ (ARQ_TX_WINDOW_START) от предыдущей нижней границы SN=x до SN=y+1. На этапе 1004 передатчик ARQ осуществляет оценку текущего блока (то есть блока ARQ с SN=y).

[113] На этапе 1006 определяется, соответствует ли последний бит блока ARQ последнему биту блока SDU. Последний бит блока ARQ может быть определен как соответствующий последнему биту блока SDU, если FC=00 или если FC=10.

[l14] Если определяется, что последний бит блока ARQ соответствует последнему биту блока SDU, все блоки ARQ, вплоть до оцененного блока ARQ включительно (то есть блока ARQ с SN=y), могут быть доставлены на более высокий уровень на этапе 1008 и, таким образом, могут быть исключены из ARQ_BUFFER_USED.

[115] Если определяется, что последний бит блока ARQ не соответствует последнему биту блока SDU, на этапе 1010 определяется, соответствует ли первый бит блока ARQ первому биту блока SDU. Первый бит блока ARQ может быть определен как соответствующий первому биту блока SDU, если FC=01.

[116] Если определяется, что первый бит блока ARQ соответствует первому биту блока SDU, все блоки ARQ, вплоть до, но не включая оцененный блок ARQ (то есть блок ARQ с SN=y), могут быть доставлены на более высокий уровень на этапе 1012 и, таким образом, могут быть исключены из ARQ_BUFFER_USED.

[117] В противоположность этому, если определяется, что первый бит блока ARQ не соответствует первому биту блока SDU, передатчик ARQ на этапе 1014 осуществляет оценку предыдущего блока ARQ (то есть блока ARQ с SN=y-1). После этого процесс возвращается к этапу 1006.

[118] Процедура продолжается до тех пор, пока она не закончит оценку блока ARQ с SN=x, если брать предельный случай. В данном случае все блоки ARQ от SN=x-1 до SN=y остаются ожидающими в буфере приема ARQ, даже хотя они находятся вне окна приема ARQ.

[119] Третий иллюстративный вариант осуществления

[120] Третий иллюстративный вариант осуществления настоящего изобретения включает в себя способ, где передатчик ARQ не обязан включать весь блок ARQ в вычисление ARQ_BUFFER_USED, если часть блока ARQ может быть доставлена на более высокий уровень в приемнике ARQ. Например, учитывая сценарий на фиг.5, допускающий, что передатчик ARQ передал блоки PDU RLC вплоть до k+10. Дополнительно предположим, что ARQ_TX_ WINDOW_START является равным k, что означает, что все блоки PDU, вплоть до, но не включая k, были подтверждены приемником ARQ. В соответствии с этим в данном иллюстративном варианте осуществления ARQ_BUFFER_USED должен включать в себя, по меньшей мере, блок PDU k-1 RLC, поскольку блок SDU n не может быть реконструирован без блока PDU k RLC. Предполагая, что приемник ARQ подтвердил прием блока PDU k RLC, передатчик ARQ определяет, что блок SDU n, n+1 и n+2 RLC может быть реконструирован приемником ARQ, и, таким образом, блок PDU k-1 RLC может быть исключен из ARQ_BUFFER_USED. Более того, только последняя часть блока PDU k RLC нуждается во включении в ARQ_BUFFER_USED, поскольку часть, соответствующая блоку SDU n, n+1 и n+2 RLC, может быть удалена из буфера приема ARQ и доставлена на более высокий уровень.

[121] Четвертый иллюстративный вариант осуществления

[122] Четвертый иллюстративный вариант осуществления настоящего изобретения включает в себя способ определения для передатчика ARQ того, включать ли блок ARQ в ARQ_BUFFER_USED с использованием другой информации. В данном случае передатчик ARQ сбрасывает блок ARQ с SN, соответствующим нижней границе текущего окна передачи ARQ, и информирует приемник ARQ. Получив подтверждение от приемника ARQ, передатчик ARQ может без риска заранее исключить данный блок ARQ из ARQ_BUFFER_USED, поскольку приемник ARQ сбросил данный блок ARQ и продвинул окно приема ARQ. Если приемник ARQ поддерживает таймер ARQ_RX_PURGE_TIMEOUT, и когда данный таймер истекает на SN=z, приемник ARQ продвигает окна приема ARQ сверх SN=z. В этом случае приемник ARQ удалит все блоки ARQ с номером SN, меньшим, чем или равным номеру SN=z, из буфера приема ARQ. Вследствие этого передатчик ARQ может также поддерживать схожий таймер, так чтобы после того, как он получит подтверждение от приемника ARQ, он мог исключать эти блоки ARQ при вычислении ARQ_BUFFER_USED.

[123] Пятый иллюстративный вариант осуществления

[124] Пятый иллюстративный вариант осуществления настоящего изобретения включает в себя способ для использования поля информации в IE обратной передачи ARQ, так чтобы приемник ARQ мог ясно информировать передатчик ARQ, были ли или нет удалены из буфера приема ARQ все блоки ARQ, вплоть до, но не включая, нижней границы окна приема ARQ. Пример IE, используемого для информирования передатчика ARQ, продемонстрирован в Таблице 4.

[125] Таблица 4

[126] Фиг.11 представляет собой структурную диаграмму, иллюстрирующую приемник ARQ в беспроводной системе связи в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

[127] Касательно фиг.11 приемник ARQ включает в себя дуплексер 1100, приемник 1110, передатчик 1120, контроллер 1130, а также блок 1140 хранения. Приемник ARQ может включать в себя любое количество дополнительных структурных элементов. Однако описание дополнительных структурных элементов приемника ARQ является опущенным для краткости. Приемник ARQ может представлять собой MS в беспроводной системе связи.

[128] Дуплексер 1100 передает сигнал передачи, обеспечиваемый от передатчика 1120, через посредство антенны, и обеспечивает сигнал приема от антенны на приемник 1110 в соответствии со схемой дуплексной передачи.

[129] Приемник 1110 преобразует сигнал приема, обеспечиваемый от дуплексера 1100, в тональный модулирующий сигнал, и обеспечивает данный тональный модулирующий сигнал на контроллер 1130. Например, когда беспроводная система связи использует схему мультиплексирования с ортогональным частотным разделением (OFDM), приемник 1110 включает в себя высокочастотный (RF) процессор, аналого-цифровой преобразователь (ADC), демодулятор OFDM и декодер. В соответствии с этим RF процессор преобразует сигнал RF, обеспечиваемый от дуплексера 1100, в групповой аналоговый сигнал. ADC преобразует аналоговый сигнал, обеспечиваемый от RF процессора, в цифровые дискретные данные. Демодулятор OFDM преобразует дискретные данные во временной области, обеспечиваемые от ADC, в данные в частотной области посредством осуществления быстрого преобразования Фурье (FFT). Декодер демодулирует и декодирует сигнал, обеспечиваемый от демодулятора OFDM, в соответствии с уровнем схемы модуляции и кодирования (MCS).

[130] Контроллер 1130 управляет всеми операциями приемника ARQ. Данные операции приемника ARQ включают в себя любые из операций, описанные выше в прямой или косвенной форме как осуществляемые посредством приемника ARQ.

[131] Передатчик 1120 преобразует сигнал передачи в сигнал RF и обеспечивает данный сигнал RF на дуплексер 1100 под управлением контроллера 1130. Например, когда беспроводная система связи использует схему OFDM, передатчик 1120 включает в себя кодер, модулятор OFDM, цифроаналоговый преобразователь (DAC) и RF процессор. Кодер осуществляет кодирование и модулирование сигнала передачи в соответствии с уровнем MCS под управлением контроллера 1130. Модулятор OFDM преобразует данные в частотной области, обеспечиваемые от кодера, в дискретные данные (то есть символ OFDM) во временной области посредством осуществления обратного FFT (IFFT). DAC преобразует дискретные данные, обеспечиваемые от модулятора OFDM, в аналоговый сигнал. RF процессор преобразует групповой аналоговый сигнал, обеспечиваемый от DAC, в сигнал RF.

[132] Блок 1140 хранения сохраняет программы, требуемые для всех операций приемника ARQ, а также различные данные. Также блок 1140 хранения может быть использован в качестве буфера приемника ARQ.

[133] Фиг.12 представляет собой структурную диаграмму, иллюстрирующую передатчик ARQ в беспроводной системе связи в соответствии с одним иллюстративным вариантом осуществления настоящего изобретения.

[134] Касательно фиг.12 передатчик ARQ включает в себя дуплексер 1200, приемник 1210, передатчик 1220, контроллер 1230, блок хранения 1240, а также широкополосный приемопередатчик 1250. Передатчик ARQ может включать в себя любое количество дополнительных структурных элементов. Однако описание дополнительных структурных элементов передатчика ARQ является опущенным для краткости. Передатчик ARQ может представлять собой BS в беспроводной системе связи.

[135] Дуплексер 1200 передает сигнал передачи, обеспечиваемый от передатчика 1220, через посредство антенны, и обеспечивает сигнал приема от антенны на приемник 1210 в соответствии со схемой дуплексной передачи.

[136] Приемник 1210 преобразует сигнал приема, обеспечиваемый от дуплексера 1200, в тональный модулирующий сигнал, и обеспечивает данный тональный модулирующий сигнал на контроллер 1230. Например, когда беспроводная система связи использует схему OFDM, приемник 1210 включает в себя RF процессор, ADC, демодулятор OFDM и декодер. RF процессор преобразует сигнал RF, обеспечиваемый от дуплексера 1200, в групповой аналоговый сигнал. ADC преобразует аналоговый сигнал, обеспечиваемый от RF процессора, в цифровые дискретные данные. Демодулятор OFDM преобразует дискретные данные во временной области, обеспечиваемые от ADC, в данные в частотной области посредством осуществления FFT. Декодер демодулирует и декодирует сигнал, обеспечиваемый от демодулятора OFDM в соответствии с уровнем MCS.

[137] Контроллер 1230 управляет всеми операциями передатчика ARQ. Данные операции передатчика ARQ включают в себя любые из операций, описанные выше в прямой или косвенной форме как осуществляемые посредством передатчика ARQ. Например, контроллер 1230 может определять неиспользованную емкость буфера приемника ARQ в приемнике ARQ, определять, может ли буфер приемника ARQ поддерживать блок ARQ, назначенный к передаче, на основе определенной неиспользованной емкости буфера приемника ARQ, а также, если определено, что буфер приемника ARQ может поддерживать блок ARQ, назначенный к передаче, может осуществлять управление с целью передачи блока ARQ на приемник ARQ.

[138] Передатчик 1220 преобразует сигнал передачи в сигнал RF и обеспечивает данный сигнал RF на дуплексер 1200 под управлением контроллера 1230. Например, когда беспроводная система связи использует схему OFDM, передатчик 1220 включает в себя кодер, модулятор OFDM, цифроаналоговый преобразователь (DAC) и RF процессор. Кодер осуществляет кодирование и модулирование сигнала передачи в соответствии с уровнем MCS под управлением контроллера 1230. Модулятор OFDM преобразует данные в частотной области, обеспечиваемые от кодера, в дискретные данные (то есть символ OFDM) во временной области посредством осуществления IFFT. DAC преобразует дискретные данные, обеспечиваемые от модулятора OFDM, в аналоговый сигнал. RF процессор преобразует групповой аналоговый сигнал, обеспечиваемый от DAC, в сигнал RF.

[139] Блок 1240 хранения сохраняет программы, требуемые для всех операций приемника ARQ, а также различные данные.

[140] Широкополосный приемопередатчик 1250 облегчает связь с по меньшей мере одним другим модулем в опорной сети (CN) беспроводной системы связи, такой как беспроводная система связи, работающая в соответствии со стандартами IEEE 802.16e, IEEE 802.16m или LTE 3GPP. Широкополосный приемопередатчик 1250 может быть опущен.

[141] Определенные аспекты настоящего изобретения могут также осуществляться в качестве машиночитаемого кода на считываемой компьютером записывающей среде (носителе). Считываемая компьютером записывающая среда (носитель) представляет собой любое устройство хранения данных, способное сохранять данные, которые могут быть потом считаны посредством вычислительной системы. Примеры считываемой компьютером записывающей среды (носителя) включают в себя постоянное запоминающее устройство (ROM), оперативное запоминающее устройство (RAM), компакт-диски (CD-ROM), магнитные пленки, флоппи-диски, оптические устройства хранения данных, а также несущие волны (такие как передача данных через Интернет). Считываемая компьютером записывающая среда (носитель) может также распределяться по сетевым спаренным компьютерным системам, так чтобы машиночитаемый код сохранялся и выполнялся распределенным способом. Также функциональные программы, код и сегменты кода для осуществления настоящего изобретения могут легко быть истолкованы программистами - специалистами в данной области техники, к которой относится настоящее изобретение.

[142] В то время как данное изобретение было продемонстрировано и описано со ссылкой на его определенные иллюстративные варианты осуществления, для специалистов в данной области техники будет понятно, что в нем могут быть произведены различные изменения в форме и деталях, не выходя за пределы сущности и объема настоящего изобретения, как определено посредством прилагаемой формулы изобретения и ее эквивалентов.

Изобретение относится к автоматическим запросам на повторение (ARQ)в беспроводных системах связи. Технический результат заключается в предотвращении переполнения буфера ARQ. Предложены передатчик автоматического запроса на повторение (ARQ) для использования в беспроводной системе связи и способ для управления им. Данный способ включает в себя этапы, на которых определяют неиспользованную емкость буфера приемника ARQ в приемнике ARQ посредством вычитания суммированного объема использования буфера приемника ARQ из максимального размера буфера приемника ARQ, определяют, что буфер приемника ARQ может поддерживать блок ARQ, назначенный к передаче, если размер блока ARQ, назначенного к передаче, не превышает определенную неиспользованную емкость буфера приемника ARQ и если определено, что буфер приемника ARQ может поддерживать блок ARQ, назначенный к передаче, передают блок ARQ на приемник ARQ, причем определение неиспользованной емкости буфера приемника ARQ в приемнике ARQ содержит этап, на котором: определяют блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также для любых блоков ARQ вне окна передачи ARQ, которые являются частью того же самого сервисного блока данных (SDU) управления доступом к среде (MAC), как и первый блок ARQ в пределах окна передачи ARQ. 2 н. и 22 з.п. ф-лы, 12 ил.

1. Способ управления передатчиком автоматического запроса на повторение (ARQ) в беспроводной системе связи, причем способ содержит этапы, на которых:

определяют неиспользованную емкость буфера приемника ARQ в приемнике ARQ посредством вычитания суммированного объема использования буфера приемника ARQ из максимального размера буфера приемника ARQ;

определяют, что буфер приемника ARQ может поддерживать блок ARQ, назначенный к передаче, если размер блока ARQ, назначенного к передаче, не превышает определенную неиспользованную емкость буфера приемника ARQ; и

если определено, что буфер приемника ARQ может поддерживать блок ARQ, назначенный к передаче, передают блок ARQ на приемник ARQ,

причем определение неиспользованной емкости буфера приемника ARQ в приемнике ARQ содержит этап, на котором: определяют блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также для любых блоков ARQ вне окна передачи ARQ, которые являются частью того же самого сервисного блока данных (SDU) управления доступом к среде (MAC), как и первый блок ARQ в пределах окна передачи ARQ.

2. Способ по п.1, в котором определение неиспользованной емкости буфера приемника ARQ в приемнике ARQ содержит этапы, на которых:

принимают информацию от приемника ARQ, соответствующую максимальному размеру буфера приемника ARQ; и

определяют суммированный объем использования буфера приемника ARQ, причем суммированный объем использования буфера приемника ARQ содержит суммирование объема использования буфера приемника ARQ для каждого из одного или более потоков ARQ.

3. Способ по п.1, в котором определение неиспользованной емкости буфера приемника ARQ в приемнике ARQ содержит этап, на котором определяют блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также любых блоков ARQ вне окна передачи ARQ, которые ожидают реконструкции сервисного блока данных (SDU) управления доступом к среде (MAC).

4. Способ по п.1, в котором определение неиспользованной емкости буфера приемника ARQ в приемнике ARQ содержит этапы, на которых:

определяют, соответствует ли последний бит блока ARQ вне окна передачи ARQ последнему биту сервисного блока данных (SDU) управления доступом к среде (MAC); и

если определено, что последний бит блока ARQ вне окна передачи ARQ соответствует последнему биту блока SDU MAC, определяют блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также любых блоков ARQ вне окна передачи ARQ, кроме блоков ARQ, вплоть до блока ARQ вне окна передачи ARQ включительно, которые ожидают реконструкции блока SDU MAC.

5. Способ по п.4, в котором определяют, что последний бит блока ARQ вне окна передачи ARQ соответствует последнему биту блока SDU MAC, если его значение интерпретации поля (FI) составляет одно из: «00» и «10».

6. Способ по п.4, в котором определяют, что последний бит блока ARQ вне окна передачи ARQ соответствует последнему биту блока SDU MAC, если его значение управления фрагментом (FC) составляет одно из: «00» и «01».

7. Способ по п.4, в котором определение неиспользованной емкости буфера приемника ARQ в приемнике ARQ дополнительно содержит этапы, на которых:

если определено, что последний бит блока ARQ вне окна передачи ARQ не соответствует последнему биту блока SDU MAC, определяют, соответствует ли первый бит блока ARQ вне окна передачи ARQ первому биту сервисного блока данных (SDU) управления доступом к среде (MAC); и

если определено, что первый бит блока ARQ вне окна передачи ARQ соответствует первому биту блока SDU MAC, определяют блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также любых блоков ARQ вне окна передачи ARQ, кроме блоков ARQ, вплоть до, но не включая, блока ARQ вне окна передачи ARQ, которые ожидают реконструкции блока SDU MAC.

8. Способ по п.7, в котором определяют, что первый бит блока ARQ вне окна передачи ARQ соответствует первому биту блока SDU MAC, если его значение интерпретации поля (FI) составляет «01».

9. Способ по п.7, в котором определяют, что первый бит блока ARQ вне окна передачи ARQ соответствует первому биту блока SDU MAC, если его значение управления фрагментом (FC) составляет «10».

10. Способ по п.1, в котором определение неиспользованной емкости буфера приемника ARQ в приемнике ARQ содержит этап, на котором определяют блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также для любых частей блоков ARQ вне окна передачи ARQ, которые ожидают реконструкции сервисного блока данных (SDU) управления доступом к среде (MAC).

11. Способ по п.1, в котором определение неиспользованной емкости буфера приемника ARQ в приемнике ARQ содержит этап, на котором определяют блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также для любых блоков ARQ вне окна передачи ARQ, для которых было получено подтверждение от приемника ARQ, и соответствующий таймер сброса не истек.

12. Способ по п.1, в котором определение неиспользованной емкости буфера приемника ARQ в приемнике ARQ содержит этап, на котором определяют блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также для любых блоков ARQ вне окна передачи ARQ, для которых от приемника ARQ принята индикация, обозначающая один или более блоков ARQ, которые не были удалены из буфера приемника ARQ.

13. Устройство передатчика ARQ для использования в беспроводной системе связи, причем устройство содержит:

приемник для приема сигналов от по меньшей мере одного приемника ARQ;

передатчик для передачи сигналов на по меньшей мере один приемник ARQ; и

контроллер, осуществляющий управление приемником и передатчиком, а также определяющий неиспользованную емкость буфера приемника ARQ в приемнике ARQ посредством вычитания суммированного объема использования буфера приемника ARQ из максимального размера буфера приемника ARQ, определяющий, что буфер приемника ARQ может поддерживать блок ARQ, назначенный к передаче, если размер блока ARQ, назначенного к передаче, не превышает определенную неиспользованную емкость буфера приемника ARQ, и, если определено, что буфер приемника ARQ может поддерживать блок ARQ, назначенный к передаче, осуществляющий управление с целью передачи блока ARQ на приемник ARQ,

причем контроллер, при определении неиспользованной емкости буфера приемника ARQ в приемнике ARQ, определяет блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также для любых блоков ARQ вне окна передачи ARQ, которые являются частью того же самого сервисного блока данных (SDU) управления доступом к среде (MAC), как и первый блок ARQ в пределах окна передачи ARQ.

14. Устройство по п.13, в котором контроллер, при определении неиспользованной емкости буфера приемника ARQ в приемнике ARQ, осуществляет управление с целью приема информации от приемника ARQ, соответствующей максимальному размеру буфера приемника ARQ, и определяет суммированный объем использования буфера приемника ARQ, причем данный суммированный объем использования буфера приемника ARQ содержит суммирование объема использования буфера приемника ARQ для каждого из одного или более потоков ARQ.

15. Устройство по п.13, в котором контроллер, при определении неиспользованной емкости буфера приемника ARQ в приемнике ARQ, определяет блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также любых блоков ARQ вне окна передачи ARQ, которые ожидают реконструкции сервисного блока данных (SDU) управления доступом к среде (MAC).

16. Устройство по п.13, в котором контроллер, при определении неиспользованной емкости буфера приемника ARQ в приемнике ARQ, определяет, соответствует ли последний бит блока ARQ вне окна передачи ARQ последнему биту сервисного блока данных (SDU) управления доступом к среде (MAC), и

причем, если контроллер определяет, что последний бит блока ARQ вне окна передачи ARQ соответствует последнему биту блока SDU MAC, контроллер определяет блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также любых блоков ARQ вне окна передачи ARQ, кроме блоков ARQ, вплоть до блока ARQ вне окна передачи ARQ включительно, которые ожидают реконструкции блока SDU MAC.

17. Устройство по п.16, в котором контроллер определяет, что последний бит блока ARQ вне окна передачи ARQ соответствует последнему биту блока SDU MAC, если его значение интерпретации поля (FI) составляет одно из: «00» и «10».

18. Устройство по п.16, в котором контроллер определяет, что последний бит блока ARQ вне окна передачи ARQ соответствует последнему биту блока SDU MAC, если его значение управления фрагментом (FC) составляет одно из: «00» и «01».

19. Устройство по п.16, в котором, если контроллер определяет, что последний бит блока ARQ вне окна передачи ARQ не соответствует последнему биту блока SDU MAC, контроллер определяет, соответствует ли первый бит блока ARQ вне окна передачи ARQ первому биту сервисного блока данных (SDU) управления доступом к среде (MAC), и

причем, если контроллер определяет, что первый бит блока ARQ вне окна передачи ARQ соответствует первому биту блока SDU MAC, контроллер определяет блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также любых блоков ARQ вне окна передачи ARQ, кроме блоков ARQ, вплоть до, но не включая, блока ARQ вне окна передачи ARQ, которые ожидают реконструкции блока SDU MAC.

20. Устройство по п.16, в котором контроллер определяет, что первый бит блока ARQ вне окна передачи ARQ соответствует первому биту блока SDU MAC, если его значение интерпретации поля (FI) составляет «01».

21. Устройство по п.16, в котором контроллер определяет, что первый бит блока ARQ вне окна передачи ARQ соответствует первому биту блока SDU MAC, если его значение управления фрагментом (FC) составляет «10».

22. Устройство по п.13, в котором контроллер, при определении неиспользованной емкости буфера приемника ARQ в приемнике ARQ, определяет блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также для любых частей блоков ARQ вне окна передачи ARQ, которые ожидают реконструкции сервисного блока данных (SDU) управления доступом к среде (MAC).

23. Устройство по п.13, в котором контроллер, при определении неиспользованной емкости буфера приемника ARQ в приемнике ARQ, определяет блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также для любых блоков ARQ вне окна передачи ARQ, для которых было получено подтверждение от приемника ARQ, и соответствующий таймер сброса не истек.

24. Устройство по п.13, в котором контроллер, при определении неиспользованной емкости буфера приемника ARQ в приемнике ARQ, определяет блоки ARQ в качестве использующих буфер приемника ARQ для любых блоков ARQ в пределах окна передачи ARQ, а также для любых блоков ARQ вне окна передачи ARQ, для которых от приемника ARQ принята индикация, обозначающая один или более блоков ARQ, которые не были удалены из буфера приемника ARQ.

| WO 2009044534 A1, 09.04.2009 | |||

| УСТРОЙСТВО ПРЕДОТВРАЩЕНИЯ ОШИБОК ДЛЯ МУЛЬТИМЕДИЙНОЙ СИСТЕМЫ | 1998 |

|

RU2234806C2 |

| US 2005152350 A1, 14.07.2005 | |||

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ДАННЫХ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2002 |

|

RU2251804C2 |

| WO 2006065008 A1, 22.06.2006. | |||

Авторы

Даты

2014-03-10—Публикация

2010-06-30—Подача