Область техники, к которой относится изобретение

Изобретение относится к устройству формирования изображения такому, как датчик изображения CMOS, и к системе камеры.

Уровень техники

В последнее время датчики изображения CMOS широко используются в цифровых фотокамерах, видеокамерах, камерах систем видеонаблюдения и т.д., и рынок для датчиков изображения CMOS расширился.

Каждый пиксель в датчике изображения CMOS преобразует входной свет в электроны, используя фотодиод, который является фотоэлектрическим устройством преобразования, содержит электрон в течение заданного периода и затем выводит сигнал, отражающий величину накопленных зарядов, в аналого-цифровой (AD) преобразователь, включенный в микросхему. AD преобразователь оцифровывает сигнал, который будет отправлен наружу.

В датчике изображения CMOS такие пиксели формирования изображения расположены в матричной форме.

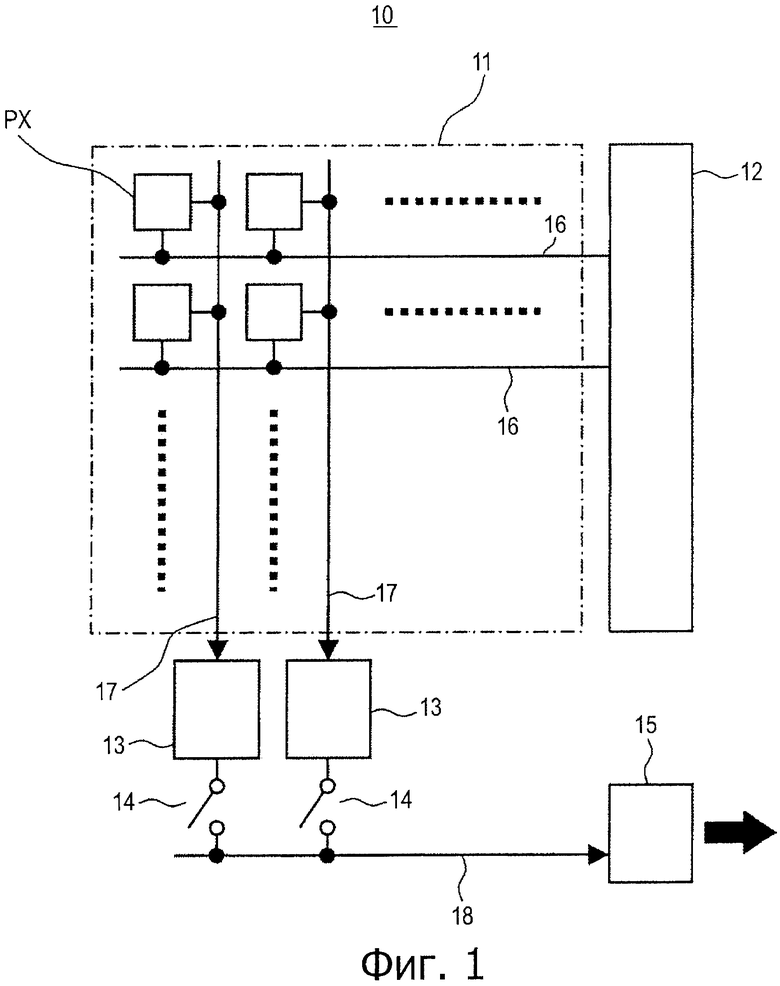

На фиг.1 показана схема, представляющая типичную конфигурацию микросхемы датчика 10 изображения CMOS, который является твердотельным устройством формирования изображения.

Такой датчик 10 изображения CMOS имеет блок 11 матрицы пикселей, схему 12 управления горизонтальной разверткой, AD преобразователь 13, переключатель 14, выходную цепь 15, линию 16 управления строки, линию 17 сигнала вертикальной развертки и линию 18 передачи.

В блоке 11 матрицы пикселей имеется множество пикселей РХ, расположенных в матричной форме в направлении строки и в направлении столбца. Линия 17 сигнала вертикальной развертки совместно используется множеством пикселей РХ, выровненных в направлении строки, и связана с AD преобразователем 13, расположенным в ассоциации с каждым столбцом.

Схема 12 управления горизонтальной разверткой выбирает только одну из множества строк и обеспечивает возможность для линии 16 управления строки считывать накопленные заряды из пикселей РХ строка за строкой.

Линия 16 управления строки сформирована из одиночной линии управления или из множества линий управления для считывания накопленных зарядов из таких пикселей или сброса пикселей строка за строкой.

Сброс здесь означает операцию разряда накопленных зарядов из пикселей, чтобы установить пиксели в состояние перед экспонированием, и выполняется как операция затвора немедленно после считывания каждой строки пикселей или во время инициализации экспонирования.

Во время считывания накопленных зарядов аналоговые сигналы, переданные в AD преобразователь 13 через линию 17 сигнала вертикальной развертки, преобразуют в цифровые сигналы, которые, в свою очередь, последовательно передают в выходную цепь 15 через переключатель 14 для вывода в устройство обработки изображения (не показано), расположенное внутри или снаружи микросхемы.

Когда заканчивают считывание одной строки пикселей в датчике 10 изображения CMOS, выбирают следующую строку и повторяют аналогичное считывание заряда, AD преобразование и вывод сигнала. Завершение обработки во всех строках заканчивает вывод одного кадра данных изображения.

Фиксирующая схема или фиксатор могут быть предусмотрены где-нибудь перед выходным каскадом для конвейерной передачи результатов считывания заряда, AD преобразования и вывода сигнала, но датчик изображения CMOS все еще не способен обрабатывать больше чем одну строку данных изображения.

Время, требуемое для окончания обработки каждой строки данных, определяет верхний предел частоты кадров движущихся изображений.

В JP-A-2002-44527 (Патентный документ 1) и в JP-A-2006-49361 (Патентный документ 2) предложен датчик изображения с многослойной структурой из пикселей и AD преобразователей.

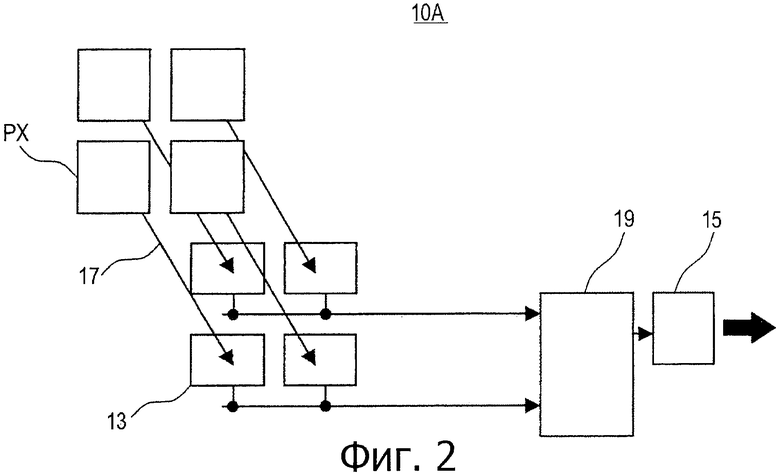

На фиг.2 показана концептуальная схема датчика 10А изображения CMOS с многослойной структурой из пикселей и AD преобразователей.

Для облегчения понимания концепции одинаковыми номерами ссылочных позиций обозначены те же компоненты, показанные на фиг.1.

Датчик 10 изображения CMOS на фиг.2 имеет пиксели РХ и AD преобразователи 13, соответственно, расположенные на разных полупроводниковых подложках в виде массивов. Две полупроводниковых подложки соединяют друг другом в виде слоев, при этом каждый пиксель соединяют с соответствующим AD преобразователем аналоговой линией 17 сигнала.

Использование такой архитектуры может гарантировать считывание зарядов из множества строк пикселей одновременно и параллельное выполнение AD преобразования строка за строкой.

Данные после преобразования временно передают в запоминающее устройство 19 для передачи в устройство обработки изображения (не показано), расположенное внутри или снаружи микросхемы.

Использование такой многослойной структуры может существенно улучшить скорость формирования изображения, по меньшей мере в микросхеме формирования изображения, таким образом гарантируя сверхбыстродействующее формирование изображения кадра.

Кроме того, в последнее время значительное внимание уделяют разработке высокоточной технологии склеивания подложки. Например, в JP-A-2007-234725 (Патентный документ 3) и JP-A-2006-191081 (Патентный документ 4) описана технология склеивания датчика изображения с "обратной стороной облучения" и подложки с установленной схемой противоположно друг другу, и сигналы передают между ними через металлические контактные площадки.

Эта технология позволяет подготовить многослойную структуру, как показано на фиг.2, во время производства на уровне подложки, и пиксели с AD преобразователями подключают, не осуществляя соединение контактными столбиками для каждой микросхемы.

Поскольку эта технология позволяет вырезать отдельные микросхемы после производства на уровне подложки, она подходит для изготовления микропроцессоров и является существенно недорогой.

В JP-A-7-67043 (Патентный документ 5) предложена новая схема подсчета фотонов с разделением времени.

В соответствии со схемой подсчета многократно выполняют двоичный выбор на основе присутствия/отсутствия входного фотона в фотодиоде за данный период, и результаты решения интегрируют, чтобы получить двумерные данные, формирующие изображение.

Таким образом, определяют сигналы от фотодиода в заданный период, и счетчик, соединенный с каждым пикселем, увеличивает величину подсчета на 1, независимо от количества входных фотонов, когда количество входа фотонов за этот период равно или больше 1.

Если частота входных фотонов является случайной вдоль оси времени, фактическое количество входных фотонов и величина подсчета соответствуют распределению Пуассона таким образом, что количество имеет, по существу, линейное отношение, когда частота падения низкая, и может быть скорректирована в любом случае, когда частота попадания высокая.

Поскольку датчик изображения, в котором используют такой подсчет фотонов с разделением времени, всегда обрабатывает выходные данные пикселей как цифровые данные, случайный шум или фиксированный выступ характеристики из-за передачи и усиления аналоговых сигналов не возникают.

В это время это остаются только флуктуационный шум, возникающий при съемке, и темновой ток, генерируемый в пикселях, и может быть получено очень высокое отношение сигнал-шум, в частности, при формировании изображений с малой освещенностью.

Сущность изобретения

Использование структуры, показанной на фиг.2, может обеспечить возможность быстрого параллельного считывания сигналов из блока матрицы пикселей и выполнения AD преобразования перед сохранением в виде данных в запоминающем устройстве.

Однако существенные трудности все еще остаются при оцифровке данных и оптимальном использовании всех снятых данных, хранящихся в запоминающем устройстве 19.

Во-первых, когда большой объем данных, полученных при в десятки раз более высокой частоте кадров, передают наружу в том виде, как они есть, интерфейс передачи и микросхема для последующей обработки изображения становятся очень дорогими. Если частоту кадров просто значительно повысить, за пределы способности восприятия глаз, область применения датчика изображения ограничивается.

Поэтому желательно предпринять некоторые новые меры для добавления полезных эффектов, включающих в себя улучшение качества изображения, если возможно, в микросхеме формирования изображения и в выходных данных в полосе, которая не сильно отличается от полосы в нормальном случае при применении такого сверхбыстрого формирования изображения.

Однако в Патентном документе 2 не описана обработка данных после сохранения в запоминающем устройстве.

В литературе, цитируемой в описании варианта выполнения в Патентном документе 1, характеристику быстрого считывания применяют для достижения "сигма-дельта" AD преобразования.

Однако эта схема затрудняет компенсацию изменений характеристик индивидуальных AD преобразователей, и достижение такого AD преобразования должно не обязательно улучшает качество изображения.

В общем, нормальный датчик изображения выводит аналоговый сигнал, фотоэлектрически преобразованный пикселем, и подвергает аналоговый сигнал AD преобразованию так, чтобы различные виды шумов были смешаны при обработке передачи аналоговых данных и обработке преобразования аналоговых данных в цифровые данные.

Для получения конфигурации нормального датчика изображения с многослойной структурой необходимо обеспечить соединение для передачи аналогового сигнала между подложками.

Однако по сравнению с соединением в пределах одной подложки соединение между подложками сопровождается большим изменением импеданса, паразитной емкости и т.д., что может генерировать дополнительный шум.

В Патентных документах 5 и 6 предложены устройства формирования изображения, в которых используют подсчет фотонов.

Такое устройство формирования изображения принимает выходной сигнал непосредственно из пикселей в цифровой форме так, что возможно полностью устранить случайный шум или фиксированный шум, возникающие при аналоговой обработке сигналов, которая неизбежна в нормальном датчике изображения. Это приводит к потенциально очень высокому отношению "сигнал-шум".

Однако поскольку для подсчета фотонов требуется обеспечить чрезвычайно быстрое считывание, в устройствах формирования изображения, раскрытых в этих двух патентных документах, предусмотрены цифровые функции принятия решения в индивидуальных пикселях, которые предусмотрены на той же подложке, где расположены устройства приема света.

Например, в Патентном документе 5 для каждого пикселя требуется счетчик.

В Патентном документе 6, в котором описано достижение миниатюризации пикселей, для отдельных пикселей требуются 1-битовые запоминающие устройства, которые располагаются в плоскости наряду с устройствами приема света.

Кроме того, схема, которая называется "1-битовым запоминающим устройством", должна также иметь функцию принятия решения в отношении сигнала, и требует более сложного управления и большого количества элементов схемы, чем простой фиксатор.

Это делает число диафрагмы пикселей очень малым, что не позволяет получить достаточную чувствительность. Кроме того, счетчик, хотя и расположен вне матрицы пикселей, предусматривается для каждого пикселя.

В соответствии с технологией, предложенной в Патентном документе 5, количество фотонов, которые могут фактически ощущаться, определяется общим количеством решений считывания за один период кадра, чтобы сформировать одно изображение при формировании изображения, используя подсчет фотонов с разделением времени.

Когда 12-битовый выход получают при 4095 решениях относительно входных фотонов, например фактическое число зарегистрированных фотонов равно или меньше, чем прежнее количество, и квадратный корень этого числа становится шумом фотосъемки, который возникает случайно для каждого кадра.

В случае формирования изображения с малой освещенностью общее количество входных фотонов на пиксель за один период кадра составляет, например, 200, большую часть из которых фактически подсчитывают без каких-либо проблем. Поэтому отношение "сигнал-шум" для шумов фотосъемки становится таким же, как и у аналогового датчика в предшествующем уровне техники, что делает подсчет фотонов с разделением времени, предпочтительным по сравнению с предшествующим уровнем техники, поскольку он не содержит шумы аналоговой передачи, значительно большие, чем шумы фотосъемки.

С другой стороны, в случае формирования изображения при высокой освещенности и при использовании аналогового датчика, фотодиод которого сохраняет, например, 10000 электронов, можно подсчитать максимум - это количество электронов.

В это время шумы фотосъемки составляют 100 e-rms, и отношение "сигнал-шум" становится в 100 раз (на 40 дБ) большим. При подсчете фотонов с разделением времени невозможно подсчитать приблизительно 1 600 электронов, если используется линейная область, с учетом точности.

В это время шумы фотосъемки составляют 40 e-rms, и полученное отношение "сигнал-шум" в 40 раз (на 32 дБ) больше.

Поэтому в случае полного цифрового формирователя изображения, в котором используется подсчет фотонов с разделением времени, общее количество подсчетов должно быть увеличено, чтобы улучшить отношение "сигнал-шум" при формировании изображения при высокой освещенности.

Однако общее количество подсчетов ограничивается временем считывания данных из пикселей во время принятия решения по входным фотонам.

В то время как считывание данных пикселя представляет собой детектирование незначительного сигнала одиночного фотона, случайные шумы цепи датчика увеличиваются при повышении скорости считывания. Поэтому увеличение частоты появления ошибок считывания ограничивает время считывания данных.

Предположим, что для считывания данных требуется 400 наносекунд. Обычно операция считывания формирователя изображения представляет собой считывание со стиранием информации так, что пиксель при считывании не может содержать заряды (накопление заряда эквивалентно экспонированию).

Поэтому, чтобы обеспечить время экспонирования, которое составляет, например, 90 процентов периода кадра, длительность цикла решения, которая представляет собой сумму времени экспонирования и периода считывания, должна составлять 4 микросекунды.

При условии, что один период кадра составляет 1/60 секунды, тогда максимальное количество подсчетов при принятии решения достигает 4166. Этого количества недостаточно, чтобы обеспечить высокое отношение "сигнал-шум" во время высокой освещенности.

Поэтому желательно предусмотреть устройство формирования изображения и систему камеры, которые избавляют от необходимости обработки аналоговых сигналов для исключения шумов схемы, возникающих в AD преобразователе, и обрабатывать аналоговые сигналы без уменьшения числа диафрагмы пикселей, таким образом улучшая характеристики формирования изображения при низких затратах.

Также желательно предусмотреть устройство формирования изображения и систему камеры, которые оптимизируют установку экспозиции, когда используется подсчет фотонов с разделением времени.

В соответствии с одним вариантом выполнения изобретения предусмотрено устройство формирования изображения, включающее в себя блок матрицы пикселей, имеющий массив пикселей, каждый из которых имеет устройство фотоэлектрического преобразования и выводит электрический сигнал в соответствии с входным фотоном, блок чувствительной схемы, имеющий множество схем датчика, каждая из которых выполняет двоичный выбор, имеется ли входной фотон в пикселе в заданный период после приема от него электрического сигнала, и блок IC результата решения, который интегрирует результаты решения, полученные из чувствительных схем, пиксель за пикселем или для каждой группы пикселей, множество раз для генерирования отображаемых данных с градацией, причем блок IC результата решения включает в себя схему подсчета, которая выполняет обработку подсчета для интегрирования результатов решения, полученных из чувствительных схем, и запоминающее устройство, предназначенное для сохранения результата подсчета для каждого пикселя из схемы подсчета, при этом множество чувствительных схем совместно используют схему подсчета для интегрирования результатов решения.

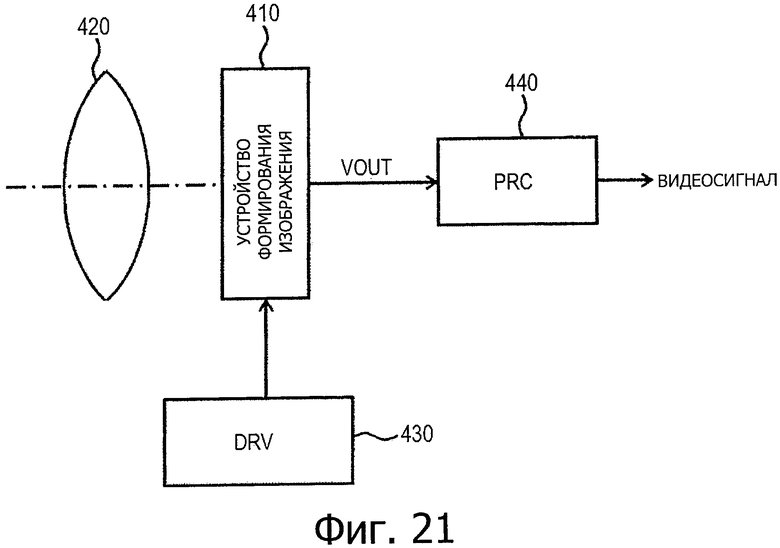

В соответствии с другим вариантом выполнения изобретения предусмотрена система камеры, имеющая устройство формирования изображения, оптическую систему, которая формирует изображение субъекта на устройстве формирования изображения, и схему обработки сигналов, которая обрабатывает выходной сигнал изображения из устройства формирования изображения, причем устройство формирования изображения включает в себя блок матрицы пикселей, имеющий массив пикселей, каждый из которых имеет устройство фотоэлектрического преобразования и выводит электрический сигнал в соответствии с входным фотоном, блок чувствительной схемы, имеющий множество схем датчика, каждая из которых выполняет двоичный выбор, поступил ли входной фотон в пиксель в заданный период после приема электрического сигнала от него, и блок IC результата решения, который интегрирует результаты решения, полученные из чувствительных схем, пиксель за пикселем или для каждой группы пикселей, множество раз для генерирования отображаемых данных с градацией, причем блок IC результата решения включает в себя схему подсчета, которая выполняет обработку подсчета, чтобы интегрировать решение, полученное из чувствительных схем, и запоминающее устройство, предназначенное для сохранения результата подсчета для каждого пикселя из схемы подсчета, причем множество чувствительных схем совместно используют схему подсчета для интегрирования результатов решения.

Варианты выполнения изобретения позволяют исключить обработку аналоговых сигналов, чтобы устранить шум в схеме, возникающий в AD преобразователе и при обработке аналоговых сигналов, без уменьшения числа диафрагмы пикселей, таким образом улучшая рабочую характеристика формирования изображения при низких затратах.

Также возможно оптимизировать установку экспозиции, когда используется подсчет фотонов с разделением времени.

Краткое описание чертежей

На фиг.1 показана схема, представляющая типичную конфигурацию микросхемы датчика изображения CMOS, который является твердотельным устройством формирования изображения;

на фиг.2 показана концептуальная схема, представляющая датчик изображения CMOS, у которого есть многослойная структура AD преобразователей и пикселей;

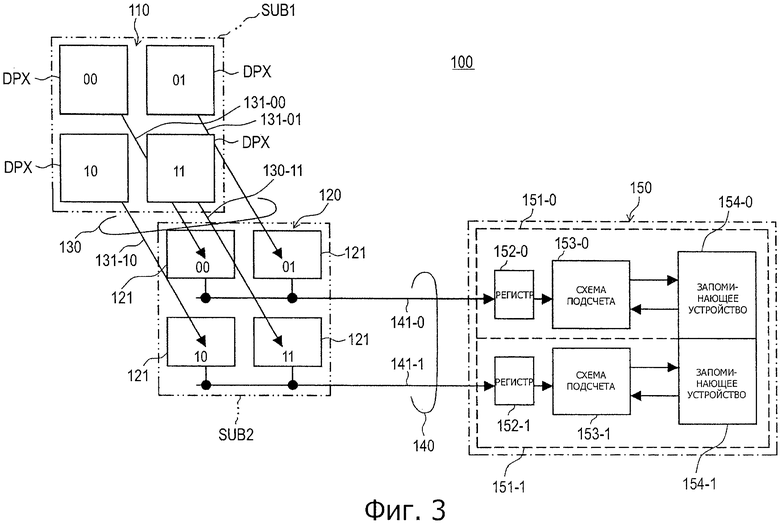

на фиг.3 показана схема, представляющая пример конфигурации датчика изображения CMOS (устройство формирования изображения) в соответствии с первым вариантом выполнения настоящего изобретения;

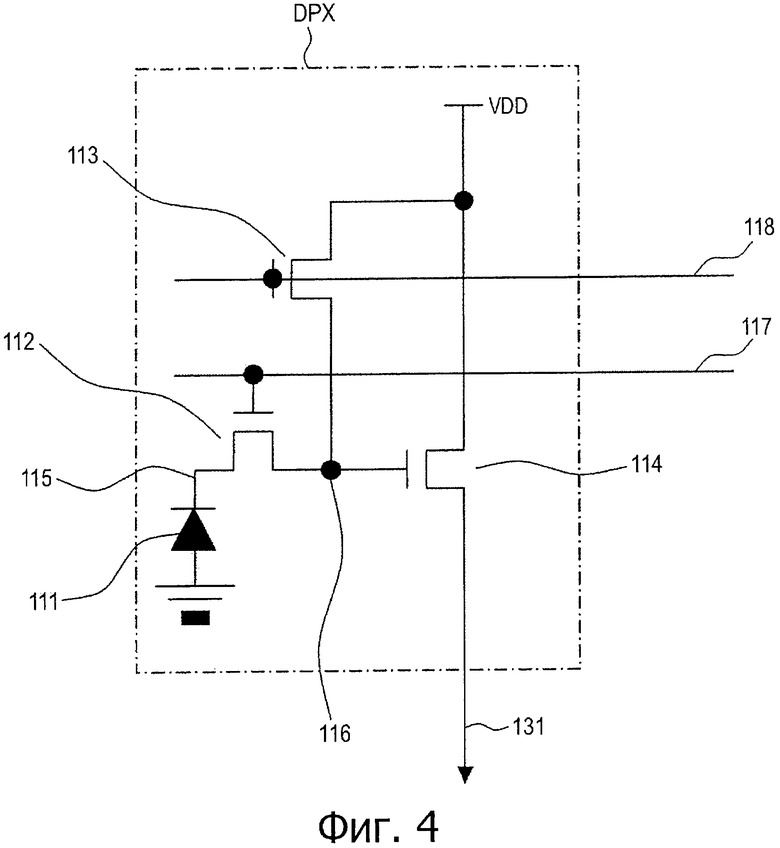

на фиг.4 показана схема, представляющая один пример конфигурации схемы пикселя в соответствии с первым вариантом выполнения;

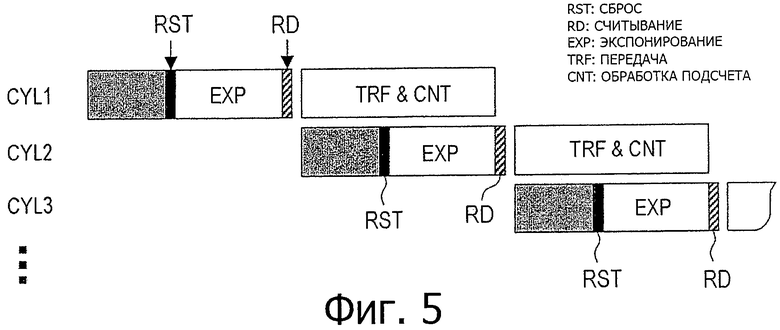

на фиг.5 показана схема, иллюстрирующая первый пример процедур доступа в соответствии с первым вариантом выполнения;

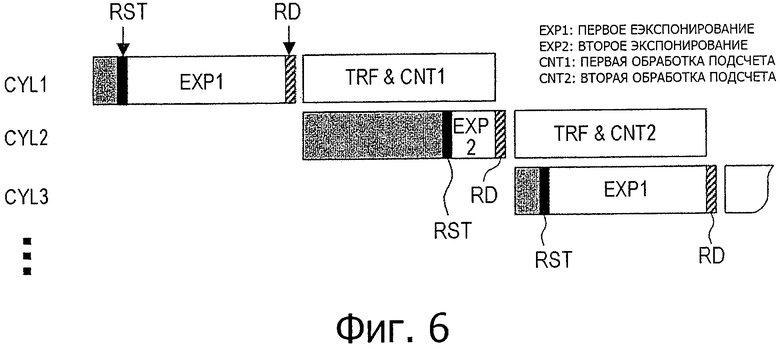

на фиг.6 показана схема, иллюстрирующая второй пример процедур доступа в соответствии с первым вариантом выполнения;

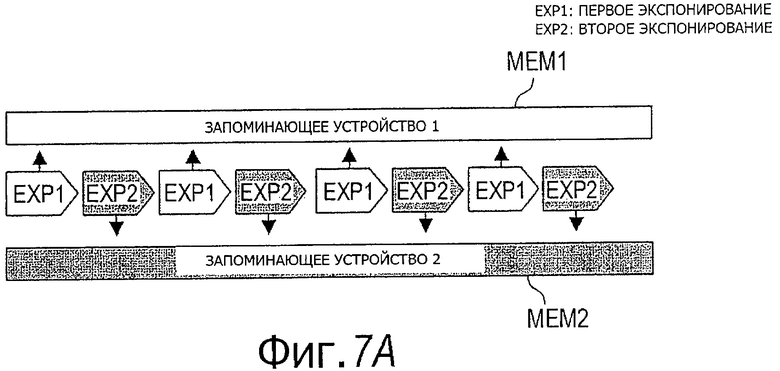

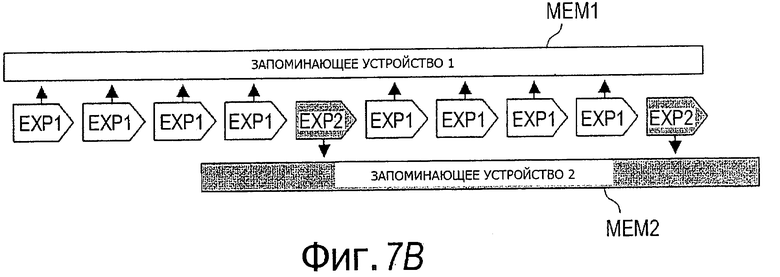

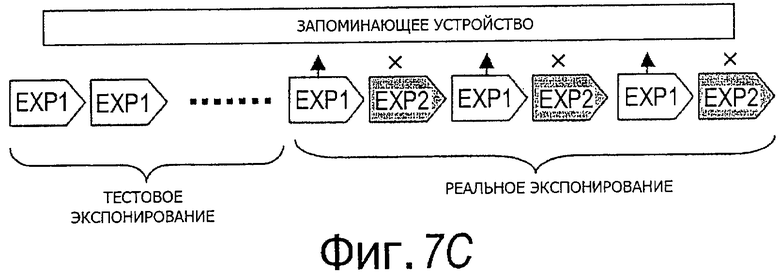

на фиг.7А-7С представлены схемы, иллюстрирующие более конкретные примеры процедур доступа на фиг.6;

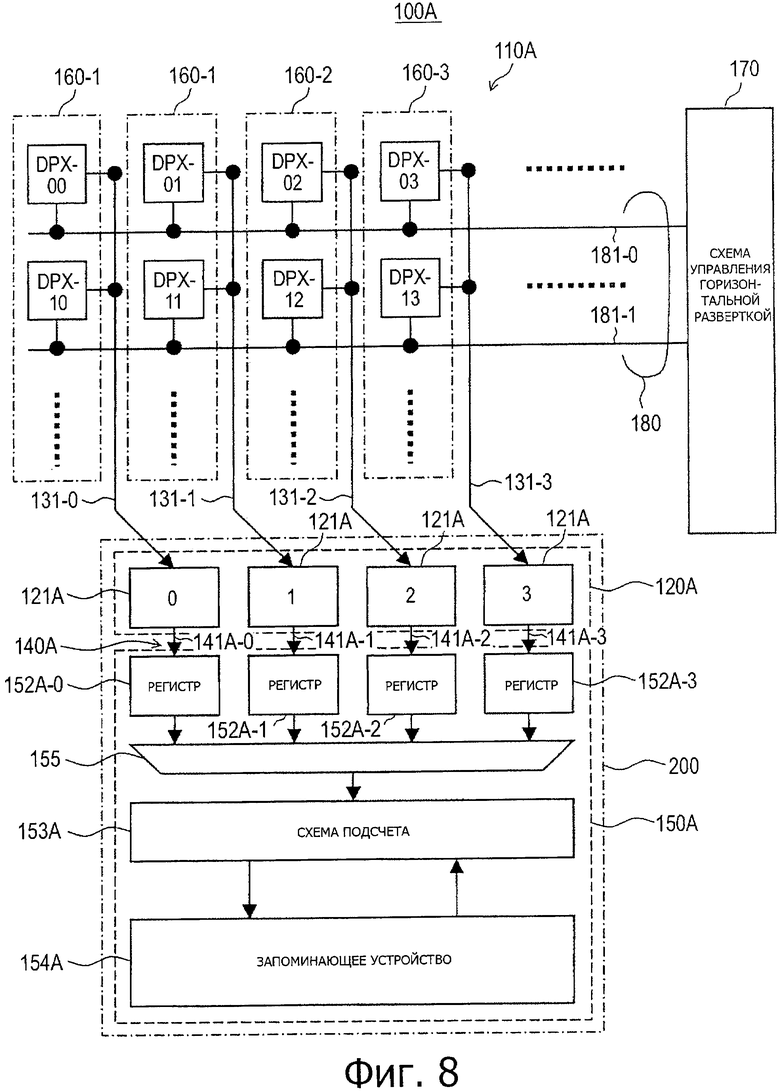

на фиг.8 показана схема, представляющая пример конфигурации датчика изображения CMOS (устройство формирования изображения) в соответствии со вторым вариантом выполнения изобретения;

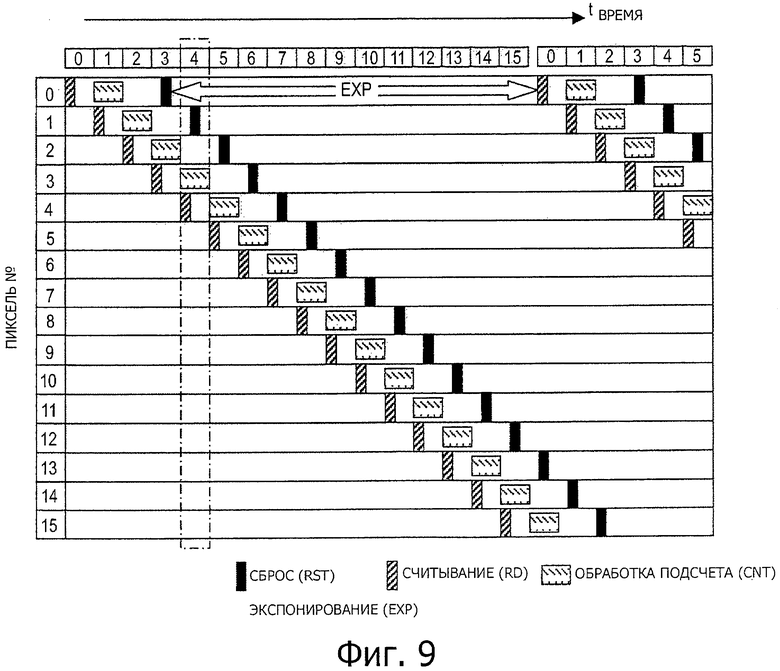

на фиг.9 показана схема для пояснения циклического доступа к блокам пикселей в соответствии со вторым вариантом выполнения;

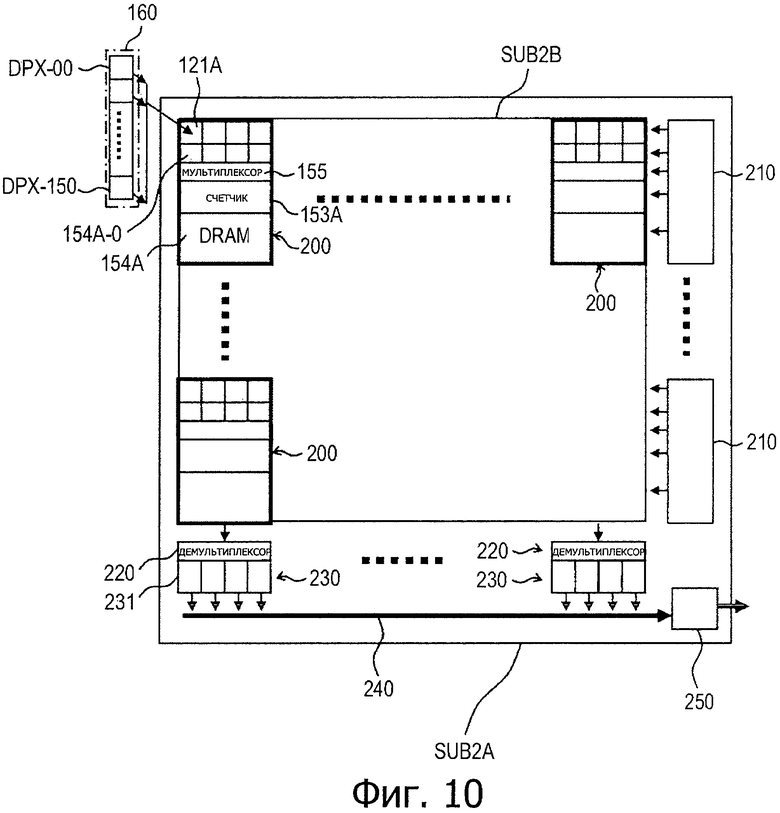

на фиг.10 показана схема, представляющая общее изображение микросхемы в соответствии со вторым вариантом выполнения, показанным на фиг.8;

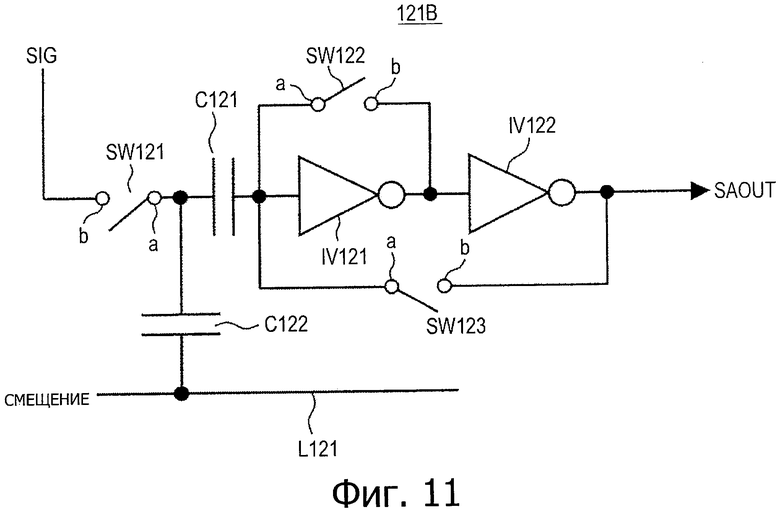

на фиг.11 показана принципиальная схема, представляющая один пример чувствительной схемы, имеющей функцию самообращения;

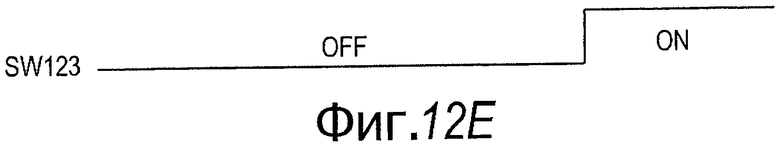

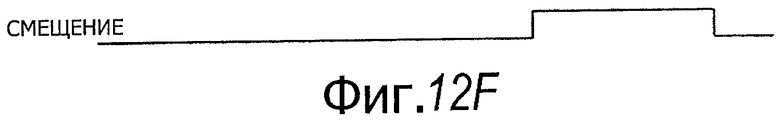

на фиг.12А-12F представлена временная диаграмма для пояснения примера операции считывания с использованием чувствительной схемы с функцией самообращения по фиг.11 со ссылкой на пиксель по фиг.4 в качестве примера;

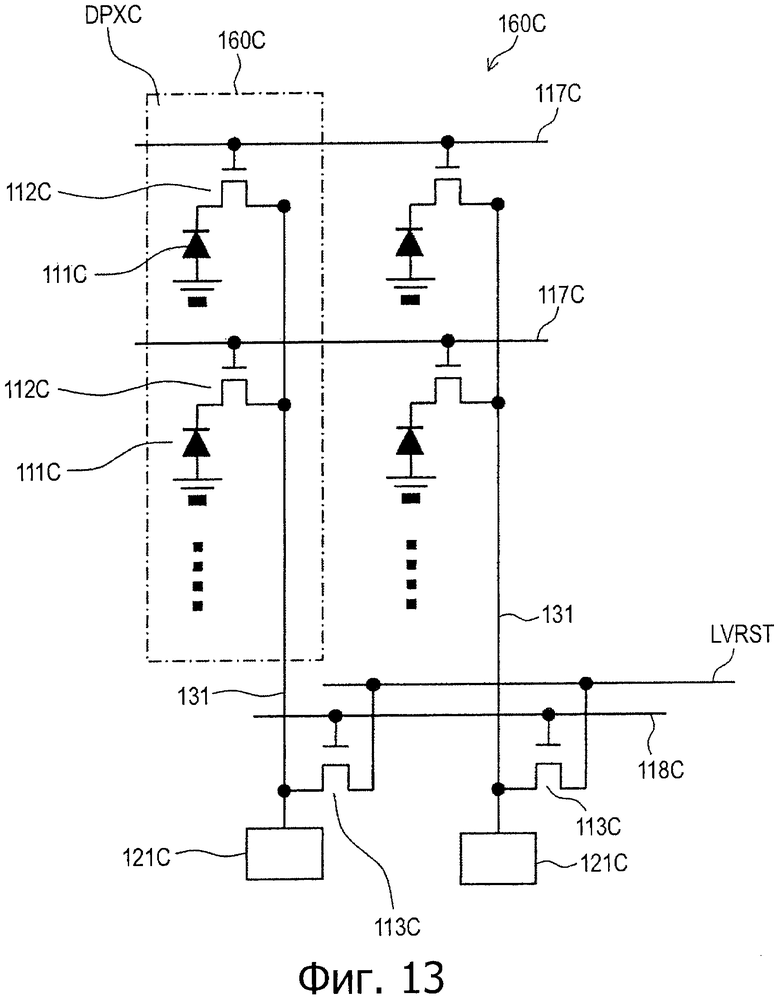

на фиг.13 показана схема, представляющая пример конфигурации блока пикселя, соответствующего второму варианту выполнения с использованием диода с внутренним усилением;

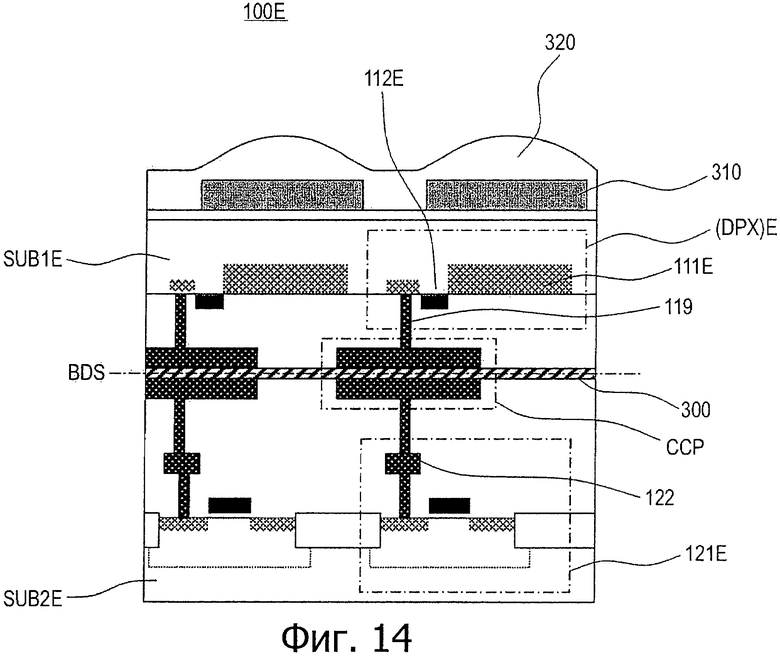

на фиг.14 показана схема, представляющая один пример поперечного сечения датчика изображения CMOS, в котором используется структура соединения на основе емкостной связи через конденсатор;

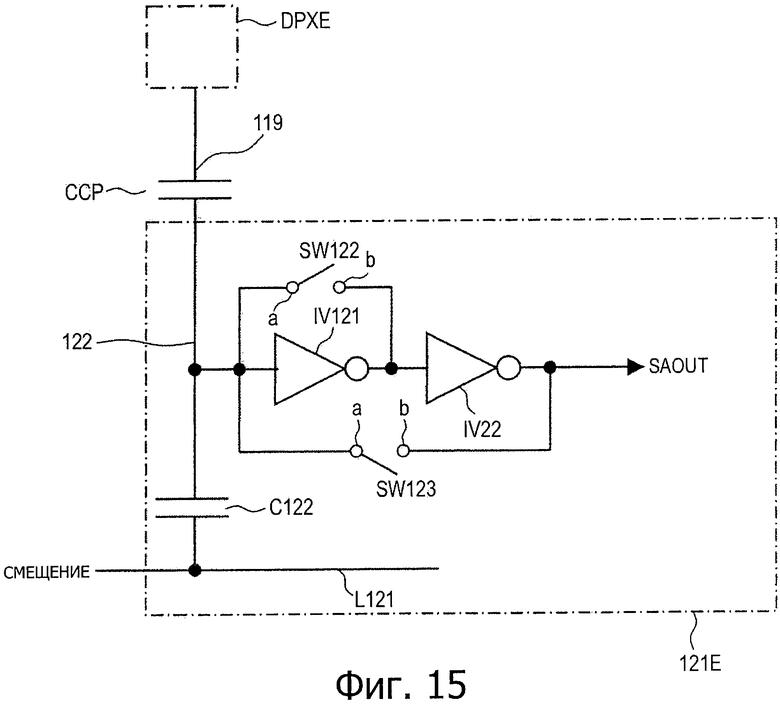

на фиг.15 показана схема, представляющая один пример чувствительной схемы с функцией самообращения в датчике изображения CMOS, в котором используется структура соединения на основе емкостной связи через конденсатор;

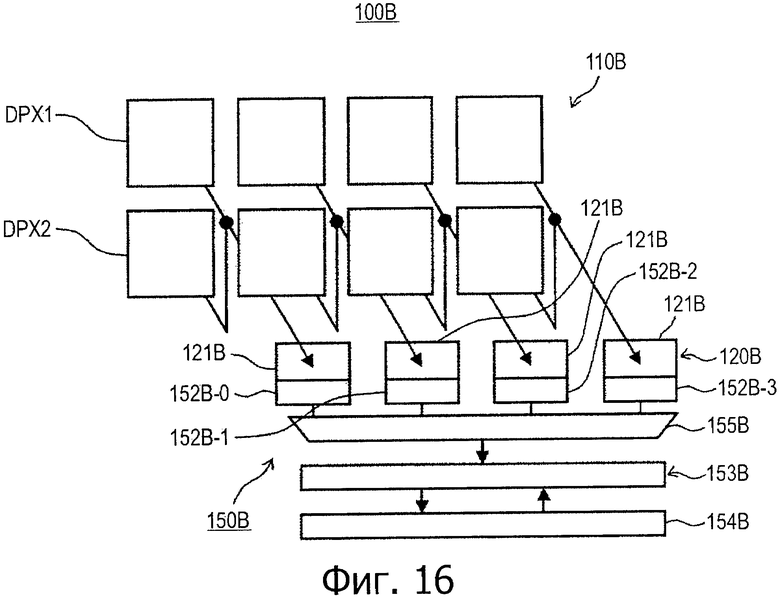

на фиг.16 показана схема, представляющая пример конфигурации датчика изображения CMOS (устройство формирования изображения) в соответствии с третьим вариантом выполнения изобретения;

на фиг.17 показана схема, иллюстрирующая поток обработки отображаемых данных при высокой освещенности в схеме на фиг.16;

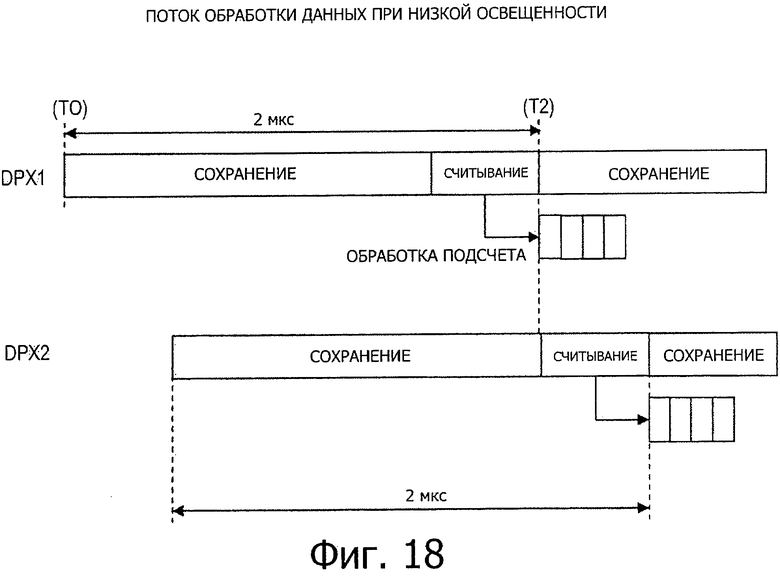

на фиг.18 показана схема, иллюстрирующая поток обработки отображаемых данных при малой освещенности в схеме на фиг.16;

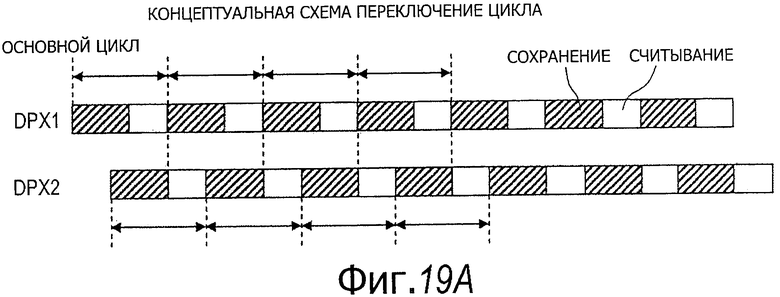

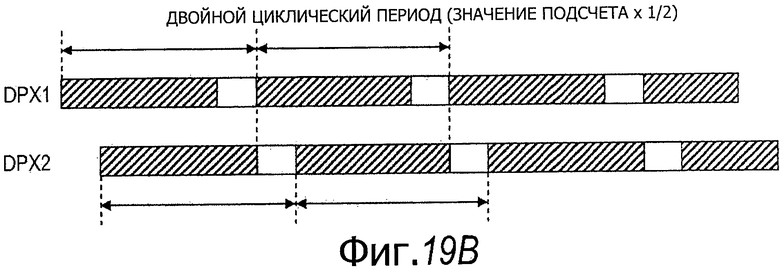

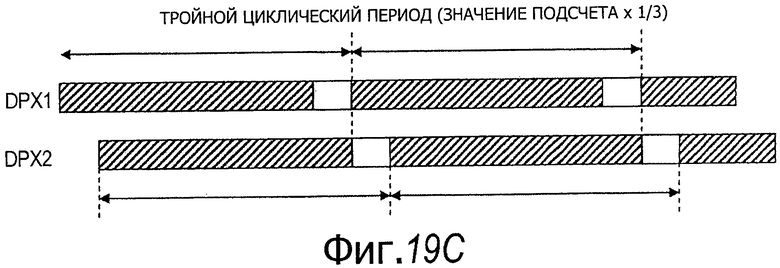

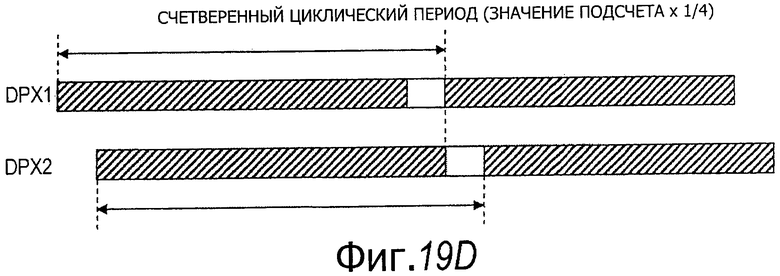

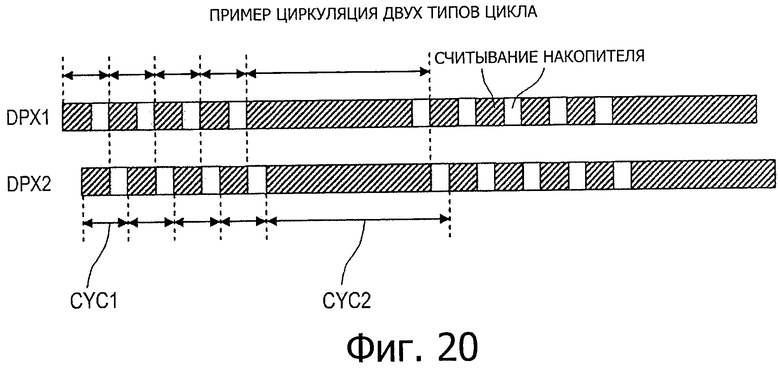

на фиг.19А к 19D показаны схемы, представляющие концепцию переключения цикла в третьем варианте выполнения;

на фиг.20 показана схема, представляющая пример, в котором динамический диапазон формирования изображения улучшен путем циклического выполнения расчета с комбинацией длительного периода цикла и короткого периода цикла; и

на фиг.21 показана схема, представляющая один пример конфигурации системы камеры, для которой адаптировано твердотельное устройство формирования изображения в соответствии с четвертым вариантом выполнения изобретения.

Подробное описание изобретения

Предпочтительные варианты воплощения настоящего изобретение будут описаны ниже со ссылкой на прилагаемые чертежи.

Описание будет приведено в следующем порядке.

1. Общие свойства устройства формирования изображения в соответствии с вариантом выполнения изобретения

2. Первый вариант выполнения (первый пример конфигурации устройства формирования изображения)

3. Второй вариант выполнения (второй пример конфигурации устройства формирования изображения)

4. Третий вариант выполнения (третий пример конфигурации устройства формирования изображения)

5. Четвертый вариант выполнения (система камеры)

<1. Общие свойства устройства формирования изображения в соответствии с вариантом выполнения изобретения>

С точки зрения быстрого параллельного считывания вариант выполнения изобретения реализует оптимальную конфигурацию устройства формирования изображения (датчик изображения CMOS) как полностью цифровой датчик изображения, в котором используется подсчет фотонов.

Во-первых, каждый пиксель выводит электрический сигнал, представляющий присутствие/отсутствие входного фотона, в пределах определенного периода. Чувствительная схема многократно принимает результат присутствия/отсутствия входного фотона за один период кадра и делает двоичный выбор для каждого результата. Устройство формирования изображения генерирует данные градации для каждого пикселя путем интеграции результатов этого решения.

На основе этой базовой конфигурации устройство формирования изображения в соответствии с режимом имеет следующие характерные структуры.

Первая характерная структура представляет собой соединенные слои пикселей и чувствительных схем, в которых используются разные полупроводниковые подложки. Пиксели и чувствительные схемы, соответственно, сформированы в виде массивов, которые соединены в виде многослойной структуры для реализации быстрого параллельного считывания без потери числа диафрагмы.

Вторая характерная структура представляет собой иерархическую компоновку множества чувствительных схем и схемы подсчета для интегрирования результатов решения так, что чувствительные схемы совместно используют схему подсчета. Совместное использование схемы подсчета множеством чувствительных схем может гарантировать гибкую оптимизацию размеров схемы и скорости обработки.

Третья характерная структура представляет собой функцию коррекции времени экспонирования путем изменения времени сброса. Время экспонирования регулируют путем изменения времени сброса, а не времени считывания, таким образом реализуя гибкий конвейер для последующей обработки передачи данных.

Четвертая характерная структура представляет собой иерархическую компоновку пикселей, чувствительных схем и схемы подсчета. Совместное использование чувствительной схемы со множеством пикселей и циклический доступ позволяют работать с малыми пикселями при обеспечении время экспонирования. Кроме того, совместное использование схемы подсчета с множеством чувствительных схем может гарантировать гибкую оптимизацию масштаба схемы и производительности процесса.

Пятая характерная структура представляет собой восприятие с использованием функции самообращения, чтобы обеспечить возможность детектирования одного фотона для пикселя. Уровень сброса и уровень сигнала считывают из пикселя, и эти два уровня, один из которых суммируют со смещением, сравнивают друг с другом, чтобы выполнить двоичный выбор. Это взаимно уничтожает вариации уровня сброса от пикселя к пикселю.

Режим, в котором используются описанные выше структуры, позволяет получить устройство формирования изображения с возможностью подсчета фотонов, без потери числа диафрагмы пикселей, и позволяет полностью устранить случайный шум и фиксированный шум, возникающие при аналоговой обработке сигналов, и которые не были бы обычно неизбежны в датчиках изображения. В это время остаются только шумы фотосъемки и темновой ток для каждого пикселя, и, таким образом, достигается очень высокое отношение "сигнал-шум", которое гарантирует генерирование ясных изображений градации.

Поскольку чувствительные схемы или подобное могут быть размещены под пикселями и нет необходимости в сложной аналоговой схеме, микросхему, главным образом, занимает одна только матрица пикселей, что способствует снижению стоимости микросхемы.

Кроме того, динамический диапазон может быть значительно расширен без изменения пикселей при увеличении количества выборок для формирования одного кадра или выполнения операции осуществления выборки с разным комбинированным временем экспонирования.

Даже если пиксели и чувствительные схемы объединяют в виде многослойной структуры с использованием разных подложек, выходы пикселей в чувствительные схемы не обязательно должны иметь точность аналоговых выходов, поскольку импеданс проводников передачи сигнала и изменения паразитной емкости не влияют на шумы.

Кроме того, цифровое считывание с использованием функции самообращения значительно улучшает точность решения.

Далее описан датчик изображения CMOS как устройство формирования изображения в соответствии с режимом, обладающим упомянутыми выше особенностями.

<2. Первый вариант выполнения>

На фиг.3 показана схема, представляющая пример конфигурации датчика 100 изображения CMOS (устройство формирования изображения) в соответствии с первым вариантом выполнения изобретения.

[Схема общей конфигурации]

Датчик 100 изображения CMOS имеет блок 110 матрицы пикселей, блок 120 чувствительной схемы, группу линий 130 выходного сигнала, группу линий 140 передачи и блок 150 IC результата решения.

В блоке 110 матрицы пикселей содержится множество цифровых пикселей DPX, расположенных в форме матрицы в направлении строк и в направлении столбцов.

Каждый цифровой пиксель DPX имеет устройство фотоэлектрического преобразования и имеет функцию вывода электрического сигнала в соответствии с входным фотоном.

Блок 110 матрицы пикселей сформирован, например, на первой полупроводниковой подложке SUB1.

Блок 120 чувствительной схемы сформирован на второй полупроводниковой подложке SUB2, отличающейся от первой полупроводниковой подложки SUB1.

Блок 120 чувствительной схемы содержит множество чувствительных схем 121, расположенных, например, в форме матрицы в направлении строк и в направлении столбцов во взаимно-однозначном соответствии с матрицей пикселей DPX в блоке 110 матрицы пикселей.

У каждой чувствительной схемы 121 есть функция двоичного выбора, определяющая, поступил ли входной фотон в соответствующий цифровой пиксель DPX в течение заданного периода после приема сигнала от него.

Первая полупроводниковая подложка SUB1 и вторая полупроводниковая подложка SUB2 соединены слоями.

Например, соединение слоями выполняют таким способом, что множество пикселей DPX, сформированных на первой полупроводниковой подложке SUB1, обращены к множеству чувствительных схем 121, сформированных на второй полупроводниковой подложке SUB2 во взаимно-однозначном соответствии. Противоположный пиксель DPX и чувствительная схема 121 соединены каждой линией 131 выходного сигнала в группе линий 130 выходного сигнала.

В примере, показанном на фиг.3, выход пикселя DPX-00, расположенного в 0-ой строке и 0-ом столбце, соединен со входом чувствительной схемы 121-00, расположенной в 0-ой строке и 0-ом столбце, линией 131-00 выходного сигнала. Выход пикселя DPX-01, расположенного в 0-ой строке и первом столбце, соединен со входом чувствительной схемы 121-01, расположенный в 0-ой строке и первом столбце, линией 131-01 выходного сигнала.

Выход пикселя DPX-10, расположенного в первой строке и 0-ом столбце, соединен со входом чувствительной схемы 121-10, расположенной в первой строке и 0-ом столбце, линией 131-10 выходного сигнала. Выход пикселя DPX-11, расположенного в первой строке и первом столбце, соединен со входом чувствительной схемы 121-11, расположенной в первой строке и первом столбце, линией 131-11 выходного сигнала.

Пиксели и чувствительные схемы, расположенные в других строках и столбцах, соединены аналогично, хотя это не показано.

Выходы чувствительных схем 121 в блоке 120 чувствительной схемы, которые расположены в одной строке, соединены с общей линией 141 передачи.

В примере, показанном на фиг.3, выходы чувствительных схем 121-00, 121-01…, расположенных в 0-ой строке, соединены с линией 141-0 передачи.

Выходы чувствительных схем 121-10, 121-11…, расположенных в первой строке, соединены с линией 141-1 передачи. Аналогичное соединение выполнено для вторых и последующих строк, хотя это не показано.

Блок 150 IC результата решения имеет функцию многократного интегрирования результатов решения чувствительных схем 121 пиксель за пикселем для генерирования двумерных данных изображения с градацией.

Блок 150 IC результата решения имеет IC 151-0, 151-1… результата решения, ассоциированные с компоновкой строки чувствительных схем 121 в блоке 120 чувствительной схемы.

Другими словами, IC 151-0 результата решения соединена с линией 141-0 передачи, с которой соединены чувствительные схемы 121-00, 121-01…, расположенные в 0-ой строке.

IC 151-1 результата решения соединена с линией 141-1 передачи, с которой соединены чувствительные схемы 121-10, 121-11…, расположенные в первой строке.

В IC 151-0 результата решения имеется регистр 152-0, который содержит значение решения, переданное по линии 141-0 передачи, схему 153-0 подсчета, которая подсчитывает значение, содержащееся в регистре 152-0, и запоминающее устройство 154-0, которое содержит результат подсчета, полученный из схемы 153-0 подсчета.

В IC 151-1 результата решения есть регистр 152-1, который содержит значение решения, переданное по линии 141-1 передачи, схему 153-1 подсчета, которая подсчитывает значение, содержащее в регистре 152-1, и запоминающее устройство 154-1, которое содержит результат подсчета из схемы 153-1 подсчета.

В соответствии с вариантом выполнения схема 153-0 подсчета в IC 151-0 результата решения совместно используется множеством чувствительных схем 121-00, 121-01,…

Аналогично схема 153-1 подсчета в IC 151-1 результата решения совместно используется множеством чувствительных схем 121-10, 121-11,…

[Функция цифрового пикселя]

Как упомянуто выше, цифровой пиксель (который ниже может просто называться "пикселем") DPX имеет устройство фотоэлектрического преобразования и выводит электрический сигнал в соответствии с входным фотоном.

Датчик 100 изображения CMOS, как устройство формирования изображения, имеет функцию сброса пикселей DPX и функцию считывания сигналов из них и может выполнять функцию сброса и функцию считывания в произвольные моменты времени.

Функция сброса сбрасывает пиксель DPX в состояние, в котором фотон не поступает на вход. У каждого пикселя DPX, предпочтительно, есть линза и цветной фильтр на его поверхности приема света.

Такие основные функции пикселя аналогичны нормальному пикселю, за исключением того, что на выходе пикселя DPX не требуются точность и линейность аналогового значения.

Один пример конфигурации цифрового пикселя будет описан ниже.

На фиг.4 показана схема, представляющая один пример конфигурации схемы пикселя в соответствии с вариантом выполнения.

На фиг.4 показан один пример схемы пикселя, включающей в себя три транзистора.

В одиночном пикселе DPX пикселя DPX есть фотодиод 111, транзистор 112 передачи, транзистор 113 сброса, транзистор 114 усилителя, узел 115 накопителя и узел 116 плавающей диффузионной (FD) области.

Электрод затвора транзистора 112 передачи соединен с линией 117 передачи, и электрод затвора транзистора 113 сброса соединен с линией 118 сброса.

У транзистора 114 усилителя есть электрод затвора, соединенный с узлом 116 FD, и электрод истока, подключенный к линии 131 выходного сигнала.

В единичном пикселе DPX поступающий на кремниевую подложку для пикселей свет генерирует пару из электрона и дырки, при этом электрон содержится в узле 115 накопителя фотодиодом 111.

Когда транзистор 112 передачи открывают в определенный момент времени, эти электроны передают в узел 116 FD для управления затвором транзистора 114 усилителя.

В результате сигнальный заряд становится сигналом в линии 131 выходного сигнала, и его считывают.

Линия 131 выходного сигнала может быть заземлена через источник постоянного тока или элемент резистора для выполнения операции истокового повторителя, или может быть временно заземлена перед считыванием и затем переведена в плавающее состояние для вывода уровня заряда установленного транзистором 114 усилителя.

Транзистор 113 сброса открывается параллельно и одновременно с транзистором 112 передачи для вытягивания электронов, содержащихся в фотодиоде 111, в источник питания так, чтобы пиксель был сброшен в темновое состояние перед состоянием накопления электронов, то есть в состояние, в котором фотон не поступает.

Такая схема и механизм работы пикселей аналогичны аналоговому пикселю и также как и в аналоговом пикселе могут иметь различные виды изменений.

Однако в то время как аналоговый пиксель выводит как аналоговый сигнал общую сумму входных фотонов, цифровой пиксель выводит в цифровой форме присутствие/отсутствие одиночного входного фотона.

Поэтому принципы проектирования аналогового пикселя и цифрового пикселя отличаются друг от друга.

Во-первых, цифровой пиксель должен генерировать достаточно большой электрический сигнал для одиночного входного фотона.

В схеме пикселя с усилителем на транзисторе, как показано, например, на фиг.4, желательно сделать как можно меньшей паразитную емкость во входном узле 116 транзистора 114 усилителя, который составляет истоковый повторитель.

Желательно поддерживать амплитуду выходного сигнала относительно одиночного входного фотона существенно большей, чем случайные шумы транзистора 114 усилителя.

Поскольку выходной сигнал цифрового пикселя не нуждается в точности, линейности и диапазоне работы аналогового пикселя, можно использовать низкое напряжение, аналогичное требуемому для цифровой схемы, для источника питания входа-выхода истокового повторителя. Кроме того, фотодиод, возможно, должен иметь минимальную емкость накопления заряда.

Датчик 100 изображения CMOS в соответствии с вариантом выполнения выполнен с возможностью иметь упомянутые выше первую, вторую и третью характерные структуры следующим образом.

У датчика 100 изображения CMOS есть блок 110 матрицы пикселей и блок 120 чувствительной схемы, соединенные как многослойная структура, с использованием разных полупроводниковых подложек. Датчик 100 изображения CMOS выполнен таким образом, что пиксели и чувствительные схемы, соответственно, сформированы в виде массивов, которые соединяют в виде многослойной структуры для реализации быстрого параллельного считывания без потери числа диафрагмы.

Датчик 100 изображения CMOS выполнен таким образом, что множество чувствительных схем совместно используют схему подсчета, чтобы обеспечить гибкую оптимизацию размеров схемы и производительность процесса.

Датчик 100 изображения CMOS выполнен таким образом, что он имеет функцию коррекции времени экспонирования путем изменения времени сброса. Время экспонирования регулируют при изменении времени сброса, а не времени считывания, таким образом реализуется гибкий конвейер для последующей обработки передачи.

Далее будет описана общая схема работы датчика 100 изображения CMOS в соответствии с первым вариантом выполнения.

Например, сброс всех пикселей DPX выполняют одновременно, и сигналы считывают из них одновременно после заданного времени экспонирования.

Присутствие/отсутствие входного фотона в каждом пикселе DPX в пределах периода экспонирования выводят как электрический сигнал в линию 131 выходного сигнала и подвергают двоичному выбору в соответствующей чувствительной схеме 121.

Чувствительная схема 121 устанавливает "1" как значение решения, когда фотон поступает в выбранный пиксель, и устанавливает "0" как значение решения, когда фотон не поступает в выбранный пиксель, и фиксирует значение решения.

Таким образом, поскольку выходной сигнал от пикселя DPX подвергается двоичному выбору как цифровой сигнал в соответствии с вариантом выполнения, в отличие от нормальной конфигурации, показанной на фиг.2, AD преобразователь здесь не используется. Кроме того, скорость принятия решения значительно выше, чем у AD преобразователя.

Значение решения, установленное и фиксированное чувствительной схемой 121, последовательно передают в регистр 152, предусмотренный для каждой строки, через линию 141 передачи и подвергают обработке подсчета, используя схему 153 подсчета.

Передача может быть выполнена при последовательном соединении отдельных чувствительных схем с общей линией переключателями, как показано на фиг.1, или может быть достигнута при использовании сдвигового регистра.

При обработке подсчета, выполняемой схемой 153 подсчета, во-первых, данные пикселя, считанные ранее, загружают в схему 153 подсчета из запоминающего устройства 154.

Когда в регистре 152 содержится "1", "1" добавляют к значению подсчета, и когда в регистре 152 содержится "0", значение подсчета не обновляют.

После этого значение схемы 153 подсчета снова записывают в запоминающее устройство 154, и на этом обработка подсчета для одного пикселя заканчивается.

Такая обработка последовательно выполняется для одной строки пикселей. В то время как выполняется такая обработка подсчета, в пикселях DPX выполняют последующий сброс и экспонирование.

Такое цифровое считывание выполняют, например, 1023 раза за один период кадра, и общее значение подсчета входных фотонов для каждого пикселя DPX становится равным 0 или больше, и 1023 или меньше.

Соответственно, 10-битовые данные градации генерируют пиксель за пикселем.

Таким образом, датчик 100 изображения CMOS работает как матрица счетчика фотонов с уникальной конфигурацией.

Как упомянуто выше, отдельные пиксели DPX расположены на другой полупроводниковой подложке, на опорной схеме, которая включает в себя ассоциированные чувствительные схемы 121.

Пиксели DPX и чувствительные схемы 121 расположены в виде матриц на соответствующих полупроводниковых подложках. Например, пиксели DPX и чувствительные схемы 121, соответственно, сформированы на отдельных полупроводниковых подложках, которые, в свою очередь, склеивают вместе для получения многослойной структуры из полупроводниковых подложек.

Кроме того, желательно, чтобы были сформированы, по меньшей мере, некоторые схемы управления для пикселей DPX, для которых должен быть выполнен сброс или которые должны быть подвергнуты считыванию данных на той же первой полупроводниковой подложке SUB1, что и пиксели DPX.

Эта конфигурация может гарантировать быстродействующий доступ к пикселю и быстрое параллельное выполнение расчетов так, чтобы упомянутое выше множественное получение данных могло быть выполнено за один период кадра.

Например, отдельные пиксели выполняют сброс и считывание одновременно, и передачу данных и подсчет выполняют в отдельных строках одновременно.

[Процедуры доступа]

Далее будут описаны процедуры доступа в соответствии с вариантом выполнения.

На фиг.5 показана схема, иллюстрирующая первый пример процедуры доступа в соответствии с первым вариантом выполнения.

На фиг.5 RST представляет сброс, ЕХР представляет экспонирование, и RD представляет считывание. Кроме того, TRF представляет обработку передачи и CNT представляет обработку подсчета.

В примере, показанном на фиг.5, когда один период кадра составляет, например, 1/30 секунды, в течение которой считывание выполняют 1023 раза, один цикл считывания RD составляет приблизительно 32 микросекунды.

В этот период выполняют сброс RST и считывание RD в пикселях DPX, и длительность от сброса RST и считывания RD составляет период ЕХР экспонирования.

Значение решения, которое было фиксировано в чувствительной схеме 121 в ходе считывания RD, передают в регистр 152 для подсчета, и в это время выполняют в конвейере экспонирование ЕХР и импульс TRF передачи, и обработку CNT подсчета.

Таким образом, в то время как значение решения, которое было фиксировано в чувствительных схемах 121 в цикле CYL1, передают в направлении строки и последовательно подсчитывают, пиксели подвергаются сбросу RST в цикле CYL2, и инициализируют экспонирование ЕХР.

У датчика 100 изображения CMOS есть функция регулирования, состоящая в управлении эффективным временем экспонирования для регулирования чувствительности при изменении сброса RST и при сохранении постоянного периода цикла.

Например, хотя два или больше фотона могут быть введены в период экспонирования при формировании изображения яркого субъекта, все они учитываются как одиночный фотон, что приводит к неполной регистрации.

В таком случае момент времени сброса следует устанавливать ближе к моменту времени считывания, чтобы сократить время экспонирования, таким образом понижая чувствительность. Это позволяет легко регулировать чувствительность во время формирования изображения, не влияя на другие операции схемы.

Система формирования изображения, например, усредняет значения подсчета всех эффективных пикселей и изменяет момент времени сброса устройства формирования изображения, чтобы сократить время экспонирования, когда среднее значение подсчета превышает заданное значение. С другой стороны, когда среднее значение подсчета меньше, чем заданное значение, система формирования изображения удлиняет время экспонирования.

Легко установить такую функцию, чтобы оптимальное время экспонирования могло быть установлено автоматически при использовании алгоритма двоичного поиска или подобного.

Когда имеется большое количество пикселей, горизонтальная передача и обработка подсчета должны быть выполнены в высокой скоростью, которая может однако быть снижена при выполнении передачи каждой строки в множестве каналов, используя множество счетчиков.

Хотя желательно сформировать схемы 153 подсчета и запоминающее устройства 154 на той же самой подложке, на которой сформированы чувствительные схемы 121 блока 120 чувствительной схемы, они могут быть расположены в виде многослойной структуры с третьей полупроводниковой подложкой под блоком 120 чувствительной схемы.

С учетом, например, потребления энергии и выступа характеристики блок 110 матрицы пикселей может быть разделен на множество блоков пикселя так, чтобы операция считывания пикселя и операция передачи для каждой строки выполнялись блок за блоком.

Хотя выборку выполняют 1023 раза, чтобы сгенерировать 10-битовую градацию в предшествующем варианте выполнения, динамический диапазон может быть увеличен при увеличении числа действий выборки, без изменения пикселей.

Когда количество выборок определено, например, как 16383, что приблизительно в 16 раз больше упомянутого количества, один цикл составляет 2 микросекунды.

Если этот период цикла полностью используется для экспонирования, количество фотонов в режиме малой освещенности может быть считано таким же образом, как обычно, и количество фотонов в режиме высокой освещенности также быть считано точно до 16-кратного количества фотонов в нормальном режиме. Эти количества выражаются как 14-битовые данные градации.

В качестве альтернативы динамический диапазон может быть эффективно улучшен при приобретении данных с другими типами предусмотренных периодов экспонирования.

На фиг.6 показана схема, иллюстрирующая второй пример процедур доступа в соответствии с первым вариантом выполнения.

На фиг.6 показан пример, где процедуры доступа на фиг.5 дополнительно развиты.

В этом примере момент времени сброса изменяют, чтобы обеспечить два периода экспонирования, первое экспонирование ЕХР1 и второе экспонирование ЕХР2, которые поочередно повторяют для получения данных.

Развитое использование такой технологии гарантирует формирование изображения в широком динамическом диапазоне при меньшем количестве действий выборки, что позволяет уменьшить нагрузку на систему.

На фиг.7А-7С представлены схемы, иллюстрирующие более конкретные примеры процедур доступа по фиг.6.

В каждом из конкретных примеров на фиг.7А-7С предполагается, что время экспонирования при первом экспонировании ЕХР1 в восемь раз больше, чем при втором экспонировании ЕХР2.

В примере, показанном на фиг.7А, сбор данных при каждом первом экспонировании ЕХР1 и втором экспонировании ЕХР2 выполняют 511 раз, и данные отдельно считывают и сохраняют в двух запоминающих устройствах, первом запоминающем устройстве МЕМ1 и втором запоминающем устройстве МЕМ2. 511 подсчетов обеспечивают 9-битовую градацию.

При этом считается, что интенсивный свет поступает на вход пикселя, величина подсчета которого при первом экспонировании ЕХР1 превышает заданное значение таким образом, что в этом случае используют величину подсчета при втором экспонировании ЕХР2.

В этом случае выход установлен, например, с 12-битовой градацией, и выход пикселя, для которого используется значение подсчета при втором экспонировании ЕХР2, сдвигают на три бита, увеличивая его в восемь раз.

В качестве альтернативы выход может быть структурирован так, чтобы иметь 9-битовую градацию и 1-битовый флаг, обозначающий выбор экспонирования, чтобы сократить количество выходных битов.

В примере, показанном на фиг.7 В, чтобы повысить чувствительность формирования изображения темного субъекта, количество полученных данных при длительном экспонировании определяют большим, чем количество полученных данных при коротком экспонировании.

Например, одно получение данных при втором экспонировании ЕХР2 неоднократно вставляют, например, для каждых четырех полученных данных при первом экспонировании ЕХР1. Соответственно, данные получают 1023 раза при первом экспонировании ЕХР1 и 255 раз при втором экспонировании ЕХР2.

Когда подсчет при втором экспонировании, ЕХР2 используется как выход, выход сдвигают, например на пять битов, делая его в 32 раза большим, как выход с учетом количества экспонирований.

В это время у выхода может быть максимум 13-битовая градация. В качестве альтернативы выход может быть структурирован так, чтобы иметь 10-битовую градацию и 1-битовый флаг, обозначающий выбор экспонирования.

В примере, показанном на фиг.7С, чтобы сэкономить память, тестовые данные получают сначала 127 раз при первом экспонировании ЕХР1, и затем данные получают 512 раз поочередно при каждом первом экспонировании ЕХР1 и втором экспонировании ЕХР2.

Пиксель, значение подсчета которого при первом экспонировании ЕХР1 превышает заданное значение при первых 127 получениях данных, рассматривают как пиксель с интенсивной подачей света, в связи с чем устанавливают флаг. Когда получение тестовых данных заканчивается, значение подсчета в запоминающем устройстве очищают один раз, за исключением флага. Для пикселя с установленным флагом подсчитывают данные только при втором экспонировании ЕХР2, и после этого содержат их в запоминающем устройстве.

Для пикселя, в котором флаг не установлен, подсчитывают данные только при первом экспонировании, ЕХР1, и содержат их в запоминающем устройстве. Запоминающее устройство, которое необходимо для операции подсчета в пикселе, представляет собой одно 10-битовое запоминающее устройство, которое содержит флаг в дополнение к 9-битовой градации.

Следует отметить, что, когда выбирают первое экспонирование ЕХР1, градация запоминающего устройства может быть увеличена после теста, вместо очистки запоминающего устройства.

Множество наборов периодов экспонирования предусматривают при изменении времени сброса, и данные многократно считывают за каждый период экспонирования, чтобы генерировать отображаемые данные, используя описанный выше подход, что позволяет выполнить формирование изображения в широком динамическом диапазоне, который обеспечивает возможность обработки субъекта с высоким контрастом, который включает в себя как яркую часть, так и темную часть.

Хотя в предшествующем примере используются два типа периодов экспонирования, три или больше типа периодов экспонирования могут использоваться, чтобы обеспечить различные модификации алгоритма синтеза.

Желательно синтезировать отображаемые данные с количеством входных фотонов за короткий период экспонирования, который в основном используется для пикселя с высокой освещенностью, в то время как количество входных фотонов за длительный период экспонирования обычно используется для пикселя с низкой освещенностью. В качестве альтернативы значения подсчета могут быть выведены для множества типов экспонирования, и синтез данных может быть выполнен во время обработки изображения, используя микросхему DSP или тому подобное, расположенную в следующем каскаде.

Хотя синтез отображаемых данных с различными значениями времени экспонирования частично выполняется существующим датчиком изображения, сбор данных при двух типах времени экспонирования выполняют в интервале одного времени кадра, в результате чего возникает такая проблема как раскрашивание движущегося субъекта в неестественные цвета.

В существующей схеме поочередного многократного получения обоих типов данных за один период кадра такая проблема не возникает.

В более общем случае желательно, чтобы был многократно выполнен сбор данных с циклическими временами экспонирования, и получаемые результаты должны быть синтезированы для генерирования данных изображения.

<3. Второй вариант выполнения>

На фиг.8 показана схема, представляющая пример конфигурации датчика изображения CMOS (устройство формирования изображения) в соответствии со вторым вариантом выполнения изобретения.

В датчике 100 изображения CMOS в соответствии с первым вариантом выполнения отдельные пиксели DPX соответствуют чувствительным схемам 121 во взаимно однозначном соответствии.

Однако промежутки, требуемые для пикселей DPX и чувствительной схемы 121, не обязательно должны быть одинаковыми.

Кроме того, в многослойной структуре из двух подложек схемы подсчета и запоминающее устройства, которые являются большими по размерам, могут быть расположены вне области матрицы пикселей, для которой существенной является быстрая передача данных на большое расстояние из каждой чувствительной схемы 121, и, вероятно, будет ограничены компоновкой.

Датчик 100А изображения CMOS в соответствии со вторым вариантом выполнения обеспечивает гибкое решение описанной выше задачи, обеспечивая возможность для множества пикселей совместно использовать одну чувствительную схему.

В датчике 100А изображения CMOS, в блоке 110А матрицы пикселей имеется множество пикселей DPX, расположенных в матричной форме в направлении строки и в направлении столбца.

Множество пикселей DPX в одном столбце и схема выбора формируют блок 160-0, 160-1, 160-2, 160-3… пикселей.

Датчик 100А изображения CMOS включает в себя схему 170 управления горизонтальной разверткой и линии 180 управления строки, предназначенные для управления пикселями DPX в блоке 110А матрицы пикселей для вывода электрических сигналов пикселей DPX в выходные линии 131 сигнала.

Датчик 100А изображения CMOS включает в себя блок схемы 200, который выполняет двоичный выбор по электрическим сигналам, переданным через выходные линии 131 сигнала, и многократно интегрирует результаты решения, пиксель за пикселем, для генерирования двумерных отображаемых данных с градацией.

В блоке 200 схемы есть блок 120А чувствительной схемы и в нем предусмотрен блок 150А IC результата решения.

В блоке 120А чувствительной схемы есть чувствительные схемы 121-0, 121-1, 121-2, 121-3…, расположенные в соответствии с блоками 160-0, 160-1, 160-2, 160-3… пикселей.

У чувствительной схемы 121-0 есть свой вход, соединенный с линией 131-0 выходного сигнала, с которым совместно соединены выходы всех пикселей DPX-00, DPX-10…, DPX-150, формирующие блок 160-0 пикселей.

Таким образом, пиксели DPX-00, DPX-10…, DPX-150 совместно используют одну чувствительную схему 121-0.

Вход чувствительной схемы 121-1 соединен с линией 131-1 выходного сигнала, с которой совместно соединены выходы всех пикселей DPX-01, DPX-11…, DPX-151, формирующие блок 160-1 пикселей.

Таким образом, пиксели DPX-01, DPX-11…, DPX-151 совместно используют одну чувствительную схему 121-1.

Вход чувствительной схемы 121-2 соединен с линией 131-2 выходного сигнала, с которой совместно соединены выходы всех пикселей DPX-02, DPX-12…, DPX-152, формирующие блок 160-2 пикселей.

Таким образом, пиксели DPX-02, DPX-12…, DPX-152 совместно используют одну чувствительную схему 121-2.

Вход чувствительной схемы 121-3 соединен с линией 131-3 выходного сигнала, с которой совместно соединены выходы всех пикселей DPX-03, DPX-13…, DPX-153, формирующие блок 160-3 пикселей.

Таким образом, пиксели DPX-03, DPX-13…, DPX-153 совместно используют одну чувствительную схему 121-3.

Для других блоков пикселей (не показаны) чувствительные схемы размещены в блоке 120А чувствительной схемы таким образом, что каждая чувствительная схема совместно используется множеством пикселей.

Блок 150А IC результата решения выполнен с возможностью многократного интегрирования решения, получаемого из чувствительных схем 121-0-121-3, пиксель за пикселем, для генерирования двумерных отображаемых данных с градацией.

В блоке 150А IC результата решения есть регистры 152А-0-152А-3, схема 155 выбора, схема 153А подсчета и запоминающее устройство 154А.

Регистры 152А-0 к 152А-3 содержат значения решения, полученные в соответствующих чувствительных схемах 121-0 к 121-3, которые были переданы через линии 141А-0-141А-3 передачи.

Схема 155 выбора последовательно выбирает выходы регистров 152А-0-152А-3, чтобы подать значения решения, содержащиеся в регистрах 152А-0-152А-3, в схему 153А подсчета.

Схема 153А подсчета последовательно выполняет обработку подсчета значений решения из множества пикселей (четыре пикселя в этом варианте выполнения), строка которых была выбрана для считывания и которые были поданы через схему 155 выбора, и содержит результат подсчета для каждого пикселя в запоминающем устройстве 154А.

Данные пикселей, считанные ранее, загружают в схему 153А подсчета из запоминающего устройства 154А.

В блоке 150А IC результата решения в соответствии со вторым вариантом выполнения есть одиночная схема 153А подсчета, которая совместно используется множеством регистров 152А-0-152А-3.

Другими словами, датчик 100А изображения CMOS в соответствии со вторым вариантом выполнения обеспечивает возможность для множества чувствительных схем 121А-0-121А-3 совместно использовать схему 153А подсчета.

Датчик 100А изображения CMOS в соответствии с вариантом выполнения выполнен с возможностью включать в себя упомянутую выше четвертую характерную структуру.

Таким образом, датчик 100А изображения CMOS выполнен таким образом, что множество пикселей совместно используют чувствительную схему, и к ним циклически осуществляют доступ, чтобы гарантировать время экспонирования и обеспечить возможность работы с более мелкими пикселями.

Кроме того, датчик 100А изображения CMOS выполнен таким образом, что множество чувствительных схем совместно используют схему подсчета, чтобы достичь гибкой оптимизации размеров схемы и производительности процесса.

Далее будет описана общая схема работы датчика 100А изображения CMOS в соответствии со вторым вариантом выполнения.

Как упомянуто выше, блок 160 (160-0, 160-1, 160-2, 160-3…) пикселя выполнен так, что он включает в себя 16 цифровых пикселей DPX и схему выбора. Схема выбора выбирает один из пикселей и сбрасывает или считывает данные из выбранного пикселя.

В этом варианте выполнения один пиксель в блоке 160 пикселей выбирают в соответствии с линией 181 управления строки, которой управляет схема 170 управления горизонтальной разверткой.

Во время считывания присутствие/отсутствие входного фотона в выбранном пикселе выводят в линию 131 (131-0, 131-1, 131-2, 131-3…) выходного сигнала, как электрический сигнал, который, в свою очередь, подвергают двоичному выбору в чувствительной схеме 121А (121А-0, 121А-1, 121А-2, 121А-3…).

Чувствительная схема 121А (121А-0, 121А-1, 121А-2, 121А-3) устанавливает "1" как значение решения, например, когда фотон попадает в выбранный пиксель, и устанавливает "0" как значение решения, когда фотон попадает в выбранный пиксель, и фиксирует значение решения.

Значение решения в чувствительной схеме 121А (121А-0, 121А-1, 121А-2, 121А-3…) сначала передают в регистр 152А (152А-0, 152А-1, 152А-2, 152А-3).

Схема 153А подсчета совместно используется четырьмя блоками 160-0-160-3 пикселей, и результат обработки подсчета последовательно выполняемой для данных из этих четырех пикселей в ряду, выбирают и считывают через схему 155 выбора.

Затем результат подсчета для каждого пикселя сохраняют в запоминающем устройстве 154А.

Таким образом, данные ранее считанного пикселя загружают в схему 153А подсчета из запоминающего устройства 154А.

Значение подсчета увеличивают на "1", когда "1" содержится в регистре 152А (152А-0, 152А-1, 152А-2, 152А-3), и не обновляют, когда там содержится "0".

После того значение схемы 153А подсчета записывают обратно в запоминающее устройство 154А, которое заканчивает обработку подсчета для одного пикселя. Такая обработка последовательно выполняется для этих четырех пикселей.

В то время как выполняется такая обработка подсчета блок 160 (160-0, 160-1, 160-2, 160-3) пикселей и чувствительная схема 121А (121А-0, 121А-1, 121А-2, 121А-3) могут параллельно выполнять считывание данных и принимать решение относительно следующей строки.

Такое цифровое считывание выполняют, например, 1023 раза за один период кадра, чтобы генерировать 10-битовые данные градации для каждого пикселя.

В это время схема 153А подсчета имеет размер 10 битов, и запоминающее устройство 154А имеет емкость 640 битов для каждого из 16х4 пикселей, поскольку каждый из пикселей имеет 10-битовые данные.

Таким образом, датчик 100А изображения CMOS работает как выстроенный в виде массива счетчик фотонов, имеющий уникальную конфигурацию.

В случае такой конфигурации, когда количество строк матрицы пикселей равно количеству строк в одном блоке, и блоки располагаются только в направлении столбца, возможно сформировать все схемы на одной и той же полупроводниковой подложке.

Однако когда в устройстве формирования изображения есть много пикселей, желательно, чтобы блоки 160-0, 160-1, 160-2, 160-3 пикселей были сформированы в виде многослойной структуры на разных полупроводниковых подложках на опорной схеме, включающей в себя соответствующие чувствительные схемы 121А-0, 121А-1, 121А-2, 121А-3.

Затем желательно, чтобы блок 110А матрицы пикселей, включая в себя блоки 160-0, 160-1, 160-2, 160-3 пикселей, и чувствительные схемы 121А-0, 121А-1, 121А-2, 121А-3 должны быть расположены в виде массива на других полупроводниковых подложках соответственно.

Другими словами, желательно, чтобы блок 110А матрицы пикселей, включающий в себя блоки 160-0, 160-1, 160-2, 160-3 пикселей, и блок 120А чувствительной схемы, включающий в себя чувствительные схемы 121А-0, 121А-1, 121А-2, 121А-3, должны быть расположены в виде массива на разных полупроводниковых подложках соответственно.

Кроме того, желательно, чтобы блоки 120А чувствительной схемы были сформированы на подложке, как блоки 200 схем, каждая из которых включает в себя схему 153А подсчета и запоминающее устройство 154А, и были расположены в виде массива. В качестве альтернативы запоминающие устройства 154А могут быть расположены в виде многослойной структуре на третьей полупроводниковой подложке под чувствительными схемами.

Ниже будет описан циклический доступ к блокам пикселей в соответствии со вторым вариантом выполнения.

На фиг.9 показана схема для пояснения циклического доступа к блокам пикселей в соответствии со вторым вариантом выполнения.

Здесь предполагается, что, когда все выстроенные в виде массива блоки пикселя работают приблизительно параллельно, доступ к отдельным пикселям предоставляется как доступ к одному блоку пикселя, независимо от того, сколько пикселей предусмотрено в устройстве формирования изображения.

Доступ к шестнадцати пикселям, включенным в каждый блок 160 (160-0, 160-1, 160-2, 160-3…) пикселей, получают последовательно и циклически.

Учитывая, что частота кадров составляет 1/30 секунды, и в течение этого периода считывание выполняют 1023 раза для каждого пикселя, один цикл обработки блока составляет приблизительно 32 микросекунды, в течение которых должно быть закончено считывание 16 пикселей.

Отрезок времени вдоль горизонтальной оси на фиг.9 представляет время t, которое выделяют для доступа к каждому пикселю в блоке, и максимальная ширина которого составляет 2 микросекунды.

Поскольку считывание данных из каждого пикселя и получение решения относительно данных представляют собой простые операции, аналогичные считыванию из полупроводниковой памяти, этот период времени выделен с достаточным запасом.

При описанном выше циклическом доступе сброс RST и считывание RD отдельных пикселей, DPX выполняют циклически.

В этом случае, хотя время доступа отличается от пикселя к пикселю, существенное время экспонирования ЕХР от момента времени сброса RST до времени считывания RD одинаково для всех пикселей.

Время экспонирования может изменяться при изменении времени сброса RST в пределах диапазона цикла так, чтобы чувствительность можно было регулировать, не влияя на другие операции схемы.

Если сброс RST для каждого пикселя, DPX устанавливают немедленно после предыдущего считывания RD (в том же отрезке времени, во время которого выполнили считывание), например, время экспонирования становится максимальным, чтобы обеспечить формирование изображения субъекта с низкой освещенностью.

С другой стороны, если сброс RST устанавливают непосредственно перед считыванием RD (на отрезке времени, который предшествует на один перед считыванием), время экспонирования становится минимальным, что позволяет формировать изображения субъекта при высокой освещенности. В качестве альтернативы, если момент времени сброса устанавливают изменяющимся на нескольких уровнях в пределах одного отрезка времени, время экспонирования может быть выбрано более свободно.

Обработка подсчета CNT следует за считыванием RD, и считывание следующего пикселя инициализируется параллельно.

Во время t4, например, считывают пиксель №4, и пиксель №1 сбрасывают. Параллельно этой операции выполняют обработку подсчета для пикселя №3.

Хотя считывание пикселя №4 и сброс пикселя №1 выполняются последовательно с разделением времени в этом варианте выполнения, считывание и сброс пикселей, для которых предусмотрен независимый механизм сброса, как показано на фиг.4, могут быть оба выполнены параллельно одновременно с управлением по двум линиям управления строки.

В соответствии со вторым вариантом выполнения, когда разные значения времени экспонирования устанавливают путем изменения времени сброса, становится возможным многократно выполнять получение данных и генерировать отображаемые данные, используя получение данных.

В частности, получение данных должно быть выполнено в соответствии со схемами, показанными на фиг.7А-7С, которые были описаны в предшествующем описании первого варианта выполнения, что обеспечивает возможность формирования изображения в широком динамическом диапазоне, который совместим с формированием изображения субъекта с высоким контрастом.

Как описано выше, второй вариант выполнения имеет иерархическую структуру, в которой множество пикселей DPX совместно используют чувствительную схему 121 А (121А-0, 121А-1, 121А-2, 121А-3), и регистр 152А (152А-0, 152А-1, 152А-2, 152А-3), и множество чувствительных схем 121 А (121А-0, 121А-1, 121А-2, 121А-3) совместно использует схему 153А подсчета.

Отношение совместного использования этих схем оптимизируют по отношению между упомянутым выше временем доступа и промежутками заполнения отдельных схем.

Поскольку у времени доступа одного пикселя есть достаточный допуск в варианте выполнения, например большее количество пикселей может совместно использовать чувствительную схему, или большее количество чувствительных схем может совместно использовать схему подсчета.

На фиг.10 показана схема, представляющая общее изображение микросхемы в соответствии со вторым вариантом выполнения, показанным на фиг.8.

Множество блоков 200 схем расположены в виде массива на полупроводниковой подложке SUB2A в примере, показанном на фиг.10.

Множество блоков 200 схем расположены в виде массива.

На полупроводниковой подложке SUB2A сформирована схема 210 управления, которая управляет множеством блоков 200 схем, демультиплексор (демультиплексор) 220, предназначенный для демультиплексирования выходов блоков 200 схем, регистры 230, линия 240 передачи и выходная цепь 250.

На фиг.10 показано, что для выходных данных из блока 160 пикселей, включающего в себя множество пикселей DPX и схему выбора, выполняют решение в чувствительной схеме 121А-0, и затем эти данные передают в регистр 152А.

Множество регистров 152А-0 к 152А-3 совместно использует схему 153А подсчета через схему 155 выбора, и результаты подсчета содержатся в запоминающем устройстве 154А, которое представляет собой, например, динамическое RAM (динамическое оперативное запоминающее устройство).

Блоки 200 схем расположены в виде массива на полупроводниковой подложке SUB2A и работают параллельно и одновременно для принятия решения в отношении данных из пикселей, выбранных в каждом блоке 200 схем и подсчета количества входных фотонов.

Основанную на времени подачу данных в блоки 200 схем и управление строкой запоминающих устройств 154А выполняют вместе для блоков 200 схем, расположенных в направлении строки, с помощью схемы 210 управления, расположенный для каждой строки.

Блоки 200 схем расположены в виде массива на другой полупроводниковой подложке SUB2B, установленной в виде многослойной структуры на полупроводниковой подложке SUB2A.

Желательно, чтобы блоки 200 схем и группа блоков 160 пикселей, соответствующих им, были расположены с одинаковым шагом так, чтобы отдельный блок 160 пикселей и соответствующие чувствительной схемы были соединены соответственно.

Когда подсчет для одного кадра заканчивается, результаты подсчета, содержащиеся в запоминающих устройствах 154А, фиксируют в регистрах 231 в группе 230 регистров через демультиплексор 220, по одной строке матрицы пикселей одновременно.

Когда выводят данные всех строк, формирующих кадр, обработка для одного кадра заканчивается.

Этот режим вывода совместим с режимом вывода нормального устройства формирования изображения, которое последовательно выводит строку данных кадра за строкой.

Когда всеми пикселями управляют для плавного формирования изображения субъекта в виде динамического изображения, желательно иметь два запоминающих устройства 154А для операций подсчета и вывода и иметь запоминающее устройства для двух кадров пикселей среди всех пикселей в целом.

В этом случае эти два запоминающее устройства используются с поочередным переключением с одного на другое кадр за кадром так, чтобы в то время как одно запоминающее устройство используется для операции подсчета, другое использовалось для операции вывода.

В качестве альтернативы запоминающие устройства для одного кадра еще могут быть разделены на две группы для нечетной строки и для четной строки, и операция между строками еще может быть выполнена для вывода данных из четной строки, в то время как пиксели в нечетной строке экспонируют и подсчитывают, и вывода данных из нечетной строки, в то время как пиксели в четной строке экспонируют и подсчитывают.

Возможен случай, когда желательно уменьшить количество выводимых данных в соответствии с вариантом использования устройства формирования изображения. Например, отображаемые данные из всех эффективных пикселей используются для неподвижного изображения, в то время как часто желательно сократить количество пикселей, чтобы уменьшить объем данных для движущегося изображения.

Для решения этой задачи в некоторых устройствах формирования изображения есть возможность суммирования данных множества пикселей и вывода этих данных как данные одного пикселя. Такое суммирование обычно выполняют в отдельно предусмотренном сумматоре, что, соответственно, увеличивает место, занимаемое схемой.

В соответствии с вариантом выполнения, в отличие от этого, ячейка памяти в запоминающем устройстве совместно используется множеством пикселей, которые совместно используют схему подсчета так, чтобы суммирование данных пикселей могло быть выполнено очень легко и гибко.

В соответствии с первым вариантом выполнения, показанным на фиг.3, например, множество пикселей, которые совместно используют схему 153 подсчета, по меньшей мере в направлении строки, могут совместно использовать ячейку памяти в запоминающем устройстве 154 для обеспечения возможности суммирования данных из пикселей.

В качестве альтернативы в соответствии со вторым вариантом выполнения, как показано на фиг.8, для множества пикселей, которые совместно используют схему 153А подсчета, обеспечивается возможность совместно использовать ячейку памяти в запоминающем устройстве 154А, чтобы обеспечить возможность выполнять гибкое суммирование данных пикселей как в направлении строки, так и в направлении столбца.

Во время выполнения такого суммирования объем используемого запоминающего устройства сохраняется и составляет, например, 1/4 в случае суммирования данных четырех пикселей.

Поэтому, когда все пиксели используются для неподвижного изображения, и данные пикселей суммируют для движущегося изображения, все запоминающее устройство 154А на фиг.10 может составлять объем пикселей одного кадра среди всех пикселей.

Один кадр полностью используется для неподвижного изображения, в то время как для движущегося изображения запоминающее устройство уменьшают при суммировании и разделяют на два запоминающих устройства, которые используют, переключая их поочередно с одного на другое кадр за кадром для операции подсчета и операции вывода.

Любая из тех операций может быть выполнена просто путем изменения адреса, который выбирают во время обращения к запоминающим устройствам, и обеспечивает простое управление.

В соответствии с вариантом выполнения подсчитываемые данные, сохраненные в запоминающих устройствах 154, 154А, выводят непосредственно. Обращение к данным в этих запоминающих устройствах может быть выполнено произвольно пиксель за пикселем, как к данным запоминающего устройства кадра так, чтобы устройство обработки данных изображения, такое как DSP, можно было бы, кроме того, установить на полупроводниковой подложке SUB2, SUB2A для выполнения обработки изображения, такой как коррекция дефектов, операция преобразования из растрового изображения в векторное и сжатие.

Кроме того, суммирование данных множества пикселей имеет преимущество, состоящее в том, что когда группу пикселей, данные которых должны быть суммированы, рассматривают как одиночный модуль приема света, динамический диапазон его выходного сигнала может быть улучшен. Когда 10-битовый подсчет будет выполнен для каждого пикселя, например на выходе суммирования данных четырех пикселей будет 12 битов.

Такое суммирование может быть выполнено гибко в соответствии с вариантом применения; данные пикселя, расположенные в двумерной матрице, могут быть суммированы для каждой группы пикселей, которая совместно использует счетчик, и сумматор может, кроме того, быть предусмотрен в выходном каскаде для суммирования данных групп пикселей во время вывода данных.

Выполнение такого поэтапного суммирования облегчает суммирование всех пикселей так, чтобы пиксели можно было использовать как одиночный счетчик фотонов. В этом случае у счетчика фотонов будет огромный динамический диапазон в соответствии с количеством пикселей.

Как упомянуто выше, каждый из цифровых пикселей, используемых в варианте выполнения, имеет устройство фотоэлектрического преобразования и функцию вывода электрического сигнала в соответствии с входными фотонами, и выполнен, например, как показано на фиг.4.

Во время считывания данных из цифровых пикселей желательно предусмотреть следующую функцию самообращения в режиме восприятия, чтобы взаимно уничтожить вариации выхода от одного пикселя до другого.

Таким образом, выход в состоянии сброса и сигнал, выводимый после экспонирования, считывают из пикселя, и чувствительная схема сравнивает оба выхода друг с другом с заданным смещением, добавляемым к одному из них, чтобы сделать двоичный выбор.

На фиг.11 показана принципиальная схема, представляющая один пример чувствительной схемы, имеющей функцию самообращения.

Чувствительная схема 121В на фиг.11 имеет переключатели SW121, SW122, SW123, конденсаторы С121, С122, инверторы IV121, IV122 и линию L121 питания для сигнала OFFSET смещения.

Вывод а переключателя SW121 подключен к первому выводу конденсатора С121 и первому выводу конденсатора С122, и вывод b подключен к выводу SIG, который соединен с линией выходного сигнала.

Второй вывод конденсатора С121 соединен с входным выводом инвертора IV121, выводом переключателя SW122 и выводом переключателя SW123.

Выходной вывод инвертора IV121 соединен с входным выводом инвертора IV122 и выводом b переключателя SW122.

Выходной вывод инвертора IV122 соединен с выводом b переключателя SW123 и выходным выводом SAOUT.

Пример операции считывания, используя чувствительную схему с функцией самообращения, как показано на фиг.11, будет описан в отношении пикселя, показанного на фиг.4, в качестве примера.

На фиг.12А-12F представлена временная диаграмма для пояснения примера операции считывания с использованием чувствительной схемы с функцией самообращения по фиг.11, со ссылкой на пиксель по фиг.4, в качестве примера.

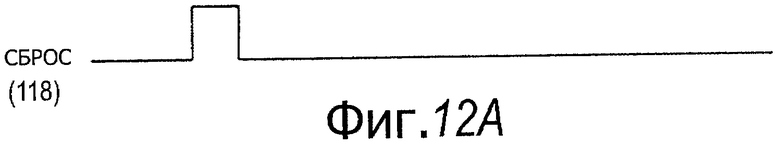

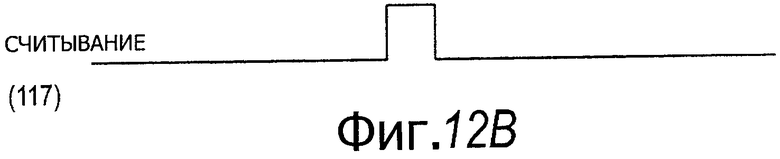

На фиг.12А показан импульс RESET сброса, который подают в линию 118 сброса по фиг.4, и на фиг.12В показан импульс READ считывания, который подают в линию 117 передачи на фиг.4.

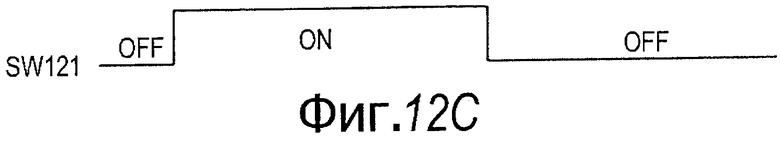

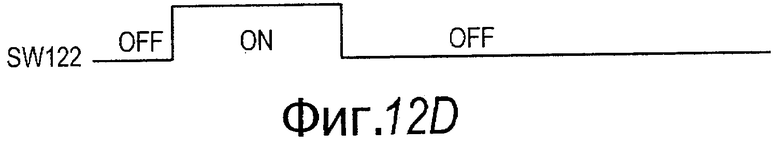

На фиг.12С показано состояние ВКЛ\ВЫКЛ переключателя SW121, на фиг.12D показано состояние ВКЛ\ВЫКЛ переключателя SW122, на фиг.12Е показано состояние ВКЛ\ВЫКЛ переключателя SW123 и на фиг.12F показан сигнал OFFSET смещения.

Вначале переключатель SW121 и переключатель SW122 устанавливают во включенное положение (ВКЛ) для подачи импульса RESET сброса в линию 118 сброса и считывания выхода пикселя в состоянии сброса, выводимого на входной вывод SIG.

Затем переключатель SW122 устанавливают в положение "выключено" (OFF) для удержания выхода сброса.

После этого импульс READ подают в линию 117 передачи для пикселя DPX, чтобы ввести выходной сигнал, представляющий результат экспонирования на вывод SIG, таким образом устанавливая в положение "выключено" переключатель SW121.

В течение того периода вход сигнала OFFSET смещения поддерживают на уровне 0 В.

Затем уровень сигнала OFFSET смещения немного увеличивают, чтобы добавить потенциал смещения к считываемому сигналу через конденсатор С122.

В результате выход пикселя в состоянии сброса и выход с небольшим смещением, суммированный со считываемым сигналом, сравнивают друг с другом.

Когда фотон попадает в пиксель по фиг.4, последний сигнал имеет более низкий потенциал, чем предыдущий сигнал так, что "0" подают на выходной вывод SAOUT.

Когда фотон не попадает в пиксель, получают противоположный результат сравнения, так что " 1" подают на выходной вывод SAOUT.

Наконец, переключатель SW123 устанавливают для фиксации результата решения.

Эта функция самообращения позволяет взаимно уничтожать фиксированный шум для каждого пикселя, возникающий в результате вариации или тому подобное порогового значения транзистора 114 усилителя, и гарантировать точное двоичное решение даже для незначительного сигнала. Кроме того, шум сброса kTC-шум также взаимно уничтожается в описанной выше последовательности.

Аналогичный эффект можно ожидать даже при коррелированной двойной выборке (CDS) при AD преобразовании аналогового сигнала.

Следует отметить, что поскольку периоды, необходимые для двух считываний и решений, являются всегда постоянными при детектировании с двоичным решением, влияние теплового шума или фликкерного шума, генерируемого транзистором усилителя пикселя и самой чувствительной схемой, может быть уменьшено следующим образом.

Поскольку большая часть шума в низкочастотной полосе также появляется (накладывается) при обоих считываниях, его влияние может быть взаимно уничтожено, чувствительность к шумам в высокочастотной полосе может быть ограничена емкостной нагрузкой чувствительной схемы.

Поэтому полоса влияющего шума может быть минимизирована при установке как можно большей емкостной нагрузки точно в диапазоне детектирования.

При коррелированной двойной выборке при AD преобразовании период, требуемый для преобразования, часто изменяется в соответствии с уровнем сигнала и количеством битов, и на него неизбежно влияет широкая полоса шумов.

Чувствительная схема не ограничивается этим примером и может быть модифицирована для сравнения сигнала сброса, суммированного со смещением с сигналом считывания, для принятия решения.

В качестве альтернативы сигнал считывания получают заранее, после чего сбрасывает пиксель, затем получают сигнал сброса, и сигнал считывания и сигнал сброса, со смещением добавленным к одному из сигналов, сравнивают друг с другом. В этом случае, хотя kTC-шумы не могут быть взаимно уничтожены, фиксированные шумы или тому подобное, возникающие из-за вариаций пикселя, могут быть взаимно уничтожены так, что модификация имеет преимущество в том, что она в общем может быть приспособлена к любой конфигурации пикселя.

Даже при установленной функции самообращения чувствительная схема имеет значительно меньше компонентов, чем нормальный AD преобразователь, и ей не требуется много места для размещения.

В случае реализации цифрового пикселя эффективно использовать фотодиод с внутренним усилением.