Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых или биполярных транзисторах [1-15], в т.ч. выполненные на основе несимметричных дифференциальных каскадов [14-16]. Основное достоинство последних - отсутствие классических источников опорного тока, отрицательно влияющих на важнейшие статические и динамические параметры.

Для работы в условиях низких температур, в условиях космического пространства, в экспериментальной физике необходимы радиационно-стойкие ОУ. Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевого технологического процесса [17], обеспечивающего формирование р-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2 [18-21]. Однако в таких ОУ при t=-100°÷-120° необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [17]. Для более низких температур в схемах рекомендуется использовать только полевые транзисторы [22-24].

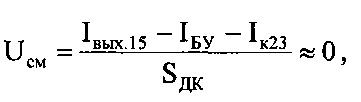

Ближайшим прототипом (фиг. 1) заявляемого устройства является мультидифференциальный операционный усилитель, представленный в патенте RU 2523124, фиг. 2. Он содержит (фиг. 1) первый 1 дифференциальный каскад на основе первого 2 и второго 3 входных транзисторов, связанных друг с другом инжектирующими выводами, первый 4 и второй 5 токовые выходы первого 1 дифференциального каскада, первый 6 и второй 7 входы первого 1 дифференциального каскада, второй 8 дифференциальный каскад на основе первого 9 и второго 10 входных транзисторов, связанных друг с другом инжектирующими выводами, первый 11 и второй 12 токовые выходы второго 8 дифференциального каскада, первый 13 и второй 14 входы второго 8 дифференциального каскада, первое 15 токовое зеркало, согласованное с первой 16 шиной источника питания, выход которого соединен с токовым выходом устройства 17, второе 18 токовое зеркало, согласованное со второй 19 шиной источника питания, вход которого соединен со вторым 5 токовым выходом первого 1 дифференциального каскада.

Существенный недостаток известного ОУ состоит в том, что он имеет повышенное напряжение смещения нуля (Uсм). Это связано с тем, что в двухканальной структуре ОУ-прототипа фиг.1 используются для передачи сигнала как первое 15, так и второе 18 токовые зеркала, реализуемые на разнотипных транзисторах (n-p-n, p-n-p), имеющих различные значения коэффициента усиления по току базы (β), а также неодинаковые напряжения Эрли. В конечном итоге, это увеличивает влияние неидентичности данных токовых зеркал на Uсм.

Основная задача предлагаемого изобретения состоит в уменьшении систематической составляющей напряжения смещения нуля.

Дополнительная задача - создание условий для применения в схеме заявляемого устройства КМОП транзисторов.

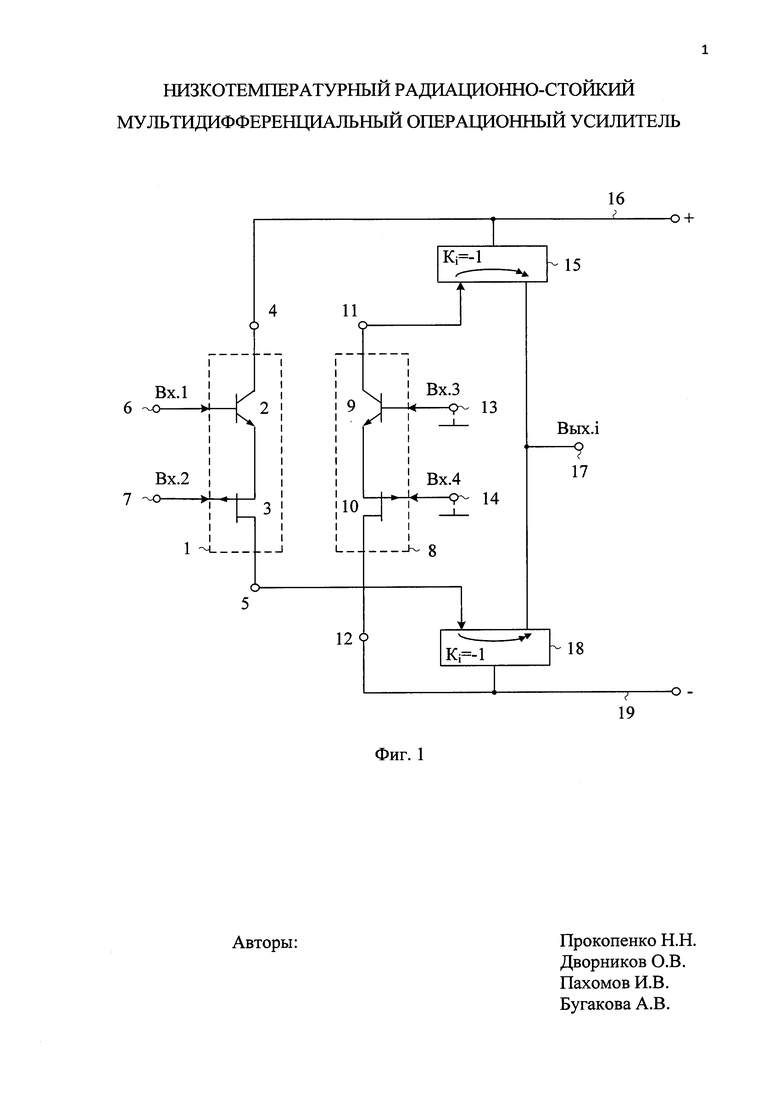

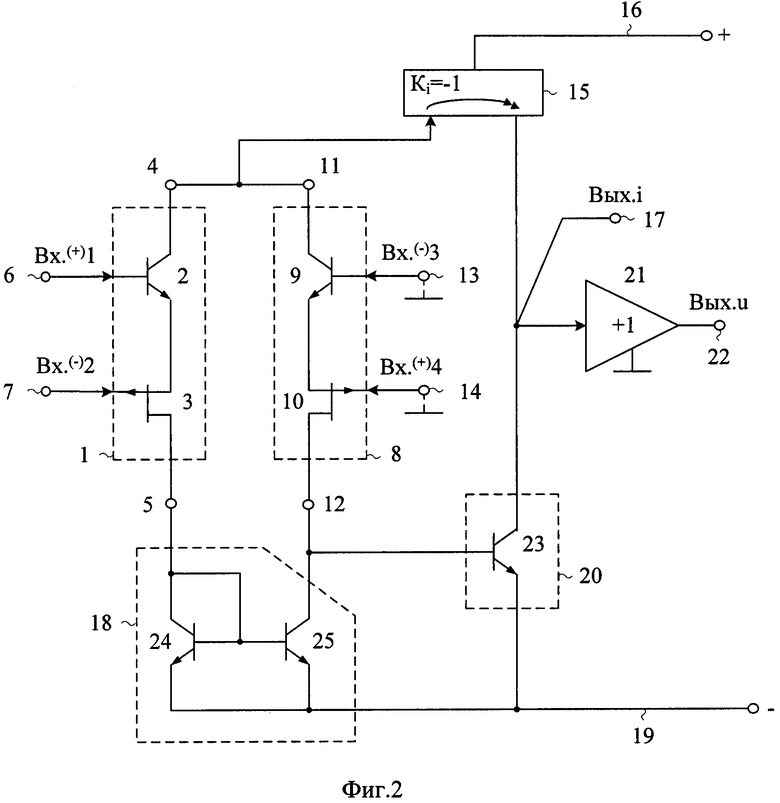

Поставленные задачи достигаются тем, что в мультидифференциальном операционном усилителе фиг. 2, содержащем первый 1 дифференциальный каскад на основе первого 2 и второго 3 входных транзисторов, связанных друг с другом инжектирующими выводами, первый 4 и второй 5 токовые выходы первого 1 дифференциального каскада, первый 6 и второй 7 входы первого 1 дифференциального каскада, второй 8 дифференциальный каскад на основе первого 9 и второго 10 входных транзисторов, связанных друг с другом инжектирующими выводами, первый 11 и второй 12 токовые выходы второго 8 дифференциального каскада, первый 13 и второй 14 входы второго 8 дифференциального каскада, первое 15 токовое зеркало, согласованное с первой 16 шиной источника питания, выход которого соединен с токовым выходом устройства 17, второе 18 токовое зеркало, согласованное со второй 19 шиной источника питания, вход которого соединен со вторым 5 токовым выходом первого 1 дифференциального каскада, предусмотрены новые элементы и связи - первый 4 токовый выход первого 1 дифференциального каскада и первый 11 токовый выход второго 8 дифференциального каскада подключены к входу первого 15 токового зеркала, второй 12 токовый выход второго 8 дифференциального каскада подключен к выходу второго 18 токового зеркала и соединен с входом дополнительного инвертирующего усилителя 20, согласованного со второй 19 шиной источника питания, токовый выход которого соединен с токовым выходом устройства 17.

На фиг. 1 показана схема ОУ-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с п. 1- 5 формулы изобретения.

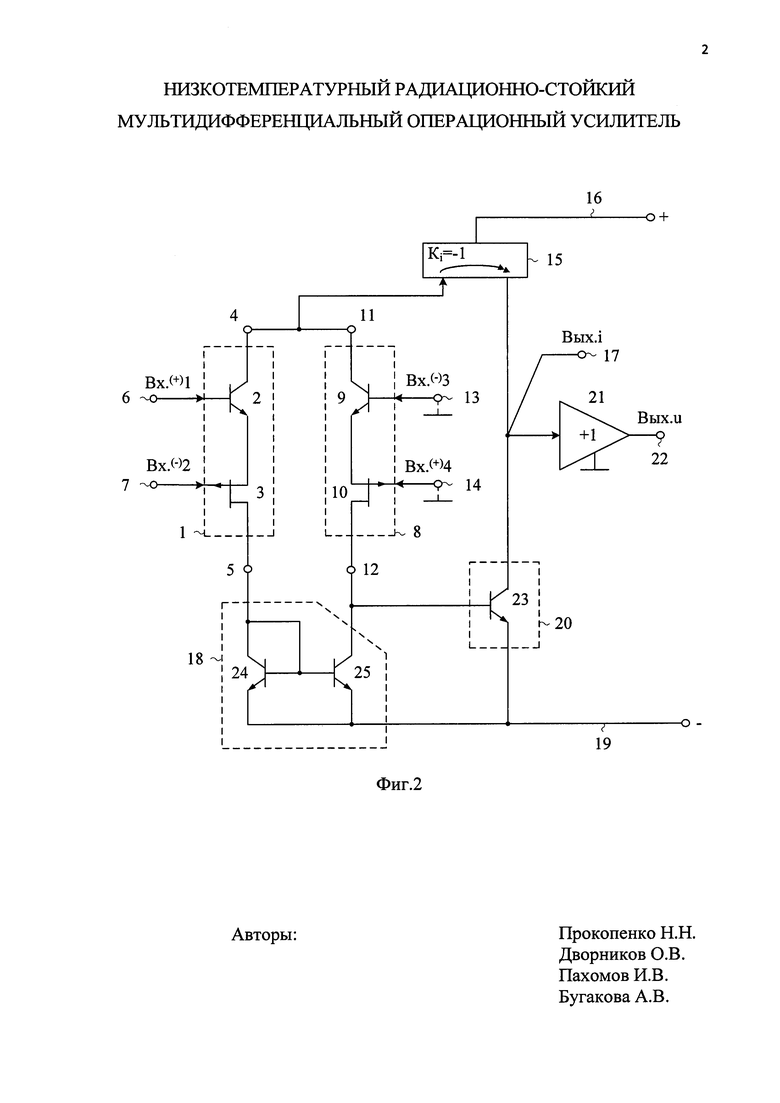

На фиг. 3 приведена схема фиг. 2 с конкретным выполнением первого 15 токового зеркала по схеме Вильсона (p-n-p транзисторы 26, 27, p-n переход 28), а также второго 18 токового зеркала, включающего первый 24 и второй 25 вспомогательные транзисторы. При этом дополнительный инвертирующий усилитель 20 реализован на транзисторе 23 по схеме с общим эмиттером.

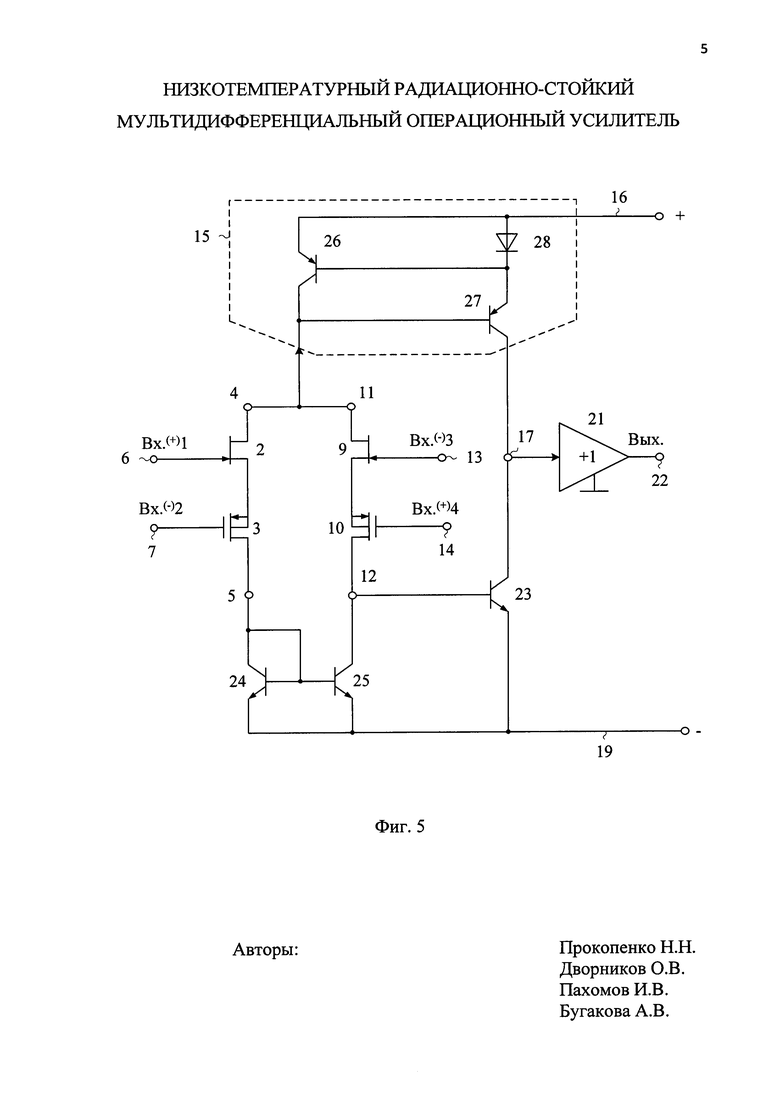

На фиг.4 приведена схема заявляемого устройства в соответствии с п. 6, а на фиг. 5 – с п. 7 формулы изобретения.

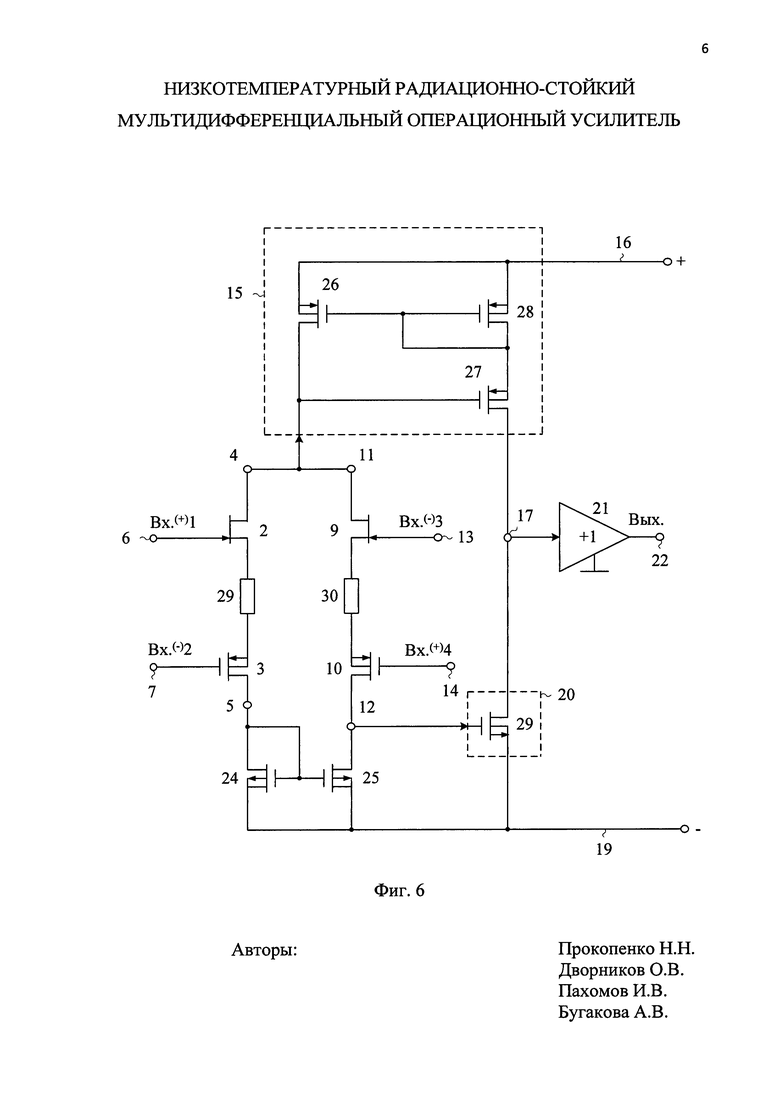

На фиг. 6 представлена схема заявляемого устройства в соответствии с п. 8 и п. 9 формулы изобретения.

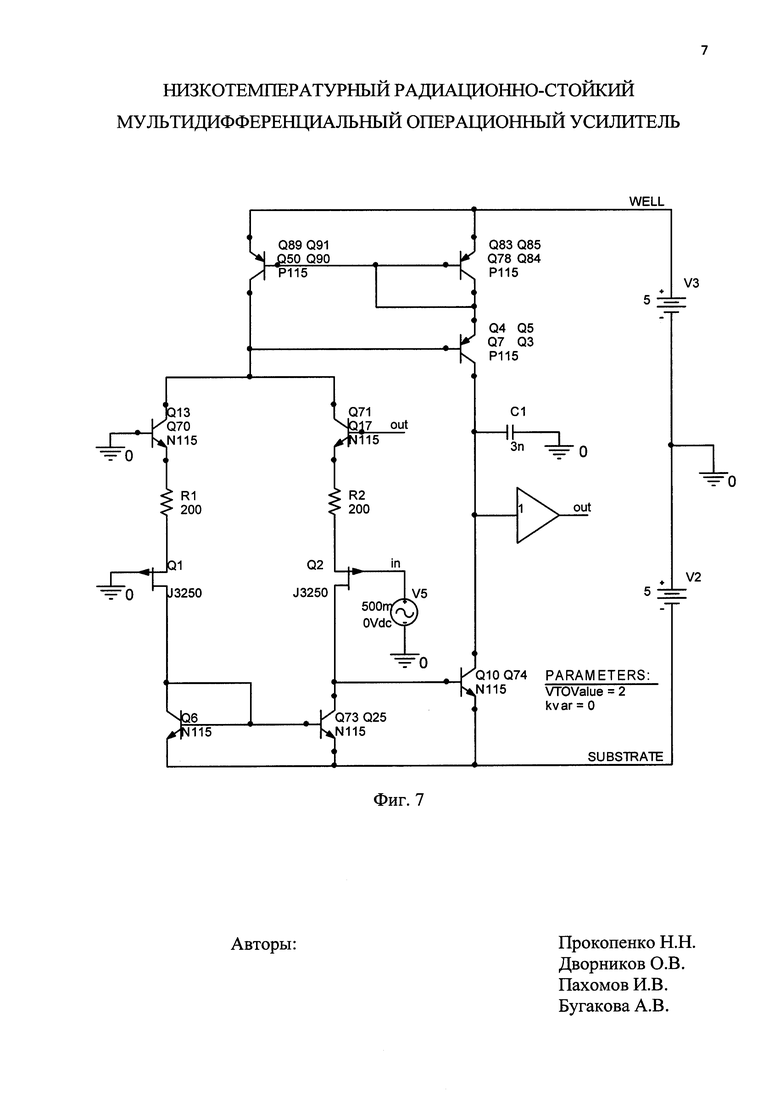

На фиг.7 представлена схема заявляемого устройства фиг. 3 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск).

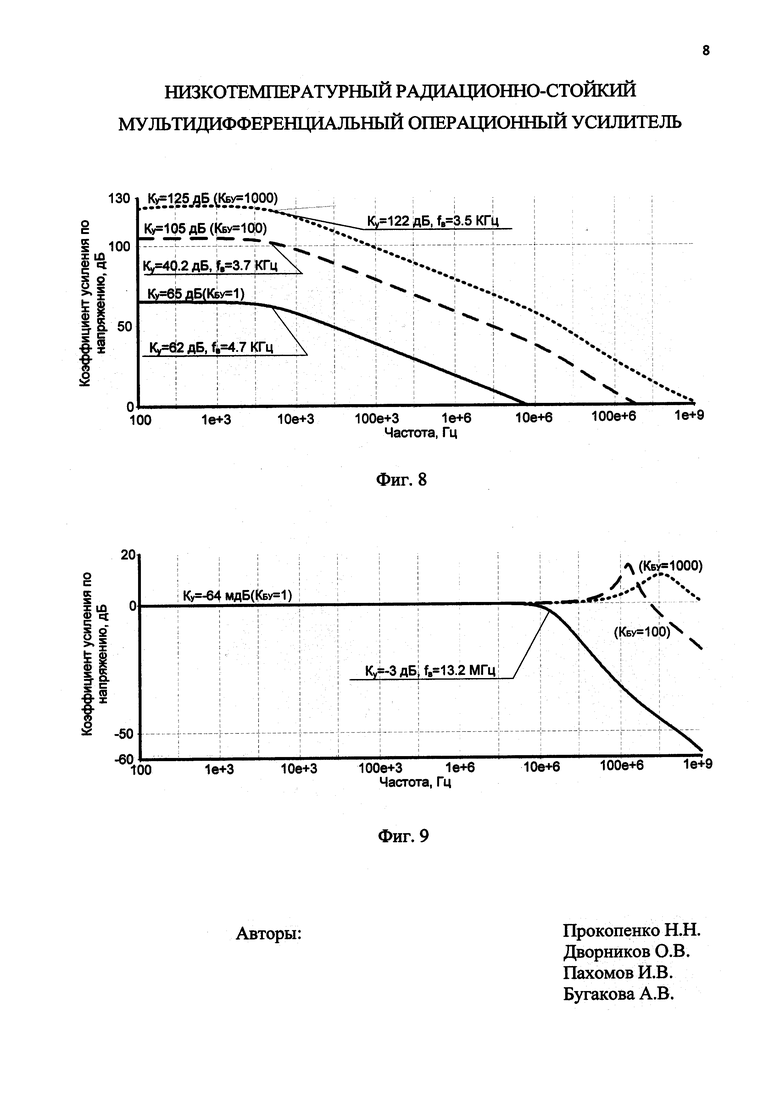

На фиг. 8 показаны амплитудно-частотные характеристики мультидифференциального операционного усилителя фиг. 7 при разных значениях коэффициента усиления буферного усилителя 21.

На фиг. 9 приведены амплитудно-частотные характеристики заявляемого мультидифференциального операционного усилителя фиг. 7 со 100% отрицательной обратной связью при разных значениях коэффициента усиления буферного усилителя 21.

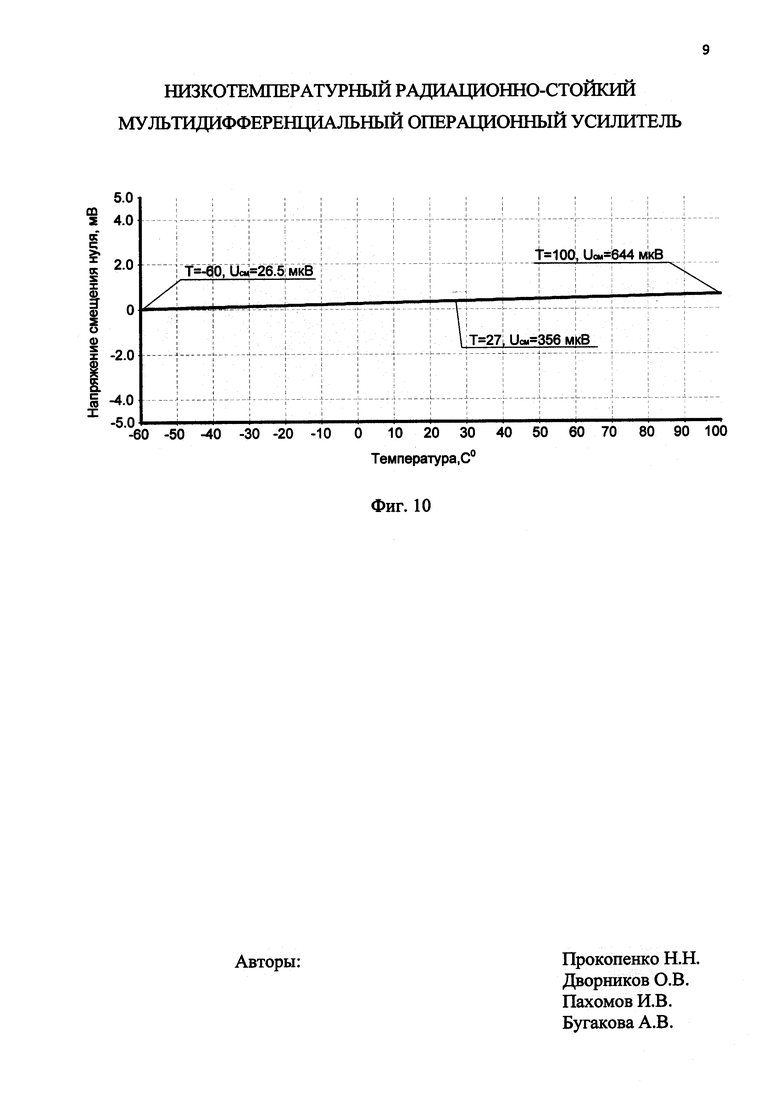

На фиг. 10 представлена зависимость напряжения смещения нуля ОУ фиг. 7 от температуры.

Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель фиг. 2 содержит первый 1 дифференциальный каскад на основе первого 2 и второго 3 входных транзисторов, связанных друг с другом инжектирующими выводами, первый 4 и второй 5 токовые выходы первого 1 дифференциального каскада, первый 6 и второй 7 входы первого 1 дифференциального каскада, второй 8 дифференциальный каскад на основе первого 9 и второго 10 входных транзисторов, связанных друг с другом инжектирующими выводами, первый 11 и второй 12 токовые выходы второго 8 дифференциального каскада, первый 13 и второй 14 входы второго 8 дифференциального каскада, первое 15 токовое зеркало, согласованное с первой 16 шиной источника питания, выход которого соединен с токовым выходом устройства 17, второе 18 токовое зеркало, согласованное со второй 19 шиной источника питания, вход которого соединен со вторым 5 токовым выходом первого 1 дифференциального каскада. Первый 4 токовый выход первого 1 дифференциального каскада и первый 11 токовый выход второго 8 дифференциального каскада подключены к входу первого 15 токового зеркала, второй 12 токовый выход второго 8 дифференциального каскада подключен к выходу второго 18 токового зеркала и соединен с входом дополнительного инвертирующего усилителя 20, согласованного со второй 19 шиной источника питания, токовый выход которого соединен с токовым выходом устройства 17.

На фиг. 2, в соответствии с п. 2 формулы изобретения, токовый выход устройства 17 соединен с входом дополнительного буферного усилителя 21, выход которого является потенциальным выходом 22 устройства.

Кроме этого на фиг. 2, в соответствии с п. 3 формулы изобретения, второе 18 токовое зеркало выполнено на основе первого 24 и второго 25 вспомогательных транзисторов, эмиттеры которых связаны со второй 19 шиной источника питания, базы объединены и подключены ко входу второго 18 токового зеркала, причем коллектор первого 24 вспомогательного транзистора соединен со входом второго 18 токового зеркала, а коллектор второго 25 вспомогательного транзистора связан с выходом второго 18 токового зеркала.

На фиг. 2, в соответствии с п. 4 формулы изобретения, дополнительный инвертирующий усилитель 20 выполнен на входном транзисторе 23, включенным по схеме с общим эмиттером.

На фиг. 2, в соответствии с п. 5 формулы изобретения, первый 2 входной транзистор первого 1 дифференциального каскада выполнен как биполярный транзистор, коллектор которого соединен с первым 4 токовым выходом первого 1 дифференциального каскада, база соединена с первым 6 входом первого 1 дифференциального каскада, причем второй 3 входной транзистор первого 1 дифференциального каскада выполнен как полевой транзистор с управляющим pn-переходом, затвор которого соединен со вторым 7 входом первого 1 дифференциального каскада, а сток связан со вторым 5 токовым выходом первого 1 дифференциального каскада, первый 9 входной транзистор второго 8 дифференциального каскада выполнен как биполярный транзистор, коллектор которого соединен с первым 11 токовым выходом второго 8 дифференциального каскада, база соединена с первым 13 входом второго 8 дифференциального каскада, причем второй 10 входной транзистор второго 8 дифференциального каскада выполнен как полевой транзистор с управляющим pn-переходом, затвор которого соединен со вторым 14 входом второго 8 дифференциального каскада, а сток связан со вторым 12 токовым выходом второго 8 дифференциального каскада.

На фиг. 3 приведена схема фиг.2 с конкретным выполнением первого 15 токового зеркала по схеме Вильсона (p-n-p транзисторы 26, 27, p-n переход 28), а также второго 18 токового зеркала, включающего первый 24 и второй 25 вспомогательные транзисторы. При этом дополнительный инвертирующий усилитель 20 реализован на транзисторе 23 по схеме с общим эмиттером.

На фиг. 4, в соответствии с п. 6 формулы изобретения, первый 2 входной транзистор первого 1 дифференциального каскада и первый 9 входной транзистор второго 8 дифференциального каскада выполнены как полевые КМОП-транзисторы, а второй 3 входной транзистор первого 1 дифференциального каскада и второй 10 входной транзистор второго 8 дифференциального каскада выполнены как полевые транзистора с управляющим pn-переходом, причем затворы первого 2 входного транзистора первого 1 дифференциального каскада и первого 9 входного транзистора второго 8 дифференциального каскада соединены соответственно с первым 6 входом первого 1 дифференциального каскада и первым 13 входом второго 8 дифференциального каскада, а затворы второго 3 входного транзистора первого 1 дифференциального каскада и второго 10 входного транзистора второго 8 дифференциального каскада соединены соответственно со вторым 7 входом первого 1 дифференциального каскада и вторым 14 входом второго 8 дифференциального каскада, сток первого 2 входного транзистора первого 1 дифференциального каскада соединен с первым 4 токовым выходом первого 1 дифференциального каскада, сток второго 3 входного транзистора первого 1 дифференциального каскада соединен со вторым 5 токовым выходом первого 1 дифференциального каскада, сток первого 9 входного транзистора второго 8 дифференциального каскада соединен с первым 11 токовым выходом второго 8 дифференциального каскада, сток второго 10 входного транзистора второго 8 дифференциального каскада соединен со вторым 12 токовым выходом второго 8 дифференциального каскада.

На фиг. 5, в соответствии с п. 7 формулы изобретения, первый 2 входной транзистор первого 1 дифференциального каскада и первый 9 входной транзистор второго 8 дифференциального каскада выполнены как полевые транзисторы с управляющим pn-переходом, а второй 3 входной транзистор первого 1 дифференциального каскада и второй 10 входной транзистор второго 8 дифференциального каскада выполнены как полевые КМОП-транзисторы, причем затвор первого 2 входного транзистора первого 1 дифференциального каскада соединен с первым 6 входом первого 1 дифференциального каскада, сток первого 2 входного транзистора первого 1 дифференциального каскада соединен с первым 4 токовым выходом первого 1 дифференциального каскада, затвор первого 9 входного транзистора второго 8 дифференциального каскада соединен с первым 13 входом второго 8 дифференциального каскада, сток первого 9 входного транзистора второго 8 дифференциального каскада соединен с первым 11 токовым выходом второго 8 дифференциального каскада, затвор второго 3 входного транзистора первого 1 дифференциального каскада соединен со вторым 7 входом первого 1 дифференциального каскада, сток второго 3 входного транзистора первого 1 дифференциального каскада соединен со вторым 5 токовым выходом первого 1 дифференциального каскада, затвор второго 10 входного транзистора второго 8 дифференциального каскада соединен со вторым 14 входом второго 8 дифференциального каскада, а сток второго 10 входного транзистора второго 8 дифференциального каскада, связан со вторым 12 токовым выходам второго 8 дифференциального каскада.

На фиг. 6, в соответствии с п. 8 формулы изобретения, инжектирующие выводы первого 2 и второго 3 входных транзисторов первого 1 дифференциального каскады связаны друг с другом через первый 29 согласующий резистор, а инжектирующие выводы первого 9 и второго 10 входных транзисторов второго 8 дифференциального каскада связаны друг с другом через второй 30 согласующий резистор.

Кроме этого на фиг. 6, в соответствии с п. 9 формулы изобретения, в качестве первого 24 и второго 25 вспомогательных транзисторов второго 18 токового зеркала и входного транзистора 23 дополнительного инвертирующего усилителя 20 используются КМОП транзисторы, затвор каждого из которых соответствует базе биполярного транзистора, исток - эмиттеру, а сток - коллектору биполярного транзистора.

Рассмотрим работу МОУ фиг. 3 с конкретным выполнением первого 15 и второго 18 токовых зеркал.

Особенность схемы фиг. 3 состоит в том, что первое 15 токовое зеркало не участвует в непосредственном усилении сигнала, а используется в качестве пассивного источника тока, создающего (вместе с входным транзистором 23) высокоимпедансный узел 17 (токовый выход 17). В статическом режиме для схемы фиг. 3 можно составить следующие уравнения Кирхгофа:

Iвх.15=2I0-2Iбр,

Iвых.15=2I0-2Iбр,

где I0 - статический ток истока второго 3 входного транзистора первого 1 дифференциального каскада и второго 10 входного транзистора второго 8 дифференциального каскада при нулевых напряжениях на первом 6, втором 7 входах первого 1 дифференциального каскада, а также на первом 13 и втором 14 входах второго 8 дифференциального каскада;

Iбр - ток базы n-p-n транзисторов схемы (первого 24, второго 25 вспомогательных транзисторов, а также входного транзистора 23) при токе эмиттера Iэ=I0.

С уменьшением температуры и повышением уровня радиации ток базы транзисторов схемы фиг. 3 существенно (в 5-10 раз) возрастает [22-24, 18-21]. Однако в заявляемом устройстве фиг. 3 (при идентичном изменении параметров указанных выше элементов) в высокоимпедансном узле 17 обеспечивается полная взаимная компенсация радиационных и температурных изменений токов базы транзисторов. Данный эффект обеспечивается за счет введения новых связей, а также конкретного построения основных функциональных узлов ОУ фиг. 3. В результате напряжение смещения нуля схемы фиг. 2 получается небольшим

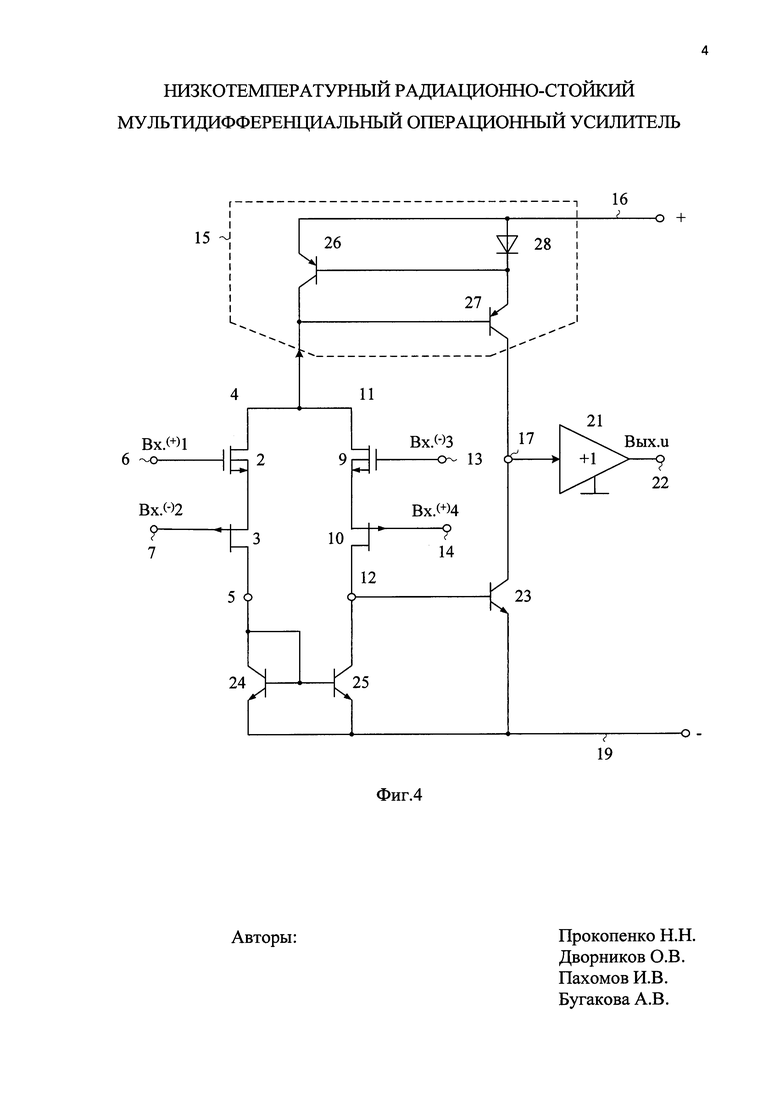

где Iвых.15=2I0-2Iбр - статический выходной ток первого 15 токового зеркала;

Iк23=2I0-2Iбр - статический коллекторный ток транзистора 23;

IБУ≈0 - входной ток дополнительного буферного усилителя 21;

SДК - крутизна передачи входного напряжения МОУ к токовому выходу 17.

Заметим, что первое 15 токовое зеркало, реализованное по схеме Вильсона [17], обеспечивает выполнение условий Iвых.15=Iвх.15=2I0-2Iбр в широком диапазоне внешних воздействий.

Из приведенного анализа следует, что схема фиг. 3 обладает уникальными свойством - в ней в высокоимпедансном узле 17 обеспечивается взаимная компенсация основных статических погрешностей преобразования сигналов, обусловленных деградацией (в 5-10 раз) коэффициента усиления по току базы транзисторов (β).

Для работы предлагаемого ОУ в диапазоне более низких, в т.ч. криогенных, температур целесообразно исключать биполярные транзисторы [22-24], что частично реализуется в схемах фиг. 4, фиг. 5, а наиболее полно в схеме фиг. 6.

Таким образом, заявляемое устройство характеризуется более высокими значениями параметров, характеризующими его прецизионность и имеет потенциальные возможности работы при низких температурах с одновременным воздействием радиации [18-21].

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US №4.596.958, fig. 2.

2. Патент US №4.901.031, fig. 3.

3. Патент US №5.291.149, fig. 4.

4. Патент US №4.357.578, fig. 1.

5. Патент US №3.703.650, fig. 1.

6. Патент US №2.070.768, fig. 1.

7. Патент US №2.571.579, fig. 4.

8. Патент US №3.873.933, fig. 2.

9. Патент US №7.202.738, fig. 10.

10. Патент US №4.198.610, fig. 3.

11. Патент US №6.407.537, fig. 1.

12. Патент US №4.667.165, fig. 3.

13. Патентная заявка US 2010/0117735, fig. 2.

14. Патент РФ 2523124.

15. Патент РФ 2517699.

16. Prokopenko, N.N. The Radiation-Hardened Differential Stages and Op Amps without Classical Reference Current Source / N.N. Prokopenko, O.V. Dvornikov, I.V. Pakhomov and N.V. Butyrlagin // 2015 Conference on Radiation Effects on Components and Systems (RADECS), September 14th-18th, 2015, Moscow, Russia. DOI: 10.1109/RADECS.2015.7365681.

17. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

18. Дворников, О. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 1 / O. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, №4. С. 44-49.

19. Дворников, О. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 2 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, №5. С. 24-28.

20. Дворников, О. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 3 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника, 2015, №6. С. 34-39.

21. Dvornikov, О.V. Specialized Integral Microcircuit of the Amplifier of Photosignals / О.V. Dvornikov, V.A. Chekhovskii, V.L. Dyatlov, and N.N. Prokopenko // Russian Microelectronics, 2015, Vol. 44, No. 3, pp. 197-202. (ISSN 1063-7397). DOI: 10.1134/S1063739715020031.

22. Dvornikov, О.V. An Integrated Circuit of a Universal Comparator / О.V. Dvornikov, V.A. Chekhovskii, V.L. Dyatlov, and N.N. Prokopenko // Instruments and Experimental Techniques, 2015, Vol. 58, No. 3, pp. 483-487. DOI: 10.1134/S0020441215030197.

23. Dvornikov, О.V. An integrated circuit for silicon photomultipliers tubes / O.V. Dvornikov, V.A. Tchekhovsi, V.L. Dyatlov, and N.N. Prokopenko // Instruments and Experimental Techniques, vol. 57, no. 1, pp. 40-44, Feb. 2014. WOS:000331640100007, JCR 2013 Impact Factor - 0.349 DOI: 10.1134/S0020441214010047

24. Dvornikov, О.V. Influence of Ionizing Radiation on the Parameters of an Operational Amplifier Based on Complementary Bipolar Transistors / О.V. Dvornikov, V.A. Tchekhovski, V.L. Dziatlau, and N. N. Prokopenko // Russian Microelectronics, 2016, Vol. 45, No. 1, pp. 54-62. (ISSN 1063-7397). DOI: 10.1134/S1063739716010030.

| название | год | авторы | номер документа |

|---|---|---|---|

| НИЗКОТЕМПЕРАТУРНЫЙ РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2624585C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2621287C2 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2583760C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| ВХОДНОЙ КАСКАД МУЛЬТИДИФФЕРЕНЦИАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571578C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2566964C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2640744C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615068C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2677401C1 |

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов. Технический результат: уменьшение систематической составляющей напряжения смещения нуля, а также создание условий для применения в схеме заявляемого устройства КМОП транзисторов. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель содержит первый (1) дифференциальный каскад на основе первого (2) и второго (3) входных транзисторов, связанных друг с другом инжектирующими выводами. Первый (4) токовый выход первого (1) дифференциального каскада и первый (11) токовый выход второго (8) дифференциального каскада подключены ко входу первого (15) токового зеркала, второй (12) токовый выход второго (8) дифференциального каскада подключен к выходу второго (18) токового зеркала и соединен со входом дополнительного инвертирующего усилителя (20), согласованного со второй (19) шиной источника питания, токовый выход которого соединен с токовым выходом устройства (17). 8 з.п. ф-лы, 10 ил.

1. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель, содержащий первый (1) дифференциальный каскад на основе первого (2) и второго (3) входных транзисторов, связанных друг с другом инжектирующими выводами, первый (4) и второй (5) токовые выходы первого (1) дифференциального каскада, первый (6) и второй (7) входы первого (1) дифференциального каскада, второй (8) дифференциальный каскад на основе первого (9) и второго (10) входных транзисторов, связанных друг с другом инжектирующими выводами, первый (11) и второй (12) токовые выходы второго (8) дифференциального каскада, первый (13) и второй (14) входы второго (8) дифференциального каскада, первое (15) токовое зеркало, согласованное с первой (16) шиной источника питания, выход которого соединен с токовым выходом устройства (17), второе (18) токовое зеркало, согласованное со второй (19) шиной источника питания, вход которого соединен со вторым (5) токовым выходом первого (1) дифференциального каскада, отличающийся тем, что первый (4) токовый выход первого (1) дифференциального каскада и первый (11) токовый выход второго (8) дифференциального каскада подключены ко входу первого (15) токового зеркала, второй (12) токовый выход второго (8) дифференциального каскада подключен к выходу второго (18) токового зеркала и соединен со входом дополнительного инвертирующего усилителя (20), согласованного со второй (19) шиной источника питания, токовый выход которого соединен с токовым выходом устройства (17).

2. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель по п. 1, отличающийся тем, что токовый выход устройства (17) соединен со входом дополнительного буферного усилителя (21), выход которого является потенциальным выходом (22) устройства.

3. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель по п. 1, отличающийся тем, что второе (18) токовое зеркало выполнено на основе первого (24) и второго (25) вспомогательных транзисторов, эмиттеры которых связаны со второй (19) шиной источника питания, базы объединены и подключены ко входу второго (18) токового зеркала, причем коллектор первого (24) вспомогательного транзистора соединен со входом второго (18) токового зеркала, а коллектор второго (25) вспомогательного транзистора связан с выходом второго (18) токового зеркала.

4. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель по п. 1, отличающийся тем, что дополнительный инвертирующий усилитель (20) выполнен на входном транзисторе (23), включенном по схеме с общим эмиттером.

5. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель по п. 1, отличающийся тем, что первый (2) входной транзистор первого (1) дифференциального каскада выполнен как биполярный транзистор, коллектор которого соединен с первым (4) токовым выходом первого (1) дифференциального каскада, база соединена с первым (6) входом первого (1) дифференциального каскада, причем второй (3) входной транзистор первого (1) дифференциального каскада выполнен как полевой транзистор с управляющим pn-переходом, затвор которого соединен со вторым (7) входом первого (1) дифференциального каскада, а сток связан со вторым (5) токовым выходом первого (1) дифференциального каскада, первый (9) входной транзистор второго (8) дифференциального каскада выполнен как биполярный транзистор, коллектор которого соединен с первым (11) токовым выходом второго (8) дифференциального каскада, база соединена с первым (13) входом второго (8) дифференциального каскада, причем второй (10) входной транзистор второго (8) дифференциального каскада выполнен как полевой транзистор с управляющим pn-переходом, затвор которого соединен со вторым (14) входом второго (8) дифференциального каскада, а сток связан со вторым (12) токовым выходом второго (8) дифференциального каскада.

6. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель по п. 1, отличающийся тем, что первый (2) входной транзистор первого (1) дифференциального каскада и первый (9) входной транзистор второго (8) дифференциального каскада выполнены как полевые КМОП-транзисторы, а второй (3) входной транзистор первого (1) дифференциального каскада и второй (10) входной транзистор второго (8) дифференциального каскада выполнены как полевые транзистора с управляющим pn-переходом, причем затворы первого (2) входного транзистора первого (1) дифференциального каскада и первого (9) входного транзистора второго (8) дифференциального каскада соединены соответственно с первым (6) входом первого (1) дифференциального каскада и первым (13) входом второго (8) дифференциального каскада, а затворы второго (3) входного транзистора первого (1) дифференциального каскада и второго (10) входного транзистора второго (8) дифференциального каскада соединены соответственно со вторым (7) входом первого (1) дифференциального каскада и вторым (14) входом второго (8) дифференциального каскада, сток первого (2) входного транзистора первого (1) дифференциального каскада соединен с первым (4) токовым выходом первого (1) дифференциального каскада, сток второго (3) входного транзистора первого (1) дифференциального каскада соединен со вторым (5) токовым выходом первого (1) дифференциального каскада, сток первого (9) входного транзистора второго (8) дифференциального каскада соединен с первым (11) токовым выходом второго (8) дифференциального каскада, сток второго (10) входного транзистора второго (8) дифференциального каскада соединен со вторым (12) токовым выходом второго (8) дифференциального каскада.

7. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель по п. 1, отличающийся тем, что первый (2) входной транзистор первого (1) дифференциального каскада и первый (9) входной транзистор второго (8) дифференциального каскада выполнены как полевые транзисторы с управляющим pn-переходом, а второй (3) входной транзистор первого (1) дифференциального каскада и второй (10) входной транзистор второго (8) дифференциального каскада выполнены как полевые КМОП-транзисторы, причем затвор первого (2) входного транзистора первого (1) дифференциального каскада соединен с первым (6) входом первого (1) дифференциального каскада, сток первого (2) входного транзистора первого (1) дифференциального каскада соединен с первым (4) токовым выходом первого (1) дифференциального каскада, затвор первого (9) входного транзистора второго (8) дифференциального каскада соединен с первым (13) входом второго (8) дифференциального каскада, сток первого (9) входного транзистора второго (8) дифференциального каскада соединен с первым (11) токовым выходом второго (8) дифференциального каскада, затвор второго (3) входного транзистора первого (1) дифференциального каскада соединен со вторым (7) входом первого (1) дифференциального каскада, сток второго (3) входного транзистора первого (1) дифференциального каскада соединен со вторым (5) токовым выходом первого (1) дифференциального каскада, затвор второго (10) входного транзистора второго (8) дифференциального каскада соединен со вторым (14) входом второго (8) дифференциального каскада, а сток второго (10) входного транзистора второго (8) дифференциального каскада, связан со вторым (12) токовым выходам второго (8) дифференциального каскада.

8. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель по п. 1, отличающийся тем, что инжектирующие выводы первого (2) и второго (3) входных транзисторов первого (1) дифференциального каскады связаны друг с другом через первый (29) согласующий резистор, а инжектирующие выводы первого (9) и второго (10) входных транзисторов второго (8) дифференциального каскада связаны друг с другом через второй (30) согласующий резистор.

9. Низкотемпературный радиационно-стойкий мультидифференциальный операционный усилитель по п. 3 или 4, отличающийся тем, что в качестве первого (24) и второго (25) вспомогательных транзисторов второго (18) токового зеркала и входного транзистора (23) дополнительного инвертирующего усилителя (20) используются КМОП-транзисторы, затвор каждого из которых соответствует базе биполярного транзистора, исток - эмиттеру, а сток - коллектору биполярного транзистора.

| СПОСОБ ОСУЩЕСТВЛЕНИЯ ПЛАЗМОХИМИЧЕСКИХ ВЗАИМОДЕЙСТВИЙ МЕЖДУ ЖИДКИМИ УГЛЕВОДОРОДАМИ, ВКЛЮЧАЯ ИХ ПРОИЗВОДНЫЕ И ГАЗООБРАЗНЫМИ ВЕЩЕСТВАМИ ИЛИ НЕСМЕШИВАЮЩИМИСЯ ЖИДКОСТЯМИ В Т.Ч. НЕОРГАНИЧЕСКИМИ | 2013 |

|

RU2533124C1 |

| ПИЩЕВОЙ ПРОДУКТ | 2000 |

|

RU2174756C1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| US 7202739 B2, 10.04.2007. | |||

Авторы

Даты

2017-08-03—Публикация

2016-02-24—Подача