Область техники, к которой относится изобретение

Данное раскрытие, в общем, относится к области информационной безопасности и, более конкретно, к детектированию и смягчению вреда от злоумышленного вызова чувствительного кода.

Уровень техники

Область сетевой безопасности становится все более и более важной в современном обществе. Интернет обеспечил возможность взаимного соединения с разными компьютерными сетями во всем мире. В частности, Интернет обеспечивает среду для обмена данными между разными пользователями, соединенными с разными компьютерными сетями через разного типа устройства клиентов. В то время как использование Интернет преобразовало деловое общение и персональную передачу данных, злонамеренные операторы также используют его, как средство для получения несанкционированного доступа к компьютерам и компьютерным сетям и для намеренного или непреднамеренного раскрытия чувствительной информации.

Вредоносное программное обеспечение ("malware"), которое заражает главный компьютер, может быть выполнено с возможностью выполнения любого количества злонамеренных действий, таких как кража чувствительной информации у бизнеса или у отдельных лиц, имеющих дело с главным компьютером, распространение на другие главные компьютеры, и/или помощь при распределенном отказе в атаках на услугу, пересылая спам или злоумышленные послания по электронной почте из главного компьютера и т.д. Следовательно, остаются нерешенными существенные административные проблемы для защиты компьютеров и компьютерных сетей от злоумышленной и непреднамеренной эксплуатации со стороны вредоносного программного обеспечения.

Краткое описание чертежей

Для обеспечения более полного понимания настоящего раскрытия и его свойств, и преимуществ, ссылка будет сделана на следующее описание, которое следует рассматривать совместно с приложенными чертежами, на которых одинаковые номера ссылочных позиций представляют одинаковые части, на которых:

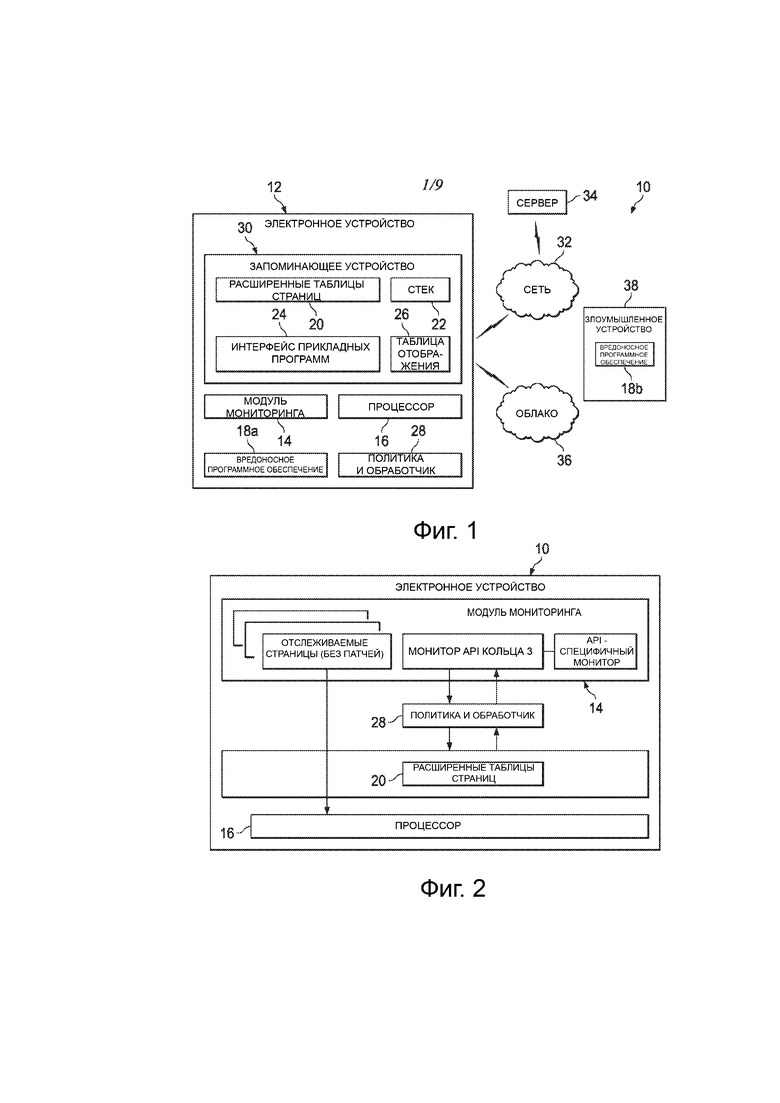

На фиг. 1 показана упрощенная блок-схема системы передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления настоящего раскрытия;

На фиг. 2 показана упрощенная блок-схема части системы передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода в соответствии с вариантом осуществления настоящего раскрытия;

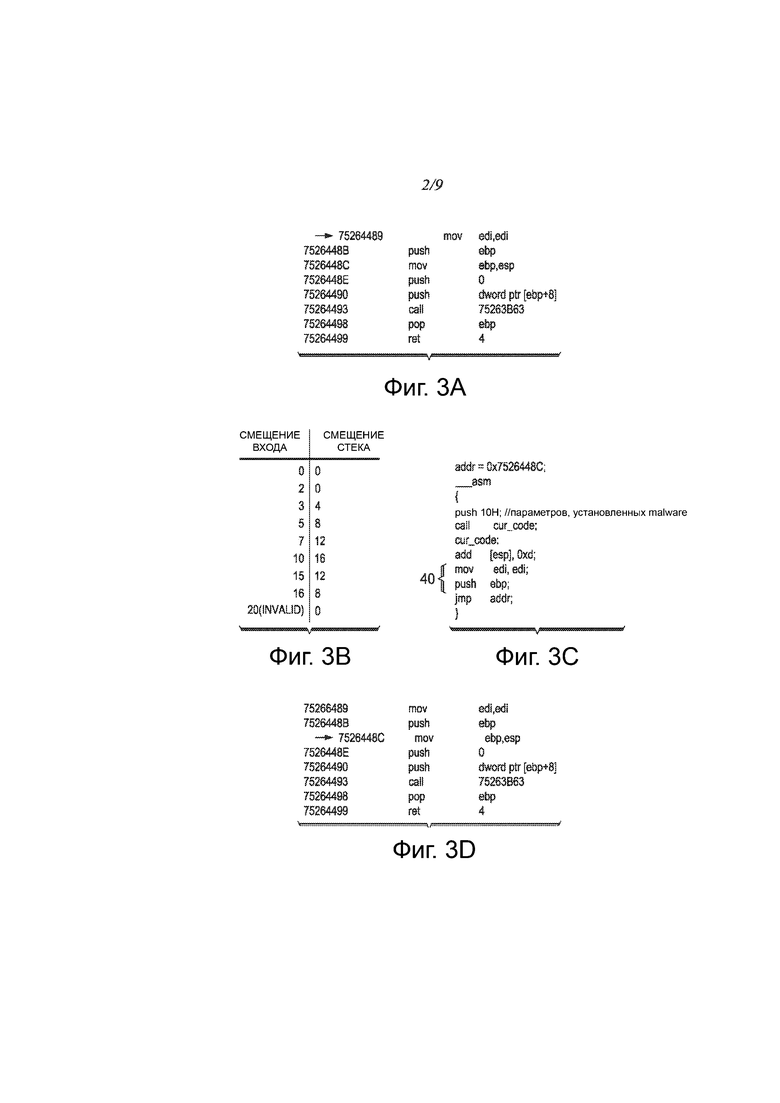

На фиг. 3А показана упрощенная схема примера деталей системы передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода в соответствии с вариантом осуществления настоящего раскрытия;

На фиг. 3B показана упрощенная схема примера деталей системы передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода в соответствии с вариантом осуществления настоящего раскрытия;

На фиг. 3C показана упрощенная схема в качестве примера системы передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода в соответствии с вариантом осуществления настоящего раскрытия;

На фиг. 3D показана упрощенная схема примера деталей системы передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода в соответствии с вариантом осуществления настоящего раскрытия;

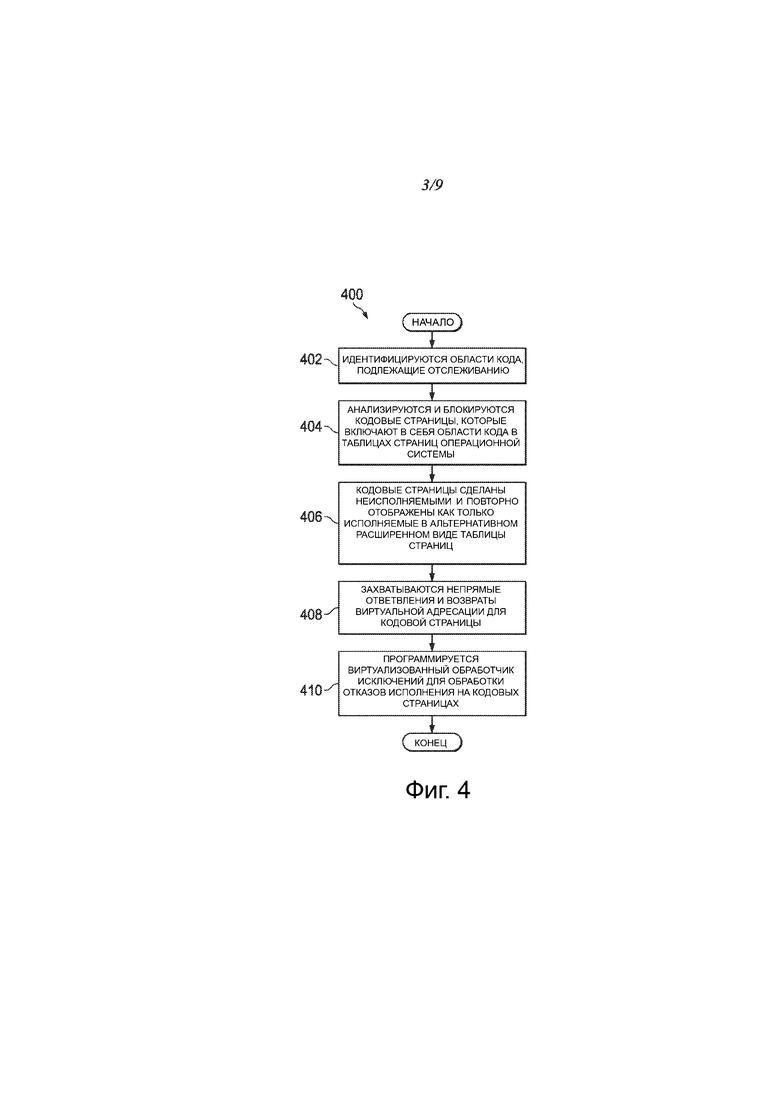

На фиг. 4 показана упрощенная блок-схема последовательности операций, поясняющая потенциальные операции, которые могут быть ассоциированы с системой передачи данных в соответствии с вариантом осуществления;

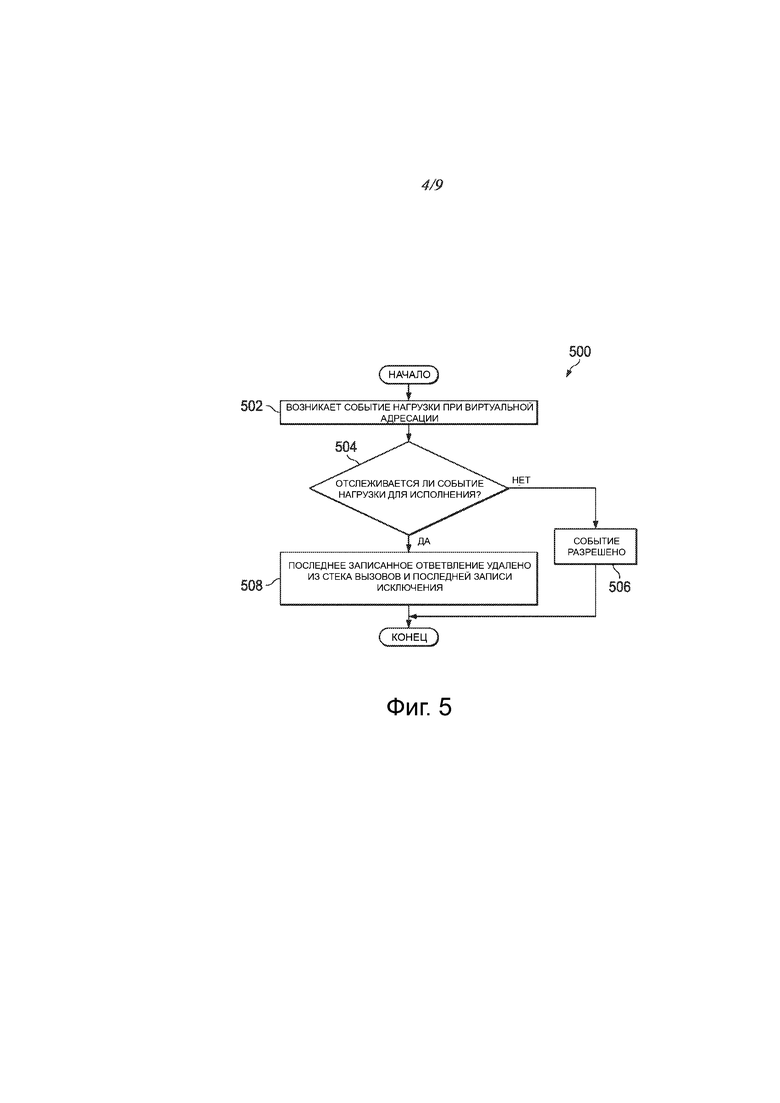

На фиг. 5 показана упрощенная блок-схема последовательности операций, поясняющая потенциальные операции, которые могут быть ассоциированы с системой передачи данных в соответствии с вариантом осуществления;

На фиг. 6 показана упрощенная блок-схема последовательности операций, поясняющая потенциальные операции, которые могут быть ассоциированы с системой передачи данных в соответствии с вариантом осуществления;

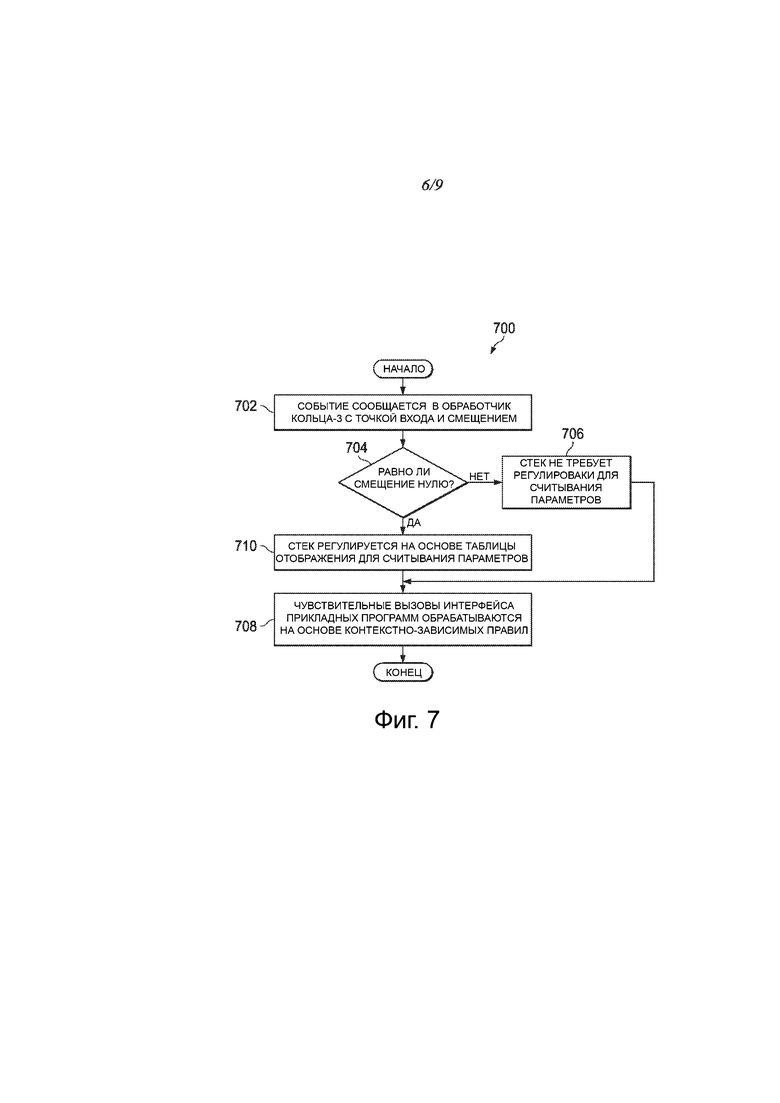

На фиг. 7 показана упрощенная блок-схема последовательности операций, поясняющая потенциальные операции, которые могут быть ассоциированы с системой передачи данных в соответствии с вариантом осуществления;

На фиг. 8 показана блок-схема, поясняющая пример вычислительной системы, которая скомпонована в конфигурации "точка-точка" в соответствии с вариантом осуществления;

На фиг. 9 показана упрощенная блок-схема, ассоциированная с примером системы на кристалле (SOC) окружающей среды ARM, в соответствии с настоящим раскрытием; и

На фиг. 10 показана блок-схема, поясняющая пример ядра процессора в соответствии с вариантом осуществления.

Чертежи не обязательно вычерчены в масштабе, поскольку их размеры могут значительно различаться, без выхода за пределы объема настоящего раскрытия.

Подробное описание изобретения

На фиг. 1 показана упрощенная блок-схема системы 10 передачи данных для детектирования и смягчения вреда от злоумышленных вызовов чувствительного кода, в соответствии с вариантом осуществления настоящего раскрытия. Система 10 передачи данных может включать в себя электронное устройство 12, сервер 34 и облако 36. Электронное устройство 12 может включать в себя модуль 14 мониторинга, процессор 16, политику и обработчик 28, и запоминающее устройство 30. Запоминающее устройство 30 может включать в себя таблицы 20 расширенной страницы (EPT), стек 22, интерфейс 24 прикладных программ (API) и таблицу 26 отображения. В варианте осуществления электронное устройство 12 может включать в себя вредоносное программное обеспечение 18a.

Злоумышленное устройство 38 может включать в себя вредоносное программное обеспечение 18b. Злоумышленное устройство 38 может пытаться ввести malware 18b в электронное устройство 12. Электронное устройство 12, сервер 34, облако 36 и злоумышленное устройство 38 могут быть соединены через сеть 32. В одном примере злоумышленное устройство 38 может быть соединено непосредственно с электронным устройством 12 (например, через соединение типа USB). Злоумышленное устройство 38 может представлять собой любое устройство, которое пытается ввести злоумышленный код (например, вредоносное программное обеспечение 18a или 18b) в электронное устройство 12.

В примерных вариантах осуществления система 10 передачи данных может быть выполнена так, чтобы она включала в себя систему для предоставления возможности детектирования обхода привязок, ориентированного по переключателям программирования (JOP), обратно ориентированного программирования (ROP) и т.д. для вызова чувствительных API, без требования каких-либо привязок или патчей в чувствительном коде API и без какого-либо предварительного знания malware (например, сигнатуры не требуются). Модуль 14 мониторинга может быть выполнен с возможностью пометки кодовых страниц, которые содержат чувствительные кодовые страницы API, как неисполнительные, улучшая, таким образом, возможность удостоверять входы в участки кода, используя исключения виртуализации (#VE). Кроме того, система может использовать возможности фильтрации последней записи исключения (LER) и последней записи ответвления (LBR) для выделения информации о непрямых ответвлениях кольца 3 (режим пользователя) и передачи сигналов о том, что непрямые CALLIJMP или RET (то есть, возврат к вызову), использовались для злоумышленного вызова чувствительного кода API на отслеживаемой странице (через перехват, используя #VE).

Элементы на фиг. 1 могут быть соединены друг с другом через один или больше интерфейсов, использующих любые соответствующие соединения (проводные или беспроводные), которые обеспечивают разные пути к сетям (например, сети 32) передачи данных. Кроме того, любой один или больше из этих элементов по фиг. 1 может быть скомбинирован или удален из архитектуры на основе конкретных требований конфигурации. Система 10 передачи данных может включать в себя конфигурацию, позволяющую выполнять передачу данных, в соответствии с протоколом управления передачей/протоколом Internet (TCP/IP) для передачи или приема пакетов в сети. Система 10 передачи данных также может работать в связи с протоколом дейтаграмм пользователя/IP (UDP/IP) или любым другим соответствующим протоколом, тогда, когда это необходимо и основано на конкретной потребности.

С целью иллюстрации определенного примера технологий системы 10 передачи данных важно понять передачу данных, которая может происходить в сетевой среде. Следующую основополагающую информацию можно рассматривать, как основу, на которой можно правильно пояснить настоящее раскрытие.

Программное обеспечение безопасности может использоваться для отслеживания выполнения чувствительного кода путем применения обходов/привязок для выполнения внутри капсулы чувствительных API. Авторы злоумышленного программного обеспечения хорошо знают об этих технологиях, применяемых программным обеспечением безопасности, и могут детектировать такие привязки путем считывания кода API (например, сравнения кода с изображением на диске или в памяти в инструментах, таких, как GMER, или в других инструментах, для детектирования и удаления руткитов и т.д.) или путем считывания кода и при анализе конкретных структур потока управления в коде API. Мэлвер также может начать выполнение таких чувствительных API путем скачка в середину чувствительных API (например, используя команду jmp) для простого и полного обмана любых обходов/привязок программного обеспечения безопасности. В этом случае, код безопасности просто не видит чувствительные API, которые исполняются злонамеренно, позволяя, таким образом, злонамеренное выполнение, модификации привилегий и организации атаки.

Современные подходы к программному обеспечению могут не детектировать атаки по обходу привязок без полной двоичной трансляции кода обработки, включая в себя чувствительный API код. Во многих случаях, двоичная трансляция не может быть избирательно включена, поскольку привязки API не могут зависеть от того, как их обходят. Следовательно, двоичная трансляция должна быть постоянно активной, что приводит к излишним издержкам, связанным с рабочими характеристиками. Таким образом, необходима система, которая могла бы детектировать атаки пропуска привязок, не требуя, чтобы патчи охватывали чувствительные API и могла бы детектировать поток управления злоумышленными данными в чувствительные API, без требования применения каких-либо патчей или обработки структуры данных или кода.

Система передачи данных для детектирования и смягчения вреда от злоумышленных вызовов чувствительного кода, как представлено в общих чертах на фиг. 1, может решать эти проблемы (и другие). Система 10 передачи данных может быть выполнена так, что она будет включать в себя систему, где модуль 14 мониторинга устанавливает политику для менеджера политики #VE и обработчика (например, политику и обработчик 28). В варианте осуществления менеджер политики #VE и обработчик обновляют EPT (например, EPT 20), администрируемые гипервизором, для того, чтобы устранить привилегии дли исполнения специфичных для API страниц в принятом по умолчанию обзоре EPT и формировать чередующееся отображение для исполнения страниц. Менеджер политики #VE и обработчик обеспечивают возможность предоставления исключения #VE для этих конкретных страниц. Когда возникает исполнение API (при нормальном или злоумышленном исполнении), поступает отчет об ошибке EPT в ненадежном обзоре. Этот отчет может представлять собой нарушение исключения #VE для менеджера #VE и обработчика, и менеджер #VE и обработчик могут отравить это событие в менеджер 14 мониторинга, который инспектирует принятую информацию содержания (например, точку входа, смещение или вызов и т.д.) и вызывает специфичный для API упаковщик или код анализа.

Если точка входа API не находится в правильной точке входа, (то есть, смещение не равно нулю), тогда можно использовать один из двух подходов для определения местоположения параметров, которое вызывающий код может устанавливать поверх стека. В первом подходе таблица отображения (например, таблица 26 отображения), которая отображает смещение входа на смещение стека, используется для отображения смещения входа на смещение стека, которое должно использоваться для доступа к параметрам в стеке. Второй подход позволяет определят местоположение параметров стека на основе смещения входа в отслеживаемый код, после точки входа и используя декодирование инструкций для идентификации операций стека и оценки смещения, необходимого для регулировки стека.

Возвращаясь к инфраструктуре на фиг. 1, здесь показана система 10 передачи данных, в соответствии с примерным вариантом осуществления. В общем, система 10 передачи данных может быть воплощена в любом типе или топологии сетей. Сеть 32 представляет собой последовательность точек или узлов, взаимно соединенных путей передачи данных для приема и передачи пакетов информации, которые распространяются через систему 10 передачи данных. Сеть 32 предлагает создавать интерфейс передачи данных между узлами, и может быть выполнена, как любая локальная вычислительная сеть (LAN), виртуальная локальная вычислительная сеть (VLAN), широкополосная вычислительная сеть (WAN), беспроводная локальная вычислительная сеть (WLAN), городская вычислительная сеть (MAN), Интранет, Экстранет, виртуальная частная сеть (VPN), и любая другая соответствующая архитектура или система, которая способствует передаче данных в сетевой окружающей среде, или любая соответствующая ее комбинация, включая в себя проводную и/или беспроводную передачу данных.

В системе 10 передачи данных сетевой трафик, который включает в себя пакеты, фреймы, сигналы, данные и т.д., может быть передан и принят в соответствии с любыми соответствующими протоколами передачи коммуникационных сообщений. Соответствующие протоколы передачи коммуникационных сообщений могут включать в себя многоуровневую схему, такую как модель взаимного соединения открытых систем (OSI), или любые ее производные или варианты (например, протокол управления передачей/ протокол Internet (TCP/IP), протокол датаграммы пользователя/IP (UDP/IP)). Кроме того, передача радиосигнала через сотовую сеть также может обеспечиваться в системе 10 передачи данных. Соответствующие интерфейсы и инфраструктура могут быть предусмотрены для обеспечения передачи данных в сотовой сети.

Термин "пакет", используемый здесь, относится к модулю данных, который может быть направлен между узлом источника и узлом назначения в сети переключения пакетов. Пакет включает в себя адрес сетевого источника и адрес сетевого назначения. Эти сетевые адреса могут представлять собой адреса соответствующего протокола Интернет (IP) и протокола передачи сообщений TCP/IP. Термин "данные", используемый здесь, относится к любому типу двоичных, цифровых, голосовых, видео данных, текстовых данных или данных сценария, или любому типу исходного или объектного кода, или любой другой соответствующей информации в любом соответствующем формате, которая может быть передана из одной точки в другую в электронных устройствах и/или сетях. Кроме того, сообщения, запросы, отклики и обращения представляют собой форму сетевого трафика и, поэтому, могут содержать пакеты, фреймы, сигналы, данные и т.д.

В примерном воплощении электронное устройство 12, сервер 34 и облако 36 представляют собой сетевые элементы, которые предназначаются для охвата сетевых устройств, серверов, маршрутизаторов, коммутаторов, шлюзов, мостов, балансировщиков нагрузки, процессоров, модулей или любых соответствующих устройств, компонентов, элементов или объектов, работающих для обмена информацией в сетевой среде. Сетевые элементы могут включать в себя любые соответствующие аппаратные, программные модули, компоненты, модули или объекты, которые способствуют их работе, а также соответствующие интерфейсы для приема, передачи и/или другой передачи данных или информации в сетевой среде. Это может включать в себя соответствующие алгоритмы и протоколы передачи данных, которые позволяют выполнять эффективный обмен данными или информацией.

Что касается внутренней структуры, ассоциированной с системой 10a (и 10b) передачи данных, каждое электронное устройство 12, сервер 34 и облако 36 может включать в себя элементы памяти для сохранения информации, предназначенной для использования в представленных здесь операциях. Каждое электронное устройство 12a, сервер 34 и облако 36 может содержать информацию в любом соответствующем элементе памяти (например, в оперативном запоминающем устройстве (RAM), постоянном запоминающем устройстве (ROM), стираемом программируемом ROM (EPROM), электрически стираемом программируемом ROM (EEPROM), специализированной интегральной схеме (ASIC) и т.д.), программном обеспечении, аппаратном обеспечении, встроенном программном обеспечении или в любом другом соответствующем компоненте, устройстве, элементе или объекте, в случае необходимости, и на основании определенных потребностей. Любой из элементов памяти, описанных здесь, следует рассматривать, как охватываемый широким термином "элемент памяти". Кроме того, используемая, отслеживаемая, передаваемая или принимаемая информация в системе 10 передачи данных может быть предусмотрена в любой базе данных, регистре, очереди, таблице, списке управления кэш или в другой структуре сохранения, все из которых могут называться любым соответствующим временным фреймом. Любые такие возможности сохранения также могут быть включены в пределах широкого термина "элемент памяти", используемого здесь.

В определенных примерных вариантах осуществления функции, представленные здесь, могут быть воплощены с помощью логики, кодированной на одном или больше материальных носителях информации (например, встроенная логика, предусмотренная в ASIC, инструкции цифрового сигнального процессора (DSP), программное обеспечение (потенциально включающее в себя объектный код и исходный код) для выполнения процессором или другим аналогичным устройством и т.д.), который может включать в себя непереходный, считываемый компьютером носитель информации. В некоторых из этих случаев элементы памяти могут сохранять данные, используемые для описанных здесь операций. Это включает в себя элементы памяти, которые позволяют сохранять программное обеспечение, логику, код или инструкции процессора, которые выполняются для выполнения действий, описанных здесь.

В примерном воплощении сетевые элементы системы 10 передачи данных, такие как электронное устройство 12, сервер 34 и облако 36, могут включать в себя программные модули (например, модуль 14 мониторинга) для достижения, или стимуляции описанных здесь операций. Такие модули могут быть соответствующим образом скомбинированы, используя любой соответствующий подход, который может быть основан на определенной конфигурации и/или потребностях предоставления. В примерных вариантах осуществления такие операции могут выполняться с помощью аппаратных средств, воплощенных во внешнем источнике для этих элементов, или включенных в некоторое другое сетевое устройство, для достижения предназначенной функции. Кроме того, модули могут быть воплощены, как программное обеспечение, аппаратное средство, встроенное программное обеспечение или любая их соответствующая комбинация. Эти элементы также могут включать в себя программное обеспечение (или рециркулирующее программное обеспечение), которое может координировать работу с другими сетевыми элементами для достижения описанных здесь операций.

Кроме того, каждое электронное устройство 12, сервер 34 и облако 36 может включать в себя процессор, который может выполнять программное обеспечение или алгоритм для выполнения описанных здесь действий. Процессор может выполнять любой тип инструкций, ассоциированных с данными, для достижения представленных здесь детально операций. В одном примере процессор может преобразовывать элемент или изделие (например, данные) из одного состояния или вещи в другое состояние или вещь. В другом примере представленные здесь действия могут быть воплощены с фиксированной логикой или программируемой логикой (например, программное обеспечение/компьютерные инструкции, выполняемое процессором), и элементы, идентифицированные здесь, могут представлять собой определенный тип программируемого процессора, программируемой цифровой логики (например, программируемая пользователем вентильная матрица (FPGA), EPROM, EEPROM) или ASIC, которая включает в себя цифровую логику, программное обеспечение, код, электронные инструкции или любую их соответствующую комбинацию. Любой из этих потенциальных элементов обработки, модулей и устройств, описанных здесь, следует рассматривать, как охватываемый широким термином "процессор".

Электронное устройство 12 может представлять собой сетевой элемент и включает в себя, например, настольные компьютеры, переносные компьютеры, мобильные устройства, карманные персональные компьютеры, смартфоны, планшетные компьютеры или другие аналогичные устройства. Сервер 34 может представлять собой сетевой элемент, такой, как сервер или виртуальный сервер, и может быть ассоциирован с клиентами, потребителями, конечными точками или конечными пользователями, которые желают инициировать обмен данными в системе 10 передачи данных через некоторую сеть (например, сеть 32). Термин "сервер" включает в себя устройства, используемые для обслуживания запросов клиентов и/или выполнения некоторых вычислительных задач от имени клиентов в системе 10 передачи данных. Хотя модуль 14 мониторинга представлен на фиг. 1, как расположенный в пределах электронного устройства 12, это представлено здесь только с целью иллюстрации. Модуль 14 мониторинга может быть скомбинирован или разделен в любой соответствующей конфигурации. Кроме того, модуль 14 мониторинга может быть интегрирован с или распределен в другой сети, доступ к которой осуществляется электронным устройством 12, таким как сервер 32 или облако 36. Облако 36 выполнено с возможностью предоставления услуг "облака" для электронного устройства 12. Услуги "облака" могут быть, в общем, определены, как использование вычислительных ресурсов, которые предоставляют, как услугу через сеть, такую как Интернет. Как правило, расчет, сохранение и сетевые ресурсы предлагаются в инфраструктуре "облака", что эффективно сдвигает рабочую нагрузку из локальной вычислительной сети в сеть облака.

На фиг. 2 показана упрощенная блок-схема части системы 10 передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления настоящего раскрытия. На фиг. 2 иллюстрируется пример операции для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления настоящего раскрытия. Модуль 14 мониторинга может устанавливать политику мониторинга кольца 3 API, как политику и обработчик 28. Политика и обработчик 28 могут обновлять EPT 20 для того, чтобы убрать привилегии для исполнения конкретных страниц API в принятом по умолчанию виде EPT и для формирования альтернативного отображения для выполнения конкретных страниц API. Политика и обработчик 28 также могут обеспечивать доставку по исключению (например, доставка исключения #VE) для конкретных страниц API. Когда происходит исполнение конкретных страниц API, передают отчет об отказе EPT в не доверенном виде. Представленный в отчете отказ представляется, как исключение, и его передают в модуль 14 мониторинга. Модуль 14 мониторинга может инспектировать контекстную информацию, относящуюся к исключению и, если точка входа API не находится на правильной точке входа, то таблица отображения (например, таблица 26 отображения), которая отображает смещение входа относительно смещения стека, может использоваться для отображения смещения входа, которое должно использоваться для доступа к параметрам в стеке (например, стеке 22). Альтернативный подход может состоять в том, чтобы разместить параметры стека на основе смещения для входа в отслеживаемые страницы после точки входа, используя декодирование инструкций для идентификации операции стека и оценки смещения, необходимого для регулировки стека.

На фиг. 3A показана упрощенная схема части системы передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления настоящего раскрытия. На фиг. 3A иллюстрируется нормальный вызов 32-битной функции. Точка входа 0x75264489 входа представлена в отчете, как entrypoint = 0x75264489, смещение OxO. Параметры (не показаны) могут быть установлены функцией вызова. Возвращаясь к фиг. 3B, на фиг. 3B показана упрощенная схема части системы передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления настоящего раскрытия. На фиг. 3B иллюстрируется таблица отображения для 32-битной функции, представленной на фиг. 3B для функции в точке входа 0x75264489.

На фиг. 3C и 3D показаны упрощенные схемы части системы передачи данных для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления настоящего раскрытия. На фиг. 3C иллюстрируется злоумышленный вызов 40 функции, показанной на фиг. 3A. Злоумышленный вызов может переключать прошлый код в середину API по адресу Ox7526448C. Злоумышленный вызов 40 может представлять собой исполнение кода с помощью вредоносного программного обеспечения 18a перед переключением в середину потока инструкций. Обратный вызов осуществляется с точкой входа "0x75264489, смещение "0x3. В этом примере адрес Ox7526448C используется (в данном случае он жестко закодирован) для иллюстрации концепции, однако, эти адреса обычно раскрывают через определенное раскрытие памяти, как часть уязвимости, эксплуатируемой вредоносным программным обеспечением 18a.

Поскольку смещение точки входа составляет 0x3, таблица отображения (например, таблица 26 отображения) может обеспечивать смещение стека, равное 4, которое может использоваться модулем 14 мониторинга, для считывания параметров из стека 22. Следует отметить, что для того, чтобы malware успешно использовало API, malware не должно нарушать стек и следовать договоренности, ожидаемой от API.

На фиг. 4 показан пример блок-схемы последовательности операций, иллюстрирующий возможные операции потока 400, который может быть ассоциирован с детектированием и уменьшением злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления. В варианте осуществления одна или больше операций потока 400 может выполняться модулем 14 мониторинга. В позиции 402, идентифицируют области кода, которые должны отслеживаться. В позиции 404, страницы кода, которые включают в себя области кода в таблицах страниц операционной системы, проверяют и блокируют. В позиции 406, страницы кода делают неисполнительными и повторно отображают, как исполнение только в альтернативном расширенном виде таблицы страниц. В позиции 408 захватывают ответвления непрямой виртуальной адресации и возврата к странице кода. В позиции 410, обработчик исключений виртуализации программируют для обработки отказов исполнения для кодовых страниц.

На фиг. 5 показан пример блок-схемы последовательности операций, иллюстрирующий возможные операции потока 500, которые могут быть ассоциированы с детектированием и уменьшением злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления. В варианте осуществления одна или больше операций потока 500 может выполняться модулем 14 мониторинга. В позиции 502, возникает событие нагрузки виртуальной адресации. В позиции 504 система определяет, отслеживается ли событие нагрузки для исполнения (например, исполнения API). Если событие нагрузки не отслеживается для исполнения, тогда событие разрешено, как в позиции 504. Если событие нагрузки отслеживается для исполнения, то самое последнее записанное ответвление удаляют из стека вызовов, и последнее исключение записывают, как в позиции 508.

На фиг. 6 показан пример блок-схемы последовательности операций, иллюстрирующий возможные операции потока 600, который может быть ассоциирован с детектированием и уменьшением злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления. В варианте осуществления одна или больше операций потока 600 могут выполняться путем отслеживания модулем 14 мониторинга. В позиции 602 происходит отказ исполнения на отслеживаемой странице кода. В позиции 604 определяют причину для отказа исполнения. В позиции 606 считывают самое последнее записанное ответвление из стека вызовов и последнего адреса записи исключения. В позиции 606, последний адрес записи исключения сравнивают с отслеживаемыми страницами областей интерфейса программы приложения. В позиции 608 система определяет, произошел ли отказ выполнения из-за возврата прерывания кольца 0. Если отказ исполнения произошел в результате возврата прерывания кольца 0, тогда генерируется сообщение об ошибке, как в позиции 622. Если отказ исполнения не произошел из-за прерываний кольца 0, тогда система определяет, был ли отслеживаемый интерфейс прикладных программ исполнен в результате ответвления от ненадежного кода, как в 612. Если отслеживаемый интерфейс прикладных программ был выполнен в результате ответвления от ненадежного кода, тогда записывают последний адрес записи исключения, как в позиции 614. Если отслеживаемый интерфейс прикладных программ не был выполнен из-за ответвления от ненадежного кода, тогда система определяет, произошло ли исполнение в точке входа, как в позиции 616. Если исполнение было выполнено в точке входа, тогда последний адрес записи исключения удаляют, и исполнение помечают, как действительная попытка интерфейса прикладных программ, как в позиции 618. Если исполнение не происходило в точке входа, тогда последний адрес записи исключения удаляют, и смещение рассчитывают по точке входа, как в позиции 620.

На фиг. 7 показан пример блок-схемы последовательности операций, иллюстрирующий возможные операции потока 700, которые могут быть ассоциированы с детектированием и уменьшением злоумышленного вызова чувствительного кода, в соответствии с вариантом осуществления. В варианте осуществления одна или больше операций потока 700 может быть выполнена с помощью модуля 14 мониторинга. В позиции 702, о событии докладывают в обработчик кольца 3 с точкой входа и смещением. В позиции 704 система определяет, равно ли смещение нулю. Если смещение равно нулю, тогда не требуется регулировка стека для считывания параметров, как в позиции 706. Если смещение не равно нулю, тогда стек регулируют на основе таблицы отображения для считывания параметров, как в позиции 710. В позиции 708 чувствительные вызовы интерфейса прикладных программ обрабатывают на основе правил, специфичных для контекста.

На фиг. 8 иллюстрируется вычислительная система 800, которая расположена в конфигурации из точки в точку (PtP), в соответствии с вариантом осуществления. В частности, на фиг. 8 показана система, где процессоры, память и устройства I/O взаимно соединены с помощью множества интерфейсов "точка-точка". В общем, один или больше сетевых элементов системы 10 передачи данных может быть выполнен таким же образом или аналогично, как и вычислительная система 800.

Как представлено на фиг. 8, система 800 может включать в себя несколько процессоров, из которых только два процессора 870 и 880, показаны, для ясности. В то время, как показаны два процессора 870 и 880, следует понимать, что вариант осуществления системы 800 также может включать в себя только один такой процессор. Процессоры 870 и 880 каждый может включать в себя набор ядер (то есть, ядер 874A и 874B процессора и ядер 884A и 884B процессора) для выполнения множества потоков программы. Ядра могут быть сконфигурированы для выполнения кода инструкции, используя подход, аналогичный описанному выше со ссылкой на фигуры 1-6. Каждый процессор 870, 880 может включать в себя, по меньшей мере, один совместно используемый кэш 871, 881. Совместно используемый кэш 871, 881 может сохранять данные (например, инструкции), которые используются одним или больше компонентами процессоров 870, 880, такими, как ядра 874 и 884 процессора.

Процессоры 870 и 880 также могут каждый включать в себя логику 872 и 882 интегрированного контроллера памяти (MC) для обмена данными с элементами 832 и 834 памяти. Элементы 832 и/или 834 памяти могут содержать различные данные, используемые процессорами 870 и 880. В альтернативных вариантах осуществления логика 872 и 882 контроллера памяти может представлять собой дискретную логику, отдельную от процессоров 870 и 880.

Процессоры 870 и 880 могут представлять собой процессор любого типа и могут выполнять обмен данными через интерфейс 850 "точка-точка" (PtP), используя схемы 878 и 888 интерфейса точка-в-точку, соответственно. Процессоры 870 и 880 каждый может выполнять обмен данными с набором 890 микросхем через отдельные интерфейсы 852 и 854 точка-точка, используя схемы 876, 886, 894 и 898 интерфейса точка-в-точку. Набор 890 микросхем также может выполнять обмен данными с графической схемой 838 с высокой пропускной способностью через графический интерфейс 839 с высокой пропускной способностью, используя схему 892 интерфейса, которая может представлять собой схему интерфейса PtP. В альтернативных вариантах осуществления любые или все из соединений PtP, представленных на фиг. 8, могут быть воплощены, как многоточечная шина, а не как соединение PtP.

Набор 890 микросхем может находиться в режиме обмена данными с шиной 820 через схему 896 интерфейса. Шина 820 может иметь одно или больше устройств, которые связываются через нее, такие, как мост 818 шины и устройства 816 I/O. Через шину 810, мост 818 шины может связываться с другими устройствами, такими как клавиатура/мышь 812 (или другими устройствами ввода данных, такими, как сенсорный экран, шаровой указатель и т.д.), устройствами 826 передачи данных (такими как модемы, устройства сетевого интерфейса или другие типы устройств передачи данных, которые могут связываться через вычислительную сеть 860), устройствами 814 аудио I/O и/или устройством 828 сохранения данных. Устройство 828 сохранения данных может сохранять код 830, который может выполняться процессорами 870 и/или 880. В альтернативных вариантах осуществления любые части архитектур шины могут быть воплощены с использованием одного или больше соединений PtP.

Вычислительная система, представленная на фиг. 8, представляет собой схематичную иллюстрацию варианта осуществления вычислительной системы, которая может использоваться для воплощения различных вариантов осуществления, описанных здесь. Следует понимать, что различные компоненты представленной на фиг. 8 системы могут быть скомбинированы в виде архитектуры системы на кристалле (SoC) или в любой другой соответствующей конфигурации. Например, раскрытые здесь варианты осуществления могут быть внедрены в мобильные устройства, включающие в себя системы, такие, как сотовые смартфоны, планшетные компьютеры, карманные персональные компьютеры, портативные игровые устройства и т.д. Следует понимать, что в этих мобильных устройствах могут быть предусмотрены архитектуры SoC, по меньшей мере, в некоторых вариантах осуществления.

На фиг. 9 представлена упрощенная блок-схема, ассоциированная с примером окружающей среды SOC 800 ARM, в соответствии с настоящим раскрытием. По меньшей мере, один пример воплощения настоящего раскрытия может включать в себя свойства проверки данных, описанные здесь и компонента ARM. Например, пример фигуры 9 может быть ассоциирован с любым ядром ARM (например, A-9, A-15 и т.д.). Кроме того, архитектура может составлять часть любого типа планшетного устройства, смартфона (включая в себя телефоны Android ™, iPhone ™), iPad ™, Google Nexus ™, Microsoft Surface ™, персональный компьютер, сервер, компоненты видеообработки, переносной компьютер (включая в себя любой тип ноутбуков), систему Ultra book™, любой тип входного устройства с сенсорным вводом и т.д.

В этом примере на фиг. 9 окружающая среда SOC 800 ARM может включать в себя множество ядер 906-907, управление 908 кэш L2, модуль 909 интерфейса шины, кэш 910 L2, модуль 915 графической обработки (GPU), взаимное соединение 902, видеокодек 920 и I/F 925 жидкокристаллического дисплея (LCD), который может быть ассоциирован с интерфейсом процессора мобильной отрасли (MIPI)/соединением мультимедийного интерфейса высокой четкости (HDMI), которые соединяются с LCD.

Окружающая среда SOC 900 ARM также может включать в себя I/F 930 модуля идентичности абонента (SIM), загрузочное постоянное запоминающее устройство (ROM) 935, контроллер 940 синхронного динамического оперативного запоминающего устройства (SDRAM), контроллер 945 памяти типа флэш, главный последовательный периферийный интерфейс (SPI) 950, соответствующее управление 955 питанием, динамическую RAM (DRAM) 960 и память флэш 965. Кроме того, один или больше примеров вариантов осуществления включают в себя одну или больше возможностей передачи данных, интерфейсов и свойств, таких, как примеры Bluetooth ™ 970, 3G модем 975, Система 980 глобальной навигации (GPS) и 902.11 Wi-Fi 985.

Во время работы пример на фиг. 9 может предлагать возможности обработки, вместе с относительно низким потреблением энергии, для обеспечения выполнения расчетов различных типов (например, мобильных вычислений, высокопроизводительных вычислений для цифрового дома, сервера, беспроводной инфраструктуры и т.д.). Кроме того, такая архитектура может обеспечивать возможность работы любого количества программных приложений (например, Android ™, Adobe® Flash® плейер, платформа Java Standard Edition (Java SE), JavaFX, Linux, Microsoft Windows Embedded, Symbian и Ubuntu и т.д.). По меньшей мере, в одном примерном варианте осуществления процессор ядра может воплощать суперскалярный магистральный конвейер, работающий не по-порядку, с соединенным кэш уровня 2 с малой задержкой.

На фиг. 10 иллюстрируется ядро 1000 процессора в соответствии с вариантом осуществления. Ядро 900 процессора может представлять собой ядро для процессора любого типа, такого как микропроцессор, встроенный процессор, цифровой сигнальный процессор (DSP), сетевой процессор или другое устройство, для выполнения кода. Хотя только одно ядро 900 процессора представлено на фиг. 10, процессор, в качестве альтернативы, может включать в себя больше чем одно ядро 1000 процессора, представленное на фиг. 9. Например, ядро 900 процессора представляет один пример варианта осуществления ядер 674a, 874b, 874a и 874b процессоров, показанных и описанных со ссылкой на процессоры 870 и 880 на фиг. 8. Ядро 1000 процессора может представлять собой однопотоковое ядро, или для, по меньшей мере, одного варианта осуществления, ядро 1000 процессора может быть многопотоковым в том, что оно может включать в себя больше, чем один контекст аппаратного потока (или "логического процессора") на ядро.

На фиг. 10 также иллюстрируется запоминающее устройство 1002, соединенное с ядром 1000 процессора, в соответствии с вариантом осуществления. Запоминающее устройство 1002 может представлять собой любое из широкого разнообразия запоминающих устройств (включая в себя различные уровни иерархии запоминающих устройств), как известно, или по-другому доступно для специалистов в данной области техники. Запоминающее устройство 1002 может включать в себя код 1004, который может представлять собой одну или больше инструкций, предназначенных для исполнения ядром 1000 процессора. Ядро 1000 процессора может следовать программной последовательности инструкций, обозначенных кодом 1004. Каждая инструкция входит в предварительную логику 1006 и обрабатывается одним или больше декодерами 1008. Декодер может генерировать, на его выходе, микрооперацию, такую как фиксированной ширины микрооперация в заданном формате, или может генерировать другие инструкции, микроинструкции или сигналы управления, которые отражают инструкцию генерального кода. Предварительная логика 1006 также включает в себя логику 1010 переименования регистра и логику 1012 планирования, которые, в общем, выделяют ресурсы и запрашивают операции, соответствующие инструкциям для исполнения.

Ядро 1000 процессора также может включать в себя исполнительную логику 1014, имеющую набор исполнительных модулей 1016-1 - 1016-N. Некоторые варианты осуществления могут включать в себя множество исполнительных модулей, специализированных для конкретных функций или наборов функций. Другие варианты осуществления могут включать в себя только один исполнительный модуль или один исполнительный модуль, который может выполнять определенную функцию. Исполнительная логика 1014 выполняет операции, установленные инструкциями кода.

После завершения исполнения операций, установленных в инструкциях кода, логика 1018 выходной обработки может завершать инструкции кода 1004. В одном варианте осуществления ядро 1000 процессора позволяет выполнять операции не по порядку, но требует завершения инструкций по порядку. Логика 1020 завершения может принимать множество известных форм (например, буферы изменения порядка и т.п.). Таким образом, ядро 1000 процессора преобразуется во время выполнения кода 1004, по меньшей мере, с точки зрения выхода, генерируемого декодером, аппаратными регистрами и таблицами, используемыми логикой 1010 переименования регистра, и любыми регистрами (не показаны), модифицированными исполнительной логикой 1014.

Хотя это не представлено на фиг. 10, процессор может включать в себя другие элементы на кристалле с ядром 1000 процессора, по меньшей мере, некоторые из которых были показаны и описаны здесь со ссылкой на фиг. 8. Например, как показано на фиг. 8, процессор может включать в себя логику управления запоминающим устройством вместе с ядром 1000 процессора. Процессор может включать в себя логику управления I/O и/или может включать в себя логику управления I/O, интегрированную с логикой управления памятью.

Следует отметить, что на основании примеров, представленных здесь, может быть описано взаимодействие с точки зрения двух, трех или больше сетевых элементов. Однако это было выполнено только с целью ясности и для примера. В определенных случаях было бы проще описать одну или больше функций из заданного набора потоков, со ссылкой только на ограниченное количество сетевых элементов. Следует понимать, что система 10 передачи данных и ее описание могут быть непосредственно масштабируемыми, и в них может размещаться большое количество компонентов, а также в них могут применяться более сложные/высокотехнологичные компоновки и конфигурации. В соответствии с этим, представленные примеры не должны ограничивать объем или сдерживать широкое описание системы 10 передачи данных и потенциально могут применяться для множества других архитектур.

Также важно отметить, что среди операций на предшествующих блок-схемах последовательности операций (то есть, на фиг. 4-7) иллюстрируются только некоторые из возможных сценариев корреляции, и структуры могут быть выполнены системой 10 передачи данных или в пределах этой системы. Некоторые из этих операций могут быть удалены или могут быть устранены, когда это соответствует, или эти операции могут быть модифицированы или существенно изменены без выхода за пределы объема настоящего раскрытия. Кроме того, множество из них были описаны, как исполняемые одновременно с, или параллельно с, одной или больше дополнительными операциями. Однако временные характеристики этих операций могут существенно изменяться. Предшествующие потоки операций были предложены с целью примера и обсуждения. Существенная гибкость обеспечивается системой 10 передачи данных в том, что любые соответствующие компоновки, хронологии, конфигурации и механизмы временной синхронизации могут быть обеспечены без выхода за пределы описания настоящего раскрытия.

Хотя настоящее раскрытие было подробно описано со ссылкой на конкретные компоновки и конфигурации, эти примеры могут существенно изменяться, без выхода за пределы объема настоящего раскрытия. Кроме того, некоторые компоненты могут быть скомбинированы, разделены, устранены или добавлены на основе конкретных потребностей и вариантов осуществления. Кроме того, хотя система 10 передачи данных была представлена со ссылкой на конкретные элементы и операции, которые способствуют обработке передачи данных, эти элементы и операции могут быть заменены любой соответствующей архитектурой, протоколами и/или процессами, которые достигают предназначенной функциональности системы 10 передачи данных.

Множество других изменений, замен, вариаций и модификаций могут быть выполнены специалистом в данной области техники, и при этом предполагается, что настоящее раскрытие охватывает все такие изменения, замены, вариации и модификации, как попадающие в пределы объема приложенной формулы изобретения. Для помощи Офису по регистрации патентов и товарных знаков США (USPTO) и, кроме того, любым читателям любого патента, выданного по данной заявке, при интерпретации приложенной здесь формулы изобретения, Заявитель желает отметить, что Заявитель: (a) не стремится, чтобы любые из приложенных пунктов формулы изобретения ссылались на шестой параграф (6) 35 USC, параграф 112, в том виде, как она существует на дату ее подачи, если только слова "средство для" или "этап для" не будут, в частности, использоваться в определенных пунктах формулы изобретения; и (b) не предполагает ни одним из заявлений в описании ограничение данного раскрытия каким-либо образом, которое не отражено по-другому в приложенной формуле изобретения.

Другие замечания и примеры

Пример С1 представляет собой, по меньшей мере, один считываемый устройством накопитель информации, имеющий одну или больше инструкций, которые при их исполнении, по меньшей мере, одним процессором обеспечивают идентификацию, по меньшей мере, одним процессором областей кода, которые следует отслеживать, зондирование и блокирование кодовых страниц, которые включают в себя идентифицированные области кода, и повторное отображение кодовых страниц, только как исполнительные.

В Примере C2 предмет изобретения по примеру C1, в случае необходимости, может включать в себя, где кодовые страницы повторно отображены, как исполнительные, только в альтернативном расширенном виде таблицы страницы.

В Примере C3 предмет изобретения по любому одному из Примеров C1-C2, в случае необходимости, может включать в себя, где инструкции, при их исполнении, по меньшей мере, одним процессором, дополнительно обеспечивают захват, по меньшей мере, одним процессором, непрямых виртуальных ответвлений адресации и возврата к кодовым страницам.

В Примере C4 предмет изобретения по любому одному из Примеров C1-C3, в случае необходимости, может включать в себя, где инструкции при их исполнении, по меньшей мере, одним процессором, дополнительно обеспечивают, по меньшей мере, прием одним процессором запроса на исполнение интерфейса прикладных программ для кодовых страниц и генерирование отказа исполнения в ответ на запрос.

В Примере C5 предмет изобретения по любому одному из Примеров C1-C4, в случае необходимости, может включать в себя, где инструкции при их исполнении, по меньшей мере, одним процессором, дополнительно обеспечивают, по меньшей мере, одним процессором обработку отказов исполнения на кодовых страницах с виртуализированным обработчиком исключений.

В Примере C6 предмет изобретения по любому одному из Примеров C1-C5, в случае необходимости, может включать в себя, где отказ исполнения представляет собой отказ расширенной таблицы страницы.

В Примере C7 предмет изобретения по любому одному из Примеров C1-C6, в случае необходимости, может включать в себя, где инструкции при их исполнении, по меньшей мере, одним процессором, дополнительно обеспечивают инспекцию, по меньшей мере, одним процессором контекстной информации, относящейся к отказу исполнения для определения, является ли точка входа для запроса на исполнение интерфейса прикладных программ действительной.

В Примере C8 предмет изобретения по любому одному из Примеров C1-C7, в случае необходимости, может включать в себя, в случае, где инструкции при их исполнении, по меньшей мере, одним процессором, дополнительно обеспечивают, по меньшей мере, отображение одним процессором смещения входа на смещение стека, если точка входа не является действительной.

В Примере Al устройство может включать в себя модуль мониторинга, где модуль мониторинга выполнен с возможностью: идентификации областей кода, которые следует проверять, зондирования и блокирования кодовых страниц, которые включают в себя идентифицированные области кода, и повторного отображения кодовых страниц, только как исполнительные.

В Примере, A2, предмет изобретения Примера Al может, в случае необходимости, включать в себя, где модуль мониторинга дополнительно выполнен с возможностью повторного отображения кодовых страниц, как исполнительные только в расширенном альтернативном виде таблицы страниц.

В Примере A3 предмет изобретения по любому из Примеров A1-A2 может в случае необходимости включать в себя, где модуль мониторинга дополнительно выполнен с возможностью захвата опосредованных виртуальных ответвлений адресации и возврата для кодовых страниц.

В Примере A4 предмет изобретения по любому из Примеров A1-A3 может, в случае необходимости, включать в себя, где модуль мониторинга, дополнительно выполнен с возможностью принимать запрос исполнения прикладного программного интерфейса кодовых страниц и генерировать отказ исполнения в ответ на запрос.

В Примере A5 предмет изобретения по любому из Примеров A1-A4 может, в случае необходимости, включать в себя, где модуль мониторинга дополнительно выполнен с возможностью обрабатывать отказы исполнения на кодовых страницах с виртуализированным обработчиком исключений.

В Примере A6 предмет изобретения по любому из Примеров A1-A5 может, в случае необходимости, включать в себя, где отказ исполнения представляет собой отказ расширенной таблицы страницы.

В Примере A7 предмет изобретения по любому из Примеров A1-A6 может, в случае необходимости, включать в себя, где модуль мониторинга дополнительно выполнен с возможностью инспектировать контекстную информацию, относящуюся к отказу исполнения, чтобы определить, является ли действительной точка входа для запроса выполнения прикладного программного интерфейса.

В Примере A8 предмет изобретения по любому из Примеров A1-A7 может, в случае необходимости, включать в себя, где модуль мониторинга дополнительно выполнен с возможностью отображения смещения входа на смещение стека, если точка входа не действительна.

Пример М 1 представляет собой пример способа, включающего в себя идентификацию областей кода, которые должны отслеживаться, зондирование и фиксацию кодовых страниц, которые включают в себя идентифицированные области кода, и повторное отображение кодовых страниц, как только исполнительные.

В Примере M2 предмет изобретения по примеру М 1 может, в случае необходимости, включать в себя, где кодовые страницы повторно отображаются как исполнительные только в альтернативном расширенном виде таблицы страницы.

В Примере M3 предмет изобретения по любому из Примеров M1-M2 может, в случае необходимости, включать в себя захват опосредованных виртуальных ответвлений адресации и возвраты для кодовых страниц.

В Примере M4 предмет изобретения по любому из Примеров M1-M3 может, в случае необходимости, включать в себя прием запроса исполнения прикладного программного интерфейса для кодовых страниц и генерирования отказа исполнения в ответ на запрос.

В Примере M5 предмет изобретения по любому из Примеров M1-M4 может, в случае необходимости, включать в себя обработку отказов исполнения на кодовых страницах с виртуализированным обработчиком исключений.

В Примере M6 предмет изобретения по любому из Примеров M1-M5 может, в случае необходимости, включать в себя, где отказ исполнения представляет собой отказ расширенной таблицы страницы.

В Примере M7 предмет изобретения по любому из Примеров M1-M6 может, в случае необходимости, включать в себя инспектирование контекстной информации, относящейся к отказу исполнения, для определения, действительна ли точка входа для запроса исполнения прикладного программного интерфейса, и отображения смещения записи на смещение пакета, если точка входа не действительна.

Пример S1 представляет собой систему для детектирования и смягчения вреда от злоумышленного вызова чувствительного кода, система включающая в себя модуль мониторинга, выполненный с возможностью идентифицировать области кода, предназначенные для мониторинга, зондирования и блокирования кодовых страниц, которые включают в себя идентифицированные области кода, и повторное отображение, кодовых страниц, только как исполнительные, где кодовые страницы повторно отображают, только как исполнительные, в альтернативном, расширенном виде таблицы страницы.

В Примере S2 предмет изобретения по Примеру S1 может, в случае необходимости, включать в себя модуль мониторинга, дополнительно выполненный с возможностью принимать запрос исполнения прикладного программного интерфейса кодовых страниц, генерировать отказ исполнения в ответ на запрос и инспектировать контекстную информацию, относящуюся к отказу исполнения, для определения, является ли действительной точка входа для запроса выполнения прикладного программного интерфейса.

Пример X1 представляет собой считываемый устройством носитель информации, включающий в себя считываемые устройством инструкции для воплощения способа или реализации устройства по любому из Примеров A1-A8, или M1-M7. Пример Y1 представляет собой устройство, содержащее средство для исполнения по любому из способов по примерам M1-M7. В Примере Y2 предмет изобретения по Примеру Y1 может, в случае необходимости, включать в себя средство для исполнения способа, содержащего процессор и запоминающее устройство. В Примере Y3 предмет изобретения Примера Y2 может, в случае необходимости, включать в себя запоминающее устройство, содержащее считываемые устройством инструкции.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА И СПОСОБ АВТОМАТИЧЕСКОЙ ОБРАБОТКИ СИСТЕМНЫХ ОШИБОК ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ | 2012 |

|

RU2521265C2 |

| ИНТЕРФЕЙС ПРОГРАММИРОВАНИЯ ДЛЯ КОМПЬЮТЕРНОЙ ПЛАТФОРМЫ | 2004 |

|

RU2365978C2 |

| Способ передачи управления между адресными пространствами | 2016 |

|

RU2634172C1 |

| Система и способ обнаружения вредоносного кода в файле | 2016 |

|

RU2637997C1 |

| Способ выполнения инструкций в системной памяти | 2016 |

|

RU2623883C1 |

| ОТОБРАЖЕНИЕ ДОСТОВЕРНОСТИ ИЗ ВЫСОКОНАДЕЖНОЙ СРЕДЫ НА НЕЗАЩИЩЕННУЮ СРЕДУ | 2004 |

|

RU2390836C2 |

| ОТЛАДКА МАШИННОГО КОДА ПУТЕМ ПЕРЕХОДА ОТ ИСПОЛНЕНИЯ В СОБСТВЕННОМ РЕЖИМЕ К ИСПОЛНЕНИЮ В ИНТЕРПРЕТИРУЕМОМ РЕЖИМЕ | 2014 |

|

RU2668973C2 |

| СПОСОБ ПЕРЕДАЧИ УПРАВЛЕНИЯ МЕЖДУ ОБЛАСТЯМИ ПАМЯТИ | 2014 |

|

RU2580016C1 |

| БРОКЕР И ПРОКСИ ОБЕСПЕЧЕНИЯ БЕЗОПАСТНОСТИ ОБЛАЧНЫХ УСЛУГ | 2014 |

|

RU2679549C2 |

| Эмулятор и способ эмуляции | 2020 |

|

RU2757409C1 |

Изобретение относится к области информационной безопасности. Технический результат заключается в защите чувствительного кода от попыток исполнения с ненадлежащей точкой входа API без излишних издержек. Раскрыт по меньшей мере один считываемый компьютером носитель информации, содержащий одну или более инструкций, которые при их исполнении по меньшей мере одним процессором вызывают: идентификацию областей кода в расширенной таблице страниц, которая включает в себя страницы чувствительного кода прикладного программного интерфейса (API), подлежащие отслеживанию; зондирование и блокирование кодовых страниц, которые включают в себя идентифицированные области кода, и повторное отображение упомянутых кодовых страниц как только исполняемых в альтернативном виде расширенной таблицы страниц; обнаружение загрузки страницы, причем загрузка страницы относится к странице, которая не включает в себя надлежащую точку входа API; определение, на основе обнаружения загрузки страницы, относящейся к странице, которая не включает в себя надлежащую точку входа API, из расширенной таблицы страниц, подлежит ли отслеживанию упомянутая страница; и генерирование, на основе определения, что страница подлежит отслеживанию, отказа исполнения. 4 н. и 15 з.п. ф-лы, 13 ил.

1. По меньшей мере один считываемый компьютером носитель информации, содержащий одну или более инструкций, которые при их исполнении по меньшей мере одним процессором вызывают:

идентификацию областей кода в расширенной таблице страниц, которая включает в себя страницы чувствительного кода прикладного программного интерфейса (API), подлежащие отслеживанию;

зондирование и блокирование кодовых страниц, которые включают в себя идентифицированные области кода, и

повторное отображение упомянутых кодовых страниц как только исполняемых в альтернативном виде расширенной таблицы страниц;

обнаружение загрузки страницы, причем загрузка страницы относится к странице, которая не включает в себя надлежащую точку входа API;

определение, на основе обнаружения загрузки страницы, относящейся к странице, которая не включает в себя надлежащую точку входа API, из расширенной таблицы страниц, подлежит ли отслеживанию упомянутая страница; и

генерирование, на основе определения, что страница подлежит отслеживанию, отказа исполнения.

2. По меньшей мере один считываемый компьютером носитель информации по п. 1, дополнительно содержащий одну или более инструкций, которые при их исполнении по меньшей мере одним процессором вызывают:

захват ответвлений и возвратов непрямой виртуальной адресации для кодовых страниц.

3. По меньшей мере один считываемый компьютером носитель информации по п. 1, дополнительно содержащий одну или более инструкций, которые при их исполнении по меньшей мере одним процессором вызывают:

обработку отказов исполнения на кодовых страницах с помощью виртуализированного обработчика исключений.

4. По меньшей мере один считываемый компьютером носитель информации по п. 1, в котором отказ исполнения представляет собой отказ расширенной таблицы страниц.

5. По меньшей мере один считываемый компьютером носитель информации по п. 1, дополнительно содержащий одну или более инструкций, которые при их исполнении по меньшей мере одним процессором вызывают:

инспектирование контекстной информации, относящейся к отказу исполнения, для определения, является ли действительной точка входа для запроса исполнения прикладного программного интерфейса.

6. По меньшей мере один считываемый компьютером носитель информации по п. 5, дополнительно содержащий одну или более инструкций, которые при их исполнении по меньшей мере одним процессором вызывают:

отображение смещения входа на смещение стека, если точка входа недействительна.

7. Устройство для защиты чувствительного кода, содержащее:

модуль мониторинга, выполненный с возможностью:

идентификации областей кода в расширенной таблице страниц, которые включают в себя страницы чувствительного кода API, подлежащие отслеживанию;

зондирования и блокирования кодовых страниц, которые включают в себя идентифицированные области кода; и

повторного отображения кодовых страниц как только исполняемых в альтернативном виде расширенной таблицы страниц,

обнаружения загрузки страницы, причем загрузка страницы относится к странице, которая не включает в себя надлежащую точку входа API;

определения, на основе обнаружения загрузки страницы, относящейся к странице, которая не включает в себя надлежащую точку входа API, из расширенной таблицы страниц, подлежит ли отслеживанию упомянутая страница; и

генерирования, на основе определения, что страница подлежит отслеживанию, отказа исполнения.

8. Устройство по п. 7, в котором модуль мониторинга дополнительно выполнен с возможностью:

захвата ответвлений и возвратов непрямой виртуальной адресации для кодовых страниц.

9. Устройство по п. 7, в котором модуль мониторинга дополнительно выполнен с возможностью:

обработки отказов исполнения на кодовых страницах с помощью виртуализированного обработчика исключений.

10. Устройство по п. 7, в котором отказ модуля мониторинга представляет собой отказ расширенной таблицы страниц.

11. Устройство по п. 7, в котором модуль мониторинга дополнительно выполнен с возможностью:

инспектирования контекстной информации, относящейся к отказу исполнения, для определения, является ли действительной точка входа для запроса исполнения прикладного программного интерфейса.

12. Устройство по п. 11, в котором модуль мониторинга дополнительно выполнен с возможностью:

отображения смещения входа на смещение стека, если точка входа недействительна.

13. Способ защиты чувствительного кода, содержащий этапы, на которых:

идентифицируют области кода в расширенной таблице страниц, которая включает в себя страницы чувствительного кода API , подлежащие отслеживанию;

зондируют и фиксируют кодовые страницы, которые включают в себя идентифицированные области кода; и

повторно отображают кодовые страницы как только исполняемые в альтернативном виде расширенной таблицы страниц,

обнаруживают загрузку страницы, причем загрузка страницы относится к странице, которая не включает в себя надлежащую точку входа API;

определяют, на основе обнаружения загрузки страницы, относящейся к странице, которая не включает в себя надлежащую точку входа API, из расширенной таблицы страниц, подлежит ли отслеживанию упомянутая страница; и

генерируют, на основе определения, что страница подлежит отслеживанию, отказ исполнения.

14. Способ по п. 13, дополнительно содержащий этап, на котором:

захватывают ответвления и возвраты непрямой виртуальной адресации для кодовых страниц.

15. Способ по п. 13, дополнительно содержащий этап, на котором:

обрабатывают отказы исполнения на кодовых страницах с помощью виртуализированного обработчика исключений.

16. Способ по п. 13, в котором отказ исполнения представляет собой отказ расширенной таблицы страниц.

17. Способ по п. 13, дополнительно содержащий этапы, на которых:

инспектируют контекстную информацию, относящуюся к отказу исполнения, для определения, является ли действительной точка входа для запроса исполнения прикладного программного интерфейса; и

отображают смещение записи на смещение стека, если точка входа недействительна.

18. Система для защиты чувствительного кода, содержащая:

модуль мониторинга, выполненный с возможностью:

идентификации областей кода в расширенной таблице страниц, которые включают в себя страницы чувствительного кода API, подлежащие отслеживанию;

зондирования и блокирования кодовых страниц, которые включают в себя идентифицированные области кода; и

повторного отображения кодовых страниц как только исполняемых, причем кодовые страницы повторно отображаются как только исполняемые в альтернативном виде расширенной таблицы страниц,

обнаружения загрузки страницы, причем загрузка страницы относится к странице, которая не включает в себя надлежащую точку входа API;

определения, на основе обнаружения загрузки страницы, относящейся к странице, которая не включает в себя надлежащую точку входа API, из расширенной таблицы страниц, подлежит ли отслеживанию упомянутая страница; и

генерирования, на основе определения, что страница подлежит отслеживанию, отказа исполнения.

19. Система по п. 18, характеризующаяся тем, что выполнена с возможностью:

инспекции контекстной информации, относящейся к отказу исполнения, для определения, является ли действительной точка входа для запроса исполнения прикладного программного интерфейса.

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 7984304 B1, 19.07.2011 | |||

| СИСТЕМА И СПОСОБ ЗАЩИТЫ КОМПЬЮТЕРНОЙ СИСТЕМЫ ОТ АКТИВНОСТИ ВРЕДОНОСНЫХ ОБЪЕКТОВ | 2011 |

|

RU2468427C1 |

Авторы

Даты

2018-09-04—Публикация

2015-08-26—Подача