ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

1. ОБЛАСТЬ ИЗОБРЕТЕНИЯ

[001] Настоящее изобретение относится к технологии жидкокристаллических дисплеев и, более конкретно, к подложке матрицы и способу ее изготовления.

2. ОПИСАНИЕ УРОВНЯ ТЕХНИКИ

В настоящее время, жидкокристаллические дисплеи (LCD) на тонкопленочных транзисторах (TFT) получили широкое применение. Соответствующие напряжения электродов пикселя обычно управляются несколькими TFT на подложке матрицы для управления выравниванием жидких кристаллов и для соответствующего отображения. Что касается традиционного процесса изготовления подложек матрицы, то, поскольку конструкция подложки матрицы является сложной, как правило, необходимо применять пять или четыре маски для выполнения процесса травления.

Однако, поскольку количество масок, используемых в процессе изготовления подложек матрицы, является большим, процесс изготовления является длительным, что приводит к увеличению расходов на изготовление.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Настоящее изобретение относится к подложке матрицы и способу ее изготовления для улучшения времязатратного процесса изготовления таким образом, чтобы снизить расходы на изготовление.

В одном аспекте способ изготовления подложек матрицы включает: осаждение проводящего слоя на подложку и формирование трех полюсов по меньшей мере одного тонкопленочного транзистора (TFT), первой сигнальной линии и второй сигнальной линии путем травления проводящего слоя посредством первой маски, причем первая сигнальная линия содержит первую часть и вторую часть, соответственно расположенные на двух сторонах второй сигнальной линии; последовательное осаждение промежуточного слоя, и формирование первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски; и осаждение проводящего электрода, и формирование по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски.

При этом первая часть первой сигнальной линии электрически соединена с первым полюсом TFT, вторая сигнальная линия электрически соединена со вторым полюсом TFT, и промежуточный слой содержит изолирующий слой, активный слой, слой омического контакта и пассивирующий слой, уложенные последовательно; причем этап формирования первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски дополнительно включает формирование второй соединительной перемычки, соединяющей второй полюс и третий полюс TFT, путем травления промежуточного слой посредством второй маски; этап формирования по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски дополнительно включает разъединение проводящего электрода, пассивирующего слоя и второго полюса и третьего полюса, соответствующего слою омического контакта, путем травления второй соединительной перемычка посредством третьей маски.

При этом этап формирования второй соединительной перемычки, соединяющей второй полюс и третий полюс TFT, путем травления промежуточного слоя посредством второй маски дополнительно включает: применение HF для травления краев пассивирующего слоя и изолирующего слоя второй соединительной перемычки таким образом, чтобы активный слой и слой омического контакта второй соединительной перемычки выступали наружу с формированием по меньшей мере одного контактного кольца.

При этом проводящий электрод на второй соединительной перемычке расположен на контактном кольце таким образом, что проводящий электрод электрически соединен с контактным кольцом, вторым полюсом и третьим полюсом.

При этом этап формирования первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски дополнительно включает формирование изолирующей структуры емкости на первой части путем травления промежуточного слоя посредством второй маски; этап формирования по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски дополнительно включает формирование электрод накопительной емкости на изолирующей структуре емкости путем травления проводящего электрода посредством третьей маски.

При этом первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой сигнальную линию и вторая сигнальная линия представляет собой линию передачи данных.

При этом первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой линию передачи данных и вторая сигнальная линия представляет собой сигнальную линию.

В другом аспекте подложка матрицы содержит: подложку; три полюса по меньшей мере одного TFT на подложке, первую сигнальную линию, и вторую сигнальная линия, причем первая сигнальная линия содержит первую часть и вторую часть, соответственно расположенные на двух сторонах второй сигнальной линии; первую соединительную перемычку между первой частью и второй частью, причем первая соединительная перемычка изолирована от второй сигнальной линии; и по меньшей мере один электрод пикселя и соединительную линию на первой соединительной перемычке, причем соединительная линия электрически соединяет первую часть и вторую часть.

При этом первая часть первой сигнальной линии электрически соединена с первым полюсом TFT; подложка матрицы дополнительно содержит вторую соединительную перемычку между вторым полюсом и третьим полюсом TFT, первый проводящий электрод и второй проводящий электрод на второй соединительной перемычке, причем вторая соединительная перемычка содержит изолирующий слой, активный слой, слой омического контакта и пассивирующий слой, причем две части пассивирующего слоя и слоя омического контакта второй соединительной перемычки, разделенные областью разъединения, расположены в соответствии со вторым полюсом и третьим полюсом, причем первый проводящий электрод электрически соединен со вторым полюсом, активным слоем и второй сигнальной линией, и проводящий электрод электрически соединен с третьим полюсом, активным слоем и электродом пикселя.

При этом активный слой и слой омического контакта второй соединительной перемычки выступают наружу с формированием по меньшей мере одного контактного кольца.

При этом проводящий электрод на второй соединительной перемычке расположен на контактном кольце таким образом, что проводящий электрод электрически соединен с контактным кольцом, вторым полюсом и третьим полюсом.

При этом подложка матрицы дополнительно содержит изолирующую структуру емкости и электрод накопительной емкости, расположенные на первой части последовательно.

При этом первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой сигнальную линию и вторая сигнальная линия представляет собой линию передачи данных.

При этом первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой линию передачи данных и вторая сигнальная линия представляет собой сигнальную линию.

В другом аспекте подложка матрицы изготовлена посредством способа изготовления. Способ включает: осаждение проводящего слоя на подложку и формирование трех полюсов по меньшей мере одного тонкопленочного транзистора (TFT), первой сигнальной линии и второй сигнальной линии путем травления проводящего слоя посредством первой маски, причем первая сигнальная линия содержит первую часть и вторую часть, соответственно расположенные на двух сторонах второй сигнальной линии; последовательное осаждение промежуточного слоя, и формирование первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски; и осаждение проводящего электрода, и формирование по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски.

При этом первая часть первой сигнальной линии электрически соединена с первым полюсом TFT, вторая сигнальная линия электрически соединена со вторым полюсом TFT, и промежуточный слой содержит изолирующий слой, активный слой, слой омического контакта и пассивирующий слой, уложенные последовательно; причем этап формирования первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски дополнительно включает формирование второй соединительной перемычки, соединяющей второй полюс и третий полюс TFT, путем травления промежуточного слой посредством второй маски; этап формирования по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски дополнительно включает разъединение проводящего электрода, пассивирующего слоя и второго полюса и третьего полюса, соответствующего слою омического контакта, путем травления второй соединительной перемычка посредством третьей маски.

При этом этап формирования второй соединительной перемычки, соединяющей второй полюс и третий полюс TFT, путем травления промежуточного слоя посредством второй маски дополнительно включает: применение HF для травления краев пассивирующего слоя и изолирующего слоя второй соединительной перемычки таким образом, чтобы активный слой и слой омического контакта второй соединительной перемычки выступали наружу с формированием по меньшей мере одного контактного кольца.

При этом проводящий электрод на второй соединительной перемычке расположен на контактном кольце таким образом, что проводящий электрод электрически соединен с контактным кольцом, вторым полюсом и третьим полюсом.

При этом этап формирования первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски дополнительно включает формирование изолирующей структуры емкости на первой части путем травления промежуточного слоя посредством второй маски; этап формирования по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски дополнительно включает формирование электрод накопительной емкости на изолирующей структуре емкости путем травления проводящего электрода посредством третьей маски.

При этом первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой сигнальную линию и вторая сигнальная линия представляет собой линию передачи данных.

С учетом вышеописанного, первая сигнальная линия подложки матрицы содержит две секции, соответственно расположенные на двух сторонах второй сигнальной линии. Затем, соединительную линию, присоединенную к первой сигнальной линии, формируют в последующем процессе с использованием маски. Таким образом, первая сигнальная линия может быть нормально расположена, и первая сигнальная линия и вторая сигнальная линия могут быть сформированы посредством одного процесса с использованием маски, и, таким образом, нет необходимости в двух отдельных процессах с использованием маски. Таким образом, количество процессов с использованием маски может быть уменьшено для экономии времени и расходов на изготовление.

КРАТКОЕ ОПИСАНИЕ ГРАФИЧЕСКИХ МАТЕРИАЛОВ

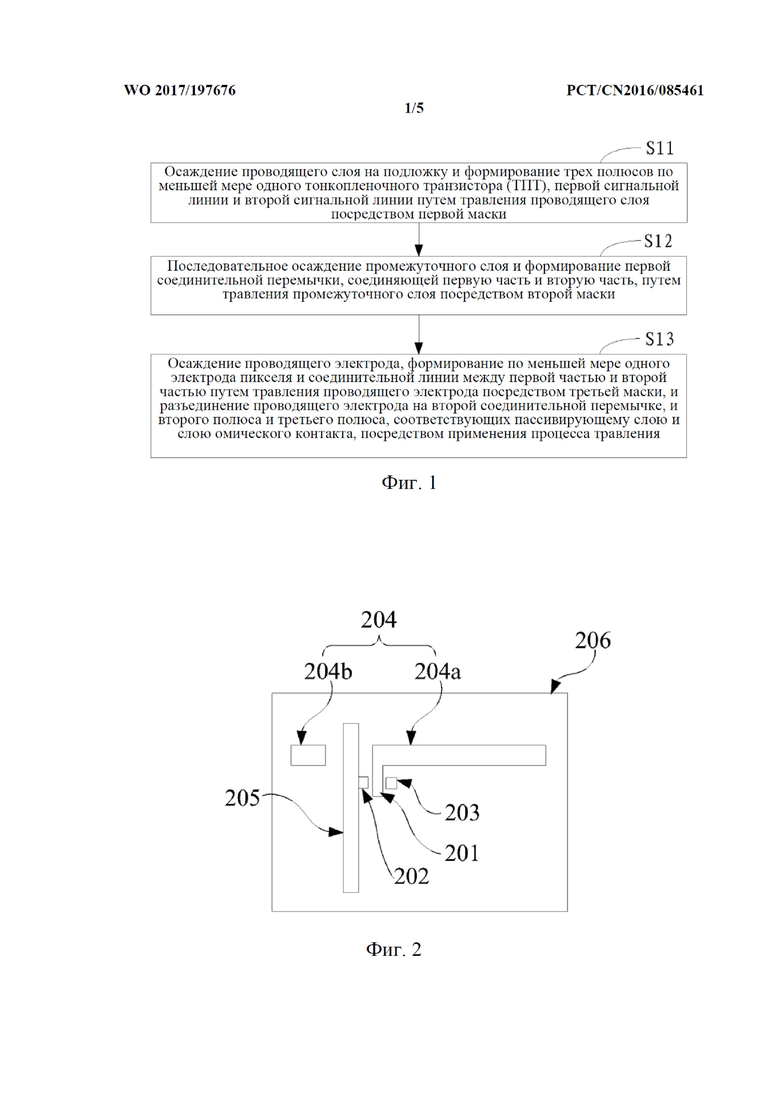

[002] На фиг. 1 показана блок-схема, изображающая способ изготовления подложки матрицы в соответствии с одним вариантом осуществления.

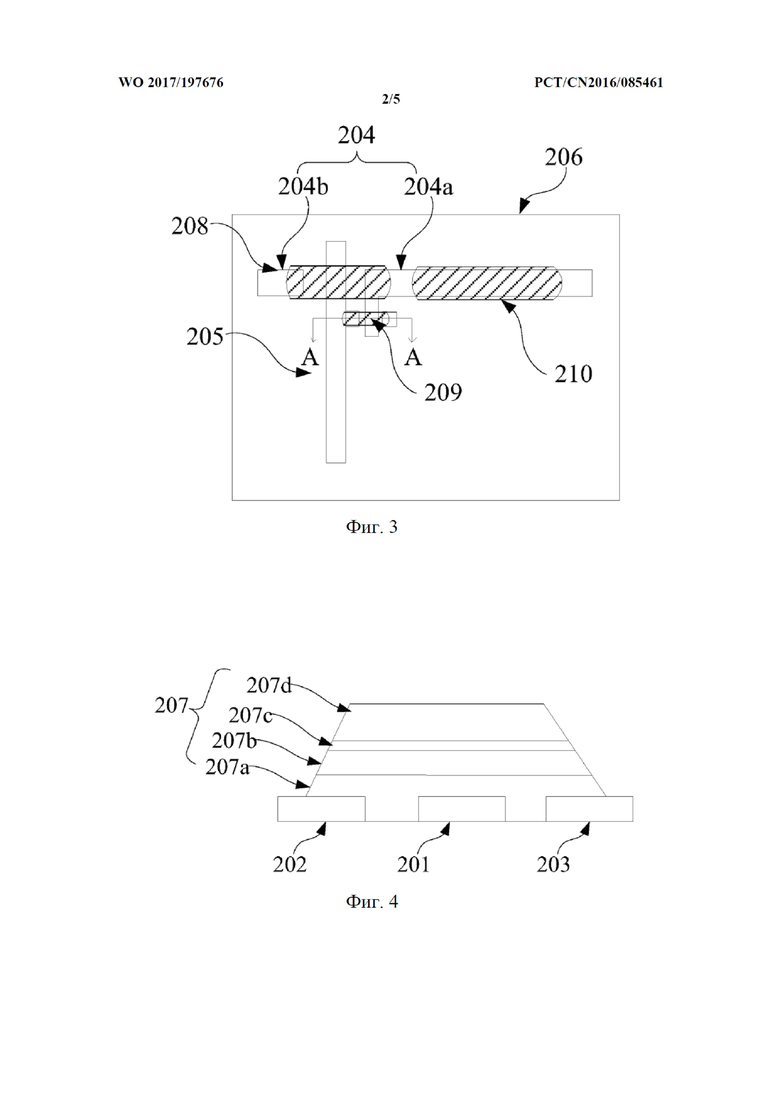

На фиг. 2 показан вид сверху, на котором изображена подложка матрицы, полученная на этапе S11, показанном на фиг. 1.

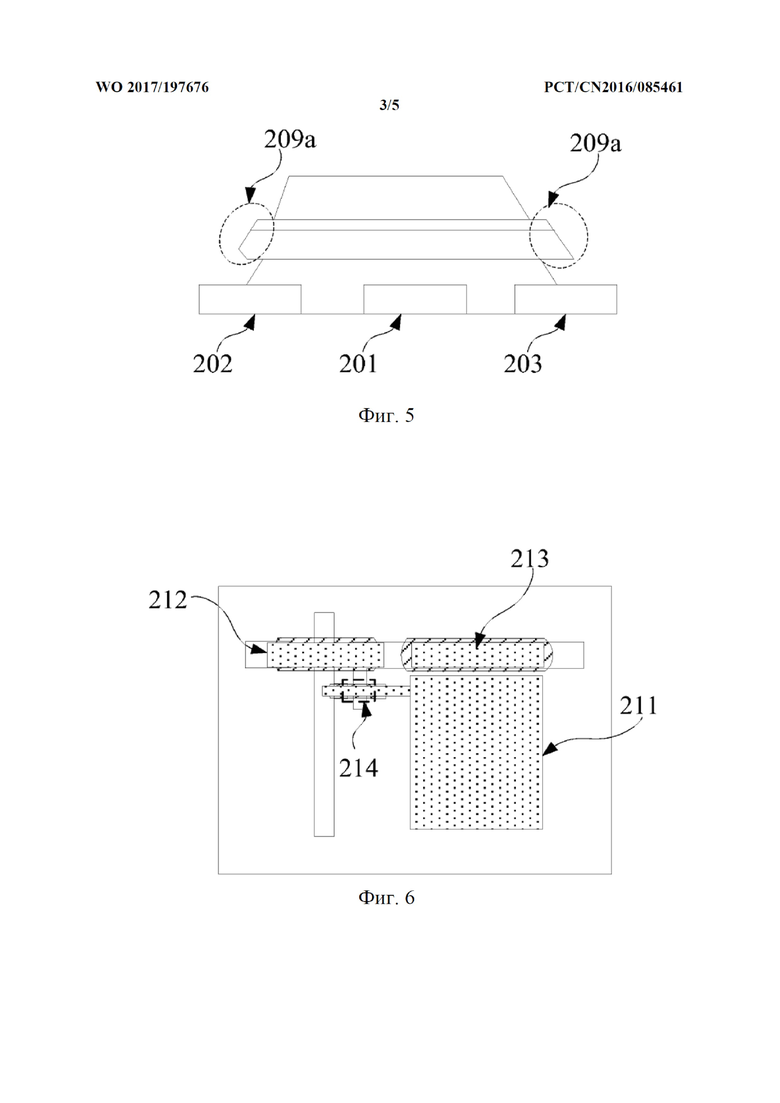

На фиг. 3 показан вид сверху, на котором изображена подложка матрицы, полученная на этапе S12, показанном на фиг. 1.

На фиг. 4 показан вид в сечении подложки матрицы в направлении A–A, причем контактное кольцо сформировано без применения процесса травления.

На фиг. 5 показан вид в сечении подложки матрицы в направлении A–A, причем контактное кольцо сформировано посредством применения процесса травления.

На фиг. 6 показан первый вид сверху, на котором изображена подложка матрицы, полученная на этапе S13, показанном на фиг. 1.

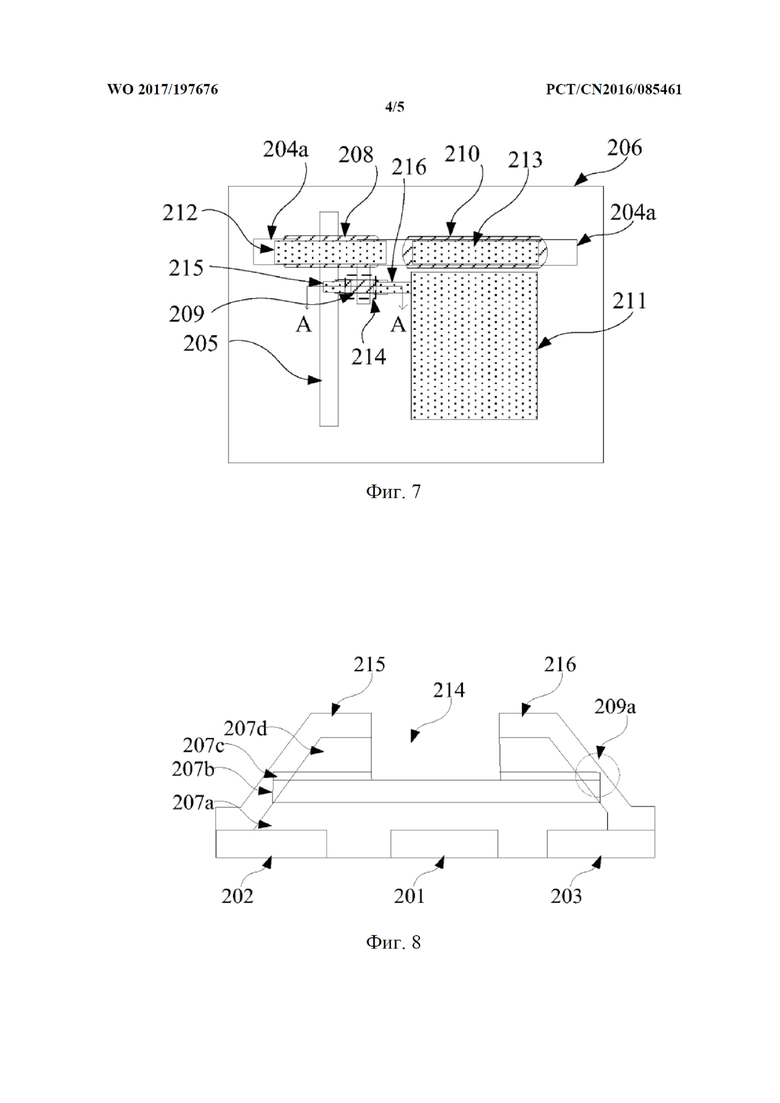

На фиг. 7 показан второй вид сверху, на котором изображена подложка матрицы, полученная на этапе S13, показанном на фиг. 1.

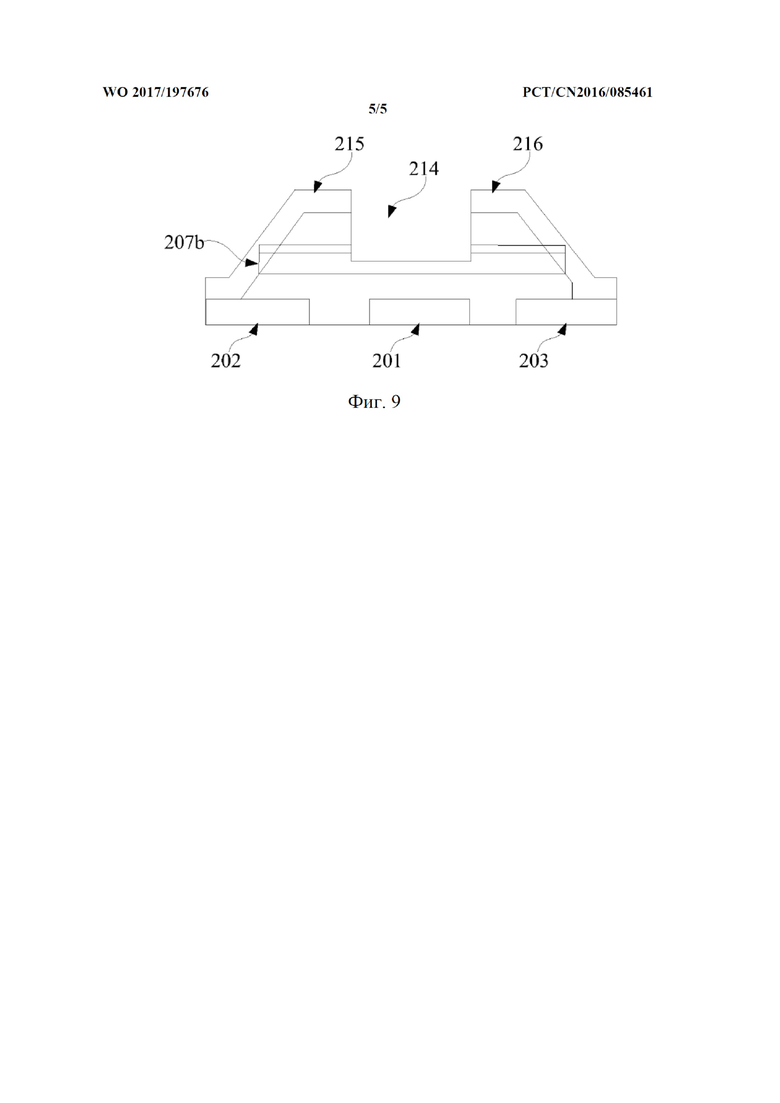

На фиг. 8 показан вид в сечении подложки матрицы, показанной на фиг. 7, в направлении A–A в соответствии с одним вариантом осуществления.

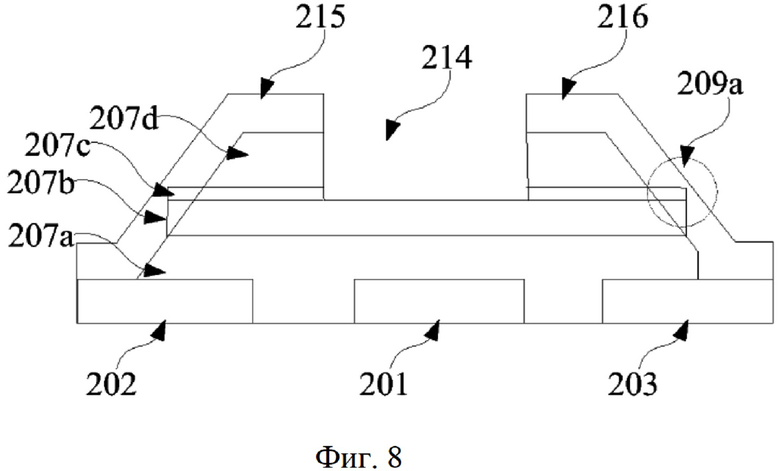

На фиг. 9 показан вид в сечении подложки матрицы, показанной на фиг. 7, в направлении A–A в соответствии с другим вариантом осуществления.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[003] Варианты осуществления настоящего изобретения будут описаны далее более подробно со ссылкой на прилагаемые графические материалы, на которых показаны варианты осуществления настоящего изобретения.

[004] На фиг. 1 показана блок-схема, изображающая способ изготовления подложки матрицы в соответствии с одним вариантом осуществления. Способ включает следующие этапы.

[005] На этапе S11 выполняют осаждение проводящего слоя на подложку и формирование трех полюсов нескольких TFT, первой сигнальной линии и второй сигнальной линии путем травления проводящего слоя посредством первой маски.

[006] Подложка может представлять собой стеклянную подложку или подложку, выполненную из другого прозрачного изолирующего материала. Проводящий слой может представлять собой металлический слой или может быть выполнен из неметаллических материалов, которые являются проводящими.

[007] Как показано на фиг. 2, проводящий слой может быть осажден на подложку 206 посредством физического осаждения из паровой фазы (PVD). Кроме того, к проводящему слою применяют процесс фотолитографии посредством рельефной первой маски для образования рельефных элементов трех полюсов TFT, первой сигнальной линии и второй сигнальной линии. Затем, процесс мокрого травления применяют для формирования первого полюса 201, второго полюса 202, третьего полюса 203, первой сигнальной линии 204 и второй сигнальной линии 205.

[008] Первая сигнальная линия 204 пересекается со второй сигнальной линией 205 в вертикальном направлении. Первая сигнальная линия 204 содержит первую часть 204a и вторую часть 204b, расположенные соответственно на двух сторонах второй сигнальной линии 205, причем первая часть 204a и вторая часть 204b не соединены электрически со второй сигнальной линией 205.

В этом варианте осуществления первая часть 204a первой сигнальной линии 204 электрически соединена с первым полюсом 201 TFT, и вторая сигнальная линия 205 электрически соединена со вторым полюсом 202 TFT.

На этапе S12 выполняют последовательное осаждение промежуточного слоя и формирование первой соединительной перемычки, второй соединительной перемычки и изолирующей структуры емкости путем травления промежуточного слоя посредством второй маски.

В одном примере промежуточный слой 207 содержит изолирующий слой 207a (также называемым как изолятор затвора (GI)), активный слой 207b, слой 207c омического контакта и пассивирующий слой 207d. Также как показано на фиг. 3, применяют плазмохимическое осаждение из паровой фазы (PECVD) для последовательного осаждения изолирующего слоя 207a, активного слоя 207b, слоя 207c омического контакта и пассивирующего слоя 207d на подложку, причем активный слой 207b может содержать a-Si и/или p-Si. Слой 207c омического контакта может представлять собой n+ a-Si.

Затем, применяют рельефную вторую маску для выполнения фотолитографии в отношении промежуточного слоя 207 для образования первой соединительной перемычки 208 и второй соединительной перемычки 209 на промежуточном слое 207 и для образования рельефных элементов на изолирующей структуре 210 емкости над первой частью 204a. Первая соединительная перемычка 208 соединяет первую часть 204a и вторую часть 204b, и вторая соединительная перемычка 209 соединяет второй полюс 202 и третий полюс 203. Процесс сухого травления выполняют на проводящем слое для формирования первой соединительной перемычки 208, второй соединительной перемычки 209 (также называемой как кремниевая перемычка) и изолирующей структуры 210 емкости.

Предпочтительно для обеспечения изоляции проводящего электрода верхнего проводящего слоя от проводящего электрода нижнего проводящего слоя первая соединительная перемычка 208 и изолирующая структура 210 емкости полностью закрывают первую сигнальную линию в направлении ширины. В одном примере ширина первой соединительной перемычки 208 больше, чем ширина первой части 204a и второй части 204b первой сигнальной линии, и ширина изолирующей структуры 210 емкости больше, чем ширина первой части 204a.

Кроме того, для обеспечения возможности улучшенного контакта активного слоя и слоя омического контакта с нижним проводящим слоем и расположенным под ним проводящим электродом, после формирования второй соединительной перемычки 209 этап дополнительно включает:

применение HF для выполнения процесса травления в отношении краев пассивирующего слоя и изолирующего слоя второй соединительной перемычки 209 таким образом, чтобы активный слой 207b и слой 207c омического контакта второй соединительной перемычки 209 выступали наружу с формированием по меньшей мере одного контактного кольца 209a. На фиг. 4 показан вид в сечении подложки матрицы в направлении A–A, причем контактное кольцо сформировано без применения процесса травления. В одном примере HF применяют для выполнения процесса травления в отношении краев пассивирующего слоя 207d и изолирующего слоя 207a второй соединительной перемычки 209 для удержания краев активного слоя 207b и слоя 207c омического контакта второй соединительной перемычки 209 с формированием полукруглого контактного кольца (уплотнительного кольца) 209a. HF применяют по той причине, что HF обладает избирательностью по отношению к Si и SiOx.

Следует понимать, что, при реальном применении, после формирования второй соединительной перемычки, контактное кольцо не формируют. То есть активный слой и слой омического контакта не имеют выступов, соответствующих пассивирующему слою и изолирующему слою.

На этапе S13 выполняют осаждение проводящего электрода и применение третьей маски для травления проводящего электрода с формированием электрода пикселя, соединительной линии и электрода накопительной емкости. Кроме того, проводящий электрод на второй соединительной перемычке, а также второй полюс и третий полюс, соответствующие пассивирующему слою и слою омического контакта, разъединены за счет применения процесса травления.

В одном примере, как показано на фиг. 6–8, применяют процесс PVD для осаждения прозрачного проводящего электрода, т. е. оксид индия и олова (ITO). Процесс фотолитографии применяют к прозрачному проводящему электроду посредством рельефной третьей маски для образования электрода 211 пикселя, соединительной линии между первой частью 204a и второй частью 204b, электрода 213 накопительной емкости на изолирующей структуре 210 емкости и области 214 разъединения второй соединительной перемычки между вторым полюсом и третьим полюсом. Затем, процесс мокрого травления применяют к прозрачному проводящему электроду для формирования электрода 211 пикселя, соединительной линии 212 и электрода 213 накопительной емкости, как показано на фиг. 6.

Затем, процесс сухого травления применяют к прозрачному проводящему электроду, пассивирующему слою 207d и слою 207c омического контакта таким образом, что прозрачный проводящий электрод, пассивирующий слой 207d и слой 207c омического контакта, соответственно соответствующие второму полюсу и третьему полюсу, разъединяются, как показано на фиг. 7 и 8. В другом варианте осуществления может быть выполнено травление верхней части над активным слоем 207b области 214 разъединения, подлежащей разъединению, как показано на фиг. 9.

Следует понимать, что рельефные элементы области 214 разъединения не были образованы в ходе процесса фотолитографии. После получения вышеописанной проводящей конструкции посредством процесса мокрого травления, вторую фотолитографию выполняют для получения области 214 разъединения. В этот момент, процесс сухого травления выполняют для получения области 214 разъединения.

Альтернативно проводящий электрод второй соединительной перемычки размещают на контактном кольце 209a таким образом, что проводящий электрод, контактное кольцо 209a, второй полюс 202 и третий полюс 203 электрически соединяются. В частности, часть проводящего электрода на второй соединительной перемычке, соответствующая второму полюсу 202, представляет собой первый проводящий электрод 215. Первый проводящий электрод 215 соединен с активным слоем и вторым полюсом 202 за счет закрывания контактного кольца на боковой поверхности второй соединительной перемычки с формированием замкнутого контура.

Часть проводящего электрода на второй соединительной перемычке, соответствующая третьему полюсу 203, представляет собой второй проводящий электрод 216. Второй проводящий электрод 216 соединен с активным слоем и третьим полюсом 203 за счет закрывания контактного кольца на боковой поверхности второй соединительной перемычки с формированием замкнутого контура. Первый проводящий электрод 215 и вторая сигнальная линия 205 находятся в электрическом контакте для обеспечения электрического соединения между второй сигнальной линией 205 и вторым полюсом 202 TFT. Второй проводящий электрод 216 и электрод 211 пикселя находятся в электрическом контакте для обеспечения электрического соединения между электродом 211 пикселя и третьим полюсом 203 TFT.

В этом варианте осуществления соединительная линия 212 длиннее, чем первая соединительная перемычка 208, и соединительная линия 212 уже, чем первая соединительная перемычка 208, для обеспечения изоляции соединительной линии 212 от второй сигнальной линии 205 и обеспечения электрического соединения соединительной линии 212 с первой частью 204a и второй частью 204b. В одном примере соединительная линия проходит через сквозное отверстие первой соединительной перемычки 208 для электрического соединения с первой частью 204a и второй частью 204b. В этот момент, длина соединительной линии 212 не больше длины первой соединительной перемычки 208. Электрод 213 накопительной емкости и соответствующая первая часть 204a образуют накопительную емкость посредством изолирующей структуры 210 емкости.

В одном варианте осуществления первый полюс, второй полюс и третий полюс соответствуют затвору, истоку и стоку TFT. Первая сигнальная линия представляет собой линию развертки, а вторая сигнальная линия представляет собой линию передачи данных. В другом варианте осуществления второй полюс и третий полюс соответствуют стоку и истоку. Альтернативно первая сигнальная линия представляет собой линию передачи данных, а вторая сигнальная линия представляет собой линию развертки. Соответственно, первый полюс представляет собой исток или сток, а второй полюс представляет собой затвор.

Первая маска, вторая маска и третья маска могут представлять собой общие маски или могут представлять собой полутоновую маску.

На фиг. 7 показан второй вид сверху, на котором изображена подложка матрицы, полученная на этапе S13, показанном на фиг. 1. На фиг. 8 показан вид в сечении подложки матрицы, показанной на фиг. 7, в направлении A–A в соответствии с одним вариантом осуществления. Подложка матрицы содержит:

подложку 206;

первый полюс 201, второй полюс 202, третий полюс 203 по меньшей мере одного TFT на подложке 206, и первую сигнальную линию 204 и вторую сигнальную линию 205, причем первая сигнальная линия 204 содержит первую часть 204a и вторую часть 204b на двух боковых сторонах второй сигнальной линии 205;

первую соединительную перемычку 208 между первой частью 204a и второй частью 204b;

по меньшей мере один электрод 211 пикселя и соединительную линию 212 на первой соединительной перемычке 208, причем соединительная линия 212 выполнена с возможностью электрического соединения первой части 204a и второй части 204b.

[009] Подложка может представлять собой стеклянную подложку или подложку, выполненную из другого прозрачного изолирующего материала. Проводящий слой может представлять собой металлический слой или может быть выполнен из неметаллических материалов, которые являются проводящими. Проводящий электрод может представлять собой прозрачный проводящий электрод, такой как ITO.

Предпочтительно ширина первой соединительной перемычки 208 больше ширины закрытой первой части 204a и закрытой второй части 204b. Кроме того, соединительная линия 212 длиннее, чем первая соединительная перемычка 208, и уже, чем первая соединительная перемычка 208. В одном примере соединительная линия проходит через сквозное отверстие первой соединительной перемычки 208 для электрического соединения с первой частью 204a и второй частью 204b. В этот момент, длина соединительной линии 212 не больше длины первой соединительной перемычки 208.

Предпочтительно первая соединительная перемычка 208 содержит изолирующий слой 207a, активный слой 207b, слой 207c омического контакта и пассивирующий слой 207d, расположенные последовательно с одной стороны рядом с подложкой 206, причем подробная информация об этих четырех слоях может быть найдена в вышеприведенном описании.

Предпочтительно первая часть 204a первой сигнальной линии электрически соединена с первым полюсом 201 TFT, а вторая сигнальная линия 205 электрически соединена со вторым полюсом 202 TFT.

Подложка матрицы дополнительно содержит вторую соединительную перемычку 209 между вторым полюсом 202 и третьим полюсом 203, и первый проводящий электрод 215 и вторая проводящий электрод 216 на второй соединительной перемычке 209, причем вторая соединительная перемычка 209 содержит изолирующий слой 207a, активный слой 207b, слой 207c омического контакта и пассивирующий слой 207d. Пассивирующий слой 207d и слой 207c омического контакта второй соединительной перемычки 209 разъединены посредством области 214 разъединения. Верхняя часть активного слоя 207b может быть разъединена посредством области 214 разъединения, как показано на фиг. 9.

Первый проводящий электрод 215 электрически соединяет второй полюс 202 и активный слой 207b, а также электрически соединен со второй сигнальной линией 205. Проводящий электрод электрически соединен с третьим полюсом 203 и активным слоем 207b, а также электрически соединен с электродом 211 пикселя.

Края активного слоя 207b и слоя 207c омического контакта второй соединительной перемычки 209 выступают относительно изолирующего слоя 207a и пассивирующего слоя 207d с формированием контактного кольца 209a. Первый проводящий электрод 215 и второй проводящий электрод 216 закрывают контактное кольцо 209a для электрического соединения с активным слоем.

Предпочтительно подложка матрицы дополнительно содержит электрод 213 накопительной емкости и изолирующую структуру 210 емкости, расположенную между электродом 213 накопительной емкости и первой сигнальной линией 204. В частности, изолирующая структура 210 емкости содержит изолирующий слой 207a, активный слой 207b, слой 207c омического контакта и пассивирующий слой 207d.

В этом варианте осуществления первая сигнальная линия 204 пересекается со второй сигнальной линией 205. Первый полюс, второй полюс и третий полюс соответствуют затвору, истоку и стоку TFT. Первая сигнальная линия представляет собой линию развертки, а вторая сигнальная линия представляет собой линию передачи данных. В других вариантах осуществления второй полюс и третий полюс могут соответствовать стоку и истоку. Альтернативно первая сигнальная линия представляет собой линию передачи данных, а вторая сигнальная линия представляет собой линию развертки. Соответственно, первый полюс представляет собой исток или сток, а второй полюс представляет собой затвор.

В настоящем изобретении также описывается подложка матрицы, изготовленная по вышеописанному способу изготовления.

Подложка матрицы может представлять собой подложку матрицы в LCD.

Настоящее изобретение также относится к дисплейной панели, имеющей подложку матрицы, подложку цветового фильтра и жидкие кристаллы, расположенные между этими двумя подложками.

С учетом вышеописанного, первая сигнальная линия подложки матрицы содержит две секции, соответственно расположенные на двух сторонах второй сигнальной линии. Затем, соединительную линию, присоединенную к первой сигнальной линии, формируют в последующем процессе с использованием маски. Таким образом, первая сигнальная линия может быть нормально расположена, и первая сигнальная линия и вторая сигнальная линия могут быть сформированы посредством одного процесса с использованием маски, и, таким образом, нет необходимости в двух отдельных процессах с использованием маски. Таким образом, количество процессов с использованием маски может быть уменьшено для экономии времени и расходов на изготовление.

[0010] Считается, что настоящие варианты осуществления и их преимущества будут понятны из вышеизложенного описания, а также очевидно, что в них могут быть внесены различные изменения без отхода от сущности и объема настоящего изобретения или без ущерба для всех его материальных преимуществ, при этом описанные выше примеры представляют собой лишь предпочтительные или иллюстративные варианты осуществления настоящего изобретения.

Изобретение относится к подложке матрицы и способу ее изготовления. Способ изготовления подложки матрицы включает: осаждение проводящего слоя на подложку и применение первой маски для травления проводящего слоя с формированием трех электродов тонкопленочного транзистора, первой сигнальной линии и второй сигнальной линии, причем первая сигнальная линия содержит первую часть и вторую часть, разделенные и расположенные с каждой стороны второй сигнальной линии, последовательное осаждение промежуточных слоев и применение второй маски при травлении промежуточных слове с формированием первой соединительной перемычки, соединяющей первую часть и вторую часть, осаждение проводящего электрода и применение третьей маски при травлении проводящего электрода с формированием электрода пикселя и соединительной линии, электрически соединенной с первой частью и второй частью. Таким образом, время, расходуемое на изготовление подложки матрицы, и расходы на изготовление снижаются. 3 н. и 17 з.п. ф-лы, 9 ил.

1. Способ изготовления подложек матрицы, включающий:

осаждение проводящего слоя на подложку и формирование трех полюсов по меньшей мере одного тонкопленочного транзистора (TFT), первой сигнальной линии и второй сигнальной линии путем травления проводящего слоя посредством первой маски, причем первая сигнальная линия содержит первую часть и вторую часть, соответственно расположенные на двух сторонах второй сигнальной линии;

последовательное осаждение промежуточного слоя и формирование первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски; и

осаждение проводящего электрода и формирование по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски.

2. Способ изготовления по п. 1, отличающийся тем, что первая часть первой сигнальной линии электрически соединена с первым полюсом TFT, вторая сигнальная линия электрически соединена со вторым полюсом TFT, и промежуточный слой содержит изолирующий слой, активный слой, слой омического контакта и пассивирующий слой, уложенные последовательно;

этап формирования первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски дополнительно включает формирование второй соединительной перемычки, соединяющей второй полюс и третий полюс TFT, путем травления промежуточного слоя посредством второй маски;

этап формирования по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски дополнительно включает разъединение проводящего электрода, пассивирующего слоя и второго полюса и третьего полюса, соответствующего слою омического контакта, путем травления второй соединительной перемычки посредством третьей маски.

3. Способ изготовления по п. 2, отличающийся тем, что этап формирования второй соединительной перемычки, соединяющей второй полюс и третий полюс TFT, путем травления промежуточного слоя посредством второй маски дополнительно включает:

применение HF для травления краев пассивирующего слоя и изолирующего слоя второй соединительной перемычки таким образом, чтобы активный слой и слой омического контакта второй соединительной перемычки выступали наружу с формированием по меньшей мере одного контактного кольца.

4. Способ изготовления по п. 3, отличающийся тем, что проводящий электрод на второй соединительной перемычке размещают на контактном кольце таким образом, что проводящий электрод электрически соединен с контактным кольцом, вторым полюсом и третьим полюсом.

5. Способ изготовления по п. 1, отличающийся тем, что этап формирования первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски дополнительно включает формирование изолирующей структуры емкости на первой части путем травления промежуточного слоя посредством второй маски;

этап формирования по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски дополнительно включает формирование электрода накопительной емкости на изолирующей структуре емкости путем травления проводящего электрода посредством третьей маски.

6. Способ изготовления по п. 1, отличающийся тем, что первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой сигнальную линию и вторая сигнальная линия представляет собой линию передачи данных.

7. Способ изготовления по п. 4, отличающийся тем, что первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой линию передачи данных и вторая сигнальная линия представляет собой сигнальную линию.

8. Подложка матрицы, содержащая:

подложку;

три полюса по меньшей мере одного TFT на подложке, первую сигнальную линию и вторую сигнальную линию, причем первая сигнальная линия содержит первую часть и вторую часть, соответственно расположенные на двух сторонах второй сигнальной линии;

первую соединительную перемычку между первой частью и второй частью, причем первая соединительная перемычка изолирована от второй сигнальной линии; и

по меньшей мере один электрод пикселя и соединительную линию на первой соединительной перемычке, причем соединительная линия электрически соединяет первую часть и вторую часть.

9. Подложка матрицы по п. 8, отличающаяся тем, что первая часть первой сигнальной линии электрически соединена с первым полюсом TFT,

причем подложка матрицы дополнительно содержит вторую соединительную перемычку между вторым полюсом и третьим полюсом TFT, первый проводящий электрод и второй проводящий электрод на второй соединительной перемычке, причем вторая соединительная перемычка содержит изолирующий слой, активный слой, слой омического контакта и пассивирующий слой, причем две части пассивирующего слоя и слоя омического контакта второй соединительной перемычки, разделенные областью разъединения, расположены в соответствии со вторым полюсом и третьим полюсом, причем первый проводящий электрод электрически соединен со вторым полюсом, активным слоем и второй сигнальной линией, и проводящий электрод электрически соединен с третьим полюсом, активным слоем и электродом пикселя.

10. Подложка матрицы по п. 9, отличающаяся тем, что активный слой и слой омического контакта второй соединительной перемычки выступают наружу с формированием по меньшей мере одного контактного кольца.

11. Подложка матрицы по п. 10, отличающаяся тем, что проводящий электрод на второй соединительной перемычке размещают на контактном кольце таким образом, что проводящий электрод электрически соединен с контактным кольцом, вторым полюсом и третьим полюсом.

12. Подложка матрицы по п. 8, отличающаяся тем, что подложка матрицы дополнительно содержит изолирующую структуру емкости и электрод накопительной емкости, расположенные на первой части последовательно.

13. Подложка матрицы по п. 8, отличающаяся тем, что первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой сигнальную линию и вторая сигнальная линия представляет собой линию передачи данных.

14. Подложка матрицы по п. 9, отличающаяся тем, что первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой линию передачи данных и вторая сигнальная линия представляет собой сигнальную линию.

15. Подложка матрицы, изготовленная посредством способа изготовления, причем способ включает:

осаждение проводящего слоя на подложку и формирование трех полюсов по меньшей мере одного тонкопленочного транзистора (TFT), первой сигнальной линии и второй сигнальной линии путем травления проводящего слоя посредством первой маски, причем первая сигнальная линия содержит первую часть и вторую часть, соответственно расположенные на двух сторонах второй сигнальной линии;

последовательное осаждение промежуточного слоя и формирование первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски; и

осаждение проводящего электрода и формирование по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски.

16. Подложка матрицы по п. 15, отличающаяся тем, что первая часть первой сигнальной линии электрически соединена с первым полюсом TFT, вторая сигнальная линия электрически соединена со вторым полюсом TFT и промежуточный слой содержит изолирующий слой, активный слой, слой омического контакта и пассивирующий слой, уложенные последовательно;

этап формирования первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски дополнительно включает формирование второй соединительной перемычки, соединяющей второй полюс и третий полюс TFT, путем травления промежуточного слоя посредством второй маски;

этап формирования по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски дополнительно включает разъединение проводящего электрода, пассивирующего слоя и второго полюса и третьего полюса, соответствующего слою омического контакта, путем травления второй соединительной перемычки посредством третьей маски.

17. Подложка матрицы по п. 16, отличающаяся тем, что этап формирования второй соединительной перемычки, соединяющей второй полюс и третий полюс TFT, путем травления промежуточного слоя посредством второй маски дополнительно включает:

применение HF для травления краев пассивирующего слоя и изолирующего слоя второй соединительной перемычки таким образом, чтобы активный слой и слой омического контакта второй соединительной перемычки выступали наружу с формированием по меньшей мере одного контактного кольца.

18. Подложка матрицы по п. 17, отличающаяся тем, что проводящий электрод на второй соединительной перемычке размещают на контактном кольце таким образом, что проводящий электрод электрически соединен с контактным кольцом, вторым полюсом и третьим полюсом.

19. Подложка матрицы по п. 15, отличающаяся тем, что этап формирования первой соединительной перемычки, соединяющей первую часть и вторую часть, путем травления промежуточного слоя посредством второй маски дополнительно включает формирование изолирующей структуры емкости на первой части путем травления промежуточного слоя посредством второй маски;

этап формирования по меньшей мере одного электрода пикселя и соединительной линии между первой частью и второй частью путем травления проводящего электрода посредством третьей маски дополнительно включает формирование электрода накопительной емкости на изолирующей структуре емкости путем травления проводящего электрода посредством третьей маски.

20. Подложка матрицы по п. 15, отличающаяся тем, что первый полюс, второй полюс и третий полюс TFT представляют собой соответственно затвор, исток и сток, и первая сигнальная линия представляет собой сигнальную линию и вторая сигнальная линия представляет собой линию передачи данных.

| US 6545359 B1, 08.04.2003 | |||

| US 6790716 B2, 14.09.2004 | |||

| US 7888148 B2, 15.02.2011 | |||

| US 9025118 B2, 05.05.2015 | |||

| US 9318614 B2, 19.04.2016 | |||

| ПОДЛОЖКА МАТРИЦЫ ТПТ И ЖИДКОКРИСТАЛЛИЧЕСКАЯ ПАНЕЛЬ ОТОБРАЖЕНИЯ | 2009 |

|

RU2491591C2 |

Авторы

Даты

2019-05-22—Публикация

2016-06-12—Подача