Область техники

Технология настоящего изобретения относится к схеме преобразования электрической мощности.

Уровень техники

Публикация не прошедшей экспертизу заявки на патент Японии № 2001-186768 (JP 2001-186768 А) раскрывает преобразователь постоянного тока в постоянный, который повышает и выводит напряжение, подаваемое из источника мощности постоянного тока. Преобразователь постоянного тока в постоянный включает в себя два нижних полевых транзистора (FET) с каналом n-типа, имеющие исток, соединенный с межсоединением с низким потенциалом. Сток первого нижнего FET соединяется с выходным межсоединением с высоким потенциалом через первый диод. Сток второго нижнего FET соединяется с выходным межсоединением с высоким потенциалом через второй диод. Преобразователь постоянного тока в постоянный имеет основной дроссель, первый вспомогательный дроссель и второй вспомогательный дроссель. Основной дроссель включает в себя первый контактный вывод и второй контактный вывод. Первый контактный вывод основного дросселя соединяется с диодным мостом (видом источника мощности постоянного тока) через входное межсоединение с высоким потенциалом. Первый конец первого вспомогательного дросселя соединяется со вторым контактным выводом основного дросселя. Второй конец первого вспомогательного дросселя соединяется со стоком первого нижнего FET. Первый конец второго вспомогательного дросселя соединяется со вторым контактным выводом основного дросселя. Второй конец второго вспомогательного дросселя соединяется со стоком второго нижнего FET. Первый нижний FET и второй нижний FET управляются таким образом, что они попеременно включаются. Ток протекает в первом диоде, когда первый нижний FET переключается из включенного в выключенное состояние. Ток протекает во втором диоде, когда второй нижний FET переключается из включенного в выключенное состояние. Как результат, относительно высокое напряжение выводится в выходное межсоединение с высоким потенциалом. В случае, если первый нижний FET и второй нижний FET управляются, как описано выше, потери на переключение, которые формируются в первом нижнем FET и втором нижнем FET, уменьшаются.

Сущность изобретения

Чтобы эффективнее уменьшать ток, который протекает в первом диоде, может предоставляться полевой транзистор с каналом n-типа (в дальнейшем в этом документе, называемый "первым верхним FET"), соединенный параллельно с первым диодом. Чтобы эффективнее уменьшать ток, который протекает во втором диоде, может предоставляться полевой транзистор с каналом n-типа (в дальнейшем в этом документе, называемый "вторым верхним FET"), соединенный параллельно со вторым диодом. Первый верхний FET включается в соответствии со временем, когда ток протекает в первом диоде, за счет чего можно рассеивать ток и эффективнее уменьшать потери на переключение (в дальнейшем в этом документе, называемые "потерями"), которые должны формироваться. Аналогично, второй верхний FET включается в соответствии со временем, когда ток протекает во втором диоде, за счет чего можно рассеивать ток и эффективнее уменьшать потери, которые должны формироваться. Хотя описывается преобразователь постоянного тока в постоянный, который повышает напряжение, подаваемое из источника мощности постоянного тока, идентичная конфигурация может использоваться в инверторе, который преобразует электрическую мощность постоянного тока в электрическую мощность переменного тока. В этом подробном описании, предлагается технология, которая эффективнее уменьшает потери посредством увеличения времени включения верхнего FET в схеме преобразования электрической мощности, такой как преобразователь постоянного тока в постоянный или инвертор.

Аспект настоящего изобретения относится к схеме преобразования электрической мощности. Схема преобразования электрической мощности включает в себя первое межсоединение с высоким потенциалом, второе межсоединение с высоким потенциалом, межсоединение с низким потенциалом, первый нижний FET с каналом n-типа, первый верхний FET с каналом n-типа, второй нижний FET с каналом n-типа, второй верхний FET с каналом n-типа, первый диод, второй диод, основной дроссель, первый вспомогательный дроссель, второй вспомогательный дроссель и контроллер затвора. Первое межсоединение с высоким потенциалом соединяется с источником подачи электрической мощности. Первый нижний FET с каналом n-типа имеет исток, соединенный с межсоединением с низким потенциалом. Первый верхний FET с каналом n-типа имеет исток, соединенный со стоком первого нижнего FET, и сток, соединенный со вторым межсоединением с высоким потенциалом. Второй нижний FET с каналом n-типа имеет исток, соединенный с межсоединением с низким потенциалом. Второй верхний FET с каналом n-типа имеет исток, соединенный со стоком второго нижнего FET, и сток, соединенный со вторым межсоединением с высоким потенциалом. Первый диод имеет анод, соединенный с истоком первого верхнего FET, и катод, соединенный со стоком первого верхнего FET. Второй диод имеет анод, соединенный с истоком второго верхнего FET, и катод, соединенный со стоком второго верхнего FET. Основной дроссель имеет первый контактный вывод и второй контактный вывод. Первый контактный вывод соединяется с первым межсоединением с высоким потенциалом. Первый вспомогательный дроссель имеет первый конец, соединенный со вторым контактным выводом основного дросселя, и второй конец, соединенный со стоком первого нижнего FET. Второй вспомогательный дроссель имеет первый конец, соединенный со вторым контактным выводом основного дросселя, и второй конец, соединенный со стоком второго нижнего FET. Контроллер затвора соединяется с затвором первого нижнего FET, затвором первого верхнего FET, затвором второго нижнего FET и затвором второго верхнего FET. Контроллер затвора выполнен с возможностью осуществлять первую операцию. Контроллер затвора выполнен с возможностью, в первой операции, осуществлять управление таким образом, что первый нижний FET, первый верхний FET, второй нижний FET и второй верхний FET удовлетворяют следующим условиям. (Условие 1) Первое состояние, в котором первый нижний FET включается, и второй нижний FET выключается, второе состояние, в котором оба из первого нижнего FET и второго нижнего FET выключаются, третье состояние, в котором первый нижний FET выключается, и второй нижний FET включается, и четвертое состояние, в котором оба из первого нижнего FET и второго нижнего FET выключаются, многократно появляются по порядку. (Условие 2) Первый верхний FET включается в первое время в середине периода второго состояния, первый верхний FET поддерживается во включенном состоянии до второго времени в середине периода третьего состояния, и первый верхний FET выключается во второе время.

В этом подробном описании, FET с каналом n-типа включают в себя биполярный транзистор с изолированным затвором (IGBT). В IGBT, сток может упоминаться как коллектор, и исток может упоминаться как эмиттер.

За счет схемы преобразования электрической мощности согласно аспекту настоящего изобретения, FET управляются таким образом, что условие 1 удовлетворяется. Когда первый нижний FET переключается из включенного в выключенное состояние, ток протекает в первом диоде. Таким образом, ток протекает в первом диоде сразу после переключения из первого состояния во второе состояние. Ток протекает в первом диоде от периода второго состояния (т.е. состояния после того, как первый нижний FET переключается из включенного в выключенное состояние) до периода третьего состояния (т.е. состояния после того, как второй нижний FET переключается из выключенного во включенное состояние). Как показано в условии 2, первый верхний FET включается в первое время в середине периода второго состояния. По этой причине, часть тока, который протекает в первом диоде, протекает в первом верхнем FET. В общем, чтобы сдерживать короткое замыкание между вторым межсоединением с высоким потенциалом и межсоединением с низким потенциалом, верхний FET выключается до того, как нижний FET включается. Тем не менее, за счет схемы преобразования электрической мощности согласно аспекту настоящего изобретения, первый верхний FET поддерживается во включенном состоянии даже после того, как второй нижний FET включен. Таким образом, первый верхний FET поддерживается во включенном состоянии от первого времени в середине периода второго состояния до второго времени в середине периода третьего состояния. Соответственно, ток протекает в первом верхнем FET до середины периода третьего состояния. Как описано выше, поскольку время включения первого верхнего FET является сравнительно большим, время, в течение которого ток рассеивается и протекает в первом верхнем FET и первом диоде, является сравнительно большим. Вследствие этого, потери, которые должны формироваться, эффективнее уменьшаются. В начале периода третьего состояния, оба из первого верхнего FET и второго нижнего FET переводятся во включенное состояние. Тем не менее, поскольку существуют первый вспомогательный дроссель и второй вспомогательный дроссель между первым верхним FET и вторым нижним FET, напряжение сохраняется с помощью первого вспомогательного дросселя и второго вспомогательного дросселя, и состояние короткого замыкания (т.е. состояние, в котором протекает чрезмерный ток) не задается между вторым межсоединением с высоким потенциалом и межсоединением с низким потенциалом. Как описано выше, за счет схемы преобразования электрической мощности согласно аспекту настоящего изобретения, можно эффективнее уменьшать потери, которые должны формироваться посредством задания времени включения первого верхнего FET сравнительно большим при ограничении короткого замыкания между вторым межсоединением с высоким потенциалом и межсоединением с низким потенциалом.

В схеме преобразования электрической мощности согласно аспекту настоящего изобретения, контроллер затвора может быть выполнен с возможностью, в первой операции, осуществлять управление таким образом, что первый нижний FET, первый верхний FET, второй нижний FET и второй верхний FET удовлетворяют такому условию, что первое состояние задается сразу после четвертого состояния, и такому условию, что второй верхний FET включается в третье время в середине периода четвертого состояния, второй верхний FET поддерживается во включенном состоянии до четвертого времени в середине периода первого состояния, и второй верхний FET выключается в четвертое время.

В схеме преобразования электрической мощности согласно аспекту настоящего изобретения, контроллер затвора может быть выполнен с возможностью осуществлять вторую операцию. Контроллер затвора может быть выполнен с возможностью, во второй операции, осуществлять управление таким образом, что первый нижний FET, первый верхний FET, второй нижний FET и второй верхний FET удовлетворяют такому условию, что состояние, в котором оба из первого нижнего FET и второго нижнего FET включаются, и состояние, в котором оба из первого нижнего FET и второго нижнего FET выключаются, появляются попеременно. Контроллер затвора может быть выполнен с возможностью осуществлять первую операцию, когда ток, протекающий в основном дросселе, равен или меньше порогового значения, и осуществлять вторую операцию, когда ток, протекающий в основном дросселе, превышает пороговое значение. Пороговое значение задается таким образом, чтобы удовлетворять взаимосвязи 0,9*Ib<Ith<1,1*Ib относительно граничного значения между областью тока, в которой потери, сформированные в первой операции, становятся равными или меньше потерь, сформированных во второй операции, и областью тока, в которой потери, сформированные в первой операции, становятся больше потерь, сформированных во второй операции, где Ith обозначает пороговое значение, Ib обозначает граничное значение.

В схеме преобразования электрической мощности согласно аспекту настоящего изобретения, контроллер затвора может быть выполнен с возможностью, во второй операции, осуществлять управление таким образом, что первый нижний FET, первый верхний FET, второй нижний FET и второй верхний FET удовлетворяют такому условию, что следующие состояния многократно появляются по порядку: состояние, в котором оба из первого нижнего FET и второго нижнего FET включаются, и оба из первого верхнего FET и второго верхнего FET выключаются; состояние, в котором все из первого нижнего FET, второго нижнего FET, первого верхнего FET и второго верхнего FET выключаются; состояние, в котором оба из первого нижнего FET и второго нижнего FET выключаются, и оба из первого верхнего FET и второго верхнего FET включаются; и состояние, в котором все из первого нижнего FET, второго нижнего FET, первого верхнего FET и второго верхнего FET выключаются.

В схеме преобразования электрической мощности согласно аспекту настоящего изобретения, контроллер затвора может быть выполнен с возможностью, во второй операции, осуществлять управление таким образом, что первый нижний FET, первый верхний FET, второй нижний FET и второй верхний FET удовлетворяют такому условию, что следующие состояния появляются попеременно: состояние, в котором оба из первого нижнего FET и второго нижнего FET включаются, и оба из первого верхнего FET и второго верхнего FET выключаются; и состояние, в котором все из первого нижнего FET, второго нижнего FET, первого верхнего FET и второго верхнего FET выключаются.

Схема преобразования электрической мощности согласно аспекту настоящего изобретения дополнительно может включать в себя третий нижний FET с каналом n-типа, третий верхний FET с каналом n-типа, третий диод и третий вспомогательный дроссель. Третий нижний FET с каналом n-типа имеет исток, соединенный с межсоединением с низким потенциалом. Третий верхний FET с каналом n-типа имеет исток, соединенный со стоком третьего нижнего FET, и сток, соединенный со вторым межсоединением с высоким потенциалом. Третий диод имеет анод, соединенный с истоком третьего верхнего FET, и катод, соединенный со стоком третьего верхнего FET. Третий вспомогательный дроссель имеет первый конец, соединенный со вторым контактным выводом основного дросселя, и второй конец, соединенный со стоком третьего нижнего FET. Контроллер затвора может соединяться с затвором третьего нижнего FET и затвором третьего верхнего FET. Контроллер затвора может осуществлять управление таким образом, что третий нижний FET выключается в первом состоянии, втором состоянии, третьем состоянии и четвертом состоянии. В первой операции, контроллер затвора может осуществлять управление таким образом, что первый нижний FET, первый верхний FET, второй нижний FET, второй верхний FET, третий нижний FET и третий верхний FET удовлетворяют такому условию, что первое состояние, второе состояние, третье состояние, четвертое состояние, пятое состояние и шестое состояние многократно появляются по порядку, и такому условию, что второй верхний FET включается в пятое время в середине периода четвертого состояния, второй верхний FET поддерживается во включенном состоянии до шестого времени в середине периода пятого состояния, и второй верхний FET выключается в шестое время. Пятое состояние может представлять собой состояние, в котором первый нижний FET выключается, второй нижний FET выключается, и третий нижний FET включается. Шестое состояние может представлять собой состояние, в котором все из первого нижнего FET, второго нижнего FET и третьего нижнего FET выключаются.

В схеме преобразования электрической мощности согласно аспекту настоящего изобретения, контроллер затвора может осуществлять управление, в первой операции, таким образом, что первый нижний FET, первый верхний FET, второй нижний FET, второй верхний FET, третий нижний FET и третий верхний FET удовлетворяют такому условию, что первое состояние задается сразу после шестого состояния, и такому условию, что третий верхний FET включается в седьмое время в середине периода шестого состояния, третий верхний FET поддерживается во включенном состоянии до восьмого времени в середине периода первого состояния, и третий верхний FET выключается в восьмое время.

В схеме преобразования электрической мощности согласно аспекту настоящего изобретения, схема преобразования электрической мощности может представлять собой преобразователь постоянного тока в постоянный.

В схеме преобразования электрической мощности согласно аспекту настоящего изобретения, схема преобразования электрической мощности может представлять собой инвертор.

Краткое описание чертежей

Ниже описываются признаки, преимущества и техническая и промышленная значимость примерных вариантов осуществления изобретения со ссылкой на прилагаемые чертежи, на которых аналогичные номера обозначают аналогичные элементы, и на которых:

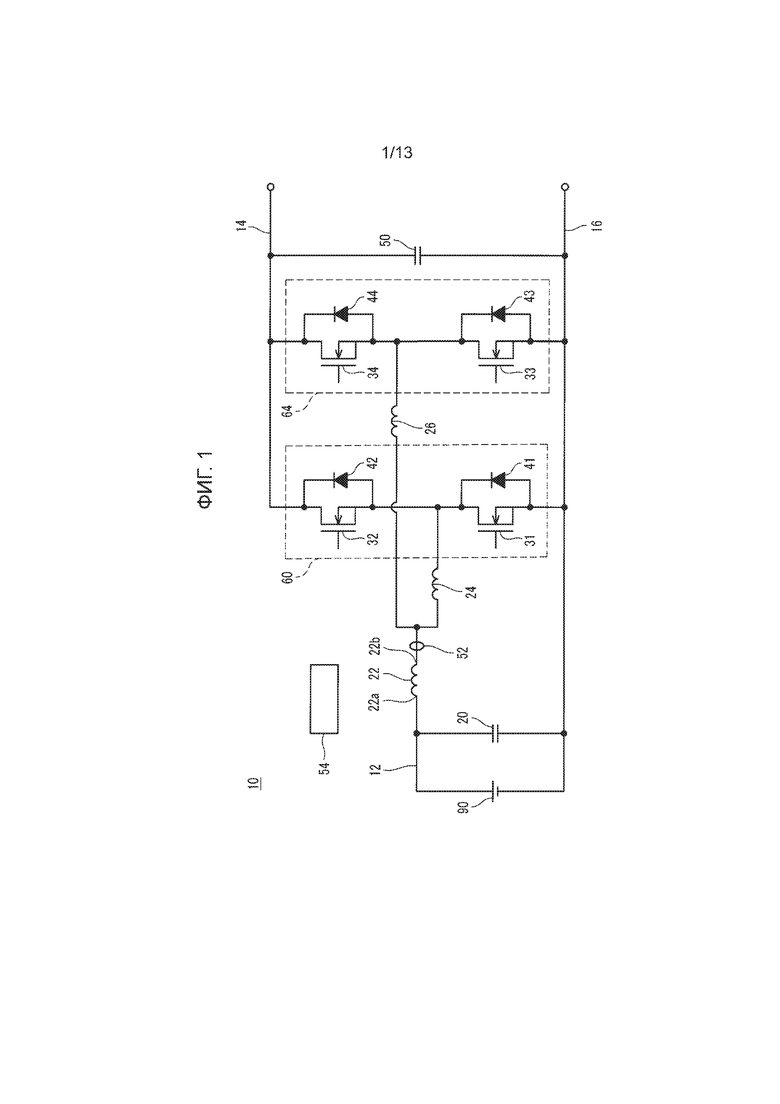

Фиг. 1 является принципиальной схемой преобразователя постоянного тока в постоянный;

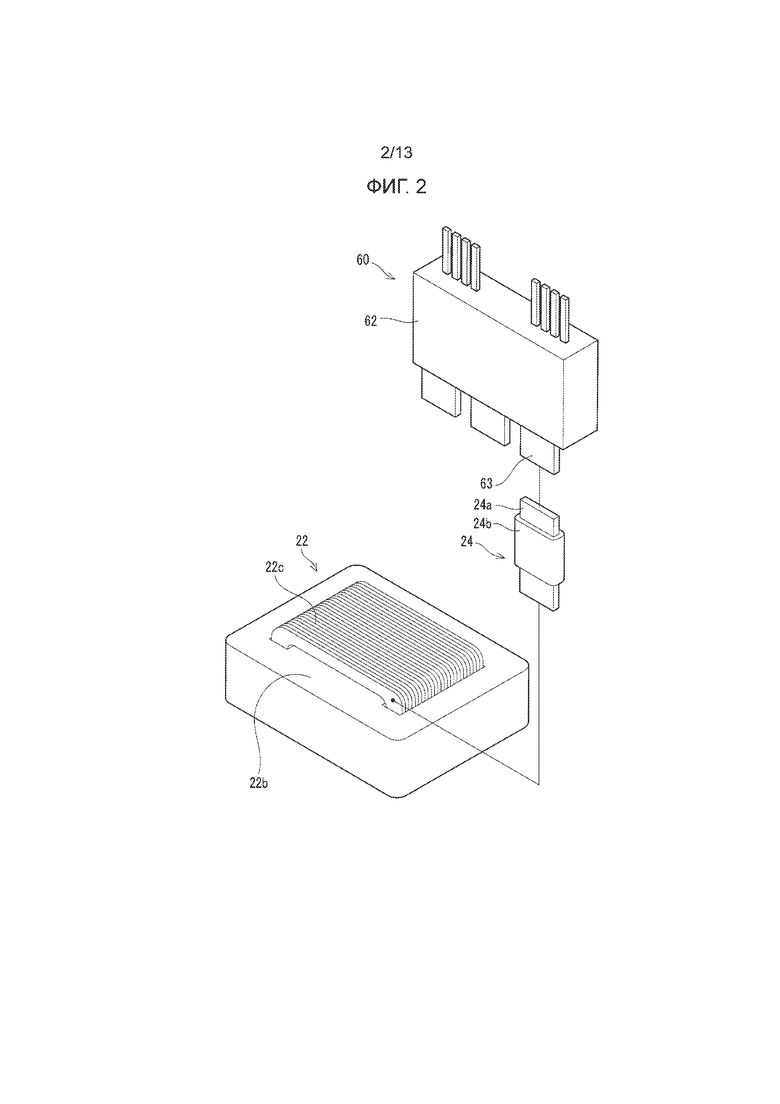

Фиг. 2 является видом в перспективе компонента, составляющего MOSFET, первый вспомогательный дроссель и основной дроссель;

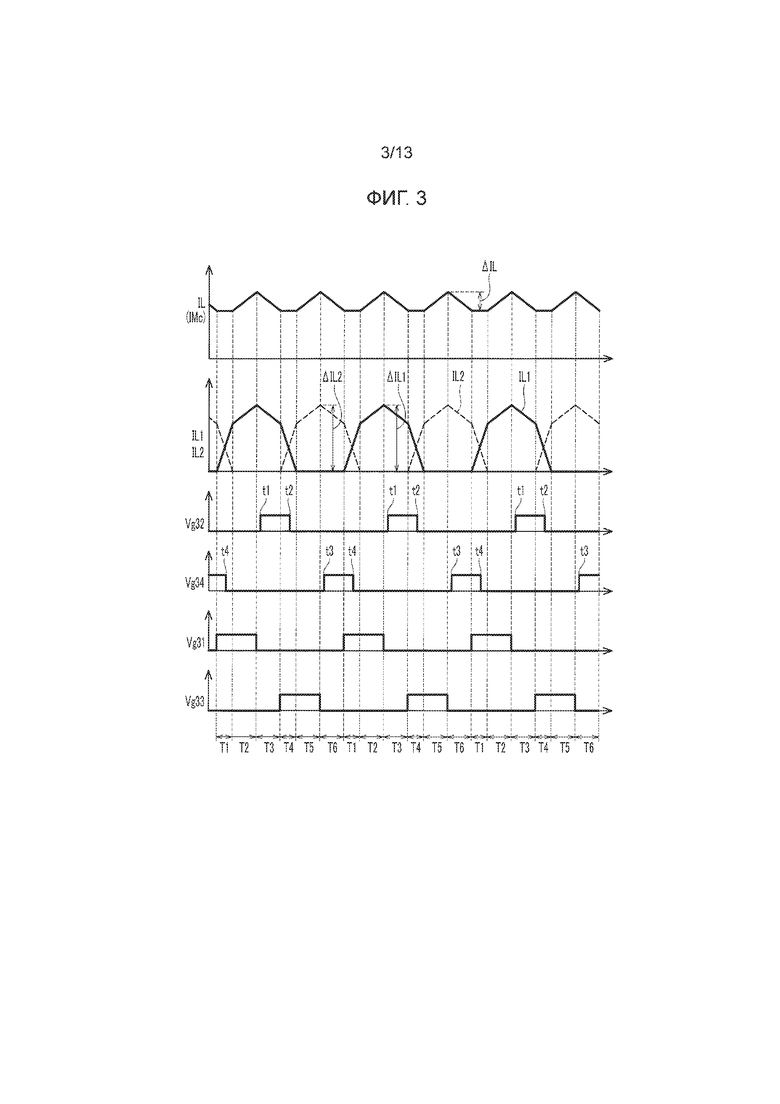

Фиг. 3 является графиком, показывающим изменение соответствующих значений в первой операции;

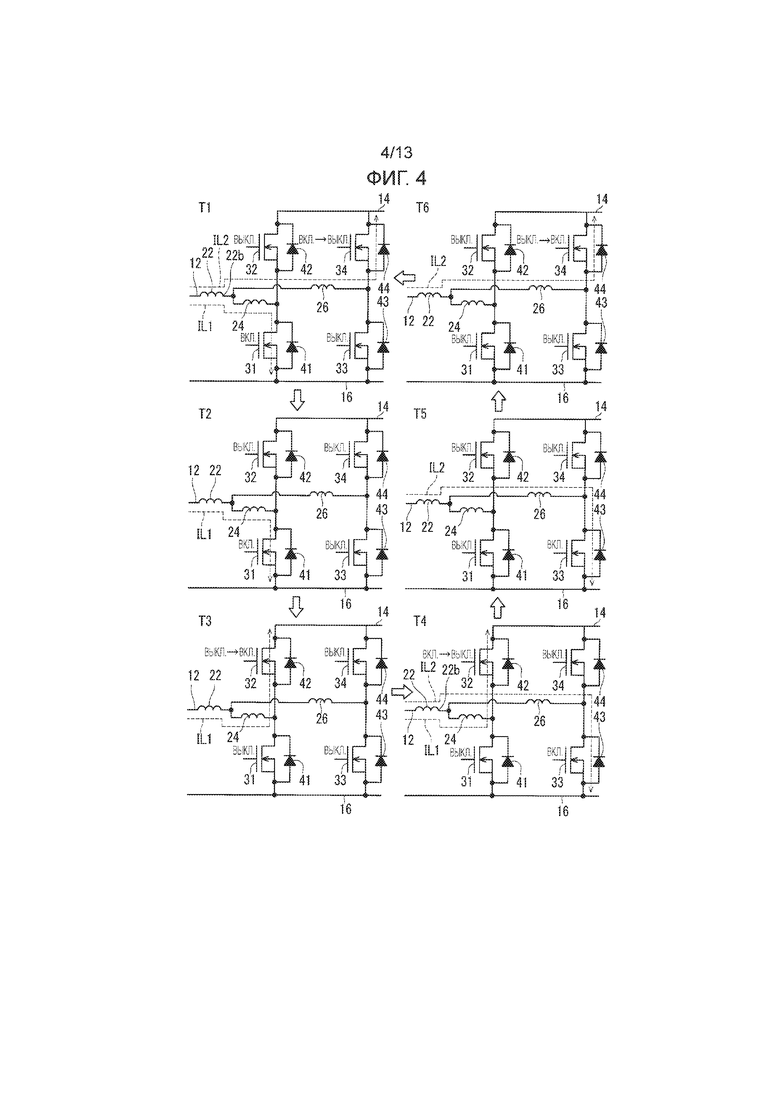

Фиг. 4 является схемой, показывающей изменение состояния преобразователя постоянного тока в постоянный в первой операции;

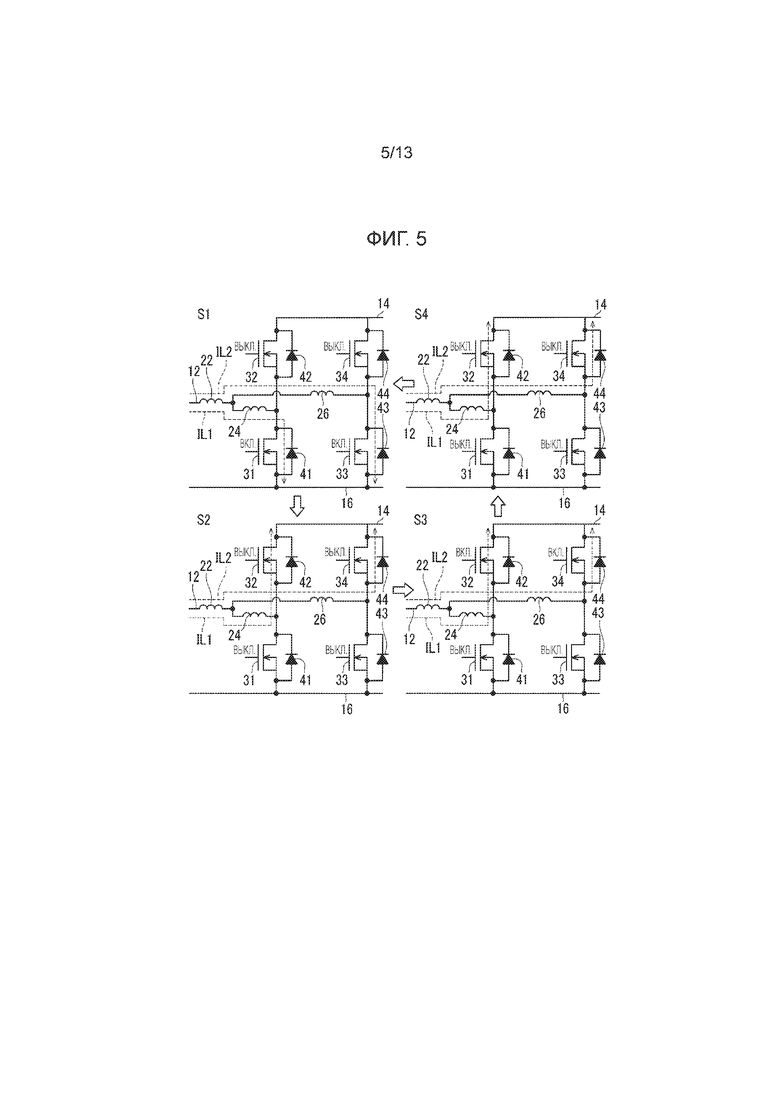

Фиг. 5 является схемой, показывающей изменение состояния преобразователя постоянного тока в постоянный во второй операции;

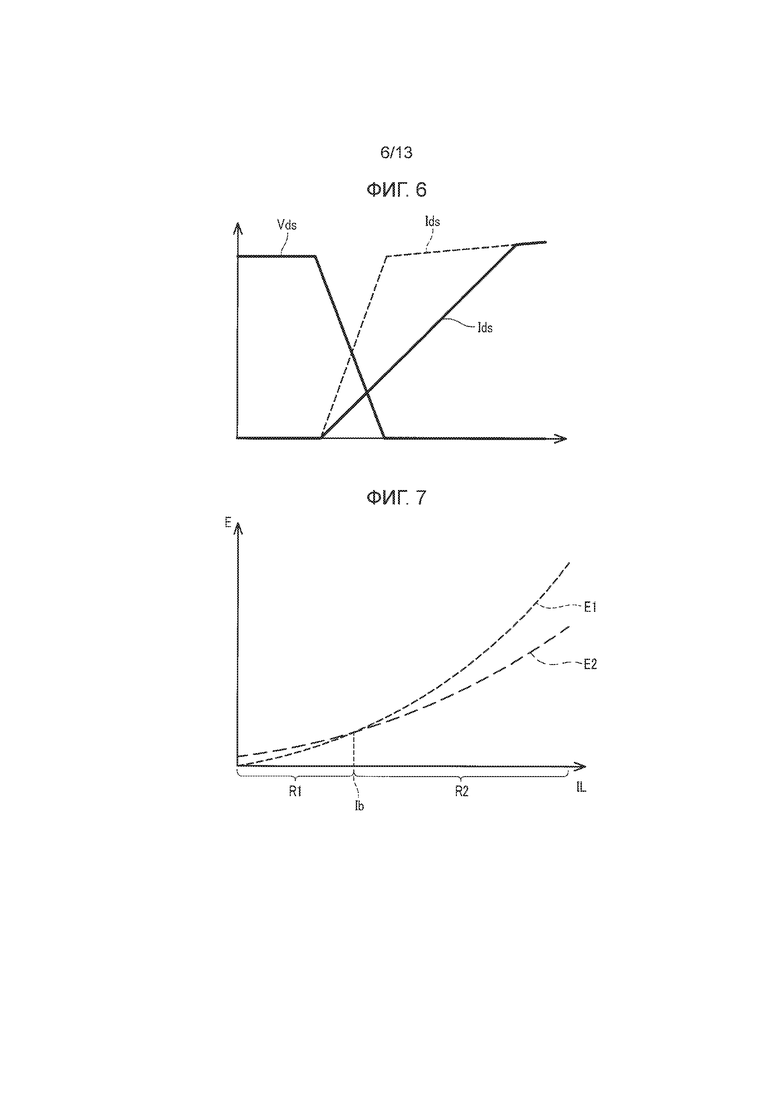

Фиг. 6 является графиком, показывающим изменение тока и напряжения, когда MOSFET включается;

Фиг. 7 является графиком, показывающим взаимосвязь между потерями E и током IL;

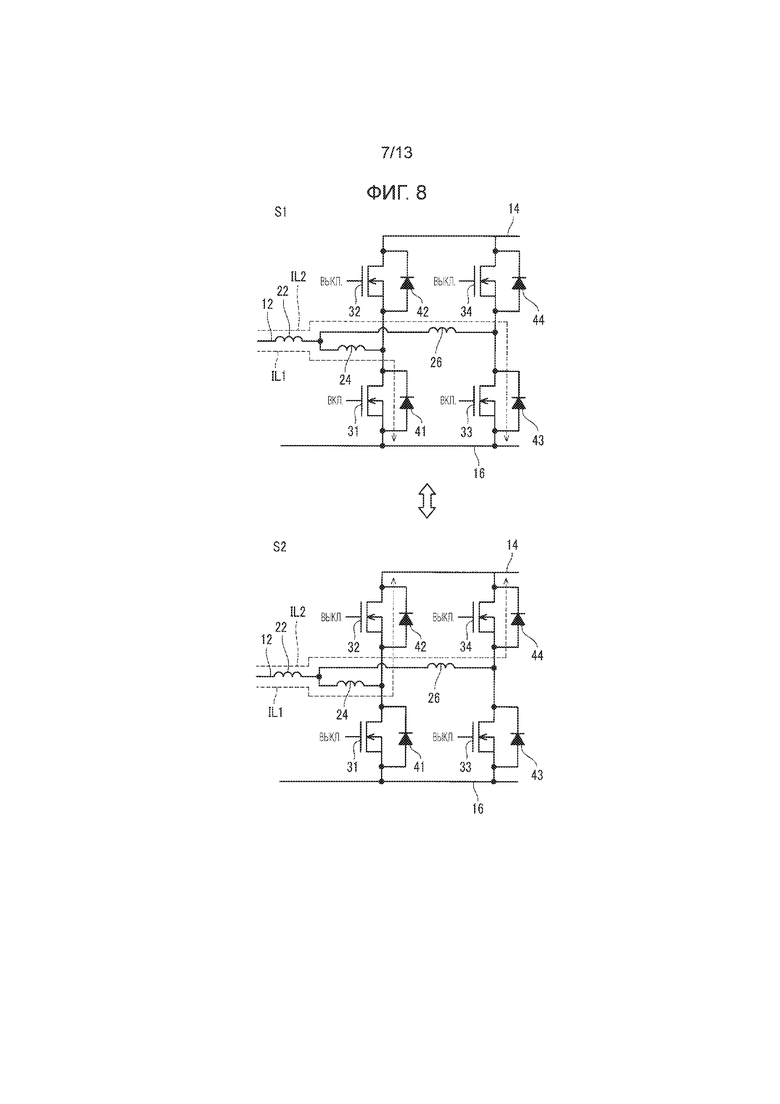

Фиг. 8 является схемой, показывающей изменение состояния преобразователя постоянного тока в постоянный во второй операции первого примера модификации;

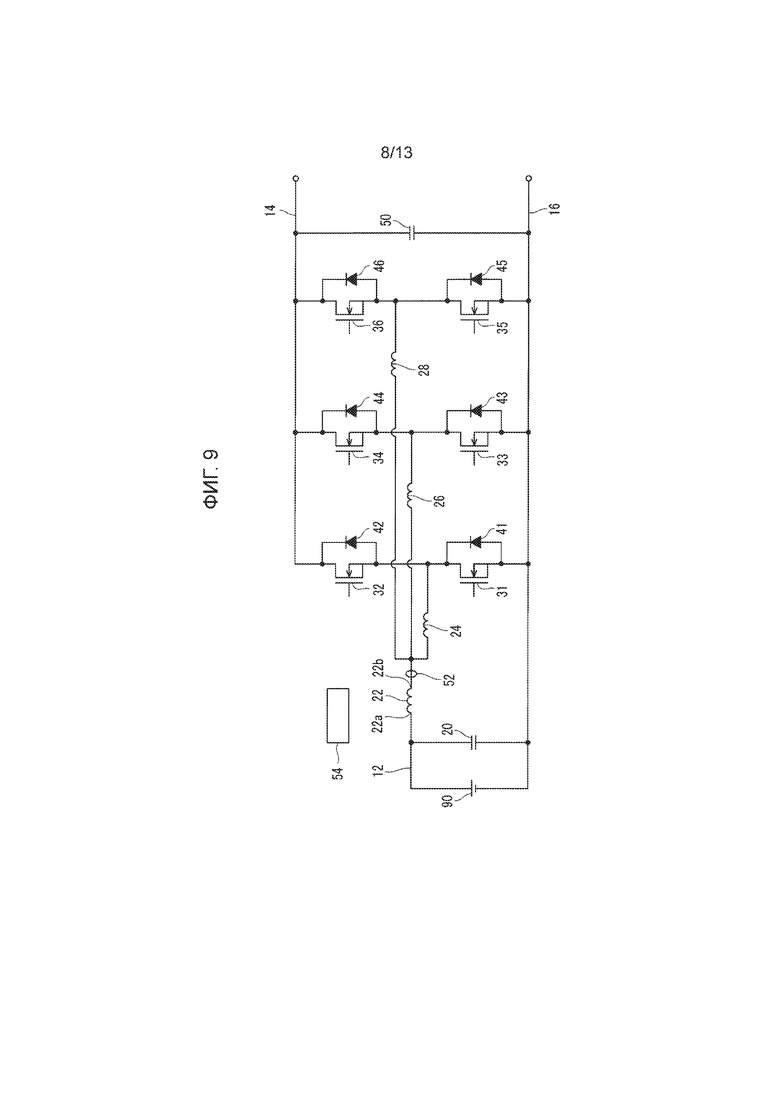

Фиг. 9 является принципиальной схемой преобразователя постоянного тока в постоянный второго примера модификации;

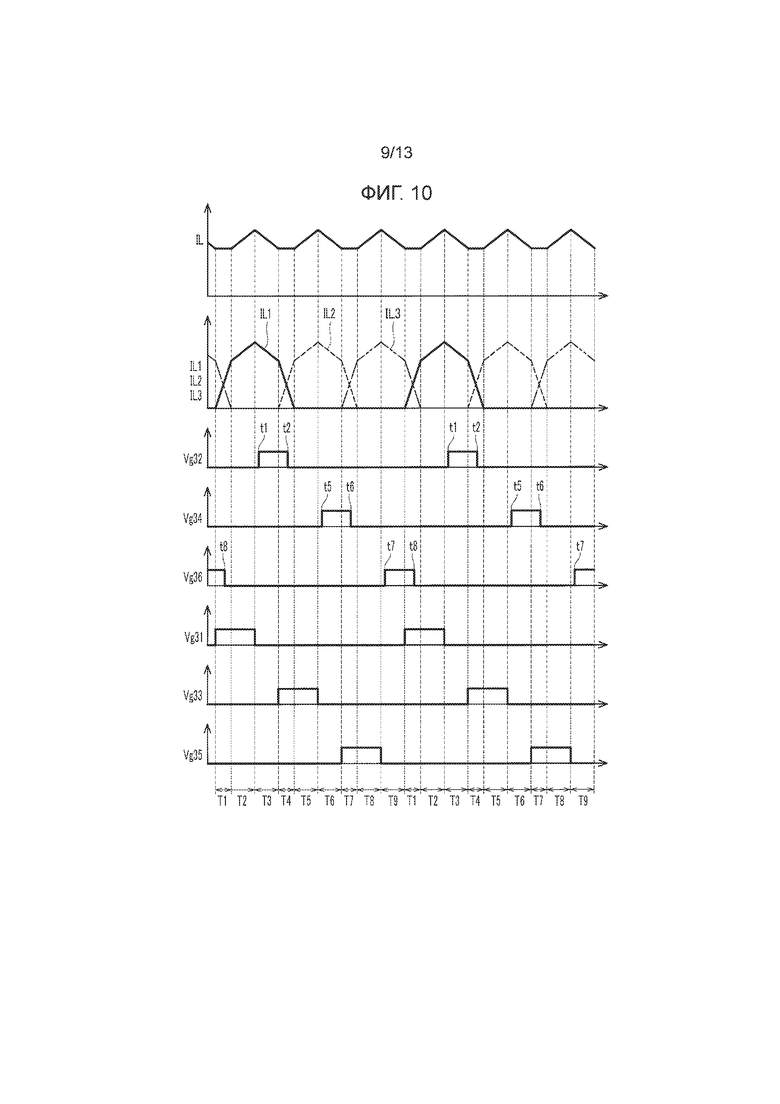

Фиг. 10 является графиком, показывающим изменение соответствующих значений в первой операции в преобразователе постоянного тока в постоянный второго примера модификации;

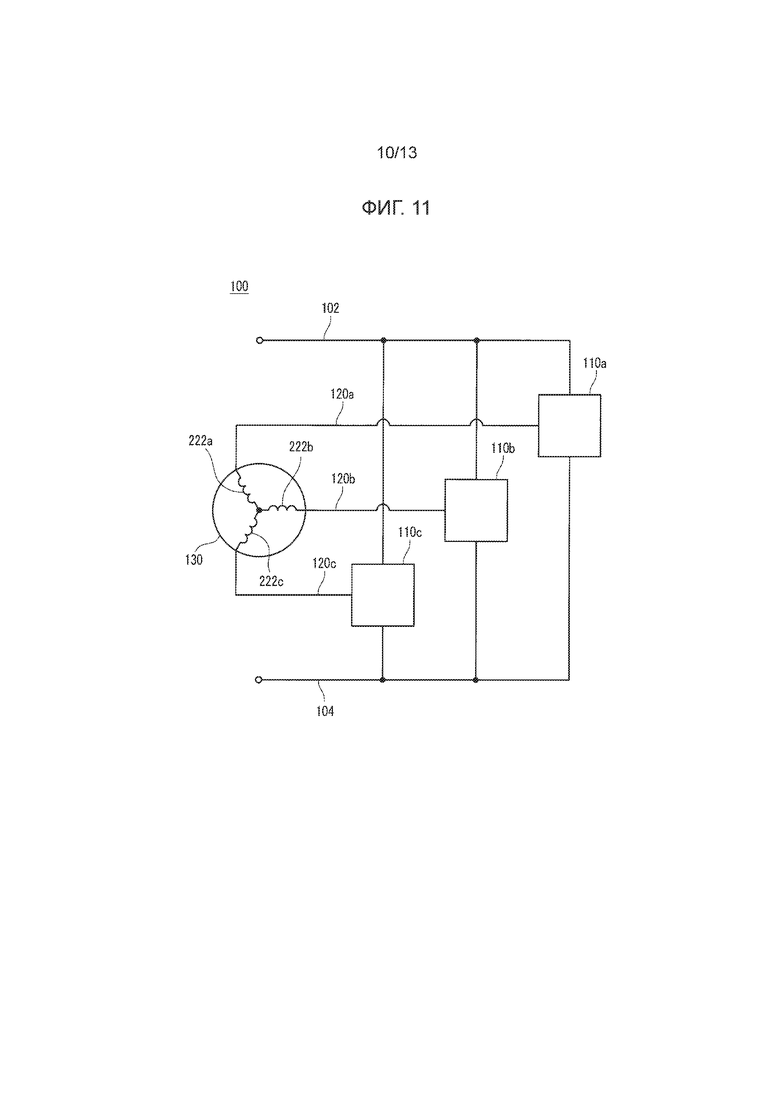

Фиг. 11 является принципиальной схемой инвертора;

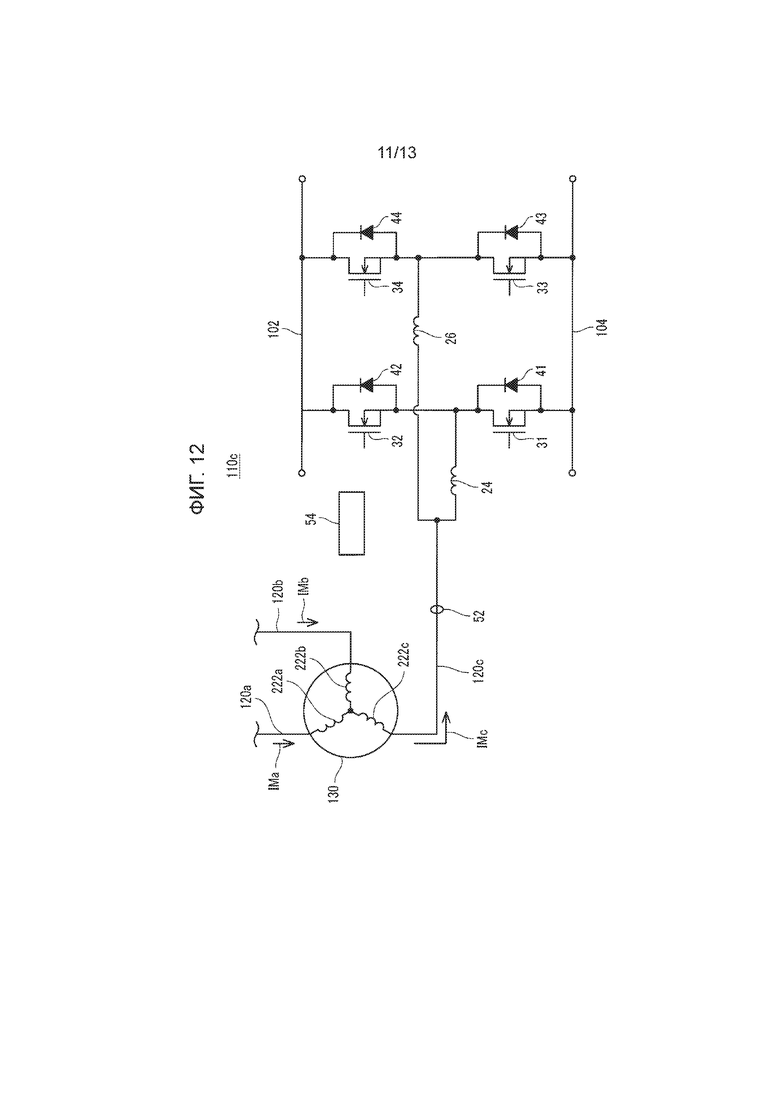

Фиг. 12 является принципиальной схемой переключающей схемы;

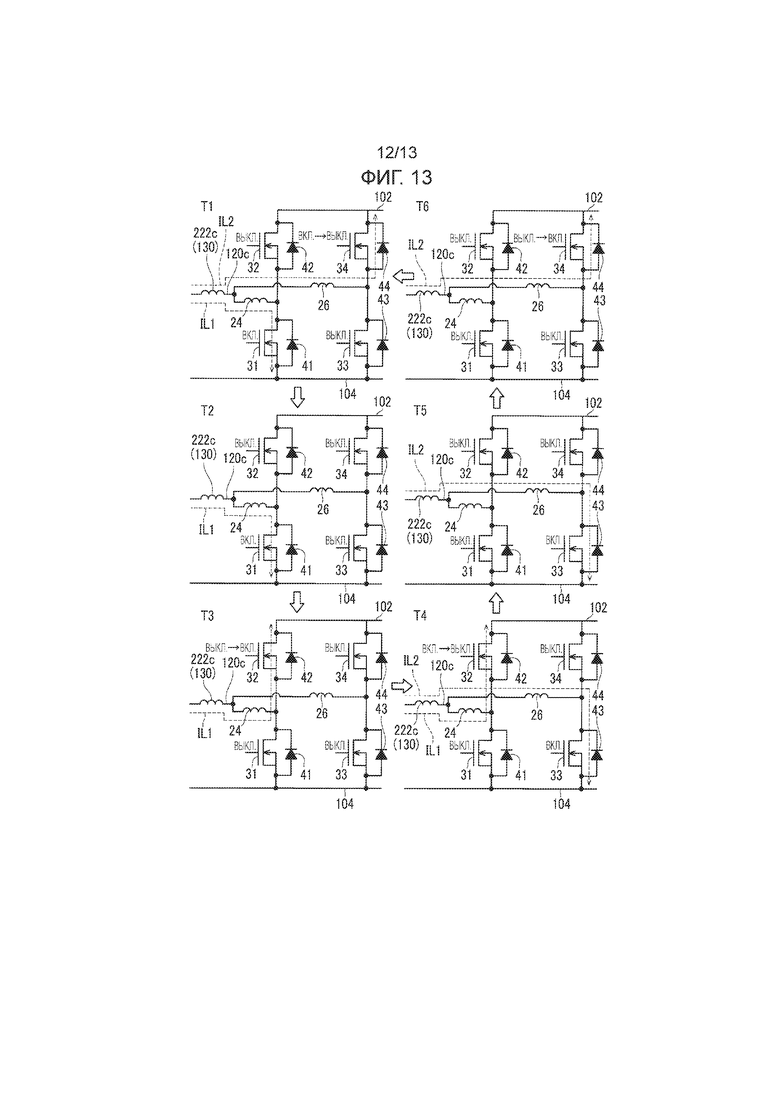

Фиг. 13 является схемой, показывающей изменение состояния переключающей схемы в первой операции; и

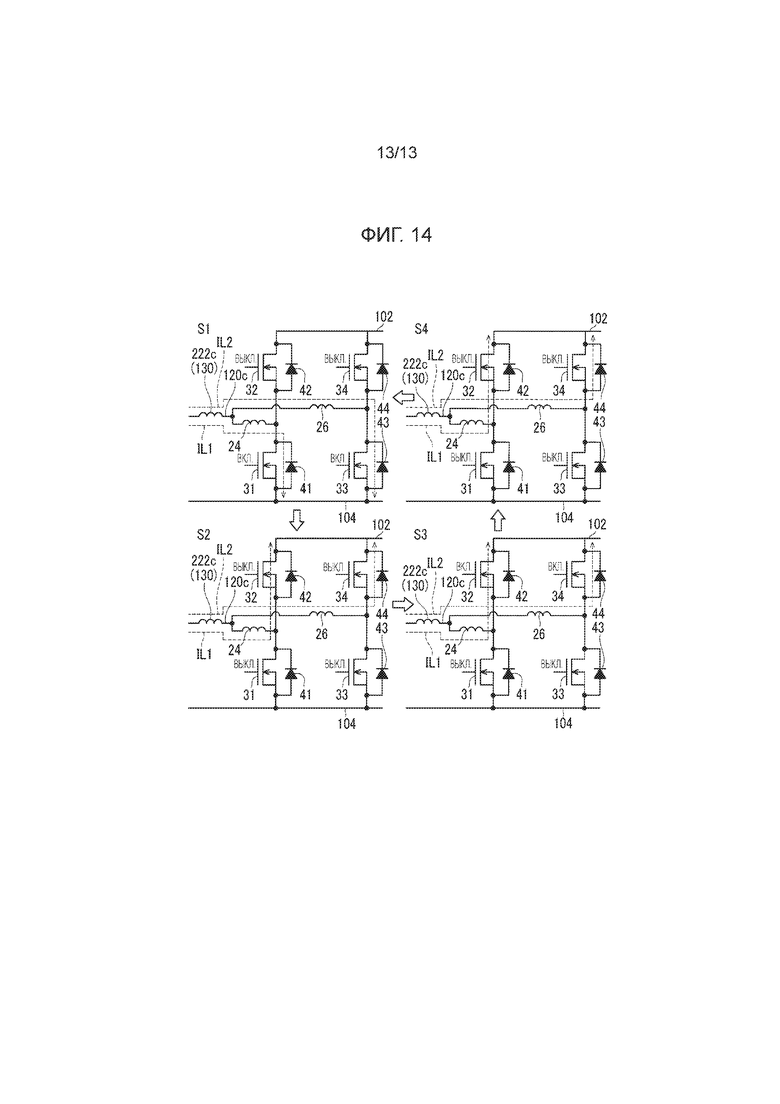

Фиг. 14 является схемой, показывающей изменение состояния переключающей схемы во второй операции.

Подробное описание вариантов осуществления

Фиг. 1 является принципиальной схемой преобразователя 10 постоянного тока в постоянный примера 1. Преобразователь 10 постоянного тока в постоянный монтируется в транспортном средстве. Преобразователь 10 постоянного тока в постоянный имеет входное межсоединение 12 с высоким потенциалом, выходное межсоединение 14 с высоким потенциалом и межсоединение 16 с низким потенциалом. Входное межсоединение 12 с высоким потенциалом соединяется с положительным электродом источника 90 мощности постоянного тока (например, аккумулятора). Межсоединение 16 с низким потенциалом соединяется с отрицательным электродом источника 90 мощности постоянного тока. Преобразователь 10 постоянного тока в постоянный повышает приложенное напряжение (т.е. напряжение между входным межсоединением 12 с высоким потенциалом и межсоединением 16 с низким потенциалом) источника 90 мощности постоянного тока и прикладывает повышенное напряжение между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом. Хотя не показано, инвертор или электромотор для движения соединяется в качестве нагрузки между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом. Соответственно, повышенное напряжение подается в нагрузку.

Преобразователь 10 постоянного тока в постоянный имеет сглаживающий конденсатор 20 на входной стороне, основной дроссель 22, первый вспомогательный дроссель 24, второй вспомогательный дроссель 26, MOSFET 31-34, диоды 41-44, сглаживающий конденсатор 50 на выходной стороне, датчик 52 тока и контроллер 54 затвора.

Сглаживающий конденсатор 20 на входной стороне соединяется между входным межсоединением 12 с высоким потенциалом и межсоединением 16 с низким потенциалом.

MOSFET 31, 32, 33, 34 представляют собой MOSFET с каналом n-типа. MOSFET 31 и MOSFET 32 последовательно соединяются между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом. Исток MOSFET 31 соединяется с межсоединением 16 с низким потенциалом. Сток MOSFET 31 соединяется с истоком MOSFET 32. Сток MOSFET 32 соединяется с выходным межсоединением 14 с высоким потенциалом. Диод 41 соединяется параллельно с MOSFET 31. Анод диода 41 соединяется с истоком MOSFET 31. Катод диода 41 соединяется со стоком MOSFET 31. Диод 42 соединяется параллельно с MOSFET 32. Анод диода 42 соединяется с истоком MOSFET 32. Катод диода 42 соединяется со стоком MOSFET 32. MOSFET 31, MOSFET 32, диод 41 и диод 42 состоят из компонента 60 с полупроводниковыми кристаллами, составляющими MOSFET 31, MOSFET 32, диод 41 и диод 42, герметизированные с помощью изоляционной смолы. Компонент 60 может упоминаться как плата питания. Как показано на фиг. 2, компонент 60 имеет изоляционную смолу 62 и множество контактных выводов, которые выступают наружу из изоляционной смолы 62. MOSFET 31, MOSFET 32, диод 41 и диод 42 встраиваются в изоляционной смоле 62 и соединяются с соответствующими контактными выводами в изоляционной смоле 62.

Как показано на фиг. 1, MOSFET 33 и MOSFET 34 последовательно соединяются между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом. Исток MOSFET 33 соединяется с межсоединением 16 с низким потенциалом. Сток MOSFET 33 соединяется с истоком MOSFET 34. Сток MOSFET 34 соединяется с выходным межсоединением 14 с высоким потенциалом. Диод 43 соединяется параллельно с MOSFET 33. Анод диода 43 соединяется с истоком MOSFET 33. Катод диода 43 соединяется со стоком MOSFET 33. Диод 44 соединяется параллельно с MOSFET 34. Анод диода 44 соединяется с истоком MOSFET 34. Катод диода 44 соединяется со стоком MOSFET 34. MOSFET 33, MOSFET 34, диод 43 и диод 44 состоят из компонента 64, аналогичного компоненту 60.

В дальнейшем в этом документе, MOSFET (т.е. MOSFET 31, 33) имеющий исток, соединенный с межсоединением 16 с низким потенциалом, упоминается как нижний MOSFET, и MOSFET (т.е. MOSFET 32, 34) имеющий сток, соединенный с выходным межсоединением 14 с высоким потенциалом упоминается как верхний MOSFET.

Основной дроссель 22 имеет первый контактный вывод 22a и второй контактный вывод 22b. Первый контактный вывод 22a соединяется с входным межсоединением 12 с высоким потенциалом. Как показано на фиг. 2, основной дроссель 22 имеет конструкцию, в которой обмотка 22c многократно наматывается вокруг сердечника 22d, изготовленного из материала с высокой магнитной проницаемостью.

Как показано на фиг. 1, первый конец первого вспомогательного дросселя 24 соединяется со вторым контактным выводом 22b основного дросселя 22. Второй конец первого вспомогательного дросселя 24 соединяется со стоком нижнего MOSFET 31 и истоком верхнего MOSFET 32. Индуктивность первого вспомогательного дросселя 24 меньше индуктивности основного дросселя 22. Как показано на фиг. 2, первый вспомогательный дроссель 24 имеет конструкцию, в которой периферия плоской пластинчатой шинной системы 24a, идущей линейно, покрывается сердечником 24b, изготовленным из материала с высокой магнитной проницаемостью. Поскольку индуктивность первого вспомогательного дросселя 24 не является сравнительно большой, первый вспомогательный дроссель 24 может предоставляться в конструкции, в которой периферия линейной шинной системы 24a покрывается сердечником 4b, вместо конструкции обмоток. Согласно вышеизложенному, первый вспомогательный дроссель 24 уменьшается по размеру. Первый конец шинной системы 24a соединяется с контактным выводом 63 (контактным выводом, соединенным со стоком нижнего MOSFET 31 и истоком верхнего MOSFET 32) компонента 60. Второй конец шинной системы 24a соединяется с первым концом (т.е. второй контактным выводом 22b) обмотки 22c основного дросселя 22.

Как показано на фиг. 1, первый конец второго вспомогательного дросселя 26 соединяется со вторым контактным выводом 22b основного дросселя 22. Второй конец второго вспомогательного дросселя 26 соединяется со стоком нижнего MOSFET 33 и истоком верхнего MOSFET 34. Индуктивность второго вспомогательного дросселя 26 меньше индуктивности основного дросселя 22. Второй вспомогательный дроссель 26 имеет конструкцию (конструкцию, в которой периферия линейной шинной системы закрыта сердечником), аналогичную первому вспомогательному дросселю 24, показанному на фиг. 2. Согласно вышеизложенному, второй вспомогательный дроссель 26 уменьшается по размеру.

Сглаживающий конденсатор 50 на выходной стороне соединяется между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом.

Датчик 52 тока определяет ток, который протекает в основном дросселе 22. Датчик 52 тока передает определенное значение тока в контроллер 54 затвора.

Контроллер 54 затвора соединяется с затвором каждого из MOSFET 31-34. Контроллер 54 затвора включает в себя схему возбуждения, которая выполняет заряд и разряд затвора для каждого MOSFET. Контроллер 54 затвора включает в себя схему управления, которая отправляет сигнал для командования включать или выключать MOSFET в схему возбуждения. Контроллер 54 затвора может независимо осуществлять управление для MOSFET 31-34.

Ниже описывается работа преобразователя 10 постоянного тока в постоянный. Контроллер 54 затвора осуществляет управление для MOSFET 31-34 таким образом, что нижний MOSFET 31 и верхний MOSFET 32 не находятся во включенном состоянии одновременно, и нижний MOSFET 33 и верхний MOSFET 34 не находятся во включенном состоянии одновременно, за исключением ошибочной операции вследствие шума и т.п. Согласно вышеизложенному, короткое замыкание между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом сдерживается. Контроллер 54 затвора может выполнять первую операцию и вторую операцию. Первая операция представляет собой операцию, чтобы эффективно подавлять потери на переключение (потери, сформированные во время переключения каждого MOSFET) преобразователя 10 постоянного тока в постоянный. Вторая операция представляет собой операцию, чтобы эффективнее уменьшать потери при переходе в установившееся состояние (потери, сформированные во время, отличное от переключения) преобразователя 10 постоянного тока в постоянный. Контроллер 54 затвора выполняет первую операцию, когда ток IL, определенный посредством датчика 52 тока, равен или меньше порогового значения Ith, и выполняет вторую операцию, когда ток IL, определенный посредством датчика 52 тока, превышает пороговое значение Ith. Контроллер 54 затвора осуществляет управление для MOSFET 31-34, за счет чего выполняются первая операция и вторая операция.

Во-первых, описывается первая операция. Фиг. 3 является графиком, показывающим изменение соответствующих значений в первой операции. На фиг. 3, ток IL представляет собой ток, который протекает в основном дросселе 22. Ток IL1 представляет собой ток, который протекает в первом вспомогательном дросселе 24. Ток IL2 представляет собой ток, который протекает во втором вспомогательном дросселе 26. Ток IL представляет собой совокупное значение тока IL1 и тока IL2. На фиг. 3, потенциал Vg31 представляет собой потенциал затвора нижнего MOSFET 31. Потенциал Vg32 представляет собой потенциал затвора верхнего MOSFET 32. Потенциал Vg33 представляет собой потенциал затвора нижнего MOSFET 33. Потенциал Vg34 представляет собой потенциал затвора верхнего MOSFET 34. Потенциалы Vg31-Vg34 затвора управляются посредством контроллера 54 затвора. Потенциалы Vg31-Vg34 затвора изменяются между высоким потенциалом и низким потенциалом. Когда потенциал затвора представляет собой высокий потенциал, MOSFET переводится во включенное состояние, и когда потенциал затвора представляет собой низкий потенциал, MOSFET переводится в отключенное состояние. Как показано на фиг. 3, в первой операции, контроллер 54 затвора осуществляет управление таким образом, что состояние преобразователя 10 постоянного тока в постоянный изменяется в порядке состояния T1, состояния T2, состояния T3, состояния T4, состояния T5 и состояния T6 и возвращается в состояние T1 сразу после состояния T6. Таким образом, контроллер 54 затвора осуществляет управление таким образом, что цикл состояний T1-T6 повторяется. Состояния T1-T6 показаны на фиг. 4. На фиг. 4, схемная конфигурация преобразователя 10 постоянного тока в постоянный упрощается по сравнению со схемной конфигурацией, показанной на фиг. 1.

Как показано на фиг. 3 и 4, в состоянии T1, нижний MOSFET 31 включается, верхний MOSFET 32 выключается, нижний MOSFET 33 выключается, и верхний MOSFET 34 переключается из включенного в выключенное состояние в середине периода состояния T1. В состоянии T1, поскольку нижний MOSFET 31 включается, ток IL1 вытекает из входного межсоединения 12 с высоким потенциалом в межсоединение 16 с низким потенциалом через основной дроссель 22, первый вспомогательный дроссель 24 и нижний MOSFET 31. Поскольку индуктивное напряжение (индуктивное напряжение, которое прикладывается в направлении блокирования тока IL1) первого вспомогательного дросселя 24 падает в период состояния T1, ток IL1 быстро увеличивается в период состояния T1. Хотя подробно описано ниже, в состоянии T1, ток IL2 вытекает из входного межсоединения 12 с высоким потенциалом в выходное межсоединение 14 с высоким потенциалом через основной дроссель 22, второй вспомогательный дроссель 26 и диод 44 с индуктивным напряжением второго вспомогательного дросселя 26. Тем не менее, ток IL2 быстро снижается в период состояния T1. Соответственно, в период состояния T1, ток IL практически не изменяется. В случае, если ток IL2 снижается до нуля в состоянии T1, состояние T2 задается.

В состоянии T2, нижний MOSFET 31 поддерживается во включенном состоянии, и ток IL1 непрерывно протекает. В период состояния T2, поскольку индуктивное напряжение основного дросселя 22 и индуктивное напряжение (индуктивное напряжение, которое прикладывается в направлении блокирования тока IL1) первого вспомогательного дросселя 24 падают, ток IL1 постепенно увеличивается в период состояния T2. По этой причине, ток IL также постепенно увеличивается. В конце периода состояния T2, нижний MOSFET 31 переключается из включенного состояния в выключенное состояние. Согласно вышеизложенному, преобразователь 10 постоянного тока в постоянный выполняет переход из состояния T2 в состояние T3.

В начале периода состояния T3, верхний MOSFET 32 выключается. В случае, если нижний MOSFET 31 выключается в начале состояния T3, основной дроссель 22 и первый вспомогательный дроссель 24 формируют индуктивные напряжения в направлении разрешения току IL1 непрерывно протекать; в силу этого потенциал на аноде диода 42 повышается. По этой причине, ток IL1 вытекает из входного межсоединения 12 с высоким потенциалом в выходное межсоединение 14 с высоким потенциалом через основной дроссель 22, первый вспомогательный дроссель 24 и диод 42. Ток IL1 протекает в выходное межсоединение 14 с высоким потенциалом, как описано выше, за счет чего сглаживающий конденсатор 50 на выходной стороне (см. фиг. 1) заряжается, и потенциал на выходном межсоединении 14 с высоким потенциалом повышается. В период состояния T3, поскольку индуктивные напряжения (индуктивные напряжения, которые прикладываются в направлении разрешения току IL1 протекать) основного дросселя 22 и первого вспомогательного дросселя 24 падают, ток IL1 постепенно снижается в период состояния T3. По этой причине, ток IL также постепенно снижается.

Во время t1 в середине периода состояния T3, верхний MOSFET 32 переключается из выключенного состояния во включенное состояние. В случае, если верхний MOSFET 32 включается, ток IL1 разветвляется и протекает в диод 42 и верхний MOSFET 32. Согласно вышеизложенному, плотность тока диода 42 понижается, и потери, которые формируются вследствие тока IL1, становятся небольшими. Подробнее, потери, которые формируются в диоде 42 и верхнем MOSFET 32, когда ток IL1 разветвляется и протекает в диод 42 и верхний MOSFET 32, становятся меньше потерь, которые формируются в диоде 42, когда верхний MOSFET 32 выключается, и ток IL1 протекает в диоде 42. Как описано выше, верхний MOSFET 32 включается, когда ток IL1 протекает в диоде 42, за счет чего можно эффективнее уменьшать потери. В частности, в случае, если паразитный диод (диод, состоящий из p-n-перехода поверхности раздела полупроводниковой области с каналом n-типа на исходной стороне MOSFET и полупроводниковой области с каналом p-типа, составляющей слой канала) верхнего MOSFET 32 используется в качестве диода 42, плотность тока диода 42 с большой вероятностью должна становиться высокой. Соответственно, верхний MOSFET 32 включается, чтобы понижать плотность тока диода 42, за счет чего можно эффективно подавлять потери. В конце периода состояния T3, нижний MOSFET 33 переключается из выключенного состояния во включенное состояние. Согласно вышеизложенному, преобразователь 10 постоянного тока в постоянный выполняет переход из состояния T3 в состояние T4.

В начале периода состояния T4, верхний MOSFET 32 поддерживается во включенном состоянии. Таким образом, в начале периода состояния T4 оба из верхнего MOSFET 32 и нижнего MOSFET 33 включаются. По этой причине, выходное межсоединение 14 с высоким потенциалом и межсоединение 16 с низким потенциалом соединяются через верхний MOSFET 32, первый вспомогательный дроссель 24, второй вспомогательный дроссель 26 и нижний MOSFET 33. Тем не менее, поскольку напряжение между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом сохраняется с помощью первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26, чрезмерный ток не протекает между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом. Таким образом, выходное межсоединение 14 с высоким потенциалом и межсоединение 16 с низким потенциалом не переводятся в состояние короткого замыкания.

В состоянии T4, поскольку нижний MOSFET 33 включается, ток IL2 вытекает из входного межсоединения 12 с высоким потенциалом в межсоединение 16 с низким потенциалом через основной дроссель 22, второй вспомогательный дроссель 26 и нижний MOSFET 33. Поскольку индуктивное напряжение (индуктивное напряжение, которое прикладывается в направлении блокирования тока IL2) второго вспомогательного дросселя 26 падает в период состояния T4, ток IL2 быстро увеличивается в период состояния T4. В период состояния T4, ток IL1 протекает непрерывно от периода состояния T3. Тем не менее, в период состояния T4, поскольку нижний MOSFET 33 включается, и потенциал на втором контактном выводе 22b основного дросселя 22 быстро падает, ток IL1 быстро снижается. Соответственно, в состоянии T4, ток IL практически не изменяется.

В начале периода состояния T4, поскольку верхний MOSFET 32 включается, ток IL1 разветвляется и протекает в диод 42 и верхний MOSFET 32. Согласно вышеизложенному, потери, которые формируются, когда протекает ток IL1, эффективнее уменьшаются. Тем не менее, в случае, если время включения верхнего MOSFET 32 является чрезмерно большим, ток может протекать обратно в верхний MOSFET 32, и выходное межсоединение 14 с высоким потенциалом и межсоединение 16 с низким потенциалом могут замыкаться накоротко. По этой причине, во время t2 в середине периода состояния T4, верхний MOSFET 32 переключается из включенного состояния в выключенное состояние. Даже если верхний MOSFET 32 выключается, ток IL1 непрерывно протекает через диод 42. После того, как верхний MOSFET 32 выключается, ток IL1 снижается до нуля. В случае, если ток IL1 снижается до нуля, состояние T5 задается.

В состоянии T5, нижний MOSFET 33 поддерживается во включенном состоянии, и ток IL2 непрерывно протекает. В период состояния T5, поскольку индуктивное напряжение основного дросселя 22 и индуктивное напряжение (индуктивное напряжение, которое прикладывается в направлении блокирования тока IL2) второго вспомогательного дросселя 26 падают, ток IL2 постепенно увеличивается в период состояния T5. По этой причине, ток IL также постепенно увеличивается. В конце периода состояния T5, нижний MOSFET 33 переключается из включенного состояния в выключенное состояние. Согласно вышеизложенному, преобразователь 10 постоянного тока в постоянный выполняет переход из состояния T5 в состояние T6.

В начале периода состояния T6, верхний MOSFET 34 выключается. В случае, если нижний MOSFET 33 выключается в начале состояния T6, основной дроссель 22 и второй вспомогательный дроссель 26 формируют индуктивные напряжения в направлении разрешения току IL2 непрерывно протекать; в силу этого потенциал анода диода 44 повышается. По этой причине, ток IL2 вытекает из входного межсоединения 12 с высоким потенциалом в выходное межсоединение 14 с высоким потенциалом через основной дроссель 22, второй вспомогательный дроссель 26 и диод 44. Ток IL2 протекает в выходное межсоединение 14 с высоким потенциалом, как описано выше, за счет чего сглаживающий конденсатор 50 на выходной стороне (см. фиг. 1) заряжается, и потенциал на выходном межсоединении 14 с высоким потенциалом повышается. В период состояния T6, поскольку индуктивные напряжения (индуктивные напряжения, которые прикладываются в направлении разрешения току IL2 протекать) основного дросселя 22 и второго вспомогательного дросселя 26 падают, ток IL2 постепенно снижается в период состояния T6. По этой причине, ток IL также постепенно снижается.

Во время t3 в середине периода состояния T6, верхний MOSFET 34 переключается из выключенного состояния во включенное состояние. В случае, если верхний MOSFET 34 включается, ток IL2 разветвляется и протекает в диод 44 и верхний MOSFET 34. Согласно вышеизложенному, плотность тока диода 44 понижается, и потери, которые формируются вследствие тока IL2, становятся относительно небольшими. Подробнее, потери, которые формируются в диоде 44 и верхнем MOSFET 34, когда ток IL2 разветвляется и протекает в диод 44 и верхний MOSFET 34, становятся меньше потерь, которые формируются в диоде 44, когда верхний MOSFET 34 выключается, и ток IL2 протекает в диоде 44. Как описано выше, верхний MOSFET 34 включается, когда ток IL2 протекает в диоде 44, за счет чего можно эффективнее уменьшать потери. В частности, в случае, если паразитный диод верхнего MOSFET 34 используется в качестве диода 44, плотность тока диода 44 с большой вероятностью должна становиться высокой. Соответственно, верхний MOSFET 34 включается, чтобы понижать плотность тока диода 44, за счет чего можно эффективно подавлять потери. В конце периода состояния T6, нижний MOSFET 31 переключается из выключенного состояния во включенное состояние. Согласно вышеизложенному, преобразователь 10 постоянного тока в постоянный выполняет переход из состояния T6 до вышеописанного состояния T1.

В начале периода состояния T1, верхний MOSFET 34 поддерживается во включенном состоянии. Таким образом, в начале периода состояния T1, оба из нижнего MOSFET 31 и верхнего MOSFET 34 включаются. По этой причине, выходное межсоединение 14 с высоким потенциалом и межсоединение 16 с низким потенциалом соединяются через верхний MOSFET 34, второй вспомогательный дроссель 26, первый вспомогательный дроссель 24 и нижний MOSFET 31. Тем не менее, поскольку напряжение между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом сохраняется с помощью первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26, чрезмерный ток не протекает между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом. Таким образом, выходное межсоединение 14 с высоким потенциалом и межсоединение 16 с низким потенциалом не переводятся в состояние короткого замыкания.

Как описано выше, в состоянии T1, поскольку нижний MOSFET 31 включается, ток IL1 вытекает из входного межсоединения 12 с высоким потенциалом в межсоединение 16 с низким потенциалом через основной дроссель 22, первый вспомогательный дроссель 24 и нижний MOSFET 31. Как описано выше, ток IL1 быстро увеличивается в период состояния T1. В период состояния T1, ток IL2 протекает непрерывно от периода состояния T6. Тем не менее, в период состояния T1, поскольку нижний MOSFET 31 включается, и потенциал на втором контактном выводе 22b основного дросселя 22 быстро падает, ток IL2 быстро снижается. Соответственно, в состоянии T1, ток IL практически не изменяется.

В начале периода состояния T1, поскольку верхний MOSFET 34 включается, ток IL2 разветвляется и протекает в диод 44 и верхний MOSFET 34. Согласно вышеизложенному, потери, которые формируются, когда протекает ток IL2, эффективнее уменьшаются. Тем не менее, в случае, если время включения верхнего MOSFET 34 является чрезмерно большим, ток может протекать обратно в верхний MOSFET 34, и выходное межсоединение 14 с высоким потенциалом и межсоединение 16 с низким потенциалом могут замыкаться накоротко. По этой причине, во время t4 в середине периода состояния T1, верхний MOSFET 34 переключается из включенного состояния в выключенное состояние. Даже если верхний MOSFET 34 выключается, ток IL2 непрерывно протекает через диод 44. После того, как верхний MOSFET 34 выключается, ток IL2 снижается до нуля.

Как описано выше, в первой операции, цикл состояний T1-T6 повторяется многократно. В примере 1, когда переход выполняется из состояния T3 в состояние T4, верхний MOSFET 32 поддерживается во включенном состоянии от времени t1 в середине периода состояния T3 до времени t2 в середине периода состояния T4. Согласно вышеизложенному, потери, которые формируются, когда протекает ток IL1, эффективнее уменьшаются. В частности, в примере 1, оба из верхнего MOSFET 32 и нижнего MOSFET 33 переводятся во включенное состояние в начале периода состояния T4. Тем не менее, поскольку напряжение между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом сохраняется с помощью первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26, короткое замыкание между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом сдерживается. Верхний MOSFET 32 поддерживается во включенном состоянии до времени t2 в середине периода состояния T4, за счет чего можно увеличивать период, в течение которого верхний MOSFET 32 находится во включенном состоянии. Соответственно, можно эффективнее уменьшать потери, которые формируются, когда протекает ток IL1.

В примере 1, когда переход выполняется из состояния T6 в состояние T1, верхний MOSFET 34 поддерживается во включенном состоянии от времени t3 в середине периода состояния T6 до времени t4 в середине периода состояния T1. Согласно вышеизложенному, потери, которые формируются, когда протекает ток IL2, эффективнее уменьшаются. В частности, в примере 1, оба из верхнего MOSFET 34 и нижнего MOSFET 31 переводятся во включенное состояние в начале периода состояния T1. Тем не менее, поскольку напряжение между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом сохраняется с помощью первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26, короткое замыкание между выходным межсоединением 14 с высоким потенциалом и межсоединением 16 с низким потенциалом сдерживается. Верхний MOSFET 34 поддерживается во включенном состоянии до времени t4 в середине периода состояния T1, за счет чего можно увеличивать период, в течение которого верхний MOSFET 34 находится во включенном состоянии, и эффективнее уменьшать потери, которые формируются, когда протекает ток IL2.

В первой операции, как показано на фиг. 3, амплитуда ΔIL флуктуации тока IL является относительно небольшой. По этой причине, потери, которые формируются в основном дросселе 22, являются относительно небольшими. В первой операции, амплитуда ΔIL1, ΔIL2 флуктуации токов IL1, IL2 является относительно большой. Тем не менее, поскольку индуктивность каждого из первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26 является относительно небольшой, потери, которые формируются в каждом из первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26, являются относительно небольшими. Как описано выше, в первой операции, можно эффективно подавлять потери, которые формируются в каждом дросселе.

Ниже описывается вторая операция. Как показано на фиг. 5, во второй операции, контроллер 54 затвора осуществляет управление таким образом, что состояние преобразователя 10 постоянного тока в постоянный изменяется в порядке состояния S1, состояния S2, состояния S3 и состояния S4 и возвращается в состояние S1 сразу после состояния S4. Таким образом, контроллер 54 затвора осуществляет управление таким образом, что цикл состояний S1-S4 повторяется.

В состоянии S1, оба из нижнего MOSFET 31 и нижнего MOSFET 33 включаются, и оба из верхнего MOSFET 32 и верхнего MOSFET 34 выключаются. По этой причине, ток IL1 вытекает из входного межсоединения 12 с высоким потенциалом в межсоединение 16 с низким потенциалом через основной дроссель 22, первый вспомогательный дроссель 24 и нижний MOSFET 31, и ток IL2 вытекает из входного межсоединения 12 с высоким потенциалом в межсоединение 16 с низким потенциалом через основной дроссель 22, второй вспомогательный дроссель 26 и нижний MOSFET 33. В период состояния S1, поскольку индуктивные напряжения (индуктивные напряжения, которые прикладываются в направлениях блокирования токов IL1, IL2) дросселей постепенно падают, токи IL1, IL2 постепенно увеличиваются. В конце периода состояния S1, нижний MOSFET 31 и нижний MOSFET 33 переключаются из включенного состояния в выключенное состояние. Согласно вышеизложенному, преобразователь 10 постоянного тока в постоянный выполняет переход из состояния S1 в состояние S2.

В случае, если нижний MOSFET 31 и нижний MOSFET 33 выключаются в начале состояния S2, основной дроссель 22 и первый вспомогательный дроссель 24 формируют индуктивные напряжения в направлении разрешения току IL1 непрерывно протекать, и основной дроссель 22 и второй вспомогательный дроссель 26 формируют индуктивные напряжения в направлении разрешения току IL2 непрерывно протекать. Поскольку потенциал на аноде диода 42 повышается за счет индуктивных напряжений основного дросселя 22 и первого вспомогательного дросселя 24, ток IL1 протекает в диоде 42. Таким образом, ток IL1 вытекает из входного межсоединения 12 с высоким потенциалом в выходное межсоединение 14 с высоким потенциалом через основной дроссель 22, первый вспомогательный дроссель 24 и диод 42. Поскольку потенциал на аноде диода 44 повышается за счет индуктивных напряжений основного дросселя 22 и второго вспомогательного дросселя 26, ток IL2 протекает в диоде 44. Таким образом, ток IL2 вытекает из входного межсоединения 12 с высоким потенциалом в выходное межсоединение 14 с высоким потенциалом через основной дроссель 22, второй вспомогательный дроссель 26 и диод 44. Токи IL1, IL2 протекают, как описано выше, за счет чего сглаживающий конденсатор 50 на выходной стороне (см. фиг. 1) заряжается, и потенциал на выходном межсоединении 14 с высоким потенциалом повышается. В конце периода состояния S2, верхний MOSFET 32 и верхний MOSFET 34 переключаются из выключенного состояния во включенное состояние. Согласно вышеизложенному, преобразователь 10 постоянного тока в постоянный выполняет переход из состояния S2 в состояние S3.

Даже в состоянии S3, ток IL1 протекает через диод 42, и ток IL2 протекает через диод 44. Верхний MOSFET 32 включается, за счет чего ток IL1 разветвляется и протекает в верхний MOSFET 32 и диод 42. Согласно вышеизложенному, потери, которые формируются, когда протекает ток IL1, эффективнее уменьшаются. Верхний MOSFET 34 включается, за счет чего ток IL2 разветвляется и протекает в верхний MOSFET 34 и диод 44. Согласно вышеизложенному, потери, которые формируются, когда протекает ток IL2, эффективнее уменьшаются. В конце периода состояния S3, верхний MOSFET 32 и верхний MOSFET 34 переключаются из включенного состояния в выключенное состояние. Согласно вышеизложенному, преобразователь 10 постоянного тока в постоянный выполняет переход из состояния S3 в состояние S4.

Даже в состоянии S4, аналогично состоянию S2, ток IL1 протекает через диод 42, и ток IL2 протекает через диод 44. В конце периода состояния S4, нижний MOSFET 31 и нижний MOSFET 33 переключаются из выключенного состояния во включенное состояние. Согласно вышеизложенному, преобразователь 10 постоянного тока в постоянный выполняет переход из состояния S4 в состояние S1.

В период состояний S2, S3, S4, поскольку индуктивные напряжения (индуктивные напряжения, которые прикладываются в направлениях разрешения токам IL1, IL2 протекать) дросселей постепенно падают, токи IL1, IL2 постепенно снижаются.

Как описано выше, во второй операции, состояние (состояние S1), в котором оба из нижних MOSFET 31, 33 включаются, и состояние (состояния S2, S3, S4), в котором оба из нижних MOSFET 31, 33 выключаются, попеременно повторяются. Даже во второй операции, можно повышать потенциал на выходном межсоединении 14 с высоким потенциалом.

Фиг. 6 показывает изменение напряжения Vds стока-истока и тока Ids стока-истока, когда нижние MOSFET 31, 33 включаются. На фиг. 6, график в форме сплошной линии тока Ids показывает изменение тока Ids в первой операции. График в виде ломаной линии тока Ids показывает изменение тока Ids во второй операции. В обеих из первой операции и второй операции, в случае, если нижние MOSFET 31, 33 включаются, напряжение Vds быстро падает, и ток Ids быстро увеличивается. В обеих из первой операции и второй операции, после того, как нижние MOSFET 31, 33 включаются, как описано выше, ток Ids (т.е. ток IL1 или IL2) постепенно увеличивается.

Как показано на фиг. 5, во второй операции, в состоянии (в состоянии S4) сразу до того, как нижний MOSFET 31 включается, ток IL1 протекает в основном дросселе 22 и первом вспомогательном дросселе 24. По этой причине, ток IL1 вытекает из основного дросселя 22 и первого вспомогательного дросселя 24 в нижний MOSFET 31 практически одновременно, нижний MOSFET 31 включается. По этой причине, во второй операции, как показано на графике в виде ломаной линии тока Ids по фиг. 6, темп увеличения тока Ids, когда нижний MOSFET 31 включается, является относительно высоким. Соответственно, во второй операции, потери (потери на переключение), которые формируются, когда нижний MOSFET 31 включается, являются относительно большими. Аналогично, во второй операции, потери на переключение, которые формируются, когда нижний MOSFET 33 включается, являются относительно большими.

Как показано на фиг. 4, в первой операции, в состоянии (в состоянии T6) непосредственно перед тем, как нижний MOSFET 31 включается, ток IL1 не протекает в первом вспомогательном дросселе 24. По этой причине, в то время как ток IL1 начинает протекать в нижнем MOSFET 31 одновременно с тем, как нижний MOSFET 31 включается, темп увеличения тока IL1 не является сравнительно высоким. По этой причине, в первой операции, как показано на графике в форме сплошной линии тока Ids по фиг. 6, темп увеличения тока Ids, когда нижний MOSFET 31 включается, ниже во второй операции. Соответственно, в первой операции, потери на переключение, которые формируются, когда нижний MOSFET 31 включается, являются относительно небольшими. Аналогично, в первой операции, потери на переключение, которые формируются, когда нижний MOSFET 33 включается, являются относительно небольшими.

Как описано выше, в первой операции, можно подавлять потери на переключение, которые формируются в нижних MOSFET 31, 33, по сравнению со второй операцией.

В обеих из первой операции и второй операции, когда нижние MOSFET 31, 33 включаются, потенциалы на анодах диодов 42, 44 падают, и обратное напряжение прикладывается к диодам 42, 44. В случае, если приложенное напряжение к диодам 42, 44 переключается с прямого напряжения на обратное напряжение, ток восстановления (обратный ток, который протекает в течение короткого времени) протекает в диодах 42, 44. В случае, если ток восстановления протекает, потери на восстановление (вид потерь на переключение) формируются в диодах 42, 44.

Как показано на фиг. 5, во второй операции, когда переход выполняется из состояния S4 в состояние S1, потенциалы на анодах диодов 42, 44 понижаются с высокого потенциала (потенциала выше потенциала на выходном межсоединении 14 с высоким потенциалом) до низкого потенциала (потенциала на межсоединении 16 с низким потенциалом). Таким образом, приложенное напряжение к диодам 42, 44 переключается с прямого напряжения на обратное напряжение. По этой причине, потери на восстановление формируются в диодах 42, 44.

Как показано на фиг. 4, в первой операции, когда нижний MOSFET 31 включается (т.е. когда переход выполняется из состояния T6 в состояние T1), ток не протекает в диоде 42; в силу этого потери на восстановление не формируются в диоде 42. В случае, если нижний MOSFET 31 включается, потенциал на аноде диода 44 понижается через первый вспомогательный дроссель 24 и второй вспомогательный дроссель 26. Тем не менее, темп уменьшения потенциала на аноде диода 44 является низким с влиянием индуктивных напряжений первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26. Соответственно, потери на восстановление практически не формируются даже в диоде 44. Аналогично, когда нижний MOSFET 33 включается (т.е. когда переход выполняется из состояния T3 в состояние T4), ток не протекает в диоде 44; в силу этого потери на восстановление не формируются в диоде 44. По этой причине, поскольку потенциал на аноде диода 42 медленно падает с влиянием индуктивных напряжений первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26, потери на восстановление практически не формируются даже в диоде 42.

Как описано выше, в первой операции, можно подавлять потери на восстановление (вид потерь на переключение), которые формируются в диодах 42, 44, по сравнению со второй операцией.

Как описано выше ссылаясь на фиг. 4, в первой операции, нижний MOSFET 31 переводится во включенное состояние только в состояниях T1, T2, и нижний MOSFET 33 переводится во включенное состояние только в состояниях T4, T5. Потери Eon1 при переходе в установившееся состояние, которые формируются, когда включается только нижний MOSFET 31 (или 33), удовлетворяют взаимосвязи Eon1≅RonIL2 в случае, если сопротивление во включенном состоянии нижнего MOSFET 31 (или 33) составляет Ron. Напротив, как описано выше ссылаясь на фиг. 5, во второй операции, поскольку оба из нижних MOSFET 31, 33 переводятся во включенное состояние в состоянии S1, ток IL разветвляется и протекает в нижний MOSFET 31 и нижний MOSFET 33. Соответственно, потери Eon2 при переходе в установившееся состояние, которые формируются в это время, удовлетворяют взаимосвязи Eon2≅Ron(IL/2)2+Ron(IL/2)2=RonIL2/2. Таким образом, взаимосвязь Eon2≅Eon1/2 удовлетворяется. Таким образом, во второй операции потери при переходе в установившееся состояние практически не формируются, по сравнению с первой операцией.

Фиг. 7 показывает взаимосвязь между потерями E и током IL. Потери E, показанные на фиг. 7, указывают суммарные потери, которые формируются в преобразователе 10 постоянного тока в постоянный. Потери E включают в себя потери при переходе в установившееся состояние и потери на переключение. График E1 по фиг. 7 показывает потери, которые формируются в первой операции, и график E2 по фиг. 7 показывает потери, которые формируются во второй операции. Как описано выше, первая операция имеет относительно высокий эффект подавления потерь на переключение. В области R1 тока, в которой ток IL является относительно небольшим, отношение потерь на переключение к суммарным потерям является относительно большим; в силу этого потери E1 в первой операции с относительно высоким эффектом подавления потерь на переключение становятся меньше потерь E2 во второй операции. В области R2 тока, в которой ток IL является относительно большим, отношение потерь при переходе в установившееся состояние к суммарным потерям является относительно большим; в силу этого потери E2 во второй операции с относительно высоким эффектом подавления потерь при переходе в установившееся состояние становятся меньше потерь E1 в первой операции. Как описано выше, контроллер 54 затвора выполняет первую операцию, когда ток IL равен или меньше порогового значения Ith, и выполняет вторую операцию, когда ток IL превышает пороговое значение Ith. Пороговое значение Ith задается таким образом, чтобы удовлетворять взаимосвязи 0,9*Ib<Ith<1,1*Ib относительно граничного значения Ib между областью R1 тока и областью R2 тока. Таким образом, пороговое значение Ith задается равным значению, которое практически совпадает с граничным значением Ib. Соответственно, преобразователь 10 постоянного тока в постоянный примера 1 может выполнять первую операцию в области R1 тока и может выполнять вторую операцию в области R2 тока. Соответственно, потери, которые формируются в преобразователе 10 постоянного тока в постоянный, эффективно подавляются. Ток IL представляет собой значение в области R1 тока во время нормального движения транспортного средства, и ток IL становится значением в области R2 тока в случае, если транспортное средство выполняет внезапное ускорение и т.п. Соответственно, преобразователь 10 постоянного тока в постоянный выполняет первую операцию во время нормального движения транспортного средства, и преобразователь 10 постоянного тока в постоянный выполняет вторую операцию в случае, если транспортное средство выполняет внезапное ускорение, и т.п.

Как описано выше, в случае, если ток IL становится большим, выполняется переключение из первой операции (т.е. операции, в которой нижний MOSFET 31 и нижний MOSFET 33 включаются попеременно) во вторую операцию (т.е. операцию, в которой нижний MOSFET 31 и нижний MOSFET 33 включаются и выключаются одновременно). Когда выполняется переключение из первой операции во вторую операцию, ток IL1 и ток IL (ток IL1 и ток IL2 в состоянии S1 по фиг. 5) являются несбалансированными. Тем не менее, поскольку первый вспомогательный дроссель 24 и второй вспомогательный дроссель 26 имеют относительно небольшую индуктивность, ток IL1 и ток IL2 балансируются в течение короткого времени в случае, если вторая операция начинается. Соответственно, можно выполнять вторую операцию без каких-либо проблем.

В примере 1, описанном выше, как показано на фиг. 5, во второй операции, нижние MOSFET 31, 33 и верхние MOSFET 32, 34 попеременно включаются. Тем не менее, как показано на фиг. 8, во второй операции, состояние S1 и состояние S2 могут задаваться с возможностью появляться попеременно, и верхние MOSFET 32, 34 могут поддерживаться в отключенном состоянии.

Как показано на фиг. 9, дополнительно могут предоставляться нижний MOSFET 35, диод 45, верхний MOSFET 36, диод 46 и третий вспомогательный дроссель 28. MOSFET 35, 36 имеют тип с каналом n-типа. Исток нижнего MOSFET 35 соединяется с межсоединением 16 с низким потенциалом. Исток верхнего MOSFET 36 соединяется со стоком нижнего MOSFET 35. Сток верхнего MOSFET 36 соединяется с выходным межсоединением 14 с высоким потенциалом. Первый конец третьего вспомогательного дросселя 28 соединяется со вторым контактным выводом 22b основного дросселя 22. Второй конец третьего вспомогательного дросселя 28 соединяется со стоком нижнего MOSFET 35 и истоком верхнего MOSFET 36. Анод диода 45 соединяется с истоком нижнего MOSFET 35. Катод диода 45 соединяется со стоком нижнего MOSFET 35. Анод диода 46 соединяется с истоком верхнего MOSFET 36. Катод диода 46 соединяется со стоком верхнего MOSFET 36. В этом случае, в первой операции, как показано на фиг. 10, управление может выполняться таким образом, что состояние преобразователя 10 постоянного тока в постоянный изменяется в порядке состояний T1-T9 и возвращается в состояние T1 сразу после состояния T9. Таким образом, цикл состояний T1-T9 может многократно выполняться. На фиг. 10, ток IL3 представляет собой ток, который протекает в третьем вспомогательном дросселе 28. Потенциал Vg35 представляет собой потенциал затвора нижнего MOSFET 35. Потенциал Vg36 представляет собой потенциал затвора верхнего MOSFET 36. В состояниях T1-T6 по фиг. 10, нижний MOSFET 35 выключается. В состояниях T7, T8, нижние MOSFET 31, 33 выключаются, и нижний MOSFET 35 включается. В состоянии T9, нижние MOSFET 31, 33, 35 выключаются. Верхний MOSFET 34 переводится во включенное состояние от времени t5 в середине периода состояния T6 до времени t6 в середине периода состояния T7. Согласно вышеизложенному, потери, которые формируются, когда протекает ток IL2, эффективнее уменьшаются. Верхний MOSFET 36 переводится во включенное состояние от времени t7 в середине периода состояния T9 до времени t8 в середине периода состояния T1. Согласно вышеизложенному, потери, которые формируются, когда протекает ток IL3, эффективнее уменьшаются. Как описано выше, даже если число последовательных схем верхнего MOSFET и нижнего MOSFET равно трем, можно выполнять первую операцию. Число последовательных схем верхнего MOSFET и нижнего MOSFET может увеличиваться в большей степени по сравнению с числом последовательных схем на фиг. 9.

В примере 1, описанном выше, датчик 52 тока определяет ток IL, который протекает в основном дросселе 22. Тем не менее, может предоставляться датчик тока, который измеряет ток, протекающий в другой позиции (например, по меньшей мере, в одном из входного межсоединения 12 с высоким потенциалом, первого вспомогательного дросселя 24, второго вспомогательного дросселя 26, MOSFET 31-34 и диодов 41-44), ток IL может прогнозироваться из значения определения датчика тока, и первая операция и вторая операция могут переключаться.

Первая операция и вторая операция примера 1 могут применяться к работе в рекуперативном режиме (операции заряда источника 90 мощности постоянного тока с использованием добавочной электрической мощности выходного межсоединения 14 с высоким потенциалом) преобразователя постоянного тока в постоянный. В этом случае, можно эффективно подавлять потери на переключение в верхних MOSFET 32, 34 с помощью первой операции.

В примере 1, описан преобразователь постоянного тока в постоянный. Напротив, в примере 2, описывается пример, в котором технология настоящего изобретения применяется к инвертору. Инвертор 100, показанный на фиг. 11, включает в себя межсоединение 102 с высоким потенциалом и межсоединение 104 с низким потенциалом. Межсоединение 102 с высоким потенциалом соединяется со стороной плюсовой клеммы (например, положительным электродом аккумулятора, выходным межсоединением с высоким потенциалом преобразователя постоянного тока в постоянный и т.п.) источника мощности постоянного тока. Межсоединение 104 с низким потенциалом соединяется со стороной минусовой клеммы (например, отрицательным электродом аккумулятора, межсоединением с низким потенциалом преобразователя постоянного тока в постоянный и т.п.) источника мощности постоянного тока. Три переключающих схемы 110a, 110b, 110c соединяются параллельно между межсоединением 102 с высоким потенциалом и межсоединением 104 с низким потенциалом. Межсоединения 120a, 120b, 120c электромотора соединяются с переключающими схемами 110a, 110b, 110c, соответственно. Другой конец межсоединений 120a, 120b, 120c электромотора соединяется с электромотором 130 (трехфазным электромотором) для движения. Электромотор 130 для движения имеет три катушки 222a, 222b, 222c. Межсоединение 120a электромотора соединяется с катушкой 222a. Межсоединение 120b электромотора соединяется с катушкой 222b. Межсоединение 120c электромотора соединяется с катушкой 222c. Инвертор 100 преобразует электрическую мощность постоянного тока, прикладываемую между межсоединением 102 с высоким потенциалом и межсоединением 104 с низким потенциалом, в трехфазную электрическую мощность переменного тока и подает трехфазную электрическую мощность переменного тока в электромотор 130 для движения.

Ниже описываются переключающие схемы 110a, 110b, 110c. Поскольку переключающие схемы 110a, 110b, 110c имеют идентичную конфигурацию, в дальнейшем в этом документе, описывается переключающая схема 110c.

Фиг. 12 показывает переключающую схему 110c. В дальнейшем в этом документе, составляющие элементы преобразователя постоянного тока в постоянный примера 1 из числа составляющих элементов переключающей схемы 110c представляются посредством ссылок с номерами, идентичных ссылкам с номерами в примере 1. Переключающая схема 110c имеет MOSFET 31-34. Между межсоединением 102 с высоким потенциалом и межсоединением 104 с низким потенциалом, верхний MOSFET 32 и нижний MOSFET 31 последовательно соединяются, и верхний MOSFET 34 и нижний MOSFET 33 последовательно соединяются. Диоды 41-44 соединяются параллельно с MOSFET 31-34, соответственно. В диодах 41-44, анод соединяется с истоком соответствующего MOSFET, и катод соединяется со стоком соответствующего MOSFET. Переключающая схема 110c имеет первый вспомогательный дроссель 24 и второй вспомогательный дроссель 26. Первый конец первого вспомогательного дросселя 24 соединяется со стоком нижнего MOSFET 31. Второй конец первого вспомогательного дросселя 24 соединяется с межсоединением 120c электромотора. Первый конец второго вспомогательного дросселя 26 соединяется со стоком нижнего MOSFET 33. Второй конец второго вспомогательного дросселя 26 соединяется с межсоединением 120c электромотора. Межсоединение 120c электромотора содержит датчик 52 тока. Переключающая схема 110c имеет контроллер 54 затвора, который соединяется с затворами MOSFET 31-34.

Переключающие схемы 110a-110c переключают MOSFET в переключающих схемах 110a-110c, за счет чего электрическая мощность переменного тока подается в электромотор 130 для движения. Токи IMa, IMb, IMc по фиг. 12 указывают токи, которые протекают в электромоторе 130 для движения. Фиг. 12 показывает случай, когда ток IMa вытекает из межсоединения 120a электромотора в катушку 222a, ток IMb вытекает из межсоединения 120b электромотора в катушку 222b, и ток IMc вытекает из катушки 222c в межсоединение 120c электромотора. Ток IMc представляет собой ток, полученный посредством суммирования тока IMa и тока IMb. Как описано выше, в состоянии, в котором протекают токи IMa, IMb, IMc, контроллер 54 затвора переключает MOSFET 31-34, за счет этого управляя током IMc. Контроллер 54 затвора выполняет первую операцию, когда ток IMc, определенный посредством датчика 52 тока, равен или меньше порогового значения Ith, и выполняет вторую операцию, когда ток IMc превышает пороговое значение Ith.

Первая операция переключающей схемы 110c является практически идентичной первой операции по фиг. 3. В отношении переключающей схемы 110c, фиг. 3 показывает ток IMc вместо тока IL. Состояние T1-T6 переключающей схемы 110c показано на фиг. 13. Ток IMc равен значению, полученному посредством суммирования тока IL1 и тока IL2. На фиг. 13, схемная конфигурация переключающей схемы 110c упрощается по сравнению со схемной конфигурацией, показанной на фиг. 12.

Первая операция переключающей схемы 110c, показанная на фиг. 13, является практически идентичной первой операции преобразователя 10 постоянного тока в постоянный, показанной на фиг. 4. В состоянии T1, ток IL1 протекает через нижний MOSFET 31 во включенном состоянии. В состоянии T1, ток IL2 протекает в диоде 44. Тем не менее, ток IL2 снижается до нуля в период состояния T1. В состоянии T2, поскольку нижний MOSFET 31 после этого включается, ток IL1 непрерывно протекает в нижнем MOSFET 31. В состоянии T3, нижний MOSFET 31 выключается, и ток IL1 протекает в диоде 42. Во время t1 в середине периода состояния T3, верхний MOSFET 32 включается. В состоянии T4, нижний MOSFET 33 включается, и ток IL2 протекает в нижнем MOSFET 33. Верхний MOSFET 32 непрерывно включен до времени t2 в середине периода состояния T4. Напряжение между межсоединением 102 с высоким потенциалом и межсоединением 104 с низким потенциалом сохраняется с помощью первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26. Соответственно, межсоединение 102 с высоким потенциалом и межсоединение 104 с низким потенциалом не переводятся в состояние короткого замыкания. Верхний MOSFET 32 включается от времени t1 до времени t2, за счет чего ток IL1 рассеивается и протекает в диод 42 и верхний MOSFET 32 от периода состояния T3 до периода состояния T4. Согласно вышеизложенному, потери при переходе в установившееся состояние эффективно подавляются. Ток IL1 снижается до нуля в период состояния T4. В состоянии T5, поскольку нижний MOSFET 33 после этого включается, ток IL2 непрерывно протекает в нижнем MOSFET 33. В состоянии T6, нижний MOSFET 33 выключается, и ток IL2 протекает в диоде 44. Во время t3 в середине периода состояния T6, верхний MOSFET 34 включается. В последующем состоянии T1, нижний MOSFET 31 включается, и ток IL1 протекает в нижнем MOSFET 31. Верхний MOSFET 34 непрерывно включен до времени t4 в середине периода состояния T1. Напряжение между межсоединением 102 с высоким потенциалом и межсоединением 104 с низким потенциалом сохраняется с помощью первого вспомогательного дросселя 24 и второго вспомогательного дросселя 26. Соответственно, межсоединение 102 с высоким потенциалом и межсоединение 104 с низким потенциалом не переводятся в состояние короткого замыкания. Верхний MOSFET 34 включается от времени t3 до времени t4, ток IL2 рассеивается и протекает в диод 44 и верхний MOSFET 34 от периода состояния T6 до периода состояния T1. Согласно вышеизложенному, потери при переходе в установившееся состояние эффективно подавляются.

В случае, если токи IL1, IL2 протекают в нижних MOSFET 31, 33, ток IMc, который протекает в электромоторе 130 для движения, увеличивается. В случае, если токи IL1, IL2 протекают в диодах 42, 44, токи IL1, IL2 обратно протекают, и ток IMc снижается. Соответственно, соотношения рабочей нагрузки нижних MOSFET 31, 33 управляются с помощью первой операции, за счет чего можно управлять током IMc, который протекает в электромоторе 130 для движения.

Как должно быть очевидным из фиг. 3 и 13, в первой операции переключающей схемы 110c, ток IL1, который протекает в первом вспомогательном дросселе 24, равен нулю непосредственно перед временем, когда нижний MOSFET 31 включается (т.е. в состоянии T6). Соответственно, потери на переключение, которые формируются, когда нижний MOSFET 31 включается, являются относительно небольшими. В первой операции переключающей схемы 110c, непосредственно перед временем, когда нижний MOSFET 33 включается (т.е. в состоянии T3), ток IL2, который протекает во втором вспомогательном дросселе 26, равен нулю. Соответственно, потери на переключение, которые формируются, когда нижний MOSFET 33 включается, являются относительно небольшими.

Вторая операция переключающей схемы 110c, показанная на фиг. 14, является практически идентичной первой операции преобразователя 10 постоянного тока в постоянный, показанной на фиг. 5. Как показано на фиг. 14, управление выполняется таким образом, что переключающая схема 110c повторяет цикл состояний S1-S4. На фиг. 14, схемная конфигурация переключающей схемы 110c упрощается по сравнению со схемной конфигурацией, показанной на фиг. 12.

В состоянии S1, токи IL1, IL2 протекают через нижние MOSFET 31, 33 во включенном состоянии. В состояниях S2-S4, токи IL1, IL2 протекают через диоды 42, 44. В случае, если токи IL1, IL2 протекают в нижних MOSFET 31, 33, ток IMc, который протекает в электромоторе 130 для движения, увеличивается. В случае, если токи IL1, IL2 протекают в диодах 42, 44, токи IL1, IL2 обратно протекают, и ток IMc снижается. Соответственно, соотношения рабочей нагрузки нижних MOSFET 31, 33 управляются с помощью второй операции, за счет чего можно управлять током IMc, который протекает в электромоторе 130 для движения.

Как должно быть очевидным из фиг. 14, во второй операции переключающей схемы 110c, ток рассеивается и протекает в нижние MOSFET 31, 32. Соответственно, можно уменьшать потери при переходе в установившееся состояние во второй операции по сравнению с первой операцией.

В переключающей схеме 110c примера 2, поскольку первая операция выполняется во время небольшого тока с относительно высоким отношением потерь на переключение, и вторая операция выполняется во время большого тока с относительно высоким отношением потерь при переходе в установившееся состояние, можно эффективно подавлять потери, которые формируются в переключающей схеме 110c.

В переключающей схеме 110c примера 2, аналогично фиг. 9 и 10, может увеличиваться число MOSFET, диодов и вспомогательных дросселей. В переключающей схеме 110c, аналогично фиг. 8, может выполняться вторая операция.

Первая операция и вторая операция примера 2 могут применяться к операции, когда ток IMc вытекает из переключающей схемы 110c к катушке 222c электромотора 130 для движения. В этом случае, можно эффективнее уменьшать потери на переключение в верхних MOSFET 32, 34 с помощью первой операции.

Ниже описывается взаимосвязь между составляющими элементами примеров и составляющими элементами настоящего изобретения. Источник 90 мощности постоянного тока примера 1 представляет собой пример источника подачи электрической мощности в формуле изобретения. Схема (т.е. переключающие схемы 110a, 110b, которые соединяются с межсоединениями 120a, 120b электромотора), которая подает токи IMa и IMb в электромотор 130 для движения примера 2, представляет собой пример источника подачи электрической мощности настоящего изобретения. Входное межсоединение 12 с высоким потенциалом примера 1 и межсоединение 120a, 120b электромотора примера 2 представляют собой пример первого межсоединения с высоким потенциалом настоящего изобретения. Выходное межсоединение 14 с высоким потенциалом примера 1 и межсоединение 102 с высоким потенциалом примера 2 представляют собой пример второго межсоединения с высоким потенциалом настоящего изобретения. Нижний MOSFET 31 примеров представляет собой пример первого нижнего FET настоящего изобретения. Верхний MOSFET 32 примеров представляет собой пример первого верхнего FET настоящего изобретения. Нижний MOSFET 33 примеров представляет собой пример второго нижнего FET настоящего изобретения. Верхний MOSFET 34 примеров представляет собой пример второго верхнего FET настоящего изобретения. Нижний MOSFET 35 примеров представляет собой пример третьего нижнего FET настоящего изобретения. Верхний MOSFET 36 примеров представляет собой пример третьего верхнего FET настоящего изобретения. Диод 42 примеров представляет собой пример первого диода настоящего изобретения. Диод 44 примеров второго диода настоящего изобретения. Диод 46 примеров представляет собой пример третьего диода настоящего изобретения. Состояния T1, T2 примеров представляют собой пример первого состояния настоящего изобретения. Состояние T3 примеров представляет собой пример второго состояния настоящего изобретения. Состояния T4, T5 примеров представляют собой пример третьего состояния настоящего изобретения. Состояние T6 примеров представляет собой пример четвертого состояния настоящего изобретения. Состояния T7, T8 примеров представляют собой пример пятого состояния настоящего изобретения. Состояние T9 примеров представляет собой пример шестого состояния настоящего изобретения. Время t1 примеров представляет собой пример первого времени настоящего изобретения. Время t2 примеров представляет собой пример второго времени настоящего изобретения. Время t3 примеров представляет собой пример третьего времени настоящего изобретения. Время t4 примеров представляет собой пример четвертого времени настоящего изобретения. Время t5 примеров представляет собой пример пятого времени настоящего изобретения. Время t6 примеров представляет собой пример шестого времени настоящего изобретения. Время t7 примеров представляет собой пример седьмого времени настоящего изобретения. Время t8 примеров представляет собой пример восьмого времени настоящего изобретения.

Технические элементы, раскрытые в описании изобретения, перечисляются ниже. Следующие технические элементы являются полезными независимо друг от друга.

В схеме преобразования электрической мощности примера, раскрытого в этом подробном описании, контроллер затвора может быть выполнен с возможностью, в первой операции, осуществлять управление таким образом, что первый нижний FET, первый верхний FET, второй нижний FET и второй верхний FET удовлетворяют следующим условиям. (Условие 3) Первое состояние задается сразу после четвертого состояния. (Условие 4) Второй верхний FET включается в третье время в середине периода четвертого состояния, второй верхний FET поддерживается во включенном состоянии до четвертого времени в середине периода первого состояния, и второй верхний FET выключается в четвертое время.

При вышеуказанной конфигурации, можно заставлять ток, протекающий во втором диоде, рассеиваться во второй верхний FET от периода четвертого состояния до периода первого состояния. Можно эффективнее уменьшать потери, которые формируются в схеме преобразования электрической мощности.

В схеме преобразования электрической мощности примера, раскрытого в этом подробном описании, контроллер затвора может быть выполнен с возможностью осуществлять вторую операцию. Контроллер затвора может быть выполнен с возможностью, во второй операции, осуществлять управление таким образом, что первый нижний FET, первый верхний FET, второй нижний FET и второй верхний FET удовлетворяют такому условию, что состояние, в котором оба из первого нижнего FET и второго нижнего FET включаются, и состояние, в котором оба из первого нижнего FET и второго нижнего FET выключаются, появляются попеременно. Контроллер затвора может быть выполнен с возможностью осуществлять первую операцию, когда ток, протекающий в основном дросселе, равен или меньше порогового значения Ith, и осуществлять вторую операцию, когда ток, протекающий в основном дросселе, превышает пороговое значение Ith. Пороговое значение Ith может задаваться таким образом, чтобы удовлетворять взаимосвязи 0,9*Ib<Ith<1,1*Ib относительно граничного значения Ib между областью тока, в которой потери, сформированные в первой операции, равны или меньше потерь, сформированных во второй операции, и областью тока, в которой потери, сформированные в первой операции, превышают потери, сформированные во второй операции.

В вышеуказанной конфигурации, можно выполнять первую операцию в области небольшого тока, в которой можно эффективнее уменьшать потери с первой операцией, и выполнять вторую операцию в области большого тока, в которой можно эффективнее уменьшать потери со второй операцией. Согласно вышеизложенному, можно эффективнее уменьшать потери, которые формируются в схеме преобразования электрической мощности.