Изобретение относится к области радиотехники, а также измерительной техники, и может использоваться, например, в качестве перестраиваемых ограничителей спектра, включаемых на входе аналого-цифровых преобразователей различного назначения.Универсальные программируемые активные RC-фильтры (ARCФ), обеспечивающие на разных выходах формирование амплитудно-частотных характеристик фильтра нижних частот (ФНЧ), фильтра высоких частот (ФВЧ), полосового фильтра (ПФ), широко используются в современной электронике [1-15] и оказывают существенное влияние на качественные показатели многих аналого-цифровых систем связи и автоматического управления. При этом в качестве элементов программирования и перестройки ARCФ применяются матрицы R-2R [1], управляемые кодом. Достаточно важным направлением совершенствования программируемых ARCФ является подстройка и перестройка их основных параметров, в т.ч. за счет цифровой коммутации пассивных элементов и применения микросхем цифровых потенциометров [9-15].

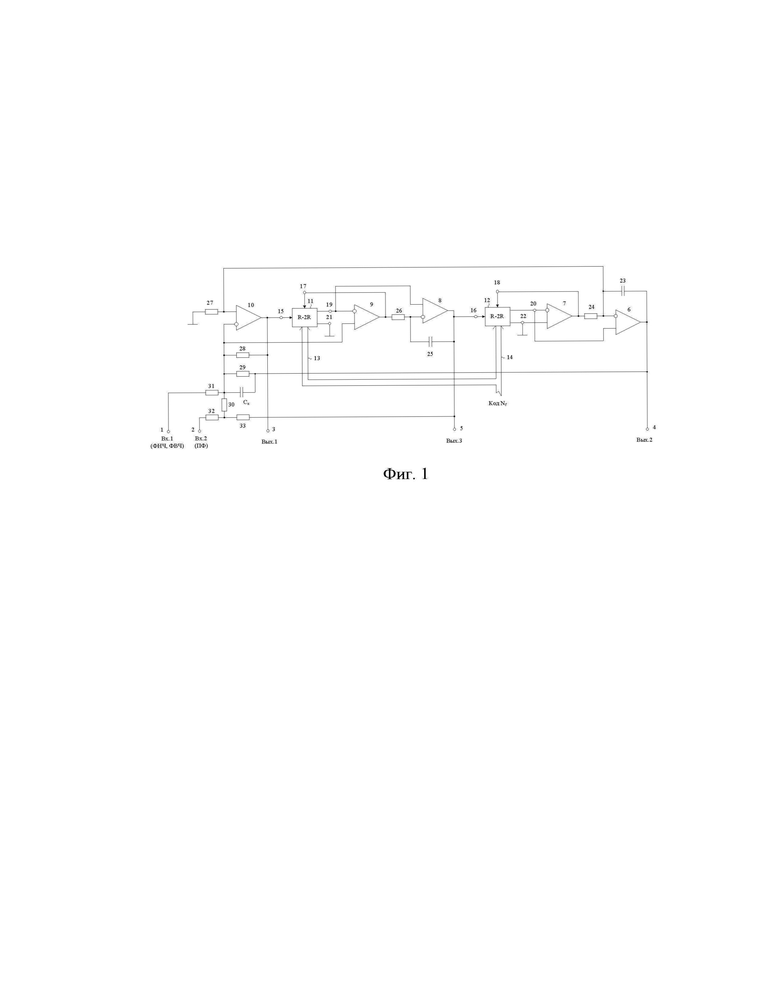

Ближайшим прототипом заявляемого устройства является схема универсального программируемого ARC-фильтра, представленная в патенте RU 2019904, 1994 г. Он содержит (фиг. 1) первый 1 и второй 2 входы, а также первый 3, второй 4 и третий 5 выходы, первый 6, второй 7, третий 8, четвертый 9 и пятый 10 дифференциальные операционные усилители, первую 11 и вторую 12 матрицы сопротивлений R-2R, каждая из которых имеет цифровое управление по многоканальным логическим входам 13 и 14 соответственно, аналоговые входы 15 и 16 первой 11 и второй 12 матриц сопротивлений R-2R, входы 17 и 18 для подключения обратных связей первой 11 и второй 12 матриц сопротивлений R-2R, аналоговые выходы 19 и 20 первой 11 и второй 12 матриц сопротивлений R-2R соответственно, а также вспомогательные аналоговые выходы 21 и 22 первой 11 и второй 12 матриц сопротивлений R-2R, согласованные с общей шиной источников питания, первый 23 конденсатор, включенный между выходом первого 6 дифференциального операционного усилителя и его инвертирующим входом, первый 24 резистор, включенный между выходом второго 7 дифференциального операционного усилителя, соединенным со входом 18 для подключения обратной связи второй 12 матрицы сопротивлений R-2R и инвертирующим входом первого 6 дифференциального операционного усилителя, аналоговый выход 20 второй 12 матрицы сопротивлений R-2R соединен с инвертирующим входом второго 7 дифференциального операционного усилителя и неинвертирующим входом первого 6 дифференциального операционного усилителя, неинвертирующий вход второго 7 дифференциального операционного усилителя подключен к общей шине источников питания, аналоговый выход 19 первой 11 матрицы сопротивления R-2R связан с инвертирующим входом четвертого 9 дифференциального операционного усилителя, выход которого связан со входом 17 для подключения обратной связи первой 11 матрицы сопротивления R-2R, выход пятого 10 дифференциального операционного усилителя связан с первым 3 выходом устройства, выход первого 6 дифференциального операционного усилителя связан со вторым 4 выходом устройства, второй 25 конденсатор, второй 26, третий 27, четвертый 28, пятый 29, шестой 30, седьмой 31, восьмой 32, девятый 33 резисторы.

Основной существенный недостаток ARCФ-прототипа фиг. 1 состоит в том, что он не позволяет реализовать высокую стабильность добротности фильтра на высоких частотах, так как здесь компенсация влияния частотных свойств операционных усилителей выполняется с помощью используемого в схеме фиг. 1 третьего конденсатора (элемент Ск).

Основная задача предполагаемого изобретения состоит в повышении стабильности реализуемой добротности.

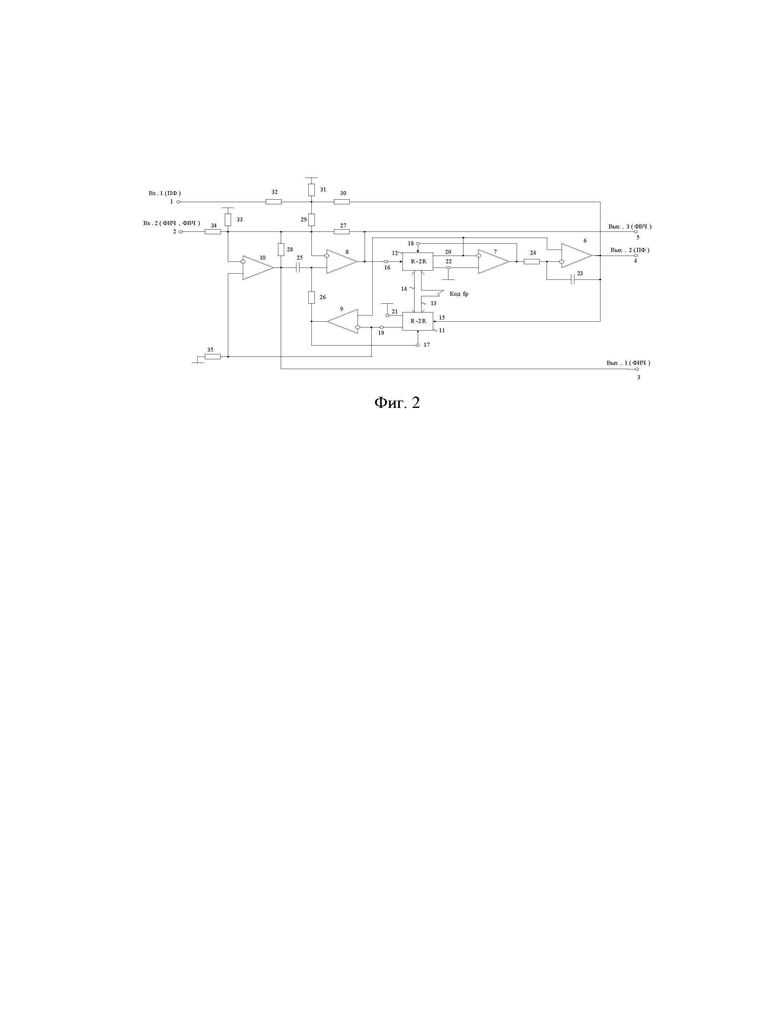

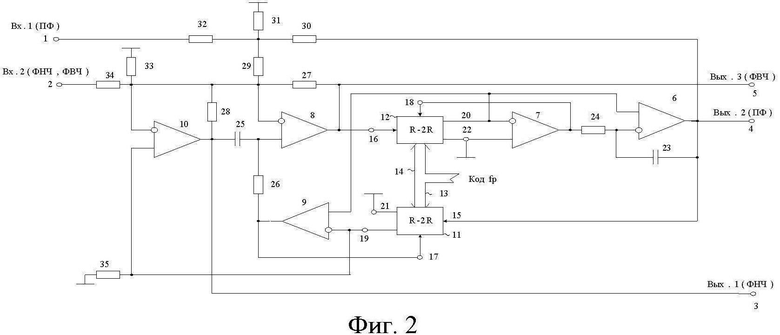

Поставленная задача достигается тем, что в универсальном программируемом ARC-фильтре фиг. 1, содержащем первый 1 и второй 2 входы, а также первый 3, второй 4 и третий 5 выходы, первый 6, второй 7, третий 8, четвертый 9 и пятый 10 дифференциальные операционные усилители, первую 11 и вторую 12 матрицы сопротивлений R-2R, каждая из которых имеет цифровое управление по многоканальным логическим входам 13 и 14 соответственно, аналоговые входы 15 и 16 первой 11 и второй 12 матриц сопротивлений R-2R, входы 17 и 18 для подключения обратных связей первой 11 и второй 12 матриц сопротивлений R-2R, аналоговые выходы 19 и 20 первой 11 и второй 12 матриц сопротивлений R-2R соответственно, а также вспомогательные аналоговые выходы 21 и 22 первой 11 и второй 12 матриц сопротивлений R-2R, согласованные с общей шиной источников питания, первый 23 конденсатор, включенный между выходом первого 6 дифференциального операционного усилителя и его инвертирующим входом, первый 24 резистор, включенный между выходом второго 7 дифференциального операционного усилителя, соединенным со входом 18 для подключения обратной связи второй 12 матрицы сопротивлений R-2R и инвертирующим входом первого 6 дифференциального операционного усилителя, аналоговый выход 20 второй 12 матрицы сопротивлений R-2R соединен с инвертирующим входом второго 7 дифференциального операционного усилителя и неинвертирующим входом первого 6 дифференциального операционного усилителя, неинвертирующий вход второго 7 дифференциального операционного усилителя подключен к общей шине источников питания, аналоговый выход 19 первой 11 матрицы сопротивления R-2R связан с инвертирующим входом четвертого 9 дифференциального операционного усилителя, выход которого связан со входом 17 для подключения обратной связи первой 11 матрицы сопротивления R-2R, выход пятого 10 дифференциального операционного усилителя связан с первым 3 выходом устройства, выход первого 6 дифференциального операционного усилителя связан со вторым 4 выходом устройства, второй 25 конденсатор, второй 26, третий 27, четвертый 28, пятый 29, шестой 30, седьмой 31, восьмой 32, девятый 33 резисторы, предусмотрены новые элементы и связи – второй 4 выход устройства подключен к аналоговому входу 15 первой 11 матрицы сопротивления R-2R, третий 5 выход устройства соединен с выходом третьего 8 дифференциального операционного усилителя, неинвертирующий вход четвертого 9 дифференциального операционного усилителя соединен с инвертирующим входом второго 7 дифференциального операционного усилителя и неинвертирующим входом первого 6 дифференциального операционного усилителя, между выходом пятого 10 дифференциального операционного усилителя и неинвертирующим входом третьего 8 дифференциального операционного усилителя включен второй 25 конденсатор, выход четвертого 9 дифференциального операционного усилителя связан с неинвертирующим входом третьего 8 дифференциального операционного усилителя через второй 26 резистор, инвертирующий вход пятого 10 дифференциального операционного усилителя соединен со вторым 2 входом устройства через первый дополнительный резистор 34 и соединен с общей шиной источников питания через девятый 33 резистор, а также связан с выходом пятого 10 дифференциального операционного усилителя через четвертый 28 резистор, инвертирующий вход третьего 8 дифференциального операционного усилителя соединен с инвертирующим входом пятого 10 дифференциального операционного усилителя и через третий 27 резистор подключен к третьему 5 выходу устройства и выходу третьего 8 дифференциального операционного усилителя, первый 1 вход устройства соединен со вторым 4 выходом устройства через последовательно соединенные восьмой 32 и шестой 30 резисторы, общий узел которых связан с инвертирующим входом третьего 8 дифференциального операционного усилителя через пятый 29 резистор и подключен к общей шине источников питания через седьмой 31 резистор, причем инвертирующий вход четвертого 9 дифференциального операционного усилителя соединен с неинвертирующим входом пятого 10 дифференциального операционного усилителя и связан с общей шиной источников питания через второй 35 дополнительный резистор.

На чертеже фиг. 1 приведена схема ARCФ-прототипа по патенту RU 2019904, 1994 г., а на чертеже фиг. 2 - заявляемая схема в соответствии с формулой изобретения.

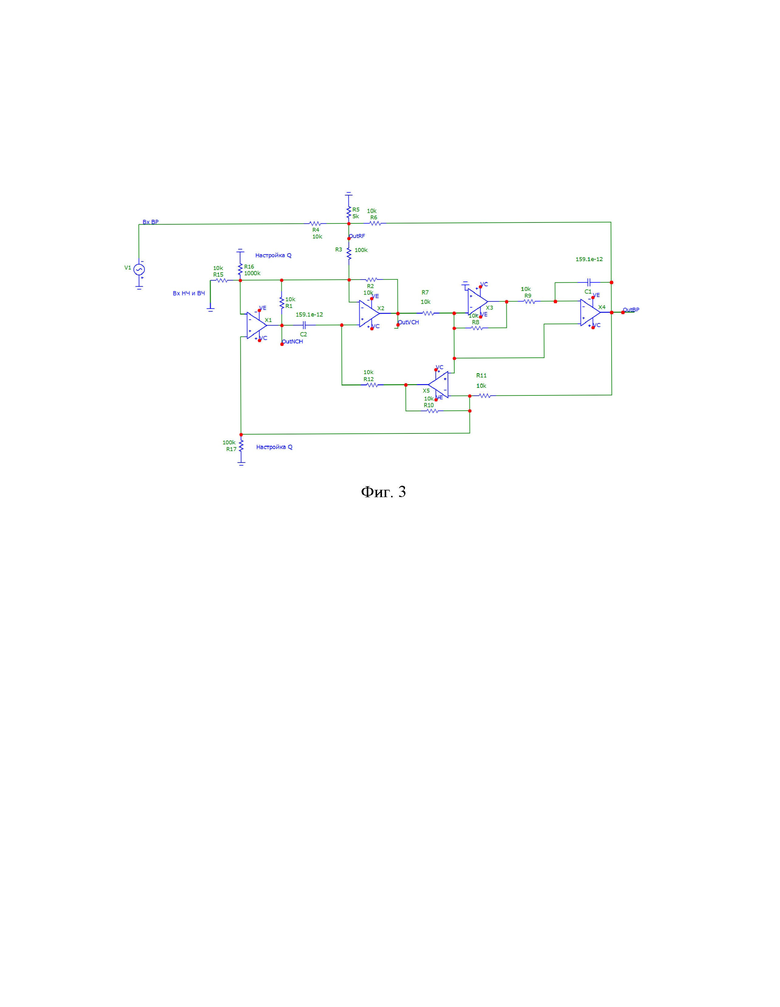

На чертеже фиг. 3 представлена схема заявляемого ARCФ фиг. 2 в среде Micro-Cap на моделях операционных усилителей OP27 (Analog Devices).

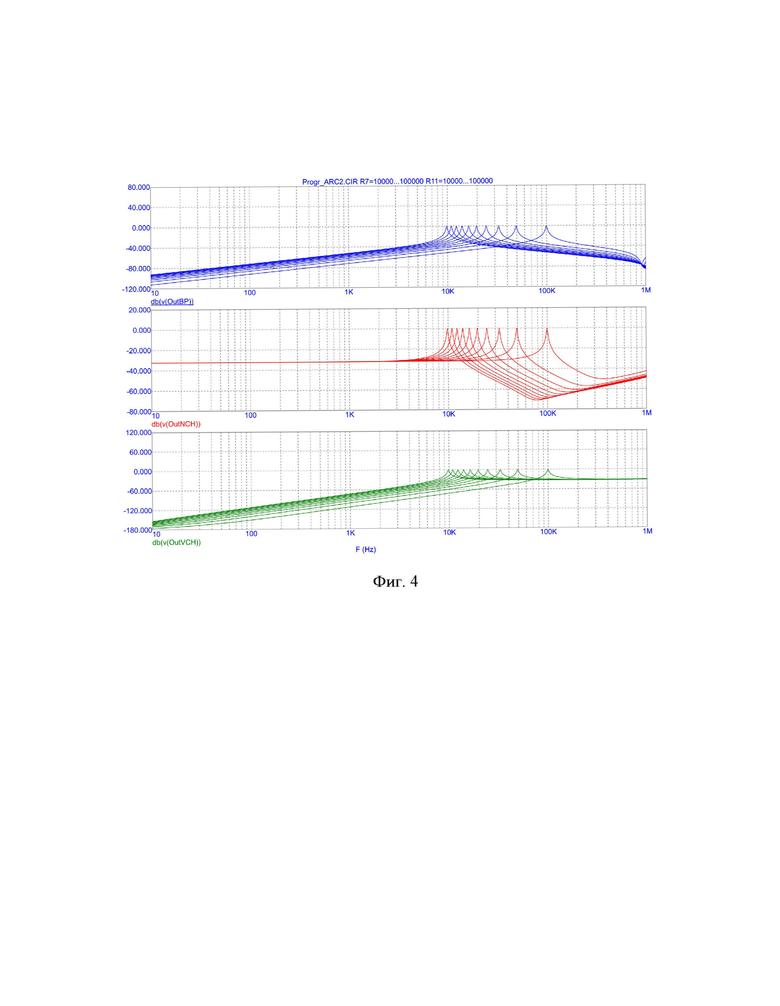

На чертеже фиг. 4 показаны амплитудно-частотные характеристики заявляемого ARCФ фиг. 3 при перестройке основных параметров.

Универсальный программируемый ARC-фильтр на основе матриц R-2R, содержащий первый 1 и второй 2 входы, а также первый 3, второй 4 и третий 5 выходы, первый 6, второй 7, третий 8, четвертый 9 и пятый 10 дифференциальные операционные усилители, первую 11 и вторую 12 матрицы сопротивлений R-2R, каждая из которых имеет цифровое управление по многоканальным логическим входам 13 и 14 соответственно, аналоговые входы 15 и 16 первой 11 и второй 12 матриц сопротивлений R-2R, входы 17 и 18 для подключения обратных связей первой 11 и второй 12 матриц сопротивлений R-2R, аналоговые выходы 19 и 20 первой 11 и второй 12 матриц сопротивлений R-2R соответственно, а также вспомогательные аналоговые выходы 21 и 22 первой 11 и второй 12 матриц сопротивлений R-2R, согласованные с общей шиной источников питания, первый 23 конденсатор, включенный между выходом первого 6 дифференциального операционного усилителя и его инвертирующим входом, первый 24 резистор, включенный между выходом второго 7 дифференциального операционного усилителя, соединенным со входом 18 для подключения обратной связи второй 12 матрицы сопротивлений R-2R и инвертирующим входом первого 6 дифференциального операционного усилителя, аналоговый выход 20 второй 12 матрицы сопротивлений R-2R соединен с инвертирующим входом второго 7 дифференциального операционного усилителя и неинвертирующим входом первого 6 дифференциального операционного усилителя, неинвертирующий вход второго 7 дифференциального операционного усилителя подключен к общей шине источников питания, аналоговый выход 19 первой 11 матрицы сопротивления R-2R связан с инвертирующим входом четвертого 9 дифференциального операционного усилителя, выход которого связан со входом 17 для подключения обратной связи первой 11 матрицы сопротивления R-2R, выход пятого 10 дифференциального операционного усилителя связан с первым 3 выходом устройства, выход первого 6 дифференциального операционного усилителя связан со вторым 4 выходом устройства, второй 25 конденсатор, второй 26, третий 27, четвертый 28, пятый 29, шестой 30, седьмой 31, восьмой 32, девятый 33 резисторы. Второй 4 выход устройства подключен к аналоговому входу 15 первой 11 матрицы сопротивления R-2R, третий 5 выход устройства соединен с выходом третьего 8 дифференциального операционного усилителя, неинвертирующий вход четвертого 9 дифференциального операционного усилителя соединен с инвертирующим входом второго 7 дифференциального операционного усилителя и неинвертирующим входом первого 6 дифференциального операционного усилителя, между выходом пятого 10 дифференциального операционного усилителя и неинвертирующим входом третьего 8 дифференциального операционного усилителя включен второй 25 конденсатор, выход четвертого 9 дифференциального операционного усилителя связан с неинвертирующим входом третьего 8 дифференциального операционного усилителя через второй 26 резистор, инвертирующий вход пятого 10 дифференциального операционного усилителя соединен со вторым 2 входом устройства через первый дополнительный резистор 34 и соединен с общей шиной источников питания через девятый 33 резистор, а также связан с выходом пятого 10 дифференциального операционного усилителя через четвертый 28 резистор, инвертирующий вход третьего 8 дифференциального операционного усилителя соединен с инвертирующим входом пятого 10 дифференциального операционного усилителя и через третий 27 резистор подключен к третьему 5 выходу устройства и выходу третьего 8 дифференциального операционного усилителя, первый 1 вход устройства соединен со вторым 4 выходом устройства через последовательно соединенные восьмой 32 и шестой 30 резисторы, общий узел которых связан с инвертирующим входом третьего 8 дифференциального операционного усилителя через пятый 29 резистор и подключен к общей шине источников питания через седьмой 31 резистор, причем инвертирующий вход четвертого 9 дифференциального операционного усилителя соединен с неинвертирующим входом пятого 10 дифференциального операционного усилителя и связан с общей шиной источников питания через второй 35 дополнительный резистор.

В качестве первой 11 и второй 12 матриц сопротивлений R-2R в схеме фиг. 2 могут применяться как российские (572ПА1), так и зарубежные (AD7520) перемножающие ЦАП с традиционным обозначением их выводов, которые приняты при описании формулы изобретения.

Результаты компьютерного моделирования ARCФ фиг. 2, представленные на чертеже фиг. 4 при параметрах элементов схемы, заданных на фиг. 3, показывают, что заявляемое устройство обеспечивает более чем десятикратную перестройку частоты квазирезонанса ПФ, частоты полюса ФНЧ и частоты полюса ФВЧ. При этом схема фиг. 2 имеет следующие достоинства в сравнении с прототипом: за счет введения новых связей достигается компенсация влияния частотных свойств операционных усилителей без применения дополнительного третьего конденсатора (элемента 35 на чертеже фиг. 1). При этом одновременно повышается и стабильность реализуемой фильтром добротности, так как устраняется влияние разности температурных коэффициентов используемых конденсаторов и площадей усиления операционных усилителей.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6407627, 2002 г.

2. Патент US 6710644, 2004 г.

3. Патент US 3787776, 1974 г.

4. Патент SU 1777233, 1992 г.

5. Патент RU 2019023,

6. Патент SU 1758833, 1992 г.

7. Патент SU 443459, 1994 г.

8. Патент SU 1417178, 1978 г.

9. Патент US 7.737.772, 2010 г.

10. Патент SU 587602, 1978 г.

11. Патент SU 536590, 1976 г.

12. Патент SU 1363443, 1987 г.

13. C.-M. Chang, "Analytical synthesis of the digitally programmable voltage-mode OTA-C universal biquad," IEEE Transactions on Circuits and Systems-II, vol. 53, pp. 607-611, 2006. DOI: 10.1109/TCSII.2006.876411

14. M. Kumngern, B. Knobnob, K. Dejhan, "Electronically tunable high-input impedance voltage-mode universal biquadratic filter based on simple CMOS OTAs," International Journal of Electronics and Communications, vol. 64, pp. 934-939, 2010.

15. M. Kumngern, U. Torteanchai and K. Dejhan, "Electronically tunable multiple-input single-output voltage-mode multifunction filter employing simple CMOS OTAs," in Proceeding of 2010 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS 2010), Kuala Lumpur, Malaysia, December 6-9, 2010, pp. 1099-1102. DOI: 10.1109/APCCAS.2010.5774819

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНЫЙ ПРОГРАММИРУЕМЫЙ ARC-ФИЛЬТР | 2019 |

|

RU2718212C1 |

| ФИЛЬТР ВЫСОКИХ ЧАСТОТ СЕМЕЙСТВА САЛЛЕНА - КИ С НЕЗАВИСИМОЙ ПОДСТРОЙКОЙ ОСНОВНЫХ ПАРАМЕТРОВ | 2021 |

|

RU2772314C1 |

| ПОЛОСОВОЙ ФИЛЬТР СЕМЕЙСТВА САЛЛЕНА-КИ | 2021 |

|

RU2774806C1 |

| ПОЛОСОВОЙ ФИЛЬТР КЛАССА САЛЛЕНА-КИ С НЕЗАВИСИМОЙ ПОДСТРОЙКОЙ ОСНОВНЫХ ПАРАМЕТРОВ | 2021 |

|

RU2771979C1 |

| ПОЛОСОВОЙ ФИЛЬТР СЕМЕЙСТВА САЛЛЕНА - КИ С НЕЗАВИСИМОЙ ПОДСТРОЙКОЙ ОСНОВНЫХ ПАРАМЕТРОВ | 2021 |

|

RU2772316C1 |

| ФИЛЬТР НИЗКИХ ЧАСТОТ СЕМЕЙСТВА САЛЛЕНА-КИ С НЕЗАВИСИМОЙ ПОДСТРОЙКОЙ ОСНОВНЫХ ПАРАМЕТРОВ | 2021 |

|

RU2771980C1 |

| Цифроаналоговый преобразователь код-ток | 1988 |

|

SU1644383A1 |

| ШИРОКОПОЛОСНЫЙ ПОЛОСОВОЙ ФИЛЬТР ЧЕТВЕРТОГО ПОРЯДКА С ОДНИМ ВХОДОМ И ПАРАФАЗНЫМ ВЫХОДОМ | 2020 |

|

RU2748610C1 |

| НИЗКОЧУВСТВИТЕЛЬНЫЙ АКТИВНЫЙ RC-ФИЛЬТР ВТОРОГО ПОРЯДКА НА ОСНОВЕ ДВУХ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫХ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ | 2019 |

|

RU2710292C1 |

| УНИВЕРСАЛЬНЫЙ АКТИВНЫЙ RC-ФИЛЬТР ВТОРОГО ПОРЯДКА НА ОСНОВЕ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫХ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ | 2019 |

|

RU2707706C1 |

Изобретение относится к средствам измерительной техники и может использоваться в качестве перестраиваемых ограничителей спектра, включаемых на входе аналого-цифровых преобразователей различного назначения. Технический результат заключается в повышении стабильности реализуемой добротности. Универсальный программируемый ARC-фильтр на основе матриц R-2R содержит также дифференциальные операционные усилители, резисторы и конденсаторы, соединенные между собой таким образом, чтобы обеспечить перестройку частоты квазирезонанса фильтров, частоты полюса ФНЧ и частоты полюса ФВЧ, компенсация влияния частотных свойств операционных усилителей повышает стабильность и добротность активного программируемого фильтра. 4 ил.

Универсальный программируемый ARC-фильтр на основе матриц R-2R, содержащий первый (1) и второй (2) входы, а также первый (3), второй (4) и третий (5) выходы, первый (6), второй (7), третий (8), четвертый (9) и пятый (10) дифференциальные операционные усилители, первую (11) и вторую (12) матрицы сопротивлений R-2R, каждая из которых имеет цифровое управление по многоканальным логическим входам (13) и (14) соответственно, аналоговые входы (15) и (16) первой (11) и второй (12) матриц сопротивлений R-2R, входы (17) и (18) для подключения обратных связей первой (11) и второй (12) матриц сопротивлений R-2R, аналоговые выходы (19) и (20) первой (11) и второй (12) матриц сопротивлений R-2R соответственно, а также вспомогательные аналоговые выходы (21) и (22) первой (11) и второй (12) матриц сопротивлений R-2R, согласованные с общей шиной источников питания, первый (23) конденсатор, включенный между выходом первого (6) дифференциального операционного усилителя и его инвертирующим входом, первый (24) резистор, включенный между выходом второго (7) дифференциального операционного усилителя, соединенным со входом (18) для подключения обратной связи второй (12) матрицы сопротивлений R-2R и инвертирующим входом первого (6) дифференциального операционного усилителя, аналоговый выход (20) второй (12) матрицы сопротивлений R-2R соединен с инвертирующим входом второго (7) дифференциального операционного усилителя и неинвертирующим входом первого (6) дифференциального операционного усилителя, неинвертирующий вход второго (7) дифференциального операционного усилителя подключен к общей шине источников питания, аналоговый выход (19) первой (11) матрицы сопротивления R-2R связан с инвертирующим входом четвертого (9) дифференциального операционного усилителя, выход которого связан со входом (17) для подключения обратной связи первой (11) матрицы сопротивления R-2R, выход пятого (10) дифференциального операционного усилителя связан с первым (3) выходом устройства, выход первого (6) дифференциального операционного усилителя связан со вторым (4) выходом устройства, второй (25) конденсатор, второй (26), третий (27), четвертый (28), пятый (29), шестой (30), седьмой (31), восьмой (32), девятый (33) резисторы, отличающийся тем, что второй (4) выход устройства подключен к аналоговому входу (15) первой (11) матрицы сопротивления R-2R, третий (5) выход устройства соединен с выходом третьего (8) дифференциального операционного усилителя, неинвертирующий вход четвертого (9) дифференциального операционного усилителя соединен с инвертирующим входом второго (7) дифференциального операционного усилителя и неинвертирующим входом первого (6) дифференциального операционного усилителя, между выходом пятого (10) дифференциального операционного усилителя и неинвертирующим входом третьего (8) дифференциального операционного усилителя включен второй (25) конденсатор, выход четвертого (9) дифференциального операционного усилителя связан с неинвертирующим входом третьего (8) дифференциального операционного усилителя через второй (26) резистор, инвертирующий вход пятого (10) дифференциального операционного усилителя соединен со вторым (2) входом устройства через первый дополнительный резистор (34) и соединен с общей шиной источников питания через девятый (33) резистор, а также связан с выходом пятого (10) дифференциального операционного усилителя через четвертый (28) резистор, инвертирующий вход третьего (8) дифференциального операционного усилителя соединен с инвертирующим входом пятого (10) дифференциального операционного усилителя и через третий (27) резистор подключен к третьему (5) выходу устройства и выходу третьего (8) дифференциального операционного усилителя, первый (1) вход устройства соединен со вторым (4) выходом устройства через последовательно соединенные восьмой (32) и шестой (30) резисторы, общий узел которых связан с инвертирующим входом третьего (8) дифференциального операционного усилителя через пятый (29) резистор и подключен к общей шине источников питания через седьмой (31) резистор, причем инвертирующий вход четвертого (9) дифференциального операционного усилителя соединен с неинвертирующим входом пятого (10) дифференциального операционного усилителя и связан с общей шиной источников питания через второй (35) дополнительный резистор.

| ПРОГРАММИРУЕМЫЙ ARC-ФИЛЬТР | 1989 |

|

RU2019904C1 |

| УНИВЕРСАЛЬНЫЙ АКТИВНЫЙ RC-ФИЛЬТР | 2019 |

|

RU2702499C1 |

| CN 102624348 A, 01.08.2012 | |||

| US 8436679 B1, 07.05.2013 | |||

| JP 2001036380 A, 09.02.2001. | |||

Авторы

Даты

2020-05-19—Публикация

2019-12-10—Подача