Настоящее изобретение испрашивает приоритет заявки на патент Китая № 201710007883.2, поданной в Патентное ведомство Китая 5 января 2017 г. и озаглавленной «СПОСОБ СОГЛАСНОВАНИЯ СКОРОСТИ, УСТРОЙСТВО КОДИРОВАНИЯ И УСТРОЙСТВО СВЯЗИ», и заявки на патент Китая № 201710157341.3, поданной в Патентное ведомство Китая от 16 марта 2017 года и озаглавленной «СПОСОБ СОГЛАСНОВАНИЯ СКОРОСТИ, УСТРОЙСТВО КОДИРОВАНИЯ И УСТРОЙСТВО СВЯЗИ», которые полностью включены в настоящий документ посредством ссылки.

Область техники, к которой относится изобретение

Варианты осуществления настоящего изобретения относятся к области связи и, более конкретно, к способу согласования скорости, устройству кодирования и устройству связи.

Уровень техники

С целью обеспечения качества связи в системе связи используют системы связи для повышения надежности передачи данных. Полярные коды, предложенные профессором Arikan из Турции, представляют собой первый тип кодов, которые теоретически доказали свою способность достигать предела Shannon и иметь низкую сложность кодирования и декодирования.

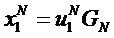

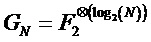

Полярный код является линейным блочным кодом. Матрица кодирования полярного кода представляет собой  , которая является

, которая является

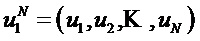

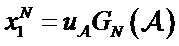

Процесс кодирования для генерирования полярного кода x1N представляет собой:

где

бит (

бит ( также называется длиной материнского кода),

также называется длиной материнского кода),  является матрицей кодирования, и

является матрицей кодирования, и  .

.  является Kronecker произведением

является Kronecker произведением

В процессе кодирования полярного кода некоторые биты в векторе  строк используют для переноса информации, и эти биты называют информационными битами. Набор индексов этих битов представлен как

строк используют для переноса информации, и эти биты называют информационными битами. Набор индексов этих битов представлен как  . Другие биты устанавливают в фиксированное значение, которое предварительно согласовывается между принимающей стороной и передающей стороной полярного кода, и эти биты называют фиксированными битами или замороженными битами. Набор индексов, фиксированных или замороженных битов представлен как

. Другие биты устанавливают в фиксированное значение, которое предварительно согласовывается между принимающей стороной и передающей стороной полярного кода, и эти биты называют фиксированными битами или замороженными битами. Набор индексов, фиксированных или замороженных битов представлен как  , который является дополнением к

, который является дополнением к  .

.

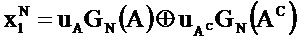

Процесс кодирования полярного кода эквивалентен

представляет собой набор информационных битов

представляет собой набор информационных битов  , и количество информационных битов в

, и количество информационных битов в  равно К.

равно К.

, и количество замороженных битов в

, и количество замороженных битов в

, в котором GN (A) является

, в котором GN (A) является  матрицей.

матрицей.

Процесс построения полярного кода представляет собой процесс выбора набора  , и выбор набора

, и выбор набора  определяет производительность полярного кода. Процесс построения полярного кода обычно включает в себя: определение на основании длины N материнского кода, что существует всего N поляризованных каналов, где каждый из поляризованных каналов соответствует одной строке в матрице кодирования, соответственно; вычисление надежности каждого из поляризованных каналов; формирование набора

определяет производительность полярного кода. Процесс построения полярного кода обычно включает в себя: определение на основании длины N материнского кода, что существует всего N поляризованных каналов, где каждый из поляризованных каналов соответствует одной строке в матрице кодирования, соответственно; вычисление надежности каждого из поляризованных каналов; формирование набора  индексов информационных битов с использованием индексов первых K поляризованных каналов с относительно высокой надежностью и формирование набора

индексов информационных битов с использованием индексов первых K поляризованных каналов с относительно высокой надежностью и формирование набора  индексов замороженных битов с использованием индексов оставшихся (N – K) поляризованных каналов. Набор

индексов замороженных битов с использованием индексов оставшихся (N – K) поляризованных каналов. Набор  определяет позиции битов информационных битов в x1N и набор

определяет позиции битов информационных битов в x1N и набор  определяет позиции битов замороженных битов в x1N.

определяет позиции битов замороженных битов в x1N.

Из матрицы кодирования можно узнать, что длина кода исходного полярного кода (материнского кода) является целочисленной степенью 2. Однако в практических применениях длина полярного кода должна быть установлена на любую длину кода и это достигают с помощью процесса, называемого согласованием скорости передачи.

В предшествующем уровне техники используют способ выкалывания или укорочения (укороченный) для реализации согласования скорости передачи. В предшествующем уровне техники материнский код, длина которого превышает целевую длину кода, обычно выкалывают или укорачивают для достижения целевой длины кода и заполняют во время декодирования для восстановления до длины материнского кода. На размеры буфера, сложность и задержки во время кодирования и декодирования оказывает влияние длина материнского кода. Когда относительно большое количество бит укорачивают или выкалывают (например, материнский код укорачивают или выкалывают с 2048 до 1200 бит), возникают довольно значительные дополнительные издержки из-за выкалывания. Увеличение целевой длины кода приводит к уменьшению скорости кода. С одной стороны, это может принести выигрыш при кодировании; с другой стороны, с увеличением длины материнского кода также увеличивается сложность.

Сущность изобретения

Варианты осуществления настоящей изобретения предоставляют способ согласования скорости передачи, устройство кодирования, способ обратного согласования скорости, устройство декодирования и устройство связи для снижения сложности полярного кодирования и декодирования.

Согласно первому аспекту предоставлен способ согласования скорости для полярного кода, включающий в себя: получение последовательности информационных битов и длины М целевого кода полярного кода; и, когда длина М целевого кода удовлетворяет заданному условию, использование полярного кода с первой длиной N1 материнского кода для кодирования последовательности информационных битов для выработки первой кодированной последовательности битов, где N1 меньше или равно M, и N1 является целочисленной степенью 2, и повторение, по меньшей мере, некоторых битов в первой кодированной последовательности битов для получения первого целевого полярного кода длиной M; или, когда целевой код длины М не удовлетворяет заданному условию, использование полярного кода со второй длиной N2 материнского кода для кодирования информационной последовательности битов для выработки второй кодированной последовательности битов, где N2 больше или равно М, и N2 является целочисленной степенью 2, и укорочение или выкалывание второй кодированной последовательности битов для получения второго целевого полярного кода длиной M.

Согласно второму аспекту предоставляют устройство кодирования, включающее в себя:

блок получения, выполненный с возможностью получать последовательность информационных битов и целевой код длины М полярного кода;

блок кодирования, выполненный с возможностью: когда целевой код длины М удовлетворяет заданному условию, использовать полярный код с первой длиной N1 материнского кода для кодирования последовательности информационных битов для выработки первой кодированной последовательности битов, в котором N1 меньше или равно М, и N1 является целой степенью 2; или, когда длина M целевого кода не удовлетворяет заданному условию, использовать полярный код со второй длиной N2 материнского кода для кодирования информационной последовательности битов для выработки второй кодированной последовательности битов, где N2 больше или равно M, и N2 является целочисленной степенью 2; и

блок согласования скорости передачи, выполненный с возможностью: повторять, по меньшей мере, некоторые биты в первой кодированной последовательности битов, чтобы получить первый целевой полярный код длиной M; или укорачивать или выкалывать вторую закодированную последовательность битов, чтобы получить второй целевой полярный код длиной M.

Согласно третьему аспекту предоставлено устройство связи, включающее в себя:

приемопередатчик, выполненный с возможностью устанавливать связь с другим устройством;

память, выполненную с возможностью хранить программу; и

процессор, выполненный с возможностью выполнять программу, хранящуюся в памяти, когда программа выполняется, процессор выполнен с возможностью: когда длина М целевого кода во время полярного кодирования удовлетворяет заданному условию, использовать полярный код с первой длиной N1 материнского кода кодировать информационную последовательность битов для выработки первой кодированной последовательности битов, где N1 меньше или равно М, и N1 является целочисленной степенью 2, и повторять, по меньшей мере, некоторые биты в первой кодированной последовательности битов, чтобы получить первый целевой полярный код длиной M; или, когда целевой код длиной M не удовлетворяет заданному условию, использовать полярный код со второй длиной N2 материнского кода для кодирования последовательности информационных битов для выработки второй кодированной последовательности битов, где N2 больше или равно M, и N2 является целочисленной степенью 2, и укорачивать или выкалывать вторую закодированную последовательность битов, чтобы получить второй целевой полярный код длиной M.

Согласно четвертому аспекту предоставлен способ обратного согласования скорости для полярного кода, включающий в себя:

прием логарифмического отношения правдоподобия LLR последовательности битов, подлежащих декодированию, с длиной M, где M является длиной целевого кода во время полярного кодирования; и

когда длина М целевого кода удовлетворяет заданному условию, определение, что передающая сторона использует способ повторения; определение местоположения повторного бита; добавление и объединение LLR в месте повторения в принятых LLRs из M битов, чтобы получить LLR первой последовательности битов, подлежащая декодированию, длина которой равна первой длине N1 материнского кода, где N1 меньше или равно М и N1 является целочисленной степенью 2; и полярное декодирование, основанное на LLR первой подлежащей декодированию последовательности битов; или

когда длина М целевого кода не удовлетворяет заданному условию, определение, что передающая сторона использует укорочение или выкалывание; определение местоположения укорочения или выкалывания и LLR на местоположении укорочения или выкалывания; восстановление принятых LLRs из M битов до второй длины N2 материнского кода, чтобы получить LLR второй последовательности битов, подлежащих декодированию, длина которой является второй длиной N2 материнского кода, где N2 больше или равно M, и N2 является целочисленной степенью 2; и полярное декодирование на основе LLR второй подлежащей декодированию последовательности битов.

Согласно пятому аспекту предоставлено устройство декодирования, включающее в себя:

блок приема, выполненный с возможностью принимать логарифмическое отношение правдоподобия LLR последовательности битов, подлежащей декодированию, с длиной M, в котором M является длиной целевого кода во время полярного кодирования;

блок де-согласования скорости, выполненный с возможностью: когда длина М целевого кода удовлетворяет заданному условию, определять, что передающая сторона использует способ повторения для реализации согласования скорости; определять местоположение повторного бита; и добавлять и объединять LLR на местоположении повторения в принятых LLRs M битов, чтобы получить LLR первой последовательности битов, подлежащей декодированию, длина которой равна первой длине N1 материнского кода, где N1 меньше или равно М, и N1 является целочисленной степенью 2; или выполнен с возможностью: когда длина М целевого кода не удовлетворяет заданному условию, определить, что передающая сторона использует способ укорочения или выкалывания для реализации согласования скорости; определять местоположение укорочения или выкалывания и LLR на местоположении укорочения или выкалывания; и восстанавливать принятые LLRs M битов до второй длины N2 материнского кода, чтобы получить LLR второй последовательности битов, подлежащих декодированию, длина которой является второй длиной N2 материнского кода, где N2 больше или равно M, и N2 является целочисленной степенью 2; и

блок декодирования, выполненный с возможностью выполнять полярное декодирование на основании LLR первой последовательности битов, подлежащей декодированию, или LLR второй последовательности битов, подлежащей декодированию.

Согласно шестому аспекту предоставлено устройство связи, включающее в себя:

приемопередатчик, выполненный с возможностью устанавливать связь с другим устройством;

память, выполненную с возможностью хранить программу; и

процессор, выполненный с возможностью выполнять программу, хранящуюся в памяти, где, при выполнении программы процессор выполнен с возможностью: когда длина М целевого кода во время полярного кодирования удовлетворяет заданному условию, определять, что передающая сторона использует способ повторения для реализации согласования скорости; определять местоположение повторного бита; добавлять и объединять LLR в местоположении повторения в принятых LLRs M битов, чтобы получить LLR первой последовательности битов, которая должна быть декодирована, длина которой равна первой длине N1 материнского кода, где N1 меньше или равно М и N1 является целочисленной степенью 2; и выполнять полярное декодирование на основании LLR первой битовой последовательности, подлежащей декодированию; или

когда целевая длина М кода не удовлетворяет заданному условию, определять, что передающая сторона использует способ укорачивания или выкалывания для реализации согласования скорости; определять место укорачивания или выкалывания и LLR в месте укорачивания или выкалывания; восстанавливать принятые LLRs M битов до второй длины N2 материнского кода, чтобы получить LLR второй последовательности битов, подлежащей декодированию, длина которой равна второй длине N2 материнского кода, где N2 больше или равно M, и N2 является целочисленной степенью 2; и выполнять полярное декодирование на основан и LLR второй подлежащей декодированию последовательности битов.

Согласно седьмому аспекту предоставлен способ согласования скорости для полярного кода, включающий в себя:

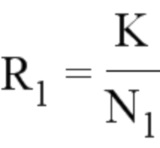

получение информационной последовательности битов и первой скорости R1 кода, где R1 = K/N1, K является количеством информационных битов, N1 = 2n, n является целым числом, меньшее или равное log2M, и M является длиной целевого кода во время полярного кодирования;

если первая скорость R1 кода меньше или равна заданной второй скорости R2 кода, использование полярного кода с длиной N1 материнского кода для кодирования информационной последовательности битов, для вывода N1 кодированных битов; и повторение, по меньшей мере, некоторых из N1 кодированных битов, чтобы получить первый целевой полярный код длиной M; или

если первая скорость R1 кода больше, чем вторая скорость R2 кода, использование полярного кода с длиной N2 материнского кода для кодирования информационной последовательности битов, для вывода N2 кодированных битов, где N2 больше или равно длине М целевого кода и N2 является целочисленной степенью 2; и укорачивание или выкалывание N2 кодированных битов, чтобы получить второй целевой полярный код с длиной M.

Согласно восьмому аспекту предоставлен способ согласования скорости для полярного кода, и способ включает в себя:

получение заданной максимальной длины Nmax материнского кода, где Nmax является целочисленной степенью 2; и

если длина M целевого кода во время полярного кодирования больше максимальной длины Nmax материнского кода, использование полярного кода с длиной Nmax материнского кода для кодирования последовательности информационных битов, чтобы вывести Nmax закодированные биты; и повторение, по меньшей мере, некоторых из Nmax кодированных битов, чтобы получить первый целевой полярный код с длиной M; или

если длина целевого кода меньше максимальной длины Nmax материнского кода, использование полярного кода с длиной N материнского кода для кодирования информационной последовательности битов, чтобы вывести N кодированных битов, где N больше или равно длине М целевого кода и N является целочисленной степенью 2; и укорачивание или выкалывание N кодированных битов, чтобы получить второй целевой полярный код длиной M.

Согласно девятому аспекту предоставлен способ согласования скорости для полярного кода, и способ включает в себя:

получение информационной последовательности битов и длины М целевого кода полярного кода; и

выбор из набора значений первой длины N1 материнского кода, которые удовлетворяют любому из следующих трех заданных условий, минимального значения в качестве значения первой длины N1 материнского кода, и использование схемы согласования частоты повторения; или, если никакое значение первой длины N1 материнского кода не удовлетворяет ни одному из следующих заданных условий, использование схемы согласования скорости посредством укорачивания или выкалывания, где три заданных условия являются следующими:

первая скорость R1 кода, определенная на основании количества K информационных битов и длины М целевого кода, меньше или равна заданной второй скорости R2 кода, и R1 = K/N1;

длина целевого кода больше заданной максимальной длины Nmax материнского кода, и первая длина N1 материнского кода равна Nmax; и

разница между длиной M целевого кода и первой длиной N1 материнского кода меньше заданного диапазона, в котором N1 меньше или равно M, и N1 представляет собой целую степень 2.

Со ссылкой на первый аспект, второй аспект, третий аспект, седьмой аспект или восьмой аспект, в возможной реализации, по меньшей мере, некоторые биты в первой кодированной последовательности битов повторяют согласно заданному правилу, и заданное правило включает в себя любой из следующих способов: в порядке с конца вперед, в порядке сначала назад, в случайном порядке, в порядке изменения бита с конца вперед, в порядке изменения бита сначала назад или в порядке убывания надежности.

Со ссылкой на четвертый аспект, пятый аспект или шестой аспект, в возможной реализации местоположение повторения определяют в соответствии с заданным правилом, и заданное правило включает в себя любой из следующих способов: в порядке с конца вперед, в порядке сначала назад, в случайном порядке, в порядке изменения бита с конца вперед, в порядке изменения бита сначала назад или в порядке убывания надежности.

Со ссылкой на любой из первого аспекта шестого аспекта, в возможной реализации, заданное условие является следующим: первая скорость R1 кода, определенная на основании величины K информационных битов, и длина целевого кода меньше или равна заданной второй скорости R2 кода, где первая скорость кода равна R1 = K/N1, K представляет собой количество информационных битов, подлежащих кодированию, N1=2n, и n является целым числом, меньшее или равное log2M. В возможной реализации первая длина материнского кода является максимальным целым числом, меньшим или равным log2M. В возможной реализации значение второй скорости кода составляет 1/42, 1/3, 1/4, 1/5, 1/6, 1/7, 1/8, 1/9, 1/10, 1/11, 1/12, 2/7, 3/8, 2/9, 3/10, 2/11 или 3/11.

Со ссылкой на любой из первого аспекта к шестому аспекту, в возможной реализации, заданное условие является следующим: длина целевого кода больше, чем заданная максимальная длина Nmax материнского кода. В возможной реализации первая длина материнского кода равна Nmax. В возможной реализации Nmax составляет 8192, 4096, 2048, 1024, 512, 256, 128 или 64.

Со ссылкой на все вышеизложенные аспекты, в возможной реализации вторая длина материнского кода представляет собой минимальную целочисленную степень 2, которая больше или равна длине целевого кода.

Со ссылкой на любой один из первого аспекта шестого аспекта, в возможной реализации, заданное условие является следующим: по меньшей мере, одно из следующих условий выполняется, и минимальное значение в наборе всех определенных значений первого кода материнского кода, соответствующая одному из следующих условий, используют в качестве значения первой длины материнского кода:

первая скорость R1 кода, определенная на основании количества K информационных битов и длины M целевого кода, меньше или равна заданной второй скорости R2 кода, и R1 = K/N1;

длина целевого кода больше, чем заданная максимальная длина Nmax материнского кода, и N1 = Nmax; или

разница между длиной M целевого кода и первой длиной N1 материнского кода меньше заданного диапазона.

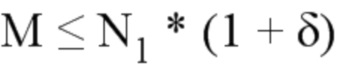

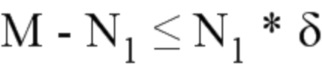

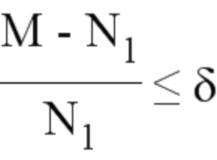

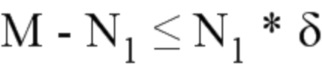

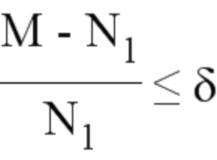

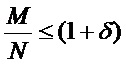

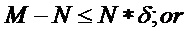

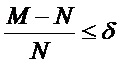

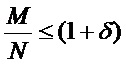

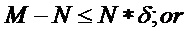

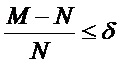

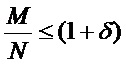

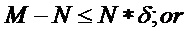

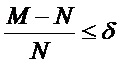

Со ссылкой на любой один из первого аспекта по шестой аспект, в возможной реализации, заданное условие является следующим: разность между длиной M целевого кода и первой длиной N1 материнского кода меньше заданного диапазона, где N1 меньше чем или равно M, и N1 представляет собой целочисленную степень, равную 2. В возможной реализации, что разница между длиной M целевого кода и первой длиной N1 материнского кода меньше, чем заданный диапазон, указывается одним из следующего:

; или

; или

.

.

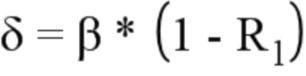

В возможной реализации δ является константой, например, значение может быть 1/8, 1/4 или 3/8.

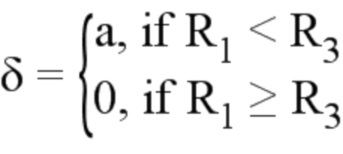

В возможной реализации значение δ является функцией первой скорости R1 кода, δ уменьшается с увеличением R1 и  .

.

В возможной реализации функциональное отношение между δ и первой скоростью R1 кода имеет вид:

или

или  , где β является константой, например, β может быть 1/2, 3/8, 1/4, 1/8 или 1/16.

, где β является константой, например, β может быть 1/2, 3/8, 1/4, 1/8 или 1/16.

В возможной реализации функциональное отношение между δ и первой скоростью R1 кода имеет вид:

, где

, где

а является константой и может быть 1/16, 1/4, 3/8, 1/2 и т.п., R3 является пороговой величиной скорости кода и является константой, и R3 может быть 1/4, 1/6, 1/3, 1/5, 1/7, 1/8, 1/9, 1/10, 1/11, 1/12, 2/7, 3/8, 2/9, 3/10, 2/11, 3/11 или тому подобное.

Другой аспект настоящего изобретения предоставляет машиночитаемый носитель данных, машиночитаемый носитель данных хранит инструкцию, и когда инструкция выполняется на компьютере, компьютер выполняет способ, описанный в предшествующих аспектах.

Другой аспект настоящего изобретения предоставляет компьютерный программный продукт, включающий в себя инструкцию, и когда компьютерный программный продукт запускают на компьютере, компьютер выполняет способ, описанный в вышеупомянутых аспектах.

Другой аспект настоящего изобретения предоставляет компьютерную программу, и когда компьютерная программа запускают на компьютере, компьютер выполняет способ, описанный в предшествующих аспектах.

Другой аспект настоящего изобретения обеспечивает устройство связи, включающее в себя:

память, выполненную с возможностью хранить программу; и

процессор, выполненный с возможностью выполнять программу, хранящуюся в памяти, где при выполнении программы процессор выполнен с возможностью выполнять способ, описанный в первом аспекте, четвертом аспекте, седьмом аспекте, восьмом аспекте или девятом аспекте, или выполнить любую возможную реализацию первого аспекта, четвертого аспекта, восьмого аспекта или девятого аспекта.

В вариантах осуществления настоящего изобретения, какой способ согласования скорости должен использоваться, определяют на основании длины целевого кода. Когда заданное условие выполнено, используют повторение. Поскольку длина материнского кода меньше или равна длине целевого кода, когда длина целевого кода не является целочисленной степенью 2, используемая длина материнского кода меньше, чем длина материнского кода, определенная при укорачивании или выкалывании. Это может удовлетворить требование усиления кодирования и уменьшить сложность кодирования и декодирования, тем самым, уменьшая задержку. Когда длина целевого кода не соответствует заданному условию, используют укорачивание или выкалывание. Сторона декодера соответствующим образом определяет способ согласования скорости, используемый стороной кодера, и выполняет де-согласование скорости и декодирование. В соответствии с вариантами осуществления настоящего изобретения достигают желаемый баланс между потерями усиления при кодировании и сложностью.

Краткое описание чертежей

Фиг. 1 является схемой базовой процедуры беспроводной связи между передающей стороной и принимающей стороной;

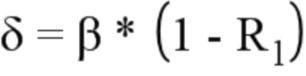

Фиг. 2 является схемой устройства 200 кодирования согласно варианту осуществления настоящего изобретения;

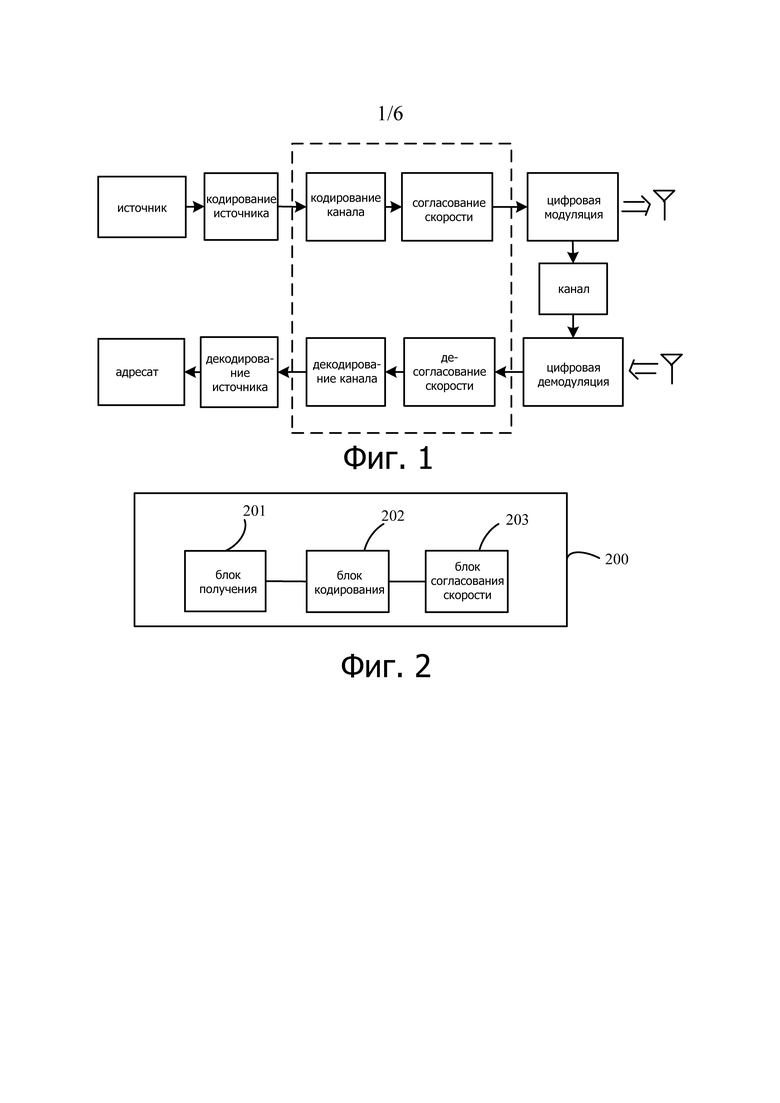

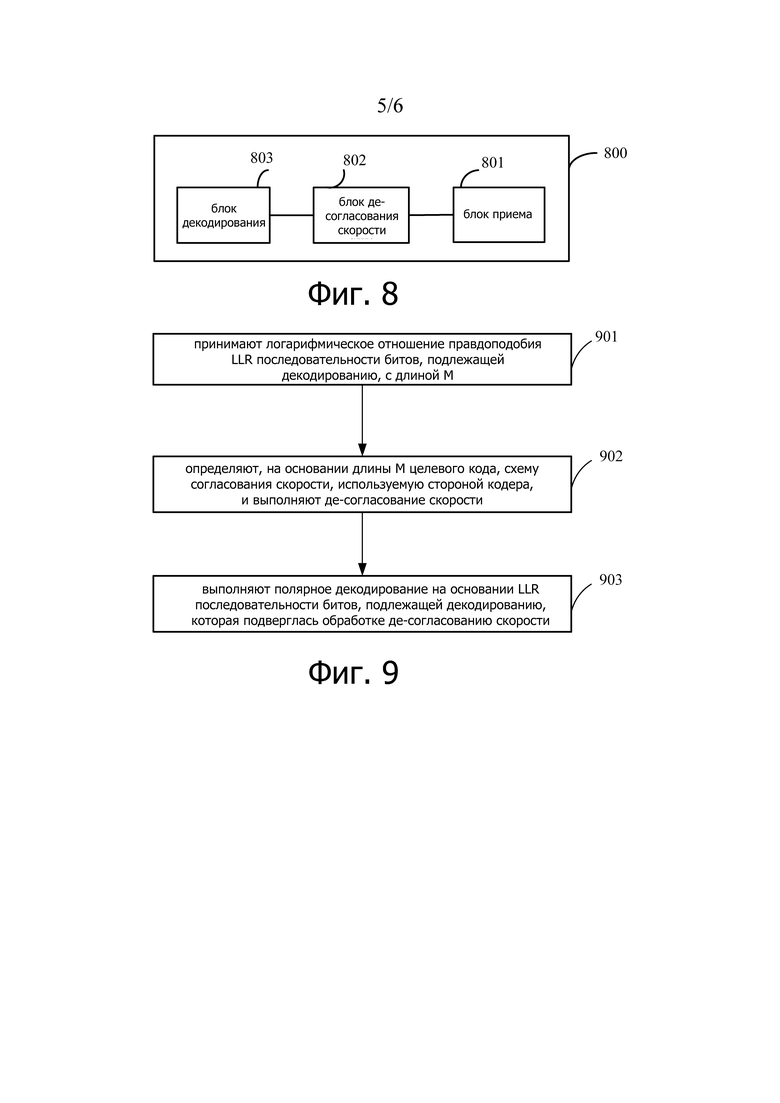

Фиг. 3 является блок-схемой последовательности операций способа согласования скорости согласно варианту осуществления настоящего изобретения;

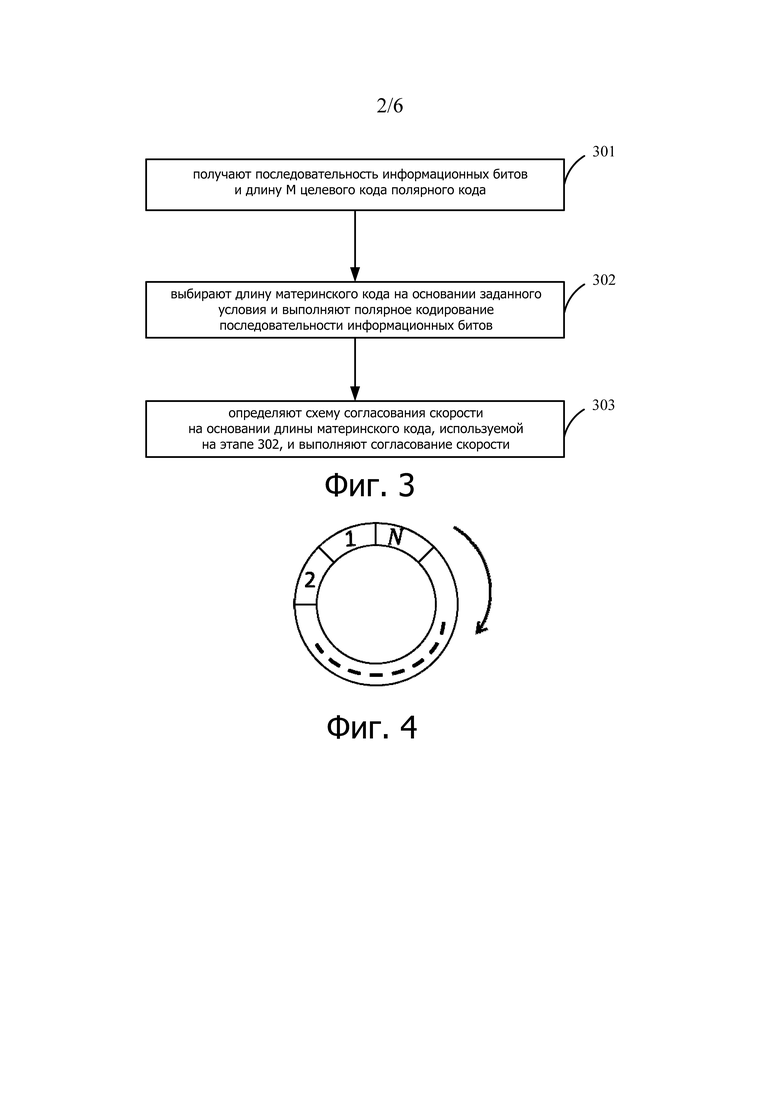

Фиг. 4 является схемой циклического буфера согласно варианту осуществления настоящего изобретения;

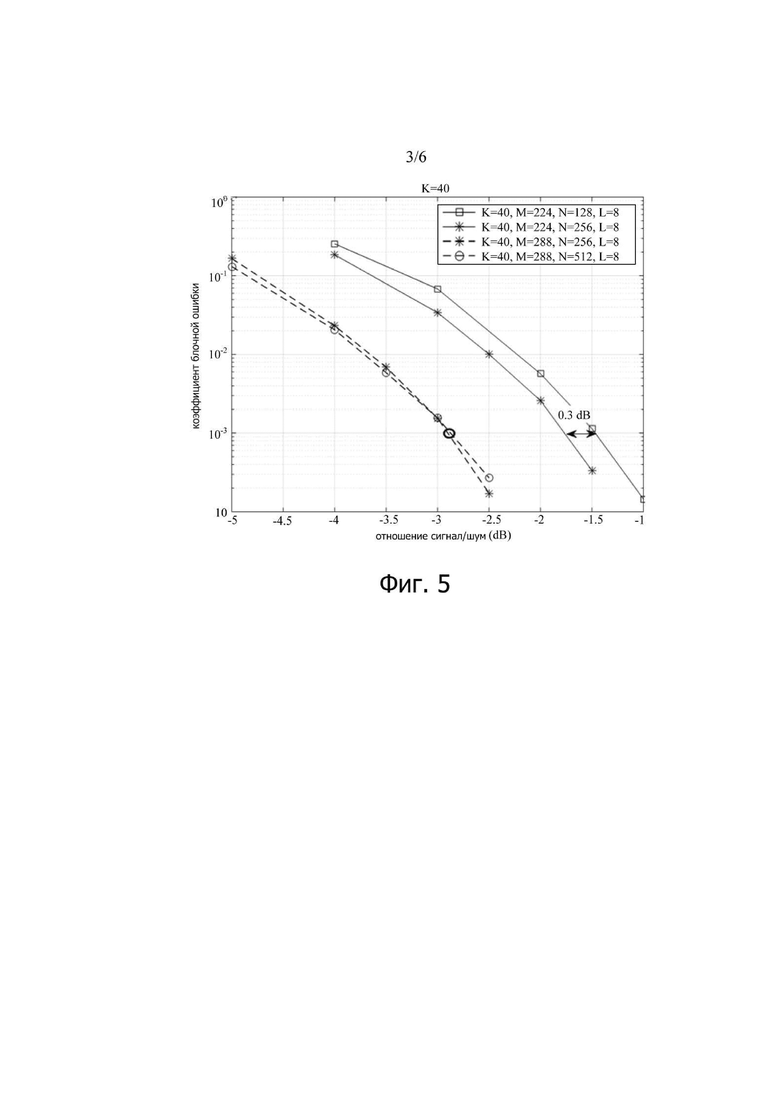

Фиг. 5 является схемой сравнения производительности между способом согласования скорости на основании повторения и способом согласования скорости на основании укорочения, которые определяют в AWGN канале с использованием порогового значения скорости кода;

Фиг. 6 является схемой сравнения производительности между способом согласования скорости на основании повторения и способом согласования скорости на основании укорачивания, которые определяются в AWGN канале с использованием максимальной длины материнского кода;

Фиг. 7 является схемой устройства 700 связи согласно варианту осуществления настоящего изобретения;

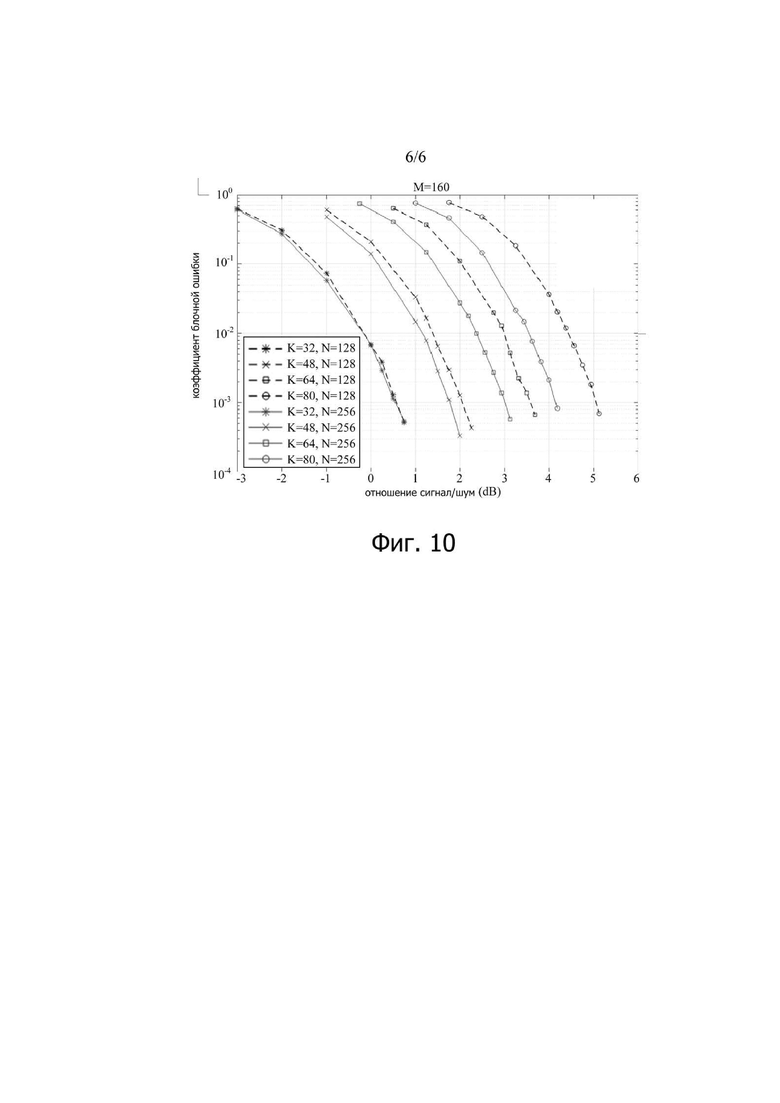

Фиг. 8 является схемой устройства 800 декодирования согласно варианту осуществления настоящего изобретения;

Фиг. 9 является блок-схемой последовательности операций способа де-согласования скорости согласно варианту осуществления настоящего изобретения; и

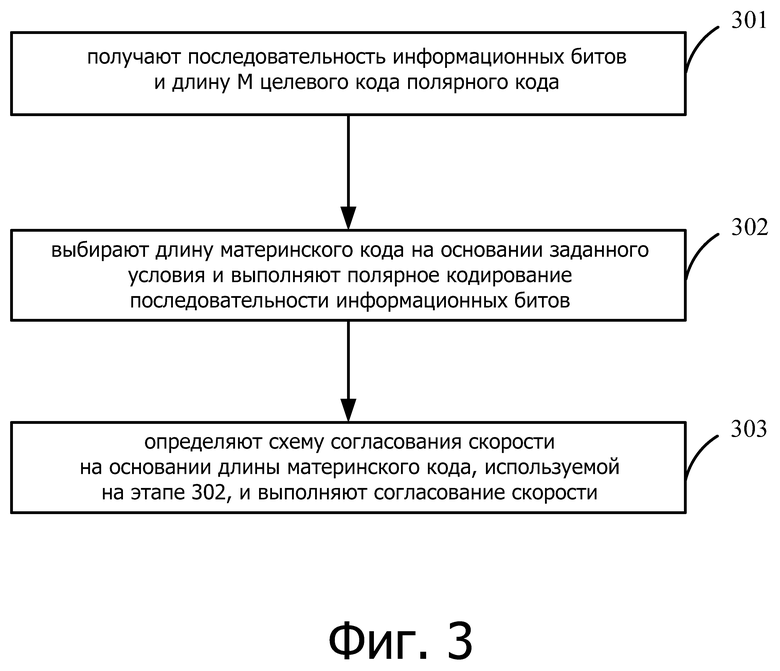

Фиг. 10 показывает сравнение производительности между способом на основании повторения и способом на основании выкалывания, которые используются, когда М = 160 и K имеет разные значения.

Описание вариантов осуществления

На фиг. 1 показывают базовую процедуру беспроводной связи. На передающей стороне сигнал от источника сигнала кодируют источником, кодируют по каналу, согласовывают по скорости, отображают с модуляцией и затем передают на приемную сторону. На принимающей стороне, после демодуляции обратного отображения, де-согласования скорости, декодирования канала и декодирования источника сигнал выводят адресату сигнала. В канальном кодировании и канальном декодировании может использоваться процесс полярного кодирования, как описано выше. Поскольку длина кода исходного полярного кода (материнского кода) является целочисленной степенью 2, в практических приложениях может потребоваться корректировка длины кода для другой длины кода. Это может быть достигнуто путем согласования скорости. Как показано на фиг. 1, на передающей стороне согласование скорости выполняют после кодирования канала для достижения любой длины целевого кода. На приемной стороне перед декодированием канала выполняют де-согласование скорости, чтобы восстановить полярный код до его первоначальной длины.

Технические решения в вариантах осуществления настоящего изобретения могут применяться к 5G системе связи, а также могут применяться к другим системам связи, таким как глобальная система мобильной связи (GSM, Global System for Mobile communications), система множественного доступа с кодовым разделением (CDMA, Code Division Multiple Access), система широкополосного множественного доступа с кодовым разделением (WCDMA, Wideband Code Division Multiple Access), служба пакетной радиосвязи общего назначения (GPRS, General Packet Radio Service), долгосрочное развитие (LTE, Long Term Evolution), LTE система дуплекса с частотным разделением (FDD, Frequency Division Duplex), LTE система дуплекса с временным разделением (TDD, Time Division Duplex) и универсальная система мобильной связи (UMTS, Universal Mobile Telecommunications System).

Согласно способу согласования скорости для полярного кода, предоставленному в варианте осуществления настоящего изобретения, определяют длину материнского кода, которая меньше или равна длине целевого кода (больше, чем количество информационных битов), и которая является целочисленной степенью 2, формируют и кодируют полярный код на основании определенной длины материнского кода, и закодированный бит повторяют для получения длины целевого кода и реализуют согласование скорости для полярного кода. Процесс согласования скорости и процесс согласования скорости являются следующими:

(1) Определяют длину N=2n материнского кода, которая меньше или равна длине M целевого кода и которая является целочисленной степенью 2 (n≤log2M, и n является целым числом), где длина M целевого кода определяется на основании количества K информационных битов и кодовой скорости R, а M = INT (K/R), где INT обозначает округление.

(2) Формируют полярный код, длина материнского кода которого равна N, и количество информационных битов которого равно K, и кодируют полярный код, чтобы получить кодированную последовательность битов.

(3) Повторяют, по меньшей мере, некоторые биты в кодированной последовательности битов на основании заданной последовательности, пока не будет получена длина М целевого кода для получения подлежащих отправке битов, которые подверглись согласованию по скорости.

(4) Принимающая сторона получает LLRs M битов, определяет местоположение повторного бита и объединяет логарифмическое отношение правдоподобия (английский: Log-likelihood Ratio, сокращенно LLR) в местоположении повторения для получения LLRs из N подлежащих декодированию битов и для реализации де-согласования скорости; и затем выполняют декодирование на основании LLRs из N подлежащих декодированию битов.

В повторении, используемом для реализации согласования скорости, поскольку длина материнского кода меньше, чем длина целевого кода, и длина материнского кода меньше, чем длина в решении, используемом в предшествующем уровне техники, сложность кодирования и декодирования уменьшается.

Когда длина материнского кода больше, производительность, вызванная усилением кодирования, лучше, но сложность выше. Уменьшение скорости кодирования приводит к увеличению длины материнского кода, и за счет усиления кодирования достигается меньшее улучшение производительности. Следовательно, может быть дополнительно решена техническая задача достижения баланса усиления и сложности кодирования с использованием параметра кодирования. Например, может быть установлено условие для длины целевого кода. Когда условие выполнено, для реализации согласования скорости используют способ повторения. Другими словами, длина материнского кода меньше, чем длина целевого кода. В этом случае, сложность относительно низкая, и потеря усиления, вызванная повторением, находится в приемлемом диапазоне. Когда указанное условие не выполняется, для реализации согласования скорости используют способ выкалывания или укорочения. В этом случае, определенная длина материнского кода больше, чем длина целевого кода, и длину целевого кода получают путем укорочения или выкалывания. В этом случае, сложность является относительно высокой, но потеря уровня усиления уменьшается.

Устройство 200 кодирования, показанное на фиг. 2 может выполнять кодирование и согласование скорости. Как показано на фиг. 3, кодирование и согласование скорости могут включать в себя следующие процессы.

301. Получают информационную последовательность битов и длину M целевого кода полярного кода.

Этот этап может быть реализован блоком 201 получения на фиг. 2. Блок 201 получения получает последовательность информационных бит и длину M целевого кода полярного кода. Длина целевого кода может быть определена на основании количества K информационных битов и используемой скорости R кода. Например, если количество информационных битов равно 20 и скорость кода равна 1/8, длина целевого кода равна 160.

302. Выбирают длину материнского кода на основании заданного условия и полярного кодирования на последовательности информационных битов.

В частности, когда длина М целевого кода удовлетворяет заданному условию, блок 202 кодирования использует полярный код с первой длиной N1 материнского кода для кодирования последовательности информационных битов для выработки первой кодированной последовательности битов с длиной N1. N1 меньше или равно М, и N1 является целочисленной степенью 2.

Когда длина М целевого кода не удовлетворяет заданному условию, блок 202 кодирования использует полярный код со второй длиной N2 материнского кода для кодирования информационной последовательности битов для выработки второй кодированной последовательности битов с длиной N2. N2 больше или равна М, и N2 является целочисленной степенью 2.

303. Определяют способ согласования скорости на основании длины материнского кода, используемого на этапе 302, и выполняют согласование скорости.

Когда длина М целевого кода удовлетворяет заданному условию, поскольку длина N1 материнского кода, используемая на этапе 302, меньше или равна длине целевого кода, блок 203 согласования скорости повторяет, по меньшей мере, некоторые биты в первой кодированной последовательности битов для получения первого целевого полярного кода с длиной M.

Когда длина М целевого кода не удовлетворяет заданному условию, длина N2 материнского кода, используемая на этапе 302, больше или равна длине целевого кода и, соответственно, блок 203 согласования скорости укорачивает или выкалывает вторую кодированную последовательность битов для получения второго целевого полярного кода длиной M.

Когда для выполнения согласования скорости используют способ повторения, повторение может выполняться в соответствии с заданным правилом до тех пор, пока не будет получена длина M целевого кода, чтобы получить целевой полярный код. Заданное правило может включать в себя любое из следующего: в порядке от конечной части к передней части, в порядке от передней части к конечной части, в случайной последовательности, в порядке перестановки битов сзади и спереди, в порядке перестановки битов от фронта назад, в порядке убывания надежности или тому подобное. Порядок обращения с битами заключается в преобразовании десятичного целого числа (индекса закодированного бита) в двоичную форму, отмене порядка элементов двоичной цифры и преобразовании отрицательной двоичной цифры в десятичную цифру. Вновь полученная цифра является значением порядка обращения битов исходной цифры. Надежность в данном документе является надежностью поляризованного канала, соответствующего кодированному биту. Выполнение повторения на основе убывания достоверности указывает, что должен предпочтительно повторяться более важный кодированный бит. N1 кодированные биты могут быть сохранены, согласно вышеупомянутому правилу предварительной установки, в циклическом буфере, показанном на фиг. 4, и закодированные биты считывают из циклического буфера по порядку во время согласования скорости, пока не будет получена длина М целевого кода. Предполагая, что N1 равно 128 и M равно 160, необходимо повторить 32 кодированных бита. 128 кодированных битов располагают на основании надежности и затем сохраняют в циклическом буфере. Биты с первого по 128-й считывают по порядку, и затем считывают 32 бита для получения полярного кода длиной 160.

То, что длина M целевого кода соответствует заданному условию, описанному на этапе 302, и на этапе 303 может заключаться в том, что первая кодовая скорость R1, определенная на основе количества K информационных битов, и первая длина N1 материнского кода меньше или равна заданной второй скорости R2 кода. Первая кодовая скорость R1 здесь равна K/N1. K является количеством информационных битов, N1 = 2n, и n является целым числом, меньшее или равное log2M. Чтобы быть конкретным, N1 является целочисленной степенью 2 и меньше или равной длине M целевого кода. Вторая скорость кода является пороговым значением скорости кода и используют для определения способа согласования скорости.

В частности, если R1≤R2, то для кодирования используют первую длину N1 материнского кода, меньшую, чем длина целевого кода, чтобы вывести N1 кодированные биты и, по меньшей мере, некоторые из N1 кодированных битов повторяют, чтобы получить целевой полярный код с длиной M. Если R1>R2, то в качестве второй длины N2 исходного кода используют минимальную целочисленную степень 2, которая больше или равна длине целевого кода, для кодирования последовательности информационных битов и вывода N2 закодированных бит и N2 закодированные биты укорачивают или выкалывают для получения второго целевого полярного кода с длиной M. Длину материнского кода определяют путем сравнения первой кодовой скорости и второй кодовой скорости. Соответственно, определяется способ согласования скорости. Вторая кодовая скорость также может упоминаться как пороговое значение кодовой скорости материнского кода. Пороговое значение скорости кодирования материнского кода может быть установлено в зависимости от фактического случая применения. В этом варианте осуществления настоящего изобретения пороговое значение скорости кодирования материнского кода может быть гибко установлено на значение между 0 и 1 в зависимости от сценария приложения. Например, значение R2 включает в себя, но не ограничивается, 1/3, 1/4, 1/5, 1/6, 1/7, 1/8, 1/9, 1/10, 1/11, 1/12, 2/7, 3/8, 2/9, 3/10, 2/11 или 3/11. Значение R2 не ограничено приведенными здесь примерами и не ограничено формой дроби, используемой в настоящем документе, и может быть установлено на значение с десятичной точкой, например, 0,167.

Определение порогового значения кодовой скорости может установить баланс между усилением и сложностью кодирования. Фиг. 5 показывает сравнение производительности между способом согласования частоты повторения и способом укорачивания, которые используют в канале с аддитивным белым гауссовским шумом (Additive White Gaussian Noise, для короткости AWGN), когда количество информационных битов равно 40, и используют разные скорости кодирования. Длина M целевого кода, соответствующая двум сплошным линиям, равна 224. Квадратный прямоугольник указывает, что используют способ согласования частоты повторения, 128 битов (первая длина N1 материнского кода) получают посредством кодирования и 96 битов повторяются, чтобы получить 224 битов (длина целевого кода). Звездочка «*» указывает, что используют способ согласования скорости укорачивания, и 256 бит (вторая длина N2 материнского кода) получают посредством кодирования и укорачивания на 32 бита, чтобы получить 224 бита (длина целевого кода). То, что пороговое значение R2 скорости кодирования равно 1/4, используется в качестве примера. В этом случае, R1 = K/N1=40/128>1/4, и R1≤R2 не выполняется. Следовательно, для выполнения согласования скорости могут использовать способ выкалывания или укорачивания. Можно выяснить, что, когда частота блочных ошибок равна 10-3, потеря усиления кодирования в режиме согласования скорости на основании повторения составляет приблизительно 0,3 дБ. Когда кодовая скорость выше, длина материнского кода меньше, и потеря усиления кодирования выше. Следовательно, когда первая кодовая скорость превышает пороговое значение кодовой скорости, подходящим является способ укорачивания или выкалывания.

Длина целевого кода, соответствующая двум пунктирным линиям на фиг. 5 - 288. Звездочка "*" указывает, что используют способ согласования частоты повторения, 256 битов (первая длина N1 материнского кода) получают посредством кодирования и 32 бита повторяют для получения 288 битов. Круг «o» указывает, что используют способ согласования скорости укорачивания, и 512 битов (вторая длина N2 материнского кода) получают посредством кодирования и укорачивания на 224 бита для получения 288 битов. Можно узнать, что усиление кодирования способом согласования скорости на основании повторений эквивалентно усилению в режиме согласования скорости на основании укорачивания; однако длина материнского кода в режиме согласования скорости на основе повторения составляет половину от длины в режиме согласования скорости на основе укорачивания. Следовательно, задержки и сложность кодирования и декодирования в режиме согласования скорости на основе повторений значительно ниже, чем в режиме согласования скорости на основе укорачивания. То, что пороговое значение R2 скорости кодирования равно 1/4, используют в качестве примера. В этом случае, R1 = K/N1 = 40/256<1/4, и заданное условие R1≤R2 выполняется. Следовательно, определяется способ согласования скорости на основе повторения. Когда кодовая скорость ниже, длина кода больше, и усиление кодирования ближе; однако способ согласования скорости на основе повторения может значительно снизить сложность и уменьшить задержку.

В этом варианте осуществления настоящего изобретения N1=2n, где n представляет собой целое число, меньшее или равное log2M. Например, когда M = 224, 7 получается путем выполнения округления log2M, и теоретически значение n может находиться в диапазоне от 1 до 7. В примере, показанном на фиг. 5, в режиме согласования скорости на основе повторения максимальное число, меньшее или равное log2M, выбирается для n. Чтобы быть конкретным, N1 = 27 = 128. В этом случае R1> R2. Если для N1 определено меньшее значение, то R1 больше, и R1 определенно больше R2. Если R2 установлено на 1/6, R1>R2. В этом случае, никакое доступное значение N1 не может соответствовать способу согласования скорости на основе повторения. В другом примере, когда M = 288, 8 получается путем выполнения округления log2M, и теоретически значение n может находиться в диапазоне от 1 до 8. В примере, показанном на фиг. 5, в режиме согласования скорости на основе повторений максимальное целое число, меньшее или равное log2M, определяется для n. Чтобы быть конкретным, 28 = 256, и условие R1≤R2 выполнено. В этом случае, если N1 равно 128, условие R1≤R2 не выполняется. Если пороговое значение R2 скорости кодирования установлено равным 1/7, независимо от того, равно ли N1 256 или 128, условие R1≤R2 не выполняется. В этом случае, используют способ согласования скорости укорачивания или выкалывания.

Для другого примера предполагают, что количество K информационных битов равно 200, длина M целевого кода равна 2400 и пороговое значение R2 скорости кодирования равно 1/4. Максимальное значение N1 может составлять 2048, 1024, 512 или тому подобное. R1 составляет соответственно 200/2048, 200/1024 или 200/512. Когда N1 равна 2048 или 1024, R1≤R2 выполняется, и могут использовать способ согласования скорости на основе повторения. Когда, по меньшей мере, две длины материнского кода удовлетворяют заданному условию, может быть определена длина материнского кода с наименьшей сложностью кодирования и декодирования, то есть, минимальная длина материнского кода. В этом примере, если и 2048, и 1024 удовлетворяют заданному условию, 1024 определяют, как значение N1. Другими словами, когда определено, что должен использоваться способ согласования скорости на основе повторения, минимальная длина материнского кода-кандидата, которая удовлетворяет заданному условию, предпочтительно определяется, как первая длина материнского кода.

В этом варианте осуществления настоящего изобретения, при условии, что значение N1 может соответствовать R1≤R2, определяется способ согласования скорости на основе повторения; и только когда никакое значение N1 не соответствует R1≤R2, используют способ согласования скорости укорачивания или выкалывания.

То, что длина M целевого кода соответствует заданному условию, описанному на этапе 302, может быть следующим: определяют, что длина M целевого кода больше или равна заданной максимальной длине Nmax материнского кода. Значение Nmax может быть гибко установлено, в зависимости от фактического сценария применения, равным целочисленной степени 2, такой как 2048, 1024, 512, 256, 128, 64 или 32. Это не ограничено. Здесь значение Nmax не имеет верхнего предела, но определяется в зависимости от сценария применения. Например, в некоторых сценариях применения, например, в канале данных, если длина целевого кода достигает 6000 или 12000, значение Nmax может быть больше. Например, значение может быть 4096 или 8192. Если определено, что для выполнения согласования скорости должен использоваться способ повторения и первая длина материнского кода равна Nmax, то передающая сторона строит и кодирует полярный код с длиной N max, и повторяет (M - Nmax) битов, чтобы получить первый целевой полярный код с длиной M целевого кода. Принимающая сторона объединяет сигнал LLR в месте повторения, восстанавливает принятый сигнал до длины Nmax материнского кода и затем выполняет декодирование.

Например, Nmax = 2048, длина M целевого кода равна 600 и M <Nmax. В этом случае, для выполнения согласования скорости используют способ укорачивания или выкалывания, и минимальная целочисленная мощность 2, превышающая 600, а именно, 1024, определяется как длина материнского кода. Полярный код строят на основании длины 1024 материнского кода и длины 600 целевого кода, и 1024 бита получают посредством кодирования и укорачиваются или прокалывают на 424 бита для получения целевых 600 битов.

Например, Nmax = 1024, длина M целевого кода равна 2400, а M> Nmax. В этом случае, способ повторения используют для выполнения согласования скорости, и определяют, что длина материнского кода равна 1024. Полярный код строят на основании длины 1024 материнского кода, 1024 битов получают посредством кодирования, и 1376 битов являются полученный посредством повторения, чтобы получить 2400-битовый целевой полярный код. Если Nmax = 2048, M> Nmax все еще выполняется. Полярный код может быть построен на основании длины 2048 кода, 2048 битов получены посредством кодирования и 352 бита повторяют для получения 2400 битового целевого полярного кода.

Если в системе максимальное количество информационных битов составляет 200 и минимальная кодовая скорость равна 1/12, длина целевого кода составляет 2400. Согласно традиционному способу согласования скорости кодирования должно выполняться до тех пор, пока не будет получено 4096 битов, и затем выполняется выкалывание или укорочение, чтобы получить 2400 бит. Согласно решениям в настоящем изобретении рассматривают усиление кодирования. 2048/1024 битов получают посредством кодирования, и затем 2400 битов получают посредством повторения. По сравнению с обычным способом согласования скорости потери при кодировании практически отсутствуют (когда при кодировании получают 1024 бита, потеря при кодировании находится в пределах 0,1 дБ). Однако с точки зрения сложности, по сравнению с буфером для выполнения кодирования для получения 4096 битов, буфер для выполнения кодирования для получения 2048 или 1024 битов уменьшен до 1/2 или 1/4. Сложность операции значительно снижается, и задержка декодирования может быть уменьшена приблизительно на 20% или 50%.

Фиг. 6 показывает сравнение производительности между способом согласования скорости на основе повторения и способом согласования скорости на основе укорачивания, которые используют в AWGN канале. Количество K информационных битов равно 200. На этом чертеже длина M целевого кода, соответствующая группе сплошных линий, равна 1184. Длина материнского кода, соответствующего квадратному прямоугольнику, равна 1024, и 160 битов повторяют, чтобы получить 1184 биты. Длина материнского кода, соответствующего звездочке «*» или кружок «o», составляет 2048, и 1184 битов получаются путем укорачивания. Это можно узнать из фиг. 6 видно, что усиление кодирования способом согласования скорости на основании повторения эквивалентно усилению при согласовании скорости на основании укорачивания.

Длина целевого кода, соответствующая группе пунктирных линий на фиг. 6, равна 2400. Длина материнского кода, соответствующая квадратной ячейке, равна 1024, и 1376 битов получено путем повторения, чтобы получить 2400 битов. Длина материнского кода, соответствующего звездочке «*», составляет 2048, и 352 бита повторяют для получения 2400 бит. Длина материнского кода, соответствующего кружку «о», составляет 4096 битов, а 2400 битов получаются путем укорачивания. Это можно узнать из фиг. 6, что усиление кодирования на основании 2048 битов способом на основании повторения эквивалентно таковому на основании укорочения, и потеря усиления кодирования на основе 1024 битов на основе повторения находится в пределах 0,05 дБ по сравнению с таковой при укорачивании. Однако по сравнению с способом укорачивания, когда длина целевого кода не является целочисленной степенью 2, длина материнского кода, используемая в способе согласования скорости на основании повторений, уменьшается, по меньшей мере, на половину. Следовательно, размер требуемого буфера может быть значительно уменьшен, сложность операций кодирования и декодирования уменьшена и задержка уменьшена.

Выкалывание, описанное в этом варианте осуществления настоящего изобретения, включают в себя квазиоднородное выкалывание (Quasi-Uniform Puncture, QUP для краткости). Во-первых, определяют, что длина материнского кода является целочисленной степенью 2, которая больше или равна длине целевого кода. Затем определяют выкалывание (место выкалывания) на основе длины материнского кода и целевой длины кода. Режим выкалывания может быть указан с использованием двоичной последовательности (00… 011… 1), и определяется, что «0» обозначает место выкалывания и «1» обозначает место, которое не выкалывают. Пропускная способность канала, соответствующая местоположению выкалывания, установлена на 0 (или вероятность ошибки установлена на 1, или отношение сигнал/шум SNR установлено на бесконечно малое значение). Надежность поляризованных каналов рассчитывают с использованием такого способа, как эволюция плотности, гауссовское приближение или линейная подгонка, и сортируют для определения местоположения информационного бита и фиксированного бита (фиксированного бита). Сторона кодера удаляет закодированный бит, который находится в месте выкалывания, чтобы получить полярный код.

Способ укорачивания полярного кода (Shorten), описанный в настоящем изобретении, заключается в следующем: определяют, что длина материнского кода представляет собой целую степень 2, которая больше или равна длине целевого кода. Кодированный бит в месте укорачивания (Shorten) относится только к фиксированному биту. Процесс включает в себя: вычисление уровня надежности поляризованных каналов на основании материнского кода, затем определяют местоположение укорачивания, фиксированный бит помещают в соответствующий поляризованный канал, оставшиеся местоположения информационного бита и замороженного бита (фиксированный бит) в поляризованном канале определяют на основе надежности, и удаляют закодированный бит в местоположении укорачивания, чтобы получить полярный код и реализовать согласование скорости. Согласно способу согласования скорости на основе укорачивания, надежность поляризованных каналов не нужно пересчитывать на основе местоположения укорачивания, но фиксированный бит помещают в поляризованный канал, соответствующий местоположению укорачивания. Это значительно уменьшает сложность построения полярного кода.

Как показано на фиг. 7, настоящее изобретение предоставляет другое устройство 700 связи, которое может реализовывать кодирование и согласование скорости. Устройство 700 связи включает в себя:

приемопередатчик 701, выполненный с возможностью устанавливать связь с другим устройством;

память 702, выполненную с возможностью хранить программу; и

процессор 703, выполненный с возможностью выполнять программу, хранящуюся в памяти, где при выполнении программы процессор выполнен с возможностью: когда длина M целевого кода во время полярного кодирования удовлетворяет заданному условию, использовать полярный код с первой длиной N1 материнского кода для кодирования последовательности информационных битов для выработки первой кодированной последовательности битов, где N1 меньше или равна М, и N1 является целочисленной степенью 2, и повторять, по меньшей мере, некоторые биты в первой кодированной последовательности битов для получения первого целевого полярного кода длиной M; или, когда длина M целевого кода не удовлетворяет заданному условию, использовать полярный код со второй длиной N2 материнского кода для кодирования информационной последовательности битов для выработки второй кодированной последовательности битов, где N2 больше или равно M, и N2 является целочисленной степенью 2, и укорачивать или выкалывать вторую кодированную последовательность битов для получения второго целевого полярного кода длиной M. Приемопередатчик 701, память 702 и процессор 703 соединены с использованием шины.

Определение, удовлетворяет ли длина М целевого кода заданному условию, и соответствующая реализация согласования скорости являются такими же, как описанные выше. Определение, используют ли повторение, укорочение или выкалывание осуществляют с использованием порогового значения скорости кода материнского кода или максимальной длины материнского кода, так что коэффициент усиления и сложность кодирования сбалансированы. Процесс повторения и процесс укорачивания или выкалывания могут быть такими же, как описано выше.

В некоторых вариантах осуществления устройство связи имеет функции как кодирования, так и декодирования. При работе в качестве отправителя устройство связи выполняет процедуру кодирования и согласования скорости. При работе в качестве приемника устройство связи выполняет процедуру де-согласования скорости и декодирования. Устройство связи включает в себя микросхему основной полосы частот. Микросхема основной полосы включает в себя кодер и декодер. Кодер может быть выполнен с возможностью выполнять функцию, которая является такой же, как у вышеупомянутого устройства кодирования, и декодер может выполнять функцию, которая является такой же, как у вышеупомянутого устройства декодирования. Устройство связи включает в себя устройство, которое имеет функцию двунаправленной беспроводной связи, такое как базовая станция или устройство пользователя.

Устройство 800 декодирования, показанное на фиг. 8 может быть выполнено с возможностью выполнять де-согласование скорости и декодирование в настоящем изобретении. Как показано на фиг. 9, процесс де-согласования скорости и декодирования включает в себя следующие этапы.

901. Принимают логарифмическое отношение правдоподобия (Log-likelihood Ratio, LLR для краткости) последовательности битов, подлежащей декодированию, с длиной M, где M является длиной целевого кода во время полярного кодирования.

Блок 801 приема принимает логарифмическое отношение правдоподобия LLR последовательности битов, подлежащей декодированию, с длиной M, где M совпадает с длиной целевого кода, используемого стороной кодера для выполнения полярного кодирования.

902. Определяют, на основании длины M целевого кода, способ согласования скорости, используемый стороной кодера, и выполняют де-согласование скорости.

Когда длина М целевого кода удовлетворяет заданному условию, блок 802 де-согласования скорости определяет, что передающая сторона использует способ повторения для выполнения согласования скорости, определяет местоположение повторного бита и добавляет и объединяет LLR на местоположении повторении в принятых LLRs M битов, чтобы получить LLR первой последовательности битов, которая должна быть декодирована, длина которой равна первой длине N1 материнского кода, где N1 меньше или равно M, и N1 является целочисленной степенью 2.

Когда длина M целевого кода не удовлетворяет заданному условию, блок 802 де-согласования скорости определяет, что сторона кодера использует способ укорачивания или выкалывания для выполнения согласования скорости, определяет местоположение укорачивания или выкалывания и LLR на местоположении укорачивания или выкалывания и восстанавливает LLRs, принятые блоком 801 приема, из M битов до второй длины N2 материнского кода, чтобы получить LLR второй последовательности битов, которая должна быть декодирована, чья длина равна второй длине N2 материнского кода, где N2 больше или равно М, и N2 является целочисленной степенью 2.

Если сторона кодера использует способ повторения для выполнения согласования скорости, то сторона декодера соответственно выполняет де-согласование скорости в соответствии с правилом повторения, предварительно установленным как на стороне кодера, так и на стороне декодера. Например, если правило повторения на стороне кодера представляет собой порядок с конца вперед во время согласования скорости, то LLRs последних M - N1 битов в M битах суммируют и объединяют для получения LLRs из N1, подлежащих декодированию битов.

Если сторона кодера использует способ укорачивания для выполнения согласования скорости, блок 802 де-согласования скорости использует бит в месте укорачивания в качестве известного бита, устанавливает соответствующее LLR равным бесконечности и восстанавливает LLR вместе с принятым LLR в месте, которое не укорочено, до длины материнского кода.

Если сторона кодера использует способ выкалывания для выполнения согласования скорости, блок 802 де-согласования скорости использует бит, соответствующий местоположению выкалывания, в качестве неизвестного бита для обработки, устанавливает соответствующее отношение логарифмического правдоподобия равным 0 и восстанавливает отношение правдоподобия вместе с принятым LLR в местоположении, которое не выколото, к длине материнского кода.

903. Выполняют полярное декодирование на основании LLR последовательности битов, которая должна быть декодирована, которая подверглась обработке де-согласованию скорости.

Когда длина М целевого кода удовлетворяет заданному условию, блок 803 декодирования соответственно выполняет полярное декодирование на основании LLR первой последовательности битов, подлежащей декодированию.

Когда длина М целевого кода не удовлетворяет заданному условию, блок 803 декодирования соответственно выполняет полярное декодирование на основе LLR второй последовательности битов, подлежащей декодированию.

Как и на стороне кодера, если длина M целевого кода соответствует заданному условию, описанному на этапе 902, и на этапе 903 может быть то, что первая скорость R1 кода, определенная на основании количества K информационных битов, и длина M целевого кода меньше или равна заданной второй скорости кода R2. Первая скорость R1 кода здесь равна K/N1. K является количеством информационных битов, N1 = 2n, и n является целым числом, меньшее или равное log2M. Процесс определения N1 такой же, как и на стороне кодера. Вторая кодовая скорость также может упоминаться как пороговое значение скорости кодирования материнского кода и предварительно устанавливается на стороне кодера и на стороне декодера. Значение R2 такое же, как на стороне кодера, и может составлять 1/4 или 1/6. Например, R2 на стороне кодера составляет 1/4, а также на 1/4 на стороне декодера. Когда R1≤R2, определяют, что сторона кодера использует способ согласования частоты повторения, и используемая длина материнского кода равна N1. Когда R1>R2, определяют, что сторона кодера использует способ укорочения или выкалывания.

Альтернативно, заданное условие может быть следующим: устанавливают максимальную длину Nmax материнского кода, и длину M целевого кода сравнивают с максимальной длиной материнского кода. Если M≥Nmax удовлетворяется, определяют, что передающая сторона использует способ повторения для выполнения согласования скорости и, следовательно, сторона декодера, соответственно, выполняет де-согласование скорости. Если M<Nmax, определяют, что передающая сторона использует способ укорочения или выкалывания для выполнения согласования скорости, и сторона декодера соответственно выполняет де-согласование скорости. Как и на стороне кодера, Nmax может быть установлено в целочисленную степень 2, такую как 2048, 1024, 512, 256, 128, 64 или 32. Это не ограничено.

Сторона кодера и сторона декодера могут быть предварительно сконфигурированы для использования способа согласования скорости укорочения или способа согласования скорости выкалывания, когда длина М целевого кода не удовлетворяет заданному условию. Например, способ укорочения используют равномерно или способ выкалывания используют равномерно.

Устройство связи, показанное на фиг. 7 также может быть выполнено с возможностью выполнять процесс де-согласования скорости и декодирования. Устройство связи включает в себя:

приемопередатчик 701, выполненный с возможностью устанавливать связь с другим устройством;

память 702, выполненную с возможностью хранить программу; и

процессор 703, выполненный с возможностью выполнять программу, хранящуюся в памяти 701, где, при выполнении программы, процессор 703 выполнен с возможностью: когда длина М целевого кода во время полярного кодирования удовлетворяет заданному условию, определять, что передающая сторона использует способ повторения для осуществления согласования скорости; определять местоположение повторного бита; добавлять и объединять LLR в местоположении повторения в принятых LLRs M битов, чтобы получить LLR первой последовательности битов, которая должна быть декодирована, длина которой равна первой длине N1 материнского кода, где N1 меньше или равно М и N1 является целой степенью 2; и выполнять полярное декодирование на основе LLR первой последовательности битов, подлежащей декодированию; или

выполнен с возможностью: когда длина M целевого кода не удовлетворяет заданному условию, определять, что передающая сторона использует способ укорочения или выкалывания для реализации согласования скорости; определять место укорочения или выкалывания и LLR в месте укорочения или выкалывания; восстанавливать принятые LLRs M битов до второй длины N2 материнского кода, чтобы получить LLR второй последовательности битов, подлежащей декодированию, длина которой равна второй длине N2 материнского кода, где N2 больше или равно M, и N2 является целочисленной степенью 2; и выполнять полярное декодирование на основании LLR второй подлежащей декодированию последовательности битов.

Определение того, соответствует ли длина М целевого кода заданному условию, и соответствующая реализация де-согласования скоростей являются такими же, как описанные выше. Использует ли сторона кодера способ согласования скорости на основании повторения или способ согласования скорости укорочения или выкалывания, может быть определено с использованием порогового значения скорости кода материнского кода или максимальной длины материнского кода.

Решения в настоящем изобретении могут быть использованы в канале управления или канале данных. Относительно небольшое количество информационных битов должно быть отправлено в канал управления. Следовательно, в варианте осуществления, когда выполняют кодирование и декодирование, длины кода (длины материнского кода) и способы согласования скорости, используемые в различных случаях, могут быть перечислены в зависимости от того, соответствует ли длина целевого кода заданному условию, описанному в настоящем документе, и сохранены на стороне кодера и стороне декодера. Другими словами, стороне кодера и стороне декодера не нужно определять, соответствует ли длина целевого кода заданному условию. Вместо этого сторона кодера и сторона декодера непосредственно считывают соответствующий параметр из сконфигурированного параметра в соответствии с заданным правилом для выполнения кодирования, согласования скорости и соответствующего де-согласования скорости и декодирования. В примере, если предположить, что используют пороговое значение скорости кода (скорости кодирования) для материнского кода, и пороговое значение R2 кодовой скорости установлено на 1/4, сконфигурированный параметр кодирования может быть сохранен в форме, показанной в таблице 1. В этом случае, количество информационных битов, длина целевого кода, длина материнского кода и способ согласования скорости были определены в соответствии с заданным правилом. В качестве альтернативы, способ согласования скорости может не отображаться. Если длина материнского кода меньше или равна длине целевого кода, определяют, что используют способ согласования частоты повторения. Если длина материнского кода больше, чем длина целевого кода, определяют, что используют способ укорочения или выкалывания. Сторона кодера и сторона декодера могут единообразно указывать, используется ли способ укорочения или режим выкалывания и соответствующий режим укорочения или режим выкалывания. Конечно, способ согласования скорости может альтернативно быть показан в сконфигурированном параметре. Способ выполнения повторения также может быть сконфигурирован на стороне кодера и на стороне декодера.

Таблица 1

При условии, что заданное условие определено, длина материнского кода и способ согласования скорости, используемые в каждом случае, могут быть определены. Например, когда R2 равен 1/6, параметры кодирования и способы согласования скорости, используемые в разных случаях, могут быть определены.

Устройство связи, описанное в этом варианте осуществления настоящего изобретение, может быть устройством беспроводной связи, таким как точка доступа, станция, базовая станция или пользовательский терминал.

Полярный код, описанный в этом варианте осуществления настоящего изобретение, включает в себя, но не ограничивается этим, Arikan полярный код или может быть CA-полярным кодом или PC-полярным кодом. Arikan полярный код является исходным полярным кодом, он не связан с другим кодом и имеет только информационный бит и замороженный бит. CA-полярный код представляет собой полярный код, каскадный с циклической проверкой избыточности (Cyclic Redundancy Check, CRC для краткости). РС-полярный код представляет собой полярный код, каскадный с кодом проверки на четность (Parity Check, РС для краткости). РС-полярный код и СА-полярный код улучшают характеристики полярного кода путем каскадирования различных кодов.

«Последовательность информационных битов», описанная в этом варианте осуществления настоящего изобретения, также может называться «кодируемой последовательностью битов» или «набором информационных бит». Соответственно, «количество информационных битов» может быть количеством кодируемых битов в последовательности битов, которые должны быть закодированы, или количеством элементов в наборе информационных битов.

То, что целевая длина М кода удовлетворяет заданному условию, описанному в настоящем изобретении, может быть дополнительно, что разность между длиной М целевого кода и первой длиной N1 материнского кода меньше заданного диапазона. N1 меньше или равно M, и N1 является целочисленной степенью 2. Например, заданное условие может быть M≤N1 * (1 + δ). Если длина N1 материнского кода удовлетворяет условию, определяют, что используется способ согласования скорости на основе повторения, первая длина N1 материнского кода используется для выполнения полярного кодирования, для получения первой кодированной последовательности битов и, по меньшей мере, некоторые биты в первой кодированной последовательности битов повторяются, чтобы получить кодированную последовательность битов с длиной целевого кода. Если условие не выполняется, используют способ согласования скорости на основании укорочения или выкалывания. Вышеуказанное заданное условие может дополнительно указываться как  ,

,  или

или  .

.

δ может быть константой, например, может быть установлен на 1/8, 1/4 или 3/8.

δ может быть значением, связанным с кодовой скоростью. δ = ФУНКЦИЯ (R1) является функцией  . δ обычно уменьшается с увеличением R1, и K является количеством информационных битов. Другими словами, значение δ связано с количеством информационных битов и длиной материнского кода.

. δ обычно уменьшается с увеличением R1, и K является количеством информационных битов. Другими словами, значение δ связано с количеством информационных битов и длиной материнского кода.

В реализации функция δ относительно кодовой скорости R1 может быть разработана как  . β - заданная константа. Например, β может быть 1/2, 3/8, 1/4, 1/8 или 1/16. Другими словами, δ является линейной функцией R1. Чем больше R1, тем меньше δ, и меньшее количество битов разрешено повторять.

. β - заданная константа. Например, β может быть 1/2, 3/8, 1/4, 1/8 или 1/16. Другими словами, δ является линейной функцией R1. Чем больше R1, тем меньше δ, и меньшее количество битов разрешено повторять.

Предполагая, что M = 160, K = 80, β = 1/2 и N1 = 128, R1 = 80/128 = 0,625 и δ = 1/2 * (1-80/128) = 0,1875. M≤N1 * (1 + δ) используют для определения, использовать ли согласование скорости повторения, и N1 * (1 + δ) = 128 * (1 + 0,1875) = 152. Поскольку M = 160> 152 и M≤N1 * (1 + δ) не выполняется, способ согласования скорости повторения не используется. Вместо этого может использоваться другой способ, такой как укорочение или выкалывание. В вышеупомянутых параметрах, если K = 32 и другие параметры остаются неизменными, R1 = 32/128 = 1/4, δ = 1/2 * (1-1/4) = 3/8, N1 * (1 + δ) = 128 * (1 + 3/8) = 176, M = 160 <176 и M≤N1 * (1 + δ). Поэтому используют способ согласования скорости на основе повторения. Чтобы быть конкретным, первая длина материнского кода равна 128. Кодированная последовательность битов длиной 128 получают посредством кодирования, и 32 бита в кодированной последовательности битов повторяют, чтобы получить длину целевого кода равную 160.

В другой реализации функция δ относительно кодовой скорости R может быть разработана как δ = β * (1-R1)2. β является константой. Например, β может быть 1/2. Чтобы быть точным, δ является квадратичной функцией R1. Чем больше R1, тем меньше δ, и меньшее количество битов разрешено повторять. Предполагая, что M = 160, K = 80, β = 1/2 и N1 = 128, R1 = 80/128 = 0,625 и δ = 1/2 * (1-80/128) 2 = 0,0703125. M≤N1 * (1 + δ) используется, чтобы определить, использовать ли согласования скорости повторением, и N1 * (1 + δ) = 128 * (1 + 0.0703125) = 137. Поскольку M = 160> 137 и M≤N1 * (1 + δ) не выполняется, способ согласования скорости повторением не используется. Вместо этого может использоваться другой способ, такой как укорочение или выкалывание. В вышеупомянутых параметрах, если K = 32 и другие параметры остаются неизменными, R1 = 32/128 = 1/4, δ = 1/2 * (1-1/4) 2 = 9/32, N1 * (1 + δ) = 128 * (1 + 9/32) = 164, М = 160 <164 и M≤N1 * (1 + δ). Поэтому используют способ согласования скорости на основе повторения. Чтобы быть конкретным, первая длина материнского кода равна 128. Получают кодированную последовательность битов длиной 128 посредством кодирования, и 32 бита в кодированной последовательности битов повторяют для получения длины целевого кода равной 160.

В другой реализации функция δ относительно кодовой скорости R1 может быть подставлена как:

формула (1)

формула (1)

δ является кусочной функцией, определенной на основании R1. Если R1 меньше заданного порогового значения R3, значение δ представляет собой a, a является константой, и значение a может составлять 1/16, 1/4, 3/8, 1/2 или тому подобное. Если R1 больше или равно пороговому значению R3, значение δ равно 0. R3 может составлять 1/4 или 1/6 или может составлять 1/3, 1/4, 1/5, 1/7, 1/8, 1/9, 1/10, 1/11, 1/12, 2/7, 3/8, 2/9, 3/10, 2/11, 3/11 или тому подобное. Предполагая, что M = 160, K = 80, R3 = 1/4 и N1 = 128, R1 = 80/128 = 0,625> 1/4 и δ = 0 на основании формулы (1). M≤N1 * (1 + δ) используется для определения, использовать ли соответствие скорости повторением, и N1 * (1 + δ) = 128 * (1 + 0) = 128. Поскольку M = 160> 128, а M≤N1 * (1 + δ) не соблюдается, способ согласования скорости повторением не используют. Вместо этого может использоваться другой способ, такой как укорочение или выкалывание. В вышеупомянутых параметрах, если K = 32 и другие параметры остаются неизменными, R1 = 32/128 = 1/4 = R3, значение δ равно 0, и способ согласования скорости повторением не используется. Если R3 = 1/6, R1 = 32/128 = 1/4 <R3, значение δ равно 1/8, N1 * (1 + δ) = 128 * (1 + 1/8) = 144, М = 160> 144, и M≤N1 * (1 + δ) не выполняется. Следовательно, способ согласования скорости повторением не используется. Вместо этого может использоваться другой способ, такой как укорочение или выкалывание. Если в формуле (1) R1 <R3 и значение δ равно 1/2, N1 * (1 + δ) = 128 * (1 + 1/2) = 192, М = 160 <192 и М≤N1 * (1 + δ) выполнено. Поэтому используется способ согласования скорости на основе повторения. Чтобы быть конкретным, длина первого материнского кода равна 128, кодированная последовательность битов длиной 128 получают посредством кодирования, и 32 бита в кодированной последовательности битов повторяют для получения длины целевого кода равной 160.

Фиг. 10 показывает сравнение производительности между способом на основе повторения и способом на основе выкалывания, которые используют, когда М = 160 и K имеет разные значения. Пунктирная линия указывает, что используют способ согласования скорости на основе повторения, и сплошная линия указывает, что используют способ согласования скорости на основе выкалывания. Длина целевого кода установлена на фиксированное значение 160. Длина целевого кода может быть получена путем выполнения выкалывания на основе 256 (сплошная линия) или получена путем выполнения повторения на основе 128 (пунктирная линия). Если повторение выполняется на основе 128, количество битов, которое необходимо повторить, составляет (160-128), то есть, 32, и пропорция повторения составляет 32/128 = 1/4. Это можно узнать из фиг. 10, что, когда количество информационных битов различно, то есть, скорости кодирования различны, производительность способа повторения отличается от производительности способа выкалывания. Когда кодовая скорость высока (K относительно велика, например, K = 80), по сравнению со способом выкалывания, способ повторения имеет очевидную потерю производительности (приблизительно 0,7 дБ). Когда кодовая скорость низкая (K относительно мала, например, K = 20 или K = 40), производительность способа повторения эквивалентна производительности способа выкалывания. Следовательно, значение δ определяется на основе кодовой скорости, и δ уменьшается с увеличением R1. Когда потери производительности эквивалентны или немного отличаются, используется согласование скорости повторением, так что достигается желаемый баланс между потерями усиления кодирования и сложностью.

Настоящее изобретение предоставляет множество вариантов осуществления для определения того, соответствует ли длина М целевого кода заданному условию. В другом варианте осуществления минимальное значение может быть определено как значение первой длины материнского кода из всех значений N1, которые удовлетворяют любому из вышеупомянутых заданных условий, и используется способ согласования скорости на основе повторения. Если никакое значение первой длины материнского кода не соответствует заданному условию, используется способ укорачивания или выкалывания. Предполагают, что M = 576 и K = 20, набор значений N1, соответствующих случаям, в которых разрешено использовать способ согласования скорости на основе повторения, получается на основе различных заданных условий.

Заданное условие 1: первая кодовая скорость R1, определенная на основе количества K информационных битов и длины M целевого кода, меньше или равна заданной второй кодовой скорости R2, и R1 = K/N1. Здесь значение R2 равно 1/4, и на основе R1 = K/N1 значение N1, которое соответствует R1<R2, составляет 512, 256 или 128.

Заданное условие 2:

Длина целевого кода больше, чем заданная максимальная длина Nmax материнского кода, и Nmax составляет 512. На основании М = 576> 512, предварительно установленное условие выполняется, используется способ согласования скорости на основе повторения, и N1 = 512.

Заданное условие 3:

Разница между длиной М целевого кода и первой длиной N1 материнского кода меньше, чем заданный диапазон, и указывается как M≤N1 * (1 + δ). Значение δ определяется по формуле (1), a = 1/8 и R3 = 1/6. Если N1 = 512, R1 = 20/512 <R3 и δ равно 1/8, N1 * (1 + δ) = 576, M = N1 * (1 + δ), и заданное условие выполняется. Если N1 = 256, R1 = 20/256 <R3 и δ равно 1/8, N1 * (1 + δ) = 288, M> N1 * (1 + δ), и заданное условие не выполняется. Следовательно, значение N1, которое определяется на основе заданного условия 3 и которое позволяет использовать способ согласования скорости на основе повторения, составляет 512.

Набор значений N1, полученных на основе вышеупомянутых трех заданных условий, равен {128, 256, 512}. Используют способ согласования скорости на основе повторений, минимальное значение 128 определяется как значение первой длины материнского кода, кодированная последовательность битов длиной 128 получается посредством кодирования, и кодированная последовательность битов повторяется, чтобы получить длину целевого кода, равной 576. Параметры в вышеупомянутых трех заданных условиях могут быть гибко установлены со ссылкой на варианты осуществления, представленные в настоящем изобретении.

Блоки и способы процессов в примерах, описанных в вариантах осуществления настоящего изобретения, могут быть реализованы посредством электронного аппаратного обеспечения или комбинации компьютерного программного обеспечения и электронного аппаратного обеспечения. Выполнение функций аппаратным или программным обеспечением зависит от конкретных приложений и условий проектирования технических решений. Специалист в данной области может использовать разные способы для реализации описанных функций для каждого конкретного применения.

В нескольких вариантах осуществления, представленных в настоящем изобретении, следует понимать, что раскрытые устройство и способ могут быть реализованы другими способами. Например, описанные варианты осуществления устройства являются просто примерами. Например, разделение на блоки является просто логическим разделением функций и может быть другим разделением во время фактической реализации. Например, множество блоков или компонентов может быть объединено или интегрировано в другую систему, или некоторые этапы могут игнорироваться или не выполняться. Кроме того, соединения или прямые соединения, или коммуникационные соединения между устройствами могут быть реализованы в электрической, механической или другой форме.

Блоки, описанные как отдельные части, могут быть или не быть физически отдельными, могут располагаться в одной позиции или могут быть распределены по множеству сетевых блоков.

Кроме того, функциональные блоки в вариантах осуществления настоящего изобретения могут быть интегрированы в один блок обработки, или каждый из блоков может существовать физически отдельно, или два или более блоков могут быть интегрированы в один блок.