Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания быстродействующих, специализированных и высокопроизводительных цифровых процессоров, выполняющих поисковые операции и функции замены в обрабатываемых словах.

Известно “Устройство поиска произвольных вхождений” (патент № 2202823 от 20.04.2003 г.), определяющая произвольные вхождения в обрабатываемых словах.

Известно “Поисковое устройство произвольных вхождений” (патент № 2209465 от 27.07.2003 г.), осуществляющая поиск произвольных вхождений в обрабатываемых словах.

Известно “Устройство поиска и замены произвольных вхождений в словах текста” (патент № 2250493 20.04.2005 г.), выполняет функцию поиска и замены произвольных вхождений в словах текста.

В качестве прототипа выбрано “Устройство параллельного поиска и замены вхождений в обрабатываемых словах” (патент № 2296366 27.03.2007 г.), выполняет параллельный поиск произвольных вхождений в обработываемых словах и осуществляет функцию замены.

Недостатком является то, что устройство параллельно-последовательного поиска и замены вхождений в обрабатываемых словах выполняет поисковые операции в параллельном и последовательном режимах с помощью компараторов.

Техническая задача заключается в расширении функциональных возможностей, увеличении скорости выполнения поисковых операций, повышении надежности работы поискового устройства произвольных вхождений.

Решение задачи осуществляется тем, что устройство параллельно-последовательного поиска и замены вхождений в обрабатываемых словах, содержащее блок памяти замены, блок замены, блок хранения результата, блок управления, отличающиеся тем, что дополнительно введены: блок памяти обрабатываемых слов и вхождений, блок параллельно-последовательного поиска, причем с первого по девятый информационные выходы блока управления, на которых формируются сигналы: обнуления, синхроимпульсов, выбора кристалла, режима запись/чтения оперативных запоминающих устройств, адреса строк и столбцов оперативных запоминающих устройств, двоичных кодов символов вхлждений и обрабатываемых слов, сдвигов, выбора режимов работы регистров буферов соединены соответственно с первым по девятый информационными входами блок памяти обрабатываемых слов и вхождений, первый и второй информационные выходы блок памяти обрабатываемых слов и вхождений, на которых формируются двоичные коды символов вхождений и обрабатываемых слов соединены соответственно с первым и вторым информационными входами блока параллельно-последовательного поиска, с первого по седьмой управляющие выходы блока параллельно-последовательного поиска, на которых формируются признаки конца обрабатываемых слов и вхождений, результат сравнения символов обрабатываемых слов и вхождений, режимы работы устройства, сигнал дешифрации двоичного счетчика, определения количества сдвигов вправо регистров, формата работы устройства соединены соответственно с третьим по девятый управляющими входами блока управления, первый и второй управляющие выходы блока управления, на которых формируются признаки работы блоков параллельного и последовательного поиска вхождений в обрабатываемых словах соединены соответственно с первым и вторым управляющими входами блока параллельно-последовательного поиска, третий и четвертый информационные входы блока параллельно-последовательного поиска, на которых формируются сигналы: обнуления, управления работой логических схем, признаки работы устройства, синхронизации, сдвига, разрешения записи, тактовых и прямоугольных импульсов, выдачи информации, признаки режимами работы устройства соединены соосветственно с десятым и одиннадцатым информационными выходами блока управления, двенадцатый и тринадцатый информационные выходы блока управления, на которых формируются сигналы: обнуления, синхронизации, разрешения записи, выдачи данных регистров результата и замены соединены соответственно с третьим и четвертым информационными входами блока замены, управляющий вход блока замены на котором формируется управляющий сигнал логических схем соединен с третьим управляющим выходом блока управления, с четырнадцатого по шестнадцатый информационные выходы блока управления на которых формируются сигналы: обнуления, выбора кристалла, запись/чтения, адреса строк, столбцов и данных оперативного запоминающего устройства соединены соответственно с первым по третий информационными входами блока памяти замены, информационный выход блока памяти замены, на котором формируются двоичные коды символов замены соединен со вторым инфмационным входом блока замены, первый информационный вход блока замены, на котором формируются двоичные коды с выхода первого регистра блока регистров обрабатываемых слов соединен со вторым информационным выходом блока параллельно-последовательного поиска, первый информационный выход блока параллельно-последовательного поиска, на котором формируются адреса вхождений в обрабатыаемом слове соединен со вторым информационным входом блока хранения результата, с первого по шестой управляющие входы блока хранения результата, на которых формируются сигналы: прямоугольные импульсы, импульсы генератора, обнуления, установки в нулевое состояние, выбора кристалла, чтения/запись соединены соответственно с четвертым по девятый управляющими выходами блока управления, первый информационный вход блока хранения результата, на котором формируется результат замены в обрабатываемом слове соединен с информационным выходом блока замены, первый и второй управляющие входы “СБРОС” и “ПУСК” блока управления являются внешними входами устройства параллельно-последовательного поиска и замены вхождений в обрабатываемых словах.

БПОсВх - блок памяти обрабатываемых слов и вхождений служит для записи, хранения и выдачи обрабатываемых слов и вхождений, с которыми необходимо проводить поисковые операции.

БППП - блок параллельно-последовательного поиска служит для анализа поисковой операции, определения способа поиска вхождений в обрабатываемом слове, а так же определения адреса вхождения.

БППА - блок параллельного поиска служит для поиска вхождений в обрабатываемом слове в параллельном режиме.

БППО - блок последовательного поиска служит для поиска вхождений в обрабатываемом слове в последовательном режиме.

БПЗМ - блок памяти замены служит для записи, хранения и выдачи замены в регистры блока регистров результата замены.

БЗАМ - блок замены служит для выполнения операций: 1) записи символа обрабатываемого слова в случае отрицательного сравнения, 2) записи замены в регистры блока регистров результата замены, если произошло положительное сравнение в блоке компараторе.

БХР - блок хранения результатов служит для записи и хранения в нем адресов вхождений в обрабатываемых словах и результатов выполнения операций замены.

БУ - блок управления.

Процессы поиска вхождений в обрабатываемом слове можно выполнить как в последовательном, так и в параллельном режимах. Формировать новое слово возможно с помощью операций замены, а так же левой или правой конкатенаций [1].

При выполнении операций поиска вхождений в обрабатываемом слове необходимо достигнуть высокой скорости поиска и замены.

Поиск вхождений в обрабатываемом слове может быть осуществлен в двух форматах работы устройства:

1) Определение вхождений, имеющих общие части, это означает что предыдущие вхождение и последующие имеют общую часть, состоящую из одной буквы или цепочки символов.

2) Определение вхождения без общих частей, это означает, что предыдущие вхождение и последующие не имеют общих частей. Такая процедура поиска, которая удовлетворяет поставленным требованиям, называется корректной.

В устройстве применяются оперативные запоминающие устройства, в которых хранится информация [2]. Вхождение, обрабатываемое слово и замена переписываются из памяти в сдвигающие регистры. Процессы записи и считывание информации в регистры могут быть следующие: параллельно-последовательный ввод - параллельно-последовательный вывод, используется в регистре для хранения вхождений, последовательный ввод - последовательный вывод, используется для в регистре для хранения замены, а также параллельно-последовательный ввод - параллельно-последовательный вывод, используется для хранения в регистре обрабатываемого слова [3]. В устройстве применяются элементы нейронной и пороговой логики [4].

В предлагаемом устройстве поиск вхождения в обрабатываемом слове выполняется в параллельном режиме. Все символы вхождения параллельно поступают на первые входы компаратора. На вторые входы, также параллельно, узла сравнения поступают символы обрабатываемого слова. В устройстве параллельного поиска и замены применены три регистра - регистр вхождения, регистр обрабатываемого слова и регистр замены. Длина регистров, в которых хранятся вхождение и обрабатываемое слово, а также количество компараторов, в которых происходит сравнение символов, одинаковая. Если произошло положительное сравнение, то на выходе компаратора формируется единичное значение. В этом случае в обрабатываемом слове найдено вхождение. В случае работы устройства в режиме поиска определяется адрес вхождения. Если устройство работает в режиме поиска и замены, то в регистр замены записывается цепочка символов - замена. Обрабатываемое слово не изменяется в процессе замены. Если произошло отрицательное сравнение, то необходимо сдвинуть обрабатываемое слово на один или несколько разрядов влево и сравнить следующую серию символов, равную по количеству символам вхождения. Процесс сдвига обрабатываемого слова в регистре выполняется до определения признака конца обрабатываемого слова. Символ в результате левого сдвига записывается в регистр замены. В регистр замены записываются символы обрабатываемого слова в результате операции левого сдвига регистра или буквы замены в режиме работы устройства поиска и замены. В устройстве осуществляются операции левой и правой конкатенаций. Если длина обрабатываемого слова больше длины вхождения по количеству сиволов, то необхожимо выключить в устройстве сранения - компараторы от шины к которой подключены не рабочие схемы. «Выключено» - состояние выхода цифровой микросхемы при котором он «отключается» от сигнальной шины. В устройстве применены логические микросхемы с высокоимпедансном логическом состоянии, при котором микросхемы обладают высоким сопротивлением (импедансом), то есть фактически отключены от не рабочих схем устройства. Сравниваются символы вхождений и обрабатываемых слов равной длины. Остальные логические элементы - не рабочие в устройстве выключены от поиска.

Последовательный поиск вхождений в обрабатываемом слове выполняется следующим образом. В регистре слов записано обрабатываемое слово. В регистре вхождений записывается вхождение - цепочка символов. Задача устройства заключается в определении вхождения в обрабатываемом слове. Если вхождение найдено, то ее адрес записывается в память устройства. Если вхождение не найдено, то в регистр обрабатываемого слова записывается новое слово для проведения поисковой операции. Сравнение в компараторе символов происходит по-буквенно. В начале работы сигналом режима работы из блока управления устанавливается режим функционирования поискового устройства. На вход компаратора поступают по одной букве из регистра обрабатываемого слова и из регистра вхождения. Если результат сравнения положительный, то происходит сдвиг влево на один разряд информации в обоих регистрах и на вход компаратора поступают очередные символы из регистров. Возможно возникнет ситуация когда положительное сравнение произойдет на первой букве. на второй, на третьей и т.д., но на k букве результат сравнения будет отрицательным и при этом конца слово-образца не будет обнаружено. Двоично-десятичные счетчики устройства подсчитывают количество положительных сравнений. Предположим их произошло k совпадений, а на k+1 получен отрицательный результат. В этом случае осуществляется сдвиг вправо на на k-1 разрядов регистра в котором хранится обрабатываемое слово. Происходит "вычеркивание" первой буквы из серии где произошли положительные сравнения. Дальнейшее сравнение будет происходить уже начиная со второй буквы обрабатываемого слова и с первой буквой вхождения. Вхождение будет переписано заново из памяти вхождений. Процедуры сдвига возможны при применение реверсивных регистров. которые осуществляют сдвиг информации как влево, так и вправо. Поисковое устройство работает в двух режимах.

На фиг. 1 изображена структурная схема устройства параллельно-последовательного поиска и замены вхождений в обрабатываемых словах.

На фиг. 2 представлены варианты технической реализации блоков памяти: вхождений, обрабатываемых слов и замены.

На фиг. 3 изображена функциональная схема блока регистров вхождений и комбанационная схема определения варианта поиска вхождений.

На фиг. 4 изображена функциональная схема блока регистров обрабатываемых слов.

На фиг. 5 показаны варианты технической реализации блоков последовательного и параллельного поиска вхождений в обрабатываемых словах.

На фиг. 6 показана функциональная схема блока параллельно-последовательных поисковых операций, схем компарации и логических схем.

На фиг. 7 изображены функциональные схемы: регистра вхождений, регистра обрабатываемых слов, компарации и логические схемы.

На фиг. 8 представлены функциональные схемы: регистра вхождений, регистра обрабатываемых слов, компарации и логическая схема.

На фиг.9 показаны комбинационные схемы: формирования адреса и варианта определения параллельных поисковых операций.

На фиг. 10 показана функциональная схема блока последовательного поиска.

На фиг. 11 показана функциональная схема блока регистров замены, блока регистров результата замены, логические схемы.

На фиг. 12 изображена функциональная схема блока регистров замены.

На фиг. 13 показана функциональная схема блока регистров результата замены.

На фиг.14 показана функциональная схема блока хранения результата.

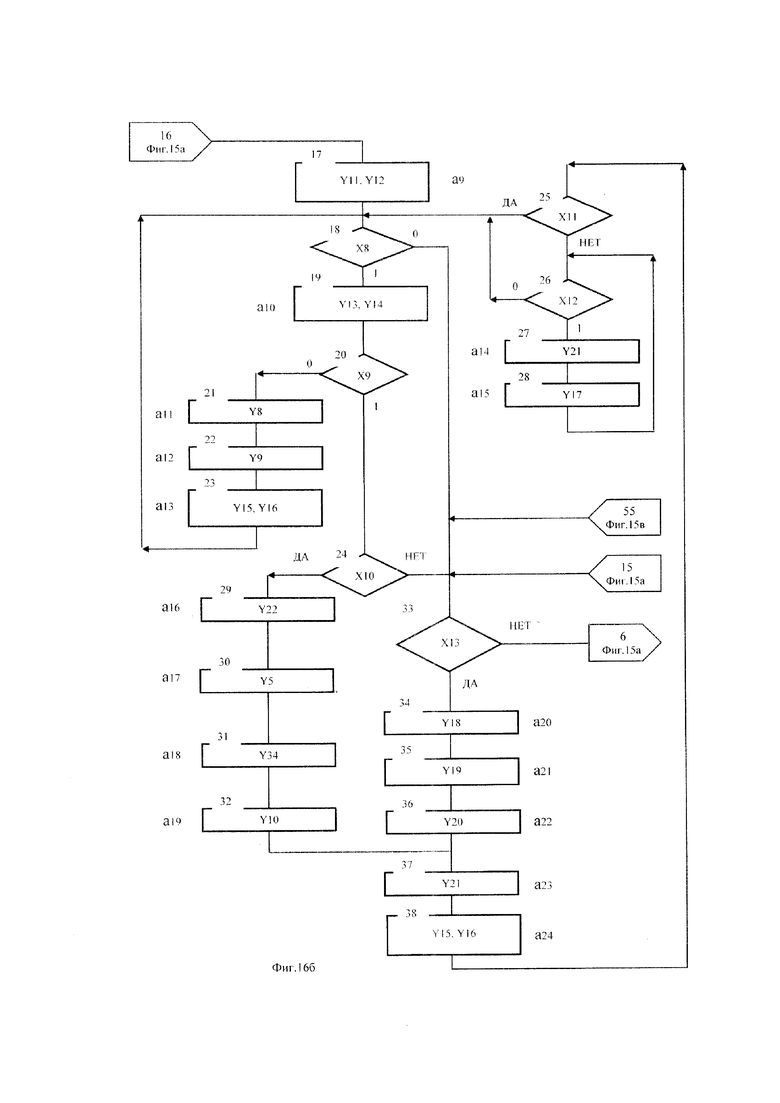

На фиг. 15а, 15б, 15в - содержательная ГСА работы устройства.

На фиг. 16а, 16б, 16в - размеченная ГСА работы устройства.

Устройство параллельно-последовательного поиска и замены вхождений в обрабатываемых словах (фиг.1) содержит блок 1 памяти обрабатываемых слов и блок памяти вхождений, блок 2 параллельно-последовательный поиск, блок 3 памяти замены, блок 4 замены, блок 5 хранения результата, блок 6 управления.

Для описания алгоритма работы блока 6 управления используются следующие идентификаторы.

1. 1. УВХ - сигналы управления оперативным запоминающим устройством блока памяти вхождений: обнуление, выбор кристалла, режим записи/считывания.

2. АдВХ - адреса столбцов и строк оперативного запоминающего устройства блока памяти вхождений.

3. ДВХ - данные, записанные в оперативное запоминающее устройство блока памяти вхождений.

4. УПРВ - управляющие сигналы: обнуления, синхроимпульсы, сигналы, формирующие режимы работы регистров блока памяти вхождений.

5. ВХ - выходные данные из оперативного запоминающего устройства блока памяти вхождений.

6. УОС - сигналы управления оперативным запоминающим устройством блока памяти обрабатываемых слов: обнуление, выбор кристалла, режим записи/считывания.

7. АдОС - адреса столбцов и строк оперативного запоминающего устройства блока памяти обрабатываемых слов.

8. ДОС - данные, записанные в оперативное запоминающее устройство блока памяти обрабатываемых слов.

9. УПРС - управляющие сигналы: обнуления, синхроимпульсы, сигналы, формирующие режимы работы регистров, блока регистров обрабатываемых слов.

10. ОС - выходные данные из оперативного запоминающего устройства блока памяти обрабатываемых слов.

11. УЗМ - сигналы управления оперативным запоминающим устройством блока памяти замен: обнуление, выбор кристалла, режим записи/считывания.

12. АдЗМ - адреса столбцов и строк оперативного запоминающего устройства блока памяти замен.

13. ДЗМ - данные, записанные в оперативное запоминающее устройство блока памяти замен.

14. ППО - признак работы последовательного поиска двоичных кодов символов вхождения в обрабатываемых словах.

15. ППА - признак работы параллельного поиска двоичных кодов символов вхождения в обрабатываемых словах.

16. РСР1 - выходной двоичный сигнал блока параллельно-последовательного поиска, который определяет результат сравнения двоичных кодов символов вхождения и обрабатываемого слова первых регистров блока.

17. СИД1 - сигнал высокоимпедансного состояния логической схемы первого регистра блока регистров вхождений.

18. ОС1 - входные данные первого регистра блока регистров обрабатываемых слов.

19. УПРВ1 - управляющие сигналы первого регистра: обнуления, синхроимпульсы, сигналы, формирующие режимы работы регистров блока регистров вхождений.

20. УПРС1 - управляющие сигналы первого регистра: обнуления, синхроимпульсы, сигналы, формирующие режимы работы регистров, блока регистров обрабатываемых слов.

21. ПСПР - команда формата работы устройства последовательном или параллельном режимах поиска вхождений в обрабатываемых словах.

22. ДОС - двоичные коды символов обрабатываемых слов.

23. СППА - управляющие сигналы: обнуления, управления работой логических схем, режима работы блока параллельного поиска вхождений в обработываемых словах устройства.

24. СППО - управляющие сигналы работы блока последовательного поиска вхождений в обработываемых словах устройства.

25. СО1 - сигнал сдвига влево на один разряд двоичного кода первого регистра в блоке регистров обрабатываемых слов.

26. ВХ1 - входные данные первого регистра блока регистров вхождений.

27. СИМ1 - выходной информационный сигнал первого регистра блока регистров вхождений.

28. СИМ2 - выходной информационный сигнал второго регистра блока регистров вхождений.

29. ЗМ - выходные данные из оперативного запоминающего устройства блока памяти замен.

30. СВ - сигнал сдвига влево на один разряд двоичного кода в блоке регистров вхождений.

31. СО - сигнал сдвига влево на один разряд двоичного кода в блоке регистров обрабатываемых слов.

32. ОСБ - сигнал сдвига влево на один разряд двоичного кода регистра буфера в блоке регистров обрабатываемых слов.

33. УПБ - управляющие сигналы: обнуления, синхроимпульсы, сдвигов, сигналы, формирующие режимы работы регистров буферов блока регистров обрабатываемых слов.

34. РСР - выходной двоичный сигнал блока параллельно-последовательного поиска, который определяет результат сравнения символов вхождения и обрабатываемого слова.

35. ОТИ - сигнал управления логической схемой И для подсчета сигналов сдвига при определении адресов вхождений в обрабатываемом слове.

36. ПОЧ - признак работы устройства с общими частями, определяющий режим работы устройства: 1) поиск вхождений с общими частями, 2) поиск вхождений без общих частей в обрабатываемом слове.

37. ОБС - информационный сигнал установки в нулевое состояние двоичных счетчиков блока параллельно-последовательного поиска.

38. АВПР - выходной информационный сигнал блока параллельно-последовательного поиска, определяющий адреса вхождений в обрабатываемом слове.

39. БОЧ - двоичный сигнал блока параллельно-последовательного поиска, определяющий режим работы устройства поиска вхождений в обрабатываемом слове без общих частей.

40. СИН - команда синхронизации, поступающая на вход двоичного счетчика Сч1 блока параллельно-последовательного поиска.

41. СВП - команда, определяющая количество сдвигов вправо регистров блока регистров обрабатываемых слов.

42. ДШЕ - команда, определяющая двоичный код 0001 на выходе двоичного счетчика Сч1 блока параллельно-последовательного поиска.

43. ОБН - команда обнуления двоичного счетчика Сч1 блока параллельно-последовательного поиска.

44. СВА - команда выдачи адреса вхождения из блока параллельно-последовательного поиска в блок хранения адреса вхождений.

45. СЗЩ - команда разрешения записи в триггер Тр блока параллельно-последовательного поиска выходного сигнала компаратора.

46. СДЛ - команда управления работой электронного ключа блока параллельно-последовательного поиска.

47. СН - команда синхронизации двоичного счетчика Сч2 блока параллельно-последовательного поиска.

48. СБР - команда обнуления двоичного счетчика Сч2 блока параллельно-последовательного поиска.

49. ПИМ - прямоугольные импульсы, поступающие на информационный вход электронного ключа блока параллельно-последовательного поиска.

50. РР - команда признака режима работы устройства.

51. ПКВХ - признак конца вхождения.

52. ПРИ - прямоугольные импульсы, поступающие из бока управления на информационный вход логического элемента И блока параллельно-последовательного поиска.

53. ТАК - тактовые прямоугольные импульсы, поступающие на информационный вход логического элемента И блока параллельно-последовательного поиска.

54. СМi - входной информационный сигнал - символ вхождения блока регистров вхождений.

55. СИМi - выходной информационный сигнал блока регистров вхождений.

56. ОС1 - символ обрабатываемого слова первого регистра Рг1 блока регистров обрабатываемого слова.

57. ОСi - выходные символы обрабатываемого слова блока регистров обрабатываемого слова.

58. ПКОС - признак конца символов обрабатываемого слова.

59. УКЛ - управляющий сигнал блока управления, поступающий на управляющие входы логических схем И блока замены.

60. УЗАМ - информационный сигнал: обнуления, синхроимпульсы, разрешение записи и выдачи информации, поступающий на управляющие входы блока регистров замены.

61. УРЗМ - информационный сигнал: обнуления, синхроимпульсы, разрешение записи и выдачи информации, поступающий на управляющие входы блока регистров результата замены.

62. ОСЗМ - информационный сигнал символов обрабатываемого слова или замены, поступающий на информационный вход блока регистров результата замены.

63. РЗ - выходной информационный сигнал результат замены, поступающий с выхода блока регистров результата замены.

64. АДВ - информационный сигнал адреса вхождения в обрабатываемом слове, поступающий на вход блока хранения результата.

65. УЗАМ - информационный сигнал блока управления: обнуление, синхроимпульсы, разрешение записи и выдачи информации, проступающий на управляющие входы регистров блока регистров замены.

66. РЕЗ - информационный сигнал результат замены или адрес вхождения в обрабатываемом слове, поступающий на информационный вход оперативного запоминающего устройства блока хранения результата.

67. АД СТЛ - адреса столбцов оперативного запоминающего устройства для записи результата замены или адреса вхождения в блок хранения результата.

68. АД СТР - адреса строк оперативного запоминающего устройства для записи результата замены или адреса вхождения в блок хранения результата.

69. ГИ - генератор импульсов, поступающий из блока управления на суммирующий вход (+) двоичного счетчика Сч1 блока хранения результата.

70. ТИ - тактовые импульсы, поступающие из блока управления на суммирующий вход (+) двоичного счетчика Сч2 блока хранения результата.

71. ОБ - команда обнуления двоичного счетчика Сч1 блока хранения результата.

72. УС “0” - команда обнуления двоичного счетчика Сч2 блока хранения результата.

73. ВК - команда выбора кристалла оперативного запоминающего устройства ОЗУ блока хранения результата.

74. Сч/Зп - команда считывания/записи оперативного запоминающего устройства ОЗУ блока хранения результата.

75. РЕПЗ - выходные данные оперативного запоминающего устройства блока хранения результата - результаты замен или адреса вхождений в обрабатываемом слове.

76. СБРОС - сигнал сброса - обнуление элементов памяти устройства выполнения параллельного поиска и замены.

77. ПУСК - сигнал начало работы устройства.

Работа блока упpавления устройства параллельно-последовательного поиска и замены вхождений в обрабатываемых словах.

Содеpжательная ГСА упpавления пpиведена на фиг. 15а, фиг. 15б, 15в и отpажает pаботу блока упpавления (фиг. 1).

В блоке 2 алгоритма по сигналу "СБРОС" пpоисходит установка в нуль всех элементов памяти устpойства (фиг. 1).

В блоке 3 алгоритма по команде "СБРОС:=1" происходит установка в единичное состояние сигнала СБРОС.

В блоке 4 алгоритма анализируется признак работы устройства “ПУСК”. По выходу блока “единица” начинается работа устройства параллельно-последовательного поиска и замены вхождений в обрабатываемых словах.

В блоке 5 алгоритма по команде ПВХ:=ДВХ на информационный вход оперативного запоминающего устройства блока памяти вхождений поступают данные вхождений, представляющие собой цепочки символов, которые необходимо обнаружить в обрабатываемых словах. По команде ПОС:=ДОС в оперативное запоминающее устройство записываются данные обрабатываемых слов. По команде ПЗМ:=ДЗМ в оперативное запоминающее устройство записываются данные замен. Блок 5 это операция загрузки вхождений, обрабатываемых слов и замен в оперативные запоминающие устройства блока памяти обрабатываемых слов и вхождений: памяти вхождений, памяти обрабатываемых слов и памяти замены (фиг. 1,2).

В блоке 6 алгоритма анализируется признак работы устройства поиска и замены РПЗ. По выходу НЕТ осуществляется переход на 61 конечный блок алгоритма работы устройства. По выходу ДА выполняется переход на блок 7 алгоритма.

В блоке 7 алгоритма анализируется признак левой конкатенации ЛЕК, операция присоединения вхождения к обрабатываемому слову слева. Такая операция имеет вид {S}P, где S - вхождение, а Р - обрабатываемое слово. По выходу НЕТ осуществляется переход на блок 11 алгоритма. По выходу ДА выполняется переход на блок 8 алгоритма.

Блоки 7, 8, 9, 10, и 15 организуют цикл в котором выполняется операция левой конкатенации. Цикл позволят получить одно или неоднократное присоединение вхождения к обрабатываемому слову слева, это можно записать как {{S1} … {Sn}}P.

В блоке 8 алгоритма по команде УКЛ:=1 на управляющий вход блока замены БЗАМ из блока управления подается управляющий сигнал УКЛ равный единице (фиг. 11). В результате этой операции данные блока регистра замены через открытые электронные ключи с прямыми управляющими входами и логических схем ИЛИ поступают на вход блока регистра результата замены. При этом осуществляется операция левой конкатенации.

В блоке 9 алгоритма по команде ОСЗМ:=ЗМ на вход данных блока регистров результата замены поступают данные из блока регистров замены.

В блоке 10 алгоритма по команде БРгРЗ:=ЗМ в блок регистров результата замены записывается вхождение из блока регистров замены (фиг. 11).

В блоке 11 алгоритма анализируется признак правой конкатенации ПРК, операция присоединения вхождения к обрабатываемому слову справа. Такая операция имеет вид P{S}, где, Р - обрабатываемое слово а S - вхождение. По выходу НЕТ осуществляется переход на блок 16 алгоритма. По выходу ДА выполняется переход на блок 12 алгоритма.

Блоки 11, 12, 13, 14, и 15 организуют цикл в результате, которого выполняется операция правой конкатенации. Цикл позволят получить одно или неоднократное присоединение к обрабатываемому слову вхождение справа, это можно записать как P{{S1} … {Sm}}.

В блоке 12 алгоритма по команде УКЛ:=0 на управляющий вход системы электронных ключей блока замены БЗАМ из блока управления подается управляющий сигнал УКЛ равный нулю (фиг. 11). В результате этой операции данные блока регистров обрабатываемого слова через открытые электронные ключи с инверсными управляющими входами и логических схем ИЛИ поступают на вход блока регистра результата замены. При этом осуществляется операция записи символов обрабатываемого слова в блок регистров результата замены.

В блоке 13 алгоритма по команде ОСЗМ:=ОС на вход данных блока регистров результата замены поступают данные из блока регистров обрабатываемого слова (фиг. 11).

В блоке 14 алгоритма по команде БРгРЗ:=ОСЗМ в блок регистров результата замены записываются символы обрабатываемого слова из блока регистров обрабатываемого слова (фиг. 11).

В блоке 15 алгоритма анализируется признак присоединения - конкатенация КОН левая или правая. По выходу ДА блока осуществляется переход на блок 7 алгоритма, в этом случае процесс присоединений слева или справа продолжается, в противном случае осуществляется переход на блок 16 алгоритма. По выходу НЕТ происходит переход на блок 33 алгоритма для записи результата конкатенаций в оперативное запоминающее устройство блока хранения результатов.

В результате выполнения этих циклов возможны следующие композиции вхождения и обрабатываемого слова: {S}P - одна левая конкатенация, {{S1} … {Sn}}P - n левых конкатенаций, а также P{S} - правая конкатенация и P{{S1} … {Sm}} - m правых конкатенаций.

В блоке 16 алгоритма анализируется формат работы устройства в последовательном или параллельном ПСПР режиме происходит поиск вхождений в обрабатываемых словах. Если устройство оуществляет поиск вхождений в параллельном режиме, формат работы ПСПР равен единице, то осуществляеься переход на блок 17 алгоритма. Иначе при последовательном поиске вхождений осуществляется переход на блок 39 алгоритма (фиг.5).

В блоке 17 алгоритма по команде БРгВХ:=ВХ на информационные входы регистров блока регистров вхождения в параллельном режиме из блока памяти вхождений поступают символы вхождения ВХ (фиг. 2, 7, 8). По команде БРгОС:=ОС на информационные входы регистров блока регистров обрабатываемого слова в последовательном режиме - посимвольно из блока памяти обрабатываемых слов поступают символы обрабатываемого слова для проведения поисковых операций (фиг. 7, 4).

В блоке 18 алгоритма анализируется признак конца обрабатываемого слова ПКОС. В случае управляющего сигнала ПКОС равного нулевому значению, это означает, что все символы обрабатываемого слова просмотрены и регистр обрабатываемого слова пуст (фиг. 4). В этом случае осуществляется переход на блок 33 алгоритма. Если сигнал ПКОС равен единичному значению, то поиск в обрабатываемом слове продолжается (фиг.4). В этом случае осуществляется переход на блок 19 алгоритма.

В 19 алгоритма по команде КОМ:=ВХ на первые входы компаратора поступают символы вхождения ВХ. По команде КОМ:=ОС на вторые входы компаратора поступают символы обрабатываемого слова ОС. В компараторе выполняется операция сравнение символов вхождения и обрабатываемого слова. Операция сравнения в блоке параллельно-последовательного поиска осуществляется в параллельном режиме (фиг. 6).

В блоке 20 алгоритма анализируется признак результата сравнения на равенство РСР символов вхождения и обрабатываемого слова. Если сравнение произошло положительно, сигнал при этом РСР равен единичному значению, то осуществляется переход на блок 24 алгоритма. В случае отрицательного сравнения на равенство входных величин, сигнал РСР равен нулевому значению, при этом выполняется переход на блок 21 алгоритма.

В блоках 21, 22, 23 выполняется операция записи символа обрабатываемого слова в регистр блока регистров результата замены, если произошло отрицательное сравнение символов обрабатываемого слова и вхождения (фиг. 11).

В блоке 21 алгоритма по команде УКЛ:=0 управляющий сигнал из блока управления поступает на входы электронных ключей с инверсными управляющими входами, тем самым, отпирая электронные ключи. В результате этого на входы логических схем ИЛИ поступает символ обрабатываемого слова, который запишется в регистр блока регистров результата замены. Этот характеризуется отрицательным сравнением символов вхождения и обрабатываемого слова (фиг. 11).

В блоке 22 алгоритма по команде ОСЗМ:=ОС на информационные входы регистра блока регистров результата замены поступает символ обрабатываемого слова ОС для дальнейшей записи его в регистр блока (фиг. 11).

В блоке 23 алгоритма по команде ОТИ:=0 из блока управления поступает управляющий сигнал ОТИ равный нулевому значению. Сигнал поступает на инверсный вход логических схем И - электронного ключа. В результате этого электронный ключ будет открыт, через него и схему ИЛИ сигнал сдвига влево поступит на суммирующий вход двоичного сумматора СчА. По команде СчА:=СО на суммирующий вход счетчика поступает сигнал сдвига влево СО для подсчета количества сигналов сдвига влево обрабатываемого слова для формирования адреса вхождения в обрабатываемом слове (фиг. 9).

По выходу из блока 23 алгоритма осуществляется переход на блок 18 алгоритма для определения признака конца обрабатываемого слова ПКОС, затем для выполнения операции сравнения символов вхождения и сдвинутым влево на один разряд обрабатываемом словом. В результате образуется цикл, в котором будут просмотрены все символы обрабатываемого слова. Циклическая операция будут продолжаться до обнаружения признака конца обрабатываемого слова ПКОС.

В блоке 24 алгоритма анализируется признак операций ПЗ: 1) поиск, 2) поиска и замены. Если устройство работает в режиме только поиска - выход НЕТ, то в этом случае осуществляется переход на блок 33 алгоритма. В случае работы в режиме поиска и замена - выход ДА алгоритма, то выполняется переход на блок 29 алгоритма.

В блоках алгоритма 29, 30, 31, и 32 определяется способ обработки информации: 1) поиск, 2) поиск и замена.

Существуют два вида комбинаций вхождений в обрабатываемом слове: 1) с общими частями символов вхождений, 2) без общих частей символов вхождений. Первый вид это когда между предыдущим вхождением в обрабатываемом слове и последующим есть общие части - символы. В этом случае поиск вхождения в обрабатываемом слове осуществляется сразу же на следующем сдвиге обрабатываемого слова, после положительного сравнения символов вхождения и обрабатываемого слова. Второй вид это когда сравнение символов осуществляется через n сигналов сдвига влево обрабатываемого слова, где n - количество символов вхождения.

В блоке 25 анализируется признак работы устройства ПОЧ с общими частями - выход ДА и без общих частей - выход НЕТ. В случае выбора режима работы устройства с общими частями осуществляется переход на блок 18 алгоритма. Если устройство работает в режиме поиска без общих частей, то выполняется переход на блок 26 алгоритма.

Блоки 26, 27 и 28 формируют цикл, в котором выполняется сдвиг влево обрабатываемого слова на один разряд до тех пор, пока признак работы устройства без общих частей БОЧ не будет равен нулевому значению.

В блоке 26 алгоритма анализируется двоичный сигнал - признак поиска вхождений без общих частей БОЧ (фиг. 9). Если сигнал равен нулевому значению, то осуществляется переход на блок 18 алгоритма. В случае равенства сигнала единичному значению, то выполняется переход на блок 27 алгоритма.

В блоке 27 алгоритма по команде БРгОС:=СО на управляющие входы регистров блока регистров обрабатываемого слова поступают сигналы сдвига влево на один разряд для выполнения операции сдвига данных обрабатываемого слова влево (фиг. 4, 7).

В блоке 28 алгоритма по команде по команде СчВ:=СО на вычитающий вход двоичного счетчика СчВ поступают сигналы сдвига влево регистров блока регистров обрабатываемого слова. В счетчике СчВ выполняется операция вычитание. От количества символов вхождения вычитается поступившее на вычитающий вход число сигналов сдвига влево на один разряд обрабатываемого слова. Предварительно при загрузке символов вхождения в регистры блока регистров вхождения в суммирующий двоичный счетчик СчС будет записана информация в двоичном коде, соответствующая количеству символов вхождения. Будет проведена предварительная установка вычитающего счетчика СчВ. Если результата на выходе счетчика равен нулю, то это означает обрабатываемое слово сдвинуто на определенное количество разрядов влево, равное количеству символов вхождения (фиг. 9).

Блоки 29, 30, 31, 32 алгоритма выполняют операцию записи замены в регистры блока регистров результата замены. Если устройство работает в режиме поиска и замены и при этом обнаружено вхождение в обрабатываемом слове, то в регистры блока регистров результата замены записывается цепочка символов замены (фиг. 11).

В блоке 29 алгоритма по команде БРгЗМ:=ЗМ в блок регистров замены записывается замена из блока памяти замены (фиг. 11).

В блоке 30 по команде УКЛ:=1 на управляющий вход блока замены БЗАМ из блока управления подается управляющий сигнал УКЛ равный единице. По выполнению этой операции данные блока регистра замены через открытые электронные ключи с прямыми управляющими входами и логических схем ИЛИ поступают на вход блока регистров результата замены (фиг. 11).

В блоке 31 алгоритма по команде ОСЗМ:=ЗМ на информационный вход данных блока регистров результата замены поступают данные из блока регистров замены (фиг. 11).

В блоке 32 алгоритма по команде БРгРЗ:=ОСЗМ выполняется запись замены в регистры блока регистров результата замены (фиг. 11).

В блоке 33 алгоритма анализируется выполнения устройством операций: 1) поиска, 2) поиска и замены, 3) конкатенаций левой или правой (П) или (ПЗ) или (КОН). Результат выполнение функций определяется с помощью логической операции ИЛИ. Если не выполнялось ни одной из этих операции устройством - выход НЕТ блока, то осуществляется переход на блок 6 алгоритма. В случае выполнения хотя бы одной из этих операций - выход ДА блока, то осуществляется переход на блок 34 алгоритма.

В блоке 34 алгоритма по команде АВД:=СчА определяется позиция адреса вхождения в обрабатываемом слове, которая вычисляется с помощью двоичного счетчика СчА блока параллельного поиска. Адрес вхождения формируется по количеству сигналов сдвига влево, поступивших на суммирующий вход счетчика СчА, вначале вхождения, затем обрабатываемого слова (фиг.9).

В блоке 35 алгоритма по команде РЕЗ:=(АДВ) или (РЗ) определяется результат РЕЗ с помощью логической операции ИЛИ. Результат поиска - местоположение вхождения, или в результате поиска и замены или после неоднократных замен, полученное новое слово из блока регистров результата замены, поступает на информационный вход оперативного запоминающего устройства блока хранения результата (фиг.11, 14).

В блоке 36 алгоритма по команде ОЗУ:=РЕЗ на входные информационные входы оперативного запоминающего устройства блока хранения результата поступает результат РЕЗ - выполнение операций: поиска или поиска и замены или конкатенаций (фиг.14).

В блоке 37 алгоритма по команде БРгОС:=СО на управляющий вход регистров блока регистров обрабатываемого слова из блока управления поступает сигнал сдвига СО. Обрабатываемое слово при этом сдвигается на один разряд влево для дальнейшего выполнения поисковой операции (фиг.4).

В блоке 38 алгоритма по команде ОТИ:=0 из блока управления поступает управляющий сигнал ОТИ равный нулю. Сигнал поступает на инверсный вход схемы И - электронного ключа, который открывается, через него и логическую схему ИЛИ сигнал сдвига влево поступит на суммирующий вход двоичного сумматора СчА (фиг. 9). По команде СчА:=СО на суммирующий вход счетчика поступает сигнал сдвига влево СО для подсчета количества сигналов сдвига влево обрабатываемого слова для формирования адреса вхождения в обрабатываемом слове (фиг. 9).

По выходу из блока 38 алгоритма осуществляется переход на блок 25 алгоритма для анализа способа поиска вхождений в обрабатываемом слове: поиск с общими частями или без общих частей.

В блоке 39 алгоритма по команде По команде РгОс1:=ОС1 на информационные входы регистров блока регистров обрабатываемого слова в последовательном режиме - посимвольно из блока памяти обрабатываемых слов поступают символы обрабатываемого слова для проведения поисковых операций (фиг. 4, 7). По команде РгВх1:=Вх1 на информационные входы регистров блока регистров вхождения в в последовательном режиме - посимвольно из блока памяти вхождений поступают символы вхождения Вх1 (фиг. 2, 7, 8).

В блоке 40 алгоритма происходит анализ сигнала сравнения РСР, поступившего с выхода компаратора КОМ DD39 (фиг.6). Если сигнал сравнения равен единице РСР=1, то это оэначает, что произошло совпадение буквы вхождения с буквой слова. В этом случае осуществляется переход на блок 51 алгоритма. Если сигнал сравнения равен нулю РСР=0, то совпадения символов не произошло, в этом случае осуществляется переход на блок 41 алгоритма.

В блоке 41 алгоритма анализируется состояние двоичного триггера ТР DD70 (фиг 10). Если триггер находится в нулевом состоянии ТР=0, то это означает, что совпадения символов вхождения и обрабатываемого слова не произошло, в этом случае формируется сигнал сдвига влево на один разряд в регистре блока обрабатываемых слов (фиг.4). Если триггер находится в единичном состоянии ТР=1, то это означает, что совпадения символов вхождения и обрабатываемого слова произошло, то осуществляется переход на блок 42 алгоритма.

В блоке 42 алгоритма по команде РгБФ:=БРгОС в регистр буфера блока регистров обрабатываемых слов записывается символ обрабатываемого слова с выхода регистра блока (фиг.4).

В блоке 43 анализируется состояние двоичного счетчика Сч1 DD74 блока последовательного поиска. Если состояние счетчика СЧ1 равно единице - выход ДА, то происходит переход на блок 46 алгоритма. Если состояние счетчика не равно единице - выход НЕТ, то осуществляется переход на блок 44 алгоритма.

В блоке 44 алгоритма выполняется подача прямоугольных импульсов ПРИ из блока 6 управления на вычитающий вход двоичного счетчика СЧ1 DD74 блока последовательного поиска до получения единичного значения (фиг. 10).

В блоке 45 алгоритма по команде БРгСО:=РгБФ в регистр обрабатываемого слова будут переписаны символы из регистра буфера РгБФ (фиг.4). По этой команде выполняется запись информации из регистра буфера в регистр блока регистров обрабатываемого слова (фиг.4).

Блоки 43, 44, 45 алгоритма формируют цикл, в котором из регистра буфера символы обрабатываемого слова переписываются обратно в регистр обрабатываемого слова, осуществляется сдвиг вправо символов обрабатываемого слова. Выходом из цикла является условие при котором значение счетчика СЧ1 будет равно единицы. По выходу из блока осуществляется переход на блок 46 алгоритма.

В блоке 46 алгоритма по команде БРгОС:=СО на блок регистров обрабатываемого слова подается сигнал сдвига влево (фиг. 4, 7). По команде РгВХ1:=ВХ1 на вход регистра вхождения подаются символы вхождения (фиг.7).

В блоке 47 алгоритма по команде СО:=0 сигнал сдвига влево подается на вход регистра обрабатываемого слова.

В блоке 48 по команде БРгОС:=ОС на регистр блок регистров обрабатываемого слова подаются символы обабатываемого слова (фиг. 4, 7). По команде РгВХ:=ВХ на вход регистра вхождения подаются символы вхождения (фиг.7).

В блоке 49 алгоритма анализируется признака конца вхождения ПКВХ (фиг. 3). Если признак конца вхождения равен единице ПКВХ=1, то в регистре вхождения обнаружен двоичный код символа, регистр не пустой. В этом случае осуществляется переход на блок 50 алгоритма. В обратном случае при равенстве признака конца вхождения нулевому значению осуществляется переход на блок 40 алгоритма.

В блоке 50 алгоритма по команде РгОС1:= ОС1 на регистр орабатываемого слова подаются символы для сравнения с символами вхождения. По команде РгВХ:=ВХ на вход регистра вхождения подаются символы вхождения (фиг.7).

В блоке 51 алгоритма по команде ТР:=1 на вход двоичного триггера подается единица, триггер устанавливается в единичное состояние. На суммирующий вход двоичного счетчика СЧ1 поступают тактовые импульсы СЧ1:=ТАК. Счетчик подсчитывает количество совпадений на входе компаратора (фиг.10).

В блоке 52 алгоритма по команде СВ:=0 сигнал сдвига влево подается на вход регистра вхождения. По команде СО:=0 сигнал сдвига влево подаются на вход регистра обрабатываемого слова.

В блоке 53 по команде РгБФ:=БРгОС на вход регистра буфера поступают символы обрабатываемого слова для сравнения очередных символов вхождения и обрабатываемого слова (фиг. 4).

В блоке 54 алгоритма анализируется признака конца вхождения ПКВХ (фиг. 3). Если признак конца вхождения равен единице ПКВХ=1, то в регистре вхождения обнаружен двоичный код символа, регистр не пустой. В этом случае осуществляется переход на блок 55 алгоритма. В обратном случае при равенстве признака конца вхождения нулевому значению, регистр пустой, осуществляется переход на блок 40 алгоритма.

В блоке 55 алгоритма анализируется признак операций ПЗ: 1) поиск, 2) поиска и замены. Если устройство работает в режиме только поиска - выход НЕТ, то в этом случае осуществляется переход на блок 33 алгоритма. В случае работы в режиме поиска и замена - выход ДА алгоритма, то выполняется переход на блок 56 алгоритма.

В блоке 56 алгоритма по команде БРгЗМ:=ЗМ в блок регистров замены записывается замена из блока памяти замены (фиг. 11).

В блоке 57 по команде УКЛ:=1 на управляющий вход блока замены БЗАМ из блока управления подается управляющий сигнал УКЛ равный единице. По выполнению этой операции данные блока регистра замены через открытые электронные ключи с прямыми управляющими входами и логических схем ИЛИ поступают на вход блока регистров результата замены (фиг. 11).

В блоке 58 алгоритма по команде ОСЗМ:=ЗМ на информационный вход данных блока регистров результата замены поступают данные из блока регистров замены (фиг. 11).

В блоке 59 алгоритма по команде БРгРЗ:=ОСЗМ выполняется запись замены в регистры блока регистров результата замены (фиг. 11).

В блок 60 алгоритма по команде БРгОС:=СО на блок регистров обрабатываемого слова подается сигнал сдвига влево (фиг. 4, 7). По команде РгВХ1:=ВХ1 на вход регистра вхождения подаются символы вхождения (фиг.7). По выходу блока 60 осуществляется переход на блок 40 алгоритма.

Блок 61 алгоритма является конечным.

Работа устройства параллельно-последовательного поиска и замены вхождений в обрабатываемых словах заключается в следующем.

Внешние упpавляющие сигналы "СБPОС" и "ПУСК" поступают в блок 6 упpавления. В блок памяти обрабатываемых слов в оперативное запоминающее устройство блока будут записаны обрабатываемые слова, в которыхнеобходимо обнаружить вхождения. В блок памяти вхождений в оперативное запоминающее устройство блока записываются вхождения - символы, которые нужно найти в обрабатываемом слове. Двоичные коды символов вхождений и обрабатываемых слов поступают на входы компараторов последовательно или параллельно, взависимости от формата поиска. При операциях левой или правой конкатенаций к обрабатываемому слову присоединяются слева или справа вхождения. Если устройство работает в режиме поиска вхождений в обрабатываемых словах, то при обнаружении символов, положительном сравнении компаратора, вычисляется адрес - местоположение вхождений в обрабатываемых словах. Эти адреса записывается в блок хранения результата. Если устройств работает в режиме поиска и замены, то при обнаружении вхождений в обрабатываемых словах осуществляется операция замены, которая выполняется в регистры блока результата замены.

Блок 1 памяти обрабатываемых слов и вхождений БПОсВх содержит оперативные запоминающие устройств ОЗУ DD7 и DD8 в которых записаны двоичные коды символов обрабатываемых слов и вхождений. Входные информационные входы блока УОС и УВХ состоят из управляющих сигналов: выбора кристалла микросхем и режима записи - считывания информации из ОЗУ блока. Адресными входами ОЗУ АдОС и АдВХ являются адреса столбцов и строк, по которым записываются данные в блоки памяти. Информационными данными ДОС и ДВХ являются двоичные коды символов, которые поступают на информационные входы оперативных запоминающих устройств блока памяти. По сигналам выбора кристалла и разрешения записи, а так же по адресным входам двоичные коды вхождений и обрабатываемых слов записываются в оперативные запоминающие устройства блока памяти. Входные информационные сигналы блока УПРС и УПРВ состоят из управляющих сигналов, формирующих режимы работы регистров памяти: разрешения записи, хранения и выдачи информации из регистров блока, сигнал сдвига влево информации на один разряд, синхроимпульсы, сигналы обнуления регистров. Входным информационным сигналом блока памяти слов является сигнал управление регистрами буферами УПБ, который поступает на вход блока обрабатываемых слов. Выходными информационными сигналами блока является сигналы обрабатываемые слова ОС и вхождения ВХ, которые поступают на вход блока параллельно-последовательного поиска (фиг. 1, 2, 6).

Блок 8 регистров вхождений БРгВХ содержит n универсальных восьмиразрядных регистров сдвига РгВх1, …, РгВхm, выполненных на элементах DD10, DD11 (фиг. 3). Регистры блока работают в режимах: параллельного ввода, параллельного вывода, хранения, установки нулей (сброс). Режимы работы регистров задаются сигналами на управляющих входах. Управляющие сигналы подаются параллельно на все регистры. Из блока 6 управления на управляющие входы регистров поступает информационный сигнал УПРВ - управление режимами работой блока регистров вхождений (фиг. 1). Входы DR и DL обеспечивают режимы сдвига информации вправо и влево соответственно. Вход СВ является тактовым, управляющие входы S1 и S0 формируют режимы работы регистров, вход R служит для установки регистров в нулевое состояние. Входным информационным сигналов блока регистров вхождений является информационный сигнал ВХ - вхождения. Этот сигнал поступает с выхода блока памяти вхождений (фиг. 1, 2). Информационные сигналы параллельно поступают на информационные входы регистров. В каждый регистр блока запишется один символ, который имеет восьмиразрядный двоичный код. На выходе регистра также будет восьмиразрядный двоичный эквивалент. Регистры имеют восьмиразрядные информационные входы СМi и восьмиразрядные выходы СИМi. Для параллельного ввода информации в регистры блока на обоих управляющих входах S1, S2 должно быть единичное значение. Информация со входов СМi будет записана в регистры и появится на выходах СИМi по перепаду 0,1 тактового импульса СВ. Когда на управляющих входах S1 и S2 установится нулевое состояние, то регистры работают в режиме хранения информации. Установка в нулевое состояние осуществляется подачей на вход R нулевого значения [3]. Перед началом работы все регистры блока регистров вхождений будут обнулены подачей нулевого уровня на входы сброса R. По приходу входного информационного сигнала ДВХ, который подается параллельно на входы регистров и состоит из информационных сигналов СМ1, …, СМn. Установкой на входах всех регистров блока, режима S1 и S2 равных единице осуществляется запись информации в регистры блока регистров вхождений. Хранение двоичных кодов в регистрах блока выполняется при режиме S1 и S2 равных нулю (фиг. 3). Входной управляющий сигнал тактовый импульс СВ поступает на входы элементов И комбинационных схем блока параллельно-последовательного поиска (фиг. 9). Выходным информационным сигналом ВХ, состоящий из информационных сигналов СИМ1, …, СИМn, блока является символ или цепочка символов вхождения, которую необходимо обнаружить в обрабатываемом слове. В структуру блока регистров вхождений входит схема определения формата поиска вхождений СхОФП, которая определяет последовательный или параллельный поиск вхождений (фиг.3). В структуру схемы входят логические элементы ИЛИ DD12 и DD13, логический элемент И DD14. На вход элемнтов ИЛИ поступают информационные сигналы СИМ1 и СИМ2, первый и второй символы вхождения для определения в регистрах двоичного кода. Выходы логических элементов ИЛИ поступают на входы логического элемента И DD14. Выходной сигнал формат поиска определяет алгоитм работы устройства - последовательный или параллельный поиск ПСПР. Сигнал поступает на вход блока 6 управления. Если сигал формат поиска ПСПР равен нулевому значению, то будет осуществлен последовательный поиск, т.к. только в первом регистре блока символ входения. Если сигнал равен единице, то поиск будет параллельным, т.к. в двух регистрах блока символы вхождения (фиг.3).

Блок 7 регистров обрабатываемого слова БРгОС содержит n универсальных восьмиразрядных регистров сдвига Рг1, Рг2, …, Ргn, выполненных на элементах DD15, DD16, DD17, DD18, h универсальных восьмиразрядных буферных регистров сдвига Ргn+1, Ргn+2, …, Ргn+k, выполненных на элементах DD19, DD20, DD21, DD22, логическую схему ИЛИ, выполненную на пороговом элементе DD23 (фиг. 4). Регистры блока работают в режимах: последовательного ввода, параллельно-последовательного вывода, хранения, установки в нулевое состояние. Режимы работы регистров задаются сигналами на управляющих входах. Управляющие сигналы подаются параллельно на все регистры. Из блока 6 управления на управляющие входы регистров поступает информационный сигнал управление режимами работой УПРС блока регистров обрабатываемого слова. Управляющие сигналы СО, P/S и A/S поступают на все регистры параллельно. Сигнал СО - синхронизирующий тактовый импульс, сочетание сигналов P/S и A/S определяют режимы работы регистров блока. Сигнал P/S формирует способ ввода информации, сигнал A/S - режим асинхронный/синхронный [3]. Входной информационный сигнал обрабатываемое слово ДОС поступает на вход регистра Ргn DD18 из блока памяти обрабатываемых слов. При поступлении сигналов сдвига информация с регистра Ргn элемента DD18 сдвигается в регистр Рг1 элемента DD15. В параллельном режиме символы обрабатываемого слова ОС1, ОС2, ОС3, …, ОСn поступают на входы компараторов. При последовательном формате только один символ обрабатываемого слова ОС1 поступает на вход компаратора. На входы компараторов поступаю символы вхождения при параллельном поиске и один символ вхождение при последовательном поиске (фиг. 4). Результатом сравнения может быть нулевое или единичное значение выходного сигнала компаратора. Если на выходе компаратора установилась единица, то операция поиска выполнена положительно, вхождение обнаружено. Если получено нулевое значение на выходе компаратора, то формируется сигнал сдвига влево на один разряд символов обрабатываемого слова. Выходной сигнал ОС1 с выходов первого регистра Рг1 поступает на входы логической схемы ИЛИ элемента DD23 (фиг. 4). Выходной управляющий сигнал признак конца обрабатываемого слова ПКОС с выхода схемы ИЛИ определяет нулевую комбинацию на входе схемы. Нулевой двоичный код 0 … 00 является признаком конца символов обрабатываемого слова. В этом случае все символы обрабатываемого слова в регистрах блока просмотрены. Если признак конца обрабатываемого слова равен единичному значению, то в регистрах блока имеется двоичная информация. Процесс поиска в этом случае продолжается. Синхронизирующий сигнал СО является выходным управляющим сигналом блока регистров обрабатываемого слова, который поступает на входы логических элементов И комбинационных схем блока последовательно-параллельного поиска (фиг. 7, 9).

Блок 2 параллельно-последовательный поиск БППП содержит: блок параллельного поиска БППА и блок последовательного поиска БППО (фиг.5). Блок параллельного поиска выполняет операцию если в регистре вхождений записано от двух и более символов. Поиск в обрабатываемом слове осуществляется параллельно, на схему сравнения поступают сразу все символы вхожения.

Блок последовательного поиска выполняет операцию если в регистре вхождений записан только один символ. Поиск в обрабатываемом слове осуществляется последовательно, посимвольно, на схему сравнения поступают по очередно по одному символу вхожения. Каждый последующий символ поступает на компаратор только после обнаружения в слове предыдущего.

Блок параллельного поиска БППА содержит: блок регистров вхождений DD54, блок регистров обрабатываемых слов DD57, логическую схему ИЛИ, выполненную на пороговом элементе DD55, логическую схему И, выполненную на пороговом элементе DD56, двоичные компараторы DD59, DD60, DD61 выполненные на формальных нейронах, комбинационную схему формирования адреса вхождения КСхФА, комбинационную схему КСхОЧ, определяющую режим работы устройства без общих частей БОЧ (фиг.7, 8, 9). Функции блока параллельного поиска заключаются в записи, хранении и выдачи символов вхождений и обрабатываемых слов, в поразрядном сравнении символов вхождений и обрабатываемых слов в компараторах, определении адресов вхождений в обрабатываемых словах, а так же определении режима работы устройства. Входным информационным сигналом, формирующим режим работы блока регистров вхождений устройства является сигнал управления вхождениями УПРВ. Этот сигнал поступает на управляющие входы блока регистров вхождений из блока 6 управления (фиг. 1, 7, 8). В состав этого сигнала входят управляющие сигналы, которые определяют режим работы блока: разрешение записи, хранения и выдача двоичных разрядов вхождений, сигнал обнуления регистров, сигнал сдвига влево информации, синхроимпульсы. На информационные входы регистров блока поступают данные - вхождения ВХ из блока памяти вхождений (фиг. 2, 7, 8). Выходной информационный сигнал блока регистров вхождений поступает на входы схем сравнений - компараторов и на входы логической схемы ИЛИ, определяющая высокоимпедансное состояние выключено (фиг. 7, 8). Входным информационным сигналом блока регистров обрабатываемого слова является сигнал управления обрабатываемами словами УПРС, который поступает на управляющие входы регистра блока регистров обрабатываемых слов из блока 6 управления. Этот сигнал состоит из управляющих сигналов, формирующих режимы работы регистров: разрешения записи, хранения и выдачи информации из регистров блока, сигнал сдвига влево информации на один разряд, синхроимпульсы, сигналы обнуления регистров (фиг.6). На информационные входы регистров блока регистров обрабатываемых слов поступает информационный сигнал обрабатываемого слова ОС из блока памяти (фиг. 2, 4). Выходной информационный сигнал регистров блока регистров обрабатываемых слов поступает на входы схем сравнений - компараторов, выполненные на формальных нейронных элементах DD59, DD60, DD61 (фиг. 8). На входы компараторов поступают символы вхождений и обрабатываемых слов в двоичном коде. Выходные сигналы компараторов поступают на входы схемы И пороговых элементов DD56. Компараторы работают в режиме равенства входных величин операции эквиваленции. Выходной сигнал результат сравнения РСР блока параллельно-последовательного поиска будет равен единичному значению только в том случае, когда двоичные коды символов вхождения и обрабатываемого слова будут равны между собой. Это означает равенство символов вхождения с фрагментом обрабатываемого слова. Единичное значение сигнала РСР означает то, вхождение найдено в обрабатываемом слове. В этом случае формируется адрес вхождения в обрабатываемом слове в режиме поиска работы устройства или записывается замена в регистры блока результата замены в режиме поиска и замены работы устройства. Если сигнал результат сравнений РСР равен нулевому значению, то равенство входных величин на входе компаратора не произошло, в этом случае необходимо сдвинуть обрабатываемое слово на один разряд влево, затем анализировать результат сравнения символов вхождения и следующего фрагмента обрабатываемого слова (фиг. 7, 8). Выходным управляющим сигналом блока является сигнал признак конца символов ПКОС обрабатываемого слова, который поступает на управляющий вход блока 6 управления. Если признак конца обрабатываемого слова равен единичному значению, то это означает, что не все символы обрабатываемого слова просмотрены, в регистрах блока регистров обрабатываемого слова еще имеется двоичная информация. В случае равенства этого сигнала нулевому значению, это означает, что все символы обрабатываемого слова просмотрены. В регистрах блока регистров обрабатываемого слова информации нет - регистры “пустые” (фиг. 4). Выходным информационным сигналом блока является символ обрабатываемого слова ОС1, поступающий с выхода первого регистра Рг1 блока регистров обрабатываемого слова, который поступает на вход блока замены (фиг. 4, 11). Этот символ будет записан в регистр блока регистров результата замены в случае отрицательного сравнения входных величин в компараторах блока. В состав блока анализа поиска входит комбинационная схема формирования адреса вхождения КСхФА. На выходе этой комбинационной схемы определяется информационный сигнал адреса вхождения АДВ в обрабатываемом слове, который поступает на вход блока хранения результата. Управляющим сигналом, поступающим на вход комбинационной схемы формирования адреса блока параллельно-последовательного поиска из блока 6 управления является сигнал отпирающий импульс ОТИ. Этот сигнал поступает на управляющие входы схем И, выполненных на пороговых элементах DD62 и DD63. Схема И на элементе DD62 имеет инверсный управляющий вход, схема И на элементе DD63 имеет прямой управляющий вход. На информационный вход схемы И элемента DD62 поступает сигнал сдвига СО влево на один разряд с входов регистров блока регистров обрабатываемого слова. На информационный вход схемы И элемента DD31 поступает сигнал сдвига СВ влево на один разряд с входов регистров блока регистров вхождений (фиг.9). Выходные сигналы схем И DD62 и DD63 поступают на входы логической схемы ИЛИ элемента DD64. Выходной сигнал логической схемы ИЛИ DD64 поступает на суммирующий вход двоичного счетчика адреса СчА DD65. На выходе счетчика СчА будет определен адрес вхождения в обрабатываемом слове. Адрес формируется из суммы сигналов сдвига влево, вначале при загрузки в регистр вхождения, затем при поиске, регистра обрабатываемого слова. Предварительно двоичный счетчик адреса СчА DD65 будет обнулен сигналом установки в нуль ОБС, поступающим из блока 6 управления на вход R1 установки в нулевое состояние двоичного счетчика (фиг. 9). Вначале сигнал отпирающий импульс ОТИ равен единичному значению. В этом случае схема И DD62 будет заперта - сигнал поступает на инверсный управляющий вход, а схема И DD63 будет открыта, так как сигнал поступает на прямой управляющий вход. Количество сигналов сдвига влево регистра вхождения через открытую схему И DD63, схему ИЛИ DD64 поступают на суммирующий вход двоичного счетчика СчА DD65. Количество сигналов сдвига СВ будет соответствовать количеству символов вхождения. После этого отпирающий импульс ОТИ устанавливается в нулевое состояния. В результате этого схема И DD62 будет открыта, так как сигнал подается на инверсный вход схемы, а схема И DD63 будет заперта, сигнал подается на прямой вход схемы. В этом случае сигналы сдвига влево регистра обрабатываемого слова через открытую схему И DD62, схему ИЛИ DD64 поступают на суммирующий вход двоичного счетчика СчА DD65. В счетчике происходит подсчет количества сигналов сдвига влево регистра обрабатываемого слова. В результате этих процедур на выходе двоичного счетчика будет сформирован адрес вхождения в обрабатываемом слове, то есть местоположения определенного фрагмента в полной цепочке символов обрабатываемого слова (фиг.9). Комбинационная схема, определяющая режим работы устройства без общих частей КCхОЧ содержит: схему И DD66, суммирующий двоичный счетчик СчС DD67, вычитающий счетчик СчВ DD68, схему ИЛИ DD69. Режим работы устройства без общих частей производит поиск в обрабатываемых словах, не имеющих общих символов между предыдущим и последующим вхождениями [7]. Для формирования этого режима работы в случае обнаружения вхождения в обрабатываемом слове, необходимо сдвинуть обрабатываемое слова влево на m разрядов влево, где m - количество букв вхождения. Предварительно двоичные счетчики СчС DD67 и СчВ DD68 будут обнулены сигналами ОБС, поступившими из блока 6 управления. На входы обнуления R2 и R3 счетчиков соответственно поступают сигналы установки в нулевое состояние элементов. Если устройство работает в режиме поиска вхождений без общих частей, то сигнал из блока 6 управления признак работы с общими частями ПОЧ принимает значение единице. Управляющий сигнал ПОЧ поступает на прямой управляющий вход электронного ключа схемы И DD66 для отпирания. Через открытую схему И сигналы сдвига влево СВ вхождений поступают на суммирующий вход двоичного счетчика СчС DD67. В счетчике СчС будет подсчитано количество символов вхождения. Выходы суммирующего счетчика СчС поступают на входы D1- Dx вычитающего счетчика СчВ. В результате этой операции происходит предварительная установка вычитающего счетчика СчВ в двоичное значение равное количеству символов вхождения. На вычитающий вход счетчика СчВ поступают сигналы сдвига влево СО обрабатываемого слова. На выходе вычитающего счетчика СчВ вычисляется разность между количеством символов вхождения и поступившими сигналами сдвига обрабатываемого слова. Логическая схема ИЛИ DD69 определяет нулевое значение сигнала признака работы устройства без общих частей БОЧ. Если сигнал БОЧ равен нулевому значению, то это означает, что обрабатываемое слово сдвинуто на m разрядов влево, где m - количество символов вхождения. В результате этой операции необходимо продолжить операцию сравнения символов вхождения и обрабатываемого слова. Выходной управляющий сигнал признак работы без общих частей БОЧ блока параллельно-последовательного поиска поступает на управляющий вход блока 6 управления (фиг.1, 9).

Блок последовательного поиска БППО содержит: триггер Тр DD70, двухвходовый логический элемент И DD71 с инверсным входом, двухвходовый логический элемент И DD72, двухвходовый логический элемент И DD76, трехвходовый логический элемент И DD73 с инверсным входом, четырехвходовый элемент И DD75 с инверсными входами, трехвходовый элемент И DD81 с инверсным входом, электронный ключ DD78, двоичный счетчик СЧ1 DD74, двоичный счетчик СЧ2 DD77, двухвходовый элемент ИЛИ с инверсными входами DD80, двухвходовый элемент И DD79 (фиг.10). Перед началом работы устройства двоичные счетчики DD74, DD77, триггер Тр DD70 установлены в нулевое состояние. На вход блока последовательного поиска БППО поступает входной сигнал результат сравнения РСР с выхода логической схемы И DD53. Если сигнал ССР равен единице, то это означает что произошло совпадение двоичных кодов символов вхождения и обрабатываемого слова. В этом случае триггер Тр DD70 по приходу из блока 6 управления разрешающего сигнала СЗЩ, равного единице, устанавливается в единичное состояние. Логический элемент И DD72, выполняющий функцию электронного ключа, отпирается, тактовые импульсы ТАК из блока 6 управления поступают на суммирующий вход двоичного счетчика СЧ1 DD74, в котором происходит суммирование тактовых импульсов, количество которых соответствует количеству совпадений в компараторе. На выходе двоичного счетчика СЧ1 DD74 формируется двоичный код, соответствующий количеству положительных совпадений на входе компаратора. При каждом положительном совпадении в компараторе происходит формирование сигналов сдвига влево СВ и СО равных нулю и осуществляется сдвиг на один символ влево в регистрах вхождения и обрабатываемом слове. В случае отрицательного сравнения входных величин в компараторе символ обрабатываемого слова ОС1, поступающий с выхода первого регистра Рг1, записывается в регистр буфер Ргn+1 DD19 блока обрабатываемого слова (фиг. 4, 10). В случае обнаружения признака конца вхождения ПРКВ равным единице логический элемент И DD12 в регистре вхождений происходит определение адреса вхождения и запись по соответствующему адресу в оперативное запоминающее устройство DD102 блока 5 хранения адреса вхождений. Если признак конца слова ПРКС равного нулю не обнаружен, то предыдущее вхождение восстанавливается, т.е. переписывается заново из памяти вхождений и процесс поиска вхождений в слове продолжается для обнаружения очередного вхождения. Если совпадений в компараторе не происходит, выходной сигнал РСР равен нулю, то формируется только сигнал СО равным нулю и происходит сдвиг влево на одну позицию обрабатываемого слова. При каждом сдвиге влево и отрицательном результате совпадения в компараторе, из памяти слов ПОС дописывается очередной символ слова в регистр блока регистров обрабатываемых слов БРгОС 7. Возможна ситуация в поисковой операции, когда был получен положительный результат сравнения символов, тогда формируется сдвиг влево на один разряд регистров вхождений и обрабатываемых слов. После сдвига получен второй раз положительный результат, третий и так далее, но признака конца вхождения еще нет. Допустим на n шаге получен отрицательный результат сравнения, а вхождение полностью не обнаружено. В этом случае триггер Тр DD70 был установлен в единичное состояние. На следующем этапе сравнение на равенство не произошло, сигнал результата на сравнения РСР равен нулю. На выходе логического элемента И DD71 будет сформирован единичный сигнал. Логический элемент И DD73 также будет открыт, прямоугольные импульсы из блока 6 управления ПРИ будут поступать на вычитающий вход двоичного счетчика СЧ1 DD74. Вычитание происходит до тех пор пока на выходе счетчика не будет двоичный код равный единице. На положительный вход счетчика СЧ1прямоугольные импульсы из блока 6 управления поступать не будут т.к. логический элемент И DD72, выполняющий функцию электронного ключа будет заперт, установившимся в нулевое состояние триггером Тр DD70. Логический элемент И DD75 выполняет роль дешифратора единицы. Выход этого элемента равен единице в случае получения на выходе счетчика СЧ1 DD74 двоичного кода 0001. При всех других входных комбинациях на выходе логического элемента И DD75 будет нулевое состояние. При единице на выходе схемы И DD75 логический элемент И DD73 запирается т.к. единица поступает на инверсный вход. Прямоугольные импульсы на вычитающий вход счетчика СЧ1 DD74 не поступают. Счетчик СЧ1 DD74 обнуляется командой ОБН, поступающей из блока 6 управления. Логический элемент И DD81 формирует количества сдвигов вправо регистра блока регистров обрабатываемых слов БРгОС. При вычитании единицы из состояния счетчика СЧ1 DD74, происходит запись информации из регистра буфера РгБФ в регистр блока регистров обрабатываемых слов БРгОС 7 (фиг. 4). Количество сдвигов вправо будет на один меньше, чем количество сдвигов влево n-1. Вторая буква из полученной серии положительных сдвигов будет первой в регистре блока регистров обрабатываемых слов БРгОС 7. Вхождение будет заново переписано из памяти вхождений в регистр блока регистров вхождений БРгВХ 8. Процесс поиска будет продолжен. Логический элемент ИЛИ DD50 определяет режим работы: 1) вхождения с общими частями; 2) без общих частей. В первом случае признак режима работы РР будет равен нулю, во втором случае признак РР равен единице. Если признак работы РР устройства равен нулю, на выходе элемента ИЛИ DD80 буде единица. Электронный ключ И DD79 будет открыт. Прямоугольные импульсы ПРИ из блока 6 управления через открытый ключ поступают на третий вход логического элемента И DD73. Этот режим характеризуется перемещением информации из регистра буферов блока регистра обрабатываемых слов в регистры блока регистров обрабатываемых слов на n-1 разрядов, т.е. будет сформирован возврат информации, где n - количество положительных сдвигов, всякий раз, когда будет обнаружено вхождение в обрабатываемом слове при этом признак конца вхождения ПРКВ будет равен единице. Если режим работы устройства будет установлен на поиск вхождений без общих частей, то в этом случае признак работы РР равен единице. В случае обнаружения вхождения, при этом признак конца вхождений ПРКВ равен единице. На выходе логического элемента ИЛИ DD80 установить нулевое значение. Электронный ключ И DD79 будет заперт. Прямоугольные импульсы ПРИ из блока 6 управления не будут поступать на вход элемента И DD73 (фиг.10). Информация из регистра буфера РгБФ в регистр блока регистров обрабатываемых слов БРгОС 7 не записывается. В этом случае будет сформирован сдвиг влево символов из регистра блока регистров обрабатываемых слов БРгОС 7 в регистр буфера РгБФ блока (фиг.10).

Блок 3 памяти замены БПЗМ содержит оперативное запоминающее устройство ОЗУ DD9. В блоке памяти оперативного запоминающего устройства записаны цепочки символов, которые записываются в блок замены, если устройство работает в режиме поиска и замены. В случае положительного сравнения символов вхождения и обрабатываемого слова, то цепочка символов замены будет записана в регистр блока замены. Входной информационный сигнал УЗМ состоит из управляющих сигналов: выбора кристалла микросхемы и режима записи/чтения информации из оперативного запоминающего устройства блока. Входные информационные сигналы АдЗМ являются адресными входами оперативного запоминающего устройства. Сигнал адреса АдЗМ состоит из адресов столбцов и строк, по которым записывается информация в блок памяти. Информационными данными ДЗМ являются символами замены, которые поступают на информационные входы оперативного запоминающего устройства блока памяти. По сигналам выбора кристалла и разрешения записи УЗМ, а так же по адресным входам АдЗМ, данные замены записываются в оперативное запоминающее устройство блока памяти. Выходной информационный сигнал блока - замены ЗМ поступает на вход блока замены (фиг.1,2).

Блок 4 замены БЗАМ содержит блок регистров замены БРгЗМ DD82, систему электронных ключей схему И с прямыми управляющими входами, выполненных на пороговых элементах DD83, DD84, DD85, систему электронных ключей схему И с инверсными управляющими входами, выполненных на пороговых элементах DD86, DD87, DD88, систему элементов ИЛИ, выполненных на пороговых элементах DD89, DD90, DD91, выполняющую собирательную функцию, блок регистров результата замены БРгРЗ DD92 (фиг. 11). Функция этого блока заключается в управлении операцией записи в блок регистров результата замены символа обрабатываемого слова, если на выходе схемы сравнения установлено нулевое значение или букв замены, в случае положительного сравнения входных величин в компараторах устройства в режиме работы поиска и замены. Блок регистров замены БРгЗМ DD82 предназначен для записи, хранения и выдачи символов замены. Замена осуществляется в случае обнаружения символов вхождения в обрабатываемом слове и в режиме работы устройства поиска и замены. Входной информационный сигнал - УЗМ поступает на управляющие входы регистров блока регистров замены и состоит из управляющих сигналов: сдвига влево информации на один разряд, синхроимпульсов, формирующих режимы записи, хранения и выдачи двоичного кода. Входной информационный сигнал замены ДЗМ поступает на информационные входы регистров блока. По приходу управляющих разрешающих сигналов из блока 6 управления происходит запись символов замены в регистры блока регистров замены. Выходной информационный сигнал блока регистров замены поразрядно поступает на информационные входы системы электронных ключей DD83, DD84, DD85 с прямыми управляющими входами. Входным информационным сигналом блока регистров замены является сигнал ОС1. Этот сигнал поступает с выхода регистра Рг1 DD15 блока регистров обрабатываемого слова БРгОС (фиг. 4). Информационный сигнал ОС1 поступает на информационные входы системы электронных ключей DD86, DD87, DD88 с инверсными управляющими входами. Информационные выходы систем электронных ключей DD83, DD84, DD85, DD86, DD87, DD88 поступают на входы системы элементов ИЛИ DD89, DD90, DD91. Выходные информационные сигналы ОСЗМ логических элементов ИЛИ поступают на информационные входы регистров блока регистров результата замены (фиг. 11). Информационный сигнал ОСЗМ является результатом логической функции ИЛИ входных величин: символа обрабатываемого слова ОС1и символов замены ЗМ: ОСЗМ=(ОС1)или(ЗМ). Входным управляющим сигналом блока замены является сигнал управления УКЛ, поступающий из блока 6 управления на прямые управляющие входы системы электронных ключей DD83, DD84, DD85, и на инверсные управляющие входы электронных ключей DD86, DD87, DD88 (фиг. 11). Если управляющий сигнал УКЛ равен нулевому значению, то система электронных ключей с прямимы управляющими входами DD83, DD84, DD85 будет заперта, а электронные ключи с инверсными управляющими входами DD86, DD87, DD88 будут открыты. В этом случае символ обрабатываемого слова ОС1 через открытые электронные ключи DD86, DD87, DD87 и систему логических элементов ИЛИ DD89, DD90, DD91 поступит на вход информационного входа регистров блока регистров результата замены (фиг. 11). По приходу информационного сигнала УРЗМ на управляющие входы регистров блока регистров результата замены из блока 6 управления, входная информация ОСЗМ будет записана в регистры блока регистров результата замены. Управляющие сигналы регистров блока формируют режимы: сдвига влево информации на один разряд С, синхронизации, записи, хранения и выдача P/S, A/S результата в регистрах блока. В случае равенства сигнала управления УКЛ единичному значению, то система электронных ключей с прямимы управляющими входами DD83, DD84, DD85 будет открыта, а электронные ключи с инверсными управляющими входами DD86, DD87, DD88 будут закрыты. В этом случае символы замены ЗМ через открытые электронные ключи DD83, DD84, DD85 и систему логических элементов ИЛИ DD89, DD90, DD91 поступают на вход информационного входа регистров блока регистров результата замены, где по приходу управляющих сигналов УРЗМ будут записаны и хранится в блоке (фиг.11). Выходной информационный сигнал блока регистров результата замены РЗ, представляет собой информацию результатов замены или символов обрабатываемого слова. Этот сигнал поступает на вход блока хранения результата (фиг. 1, 11,14).

Блок 82 регистров замены БРгЗМ содержит s универсальных восьмиразрядных регистров сдвига РгЗМ1, РгЗМ2, …, РгЗМs, выполненных на элементах DD93, DD94, DD95 (фиг. 12). Регистры блока работают в режимах: последовательного ввода, последовательного вывода, хранения, установки нулей (сброс). Режимы работы регистров задаются сигналами на управляющих входах. Регистры соединены между собой последовательно. На управляющие входы регистров из блока 6 управления поступает информационный сигнал УЗМ - управление режимами работой блока регистров замены. Управляющие сигналы С, P/S и A/S поступают на все регистры параллельно. Сигнал С - синхронизирующий тактовый импульс, комбинации сигналов P/S и A/S определяют режимы работы регистров блока. Сигнал P/S формирует способ ввода информации сигнал режим асинхронный/синхронный A/S [3]. Входной информационный сигнал символы замены ДЗМ поступает на вход регистра РгЗМs DD95 из блока памяти замены. При генерации сигналов сдвига влево на один разряд, информация с регистра РгЗМs элемента DD95 поступает на выход регистр РгЗМ1 элемента DD93 (фиг. 12). Вначале работы устройства все регистры блока будут обнулены. В режиме поиска и замены, а так же левой или правой конкатенаций, по приходу управляющих сигналов из блока 6 управления, символы замены записываются из блока памяти замены в регистры блока регистров замены (фиг. 2, 12). Выходным информационным сигналом блока регистров замены является двоичный код символов замены ЗМ. Блок работает в режиме записи, хранения и выдачи информации. Выдача информации происходит в режиме поиска и замены работы устройства. Если в обрабатываемом слове обнаружено вхождение, то необходимо в регистры блока регистров результата замены записать замену - цепочку символов. В этом случае регистры блока работают в режиме выдачи информации (фиг. 11, 12).