Изобретение относится к области силовой преобразовательной электроники, в частности, к автономным инверторам напряжения и может быть использовано в качестве источника питания для трехфазных нагрузок с индуктивностью, например, для асинхронных и синхронных электродвигателей.

Известен автономный инвертор напряжения (см. патент RU №2403667 от 27.07.2009 г., опубликован в Б.И. 31 10.11.2010 г.), который содержит подключенный к входным выводам трехфазный мост на транзисторах, зашунтированных встречными диодами, выходные выводы которого соединены с выходными выводами инвертора напряжения, три датчика тока, включенные в цепи выходных выводов инвертора напряжения, транзисторы зашунтарованы конденсаторами и варисторами, трехфазный мост на транзисторах зашунтирован ограничителем напряжения и последовательной цепью из двух конденсаторов, общая точка соединения которых подключена к выводу заземления инвертора напряжения, инвертор напряжения снабжен шестью последовательными цепями, содержащими двухвходовую схему И и выходной каскад, выходы выходных каскадов соединены с управляющими электродами транзисторов, распределителем, импульсов, выходы которого соединены с первыми входами двчхвчодовых схем И, задающим генератором, выход которого соединен с входом распределителя импульсов, шестью компараторами, выходы которых соединены с вторыми входами двухвходовых схем И, а входы попарно объединены и подключены к выходам датчиков тока, выходные выводы трехфазного моста попарно зашунтарованы дополнительными снабберными конденсаторами.

Недостатками вышеуказанного автономного инвертора напряжения является отсутствие ограничения уровней коммутационных экстратоков при включении силовых транзисторов, так как устройство работает в квазирезонансном режиме, что обеспечивает режим «мягкой» коммутации только при выключении силовых транзисторов.

Вышеуказанное устройство является наиболее близким по технической сущности к заявляемому устройству и поэтому выбрано в качестве прототипа.

Решаемой технической проблемой является создание формирователя импульсов тока с расширенными функциональными возможностями.

Достигаемым техническим результатом является обеспечение ограничения уровней коммутационных экстратоков при переключении силовых транзисторов, улучшение электромагнитной совместимости, увеличение коэффициента полезного действия (КПД), работоспособности с заданными электрическими характеристиками в условиях воздействия ВФ (внешние факторы) с высокими значениями характеристик воздействия.

Для достижения технического результата в формирователе импульсов тока, содержащем двухвходовые логические элементы «И», выход каждого из которых соединен со входом соответствующего первого выходного каскада, выход каждого из которых соединен с затвором соответствующего нижнего транзистора, вторые выходные каскады, выход каждого из которых соединен с затвором верхнего транзистора соответственно, ограничитель напряжения, датчики тока, встречные диоды, анод каждого из которых соединен с истоком верхнего пли нижнего транзистора соответственно, пороговое устройство, новым является то, что дополнительно введены первый, второй, третий, четвертый, пятый, шестой демпферы тока, первый вывод каждого из которых соединен со стоком верхнего или нижнего транзисторов соответственно, второй вывод первого, третьего и пятого демпферов тока соединен с катодом первого, третьего и пятого встречных диодов, а второй вывод второго, четвертого и шестого демпферов тока соединен с катодом второго, четвертого и шестого встречных диодов, первый, второй, третий, четвертый, пятый, шестой демпферы напряжения, первый и второй, третий и четвертый, пятый и шестой из которых соединены между собой последовательно, первый вывод первого, третьего и пятого демпферов напряжения соединен с катодом первого, третьего и пятого встречных диодов и объединены между собой и подключены к первому входу ограничителя напряжения и к плюсовой шине источника питания, вторые выводы второго, четвертого и шестого демпферов напряжения соединены с анодами второго, четвертого и шестого встречных диодов, объединены между собой и подключены к минусовой шине источника питания и ко второму входу ограничителя напряжения, бланкировщик (узел бланкирования), последовательно соединенные трехфазный мост и фильтр помех, выход которого соединен со входом порогового устройства, выход которого соединен со входом бланкировщика, выход которого соединен с первыми входами двухвходовых логических элементов «И», вторые входы которых и входы вторых выходных каскадов являются входами формирователя импульсов тока первичная цепь каждого датчика тока соединена с первым: выводом второго, четвертого и шестого демпферов напряжения и является одним из выходов формирователя импульсов тока, а вторичная цепь каждого датчика тока соединена с входом трехфазного моста соответственно.

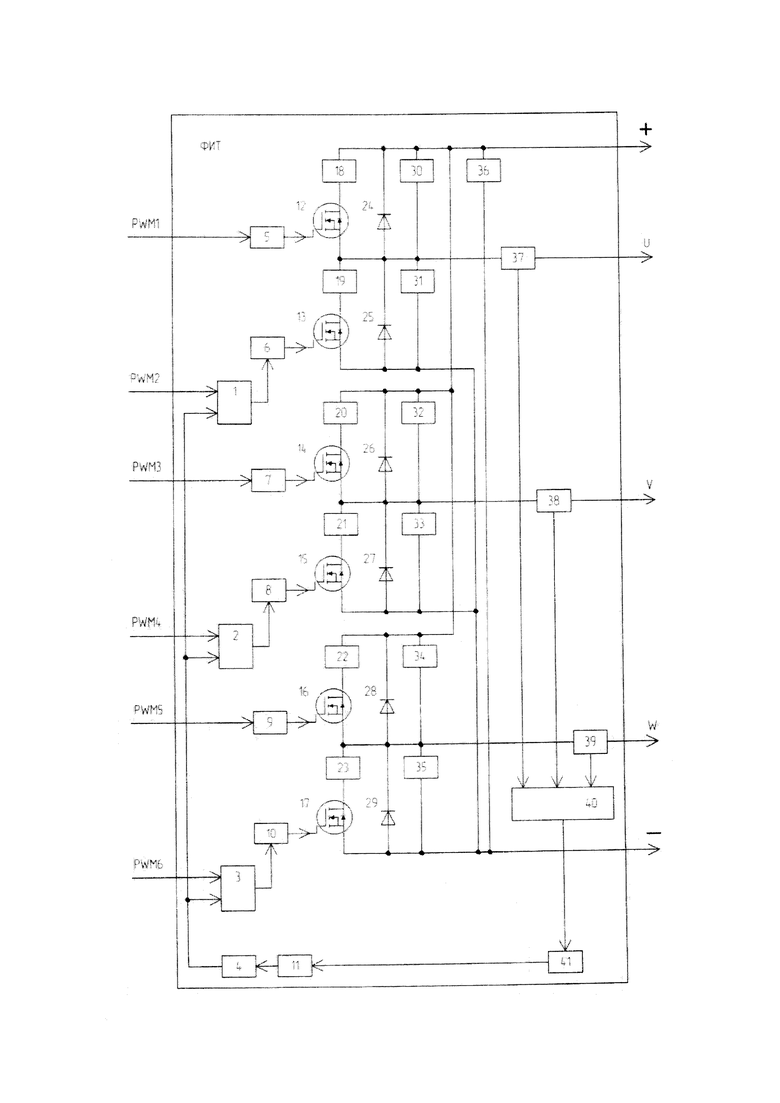

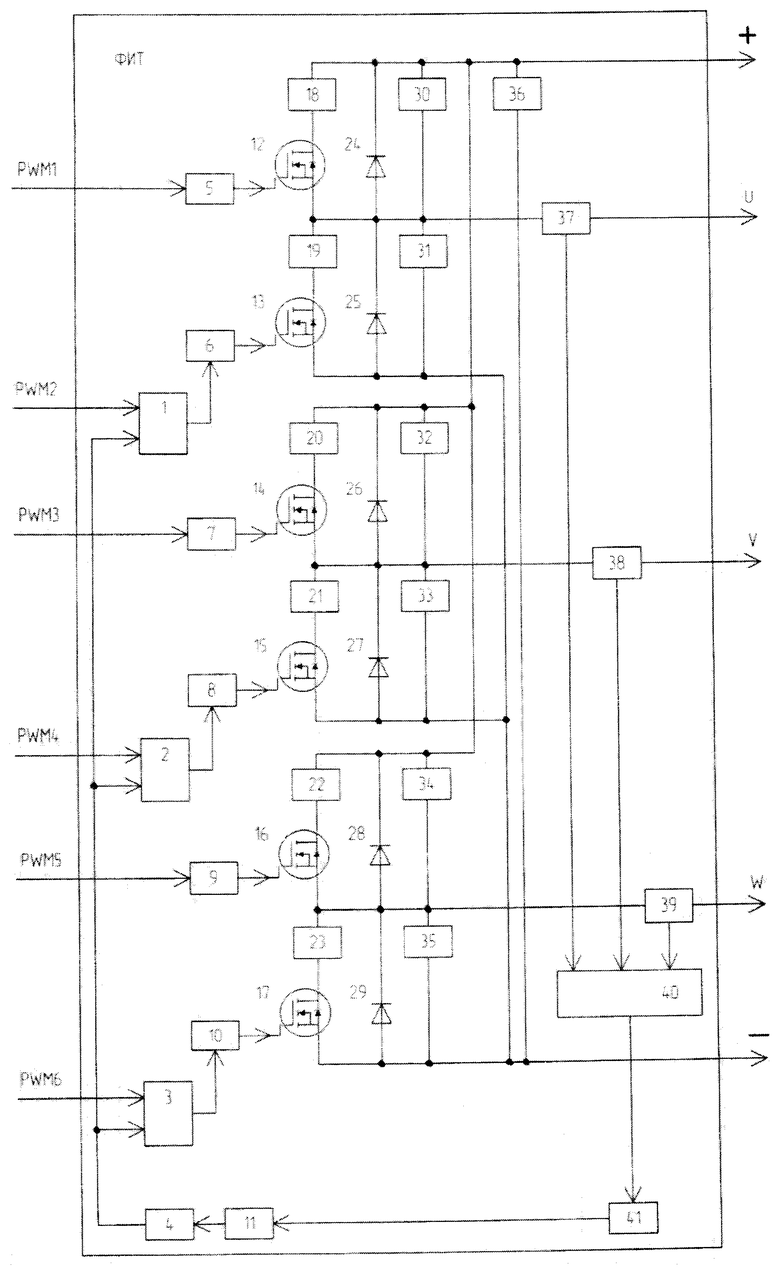

На фигуре представлена схема формирователя импульсов тока.

Формирователь импульсов тока содержит первый 1, второй 2, третий 3 двухвходовые логические элементы «И», выход 1 элемента соединен со входом первого выходного каскада 6, выход 2 элемента соединен со входом первого выходного каскада 8, выход 3 элемента соединен со входом первого выходного каскада 10. Выход каждого каскада 6, 8, 10 соединен с затвором транзисторов 13, 15 и 17, вторые выходные каскады 5, 7, 9, выход каждого из которых соединен с затвором 12, 14 и 16 транзисторов. Ограничитель напряжения 36, датчики тока 37, 38, 39, встречные диоды 24, 25, 26, 27, 28, 29, анод 24, 26, 28 диодов соединен с истоком 12, 14 и 16 транзисторов, а анод 25, 27, 29 диодов соединен с истоком 13, 15 и 17 транзисторов. Пороговое устройство 11, первый 18, второй 19, третий 20, четвертый 21, пятый 22 и шестой 23 демпферы тока, первый вывод 18, 20, 22 демпферов тока соединен со стоком 12, 14 и 16 транзисторов, а первый вывод 19, 21 и 23 демпферов тока соединен со стоком 13, 15 и 17 транзисторов. Второй вывод 18, 20 и 22 демпферов тока соединен с катодом 24, 26 и 28 встречных диодов, а второй вывод 19, 21 и 23 демпферов тока соединен с катодом 25, 27 и 29 встречных диодов. Первый 30, второй 31, третий 32, четвертый 33, пятый 34 и шестой 35 демпферы напряжения, при этом 30 и 31, 32 и 33, 34 и 35 соединены между собой последовательно. Первый вывод 30, 32 и 34 демпферов напряжения соединен с катодом 24, 26 и 28 встречных диодов, объединены между собой и подключены к первому входу ограничителя напряжения 36 и к плюсовой шине питания, а второй вывод 31, 33 и 35 демпферов напряжения соединен с анодом 25, 27 и 29 встречных диодов, объединены между собой и подключены ко второму входу ограничителя напряжения 36 и к минусовой шине питания. Бланкировщик 4, последовательно соединенные трехфазный мост 40 и фильтр помех 41, выход которого соединен со входом порогового устройства 11, выход которого соединен со входом бланкировщика 4, выход которого соединен с первыми входами двухвходовых логических элементов «И» 1, 2, 3, вторые входы которых и входы выходных каскадов 5, 7 и 9 являются входами формирователя импульса тока, первичная цепь датчиков тока 37, 38 и 39 соединена с первым выводом 31, 33 и 35 демпферов напряжения и является одним из выходов формирователя импульса тока, а вторичная цепь датчиков тока 37, 38 и 39 соединена с входом трехфазного моста 40.

Двухвходовые схемы «И» 1, 2, 3 обеспечивают передачу внешних сигналов управления на выходные каскады 6, 8, 10, а также согласуют с ними по напряжению сигналы бланкировщика 4. Двухвходовые схемы 1, 2, 3 могут быть реализованы на быстродействующих цифровых логических элементах «2И», обеспечивающих одинаково минимальные задержки передаваемых сигналов.

Выходные каскады 5-10 предназначены для усиления внешних входных сигналов с целью правления силовыми транзисторами 12-17. Они могут быть реализованы на микросхемах управления (драйверах) силовыми МОП-транзисторами (металл-окисел полупроводник).

Силовые транзисторы 12-17 предназначены для коммутации внешнего питающего напряжения с целью формирования выходных сигналов U, V, W. Они могут быть реализованы на мощных транзисторах с полевым и токовым управлением: ДМОП (двухдиффузионный МОП) и БТИЗ (биполярный транзистор с изолированным затвором).

Демпферы тока 18-23 предназначены для оптимизации процесса коммутации силовых транзисторов 12-17 в моменты их включения. Они могут быть реализованы в виде индуктивностей с сердечниками на базе магнитопроводов с прямоугольной петлей гистерезиса. Благодаря прямоугольной форме петли гистерезиса демпферы тока достигают очень большой индуктивности в моменты перехода через нуль протекающего по ним тока, т.е. формирование траектории переключения силовых транзисторов осуществляется в режиме «нулевых токов», что обеспечивает эффективное демпфирование быстрых изменений тока.

Узлы 24-29 и 36 обеспечивают шунтирование цепей формирователя импульсов тока (ФИТ) при изменении полярности и уровня напряжения питания, создаваемом динамической нагрузкой, ограничивая уровни перенапряжений на силовых транзисторах 12-17, а также рассеивают дополнительную энергию, создаваемую изменениями токов на погонных индуктивностях шин питания и монтажа при коммутации силовых транзисторов. Узлы 24-29 могут быть реализованы на сильноточных высоковольтных быстродействующих диодах, а узел 36 (ограничитель напряжения) - на мощном стабилитроне.

Демпферы напряжения 30-35 предназначены для оптимизации процесса коммутации силовыми транзисторами в момент их выключения. Они могут быть реализованы на RC-цепочках, состоящих из последовательно соединенных резистора и пленочного конденсатора. Демпферы напряжения 30-35 обеспечивают эффективное демпфирование скорости нарастания напряжения путем формирования траектории переключения силовых транзисторов в режиме «нулевых напряжении».

Датчики тока 37-39 предназначены для преобразования протекающих через них токов в напряжение. Они могут быть реализованы как на трансформаторах тока, так и на магниторезистивных датчиках тока.

Трехфазный мост 40 предназначен для выпрямления и суммирования выходных напряжений с датчиков тока 37-39. Он может быть реализован на импульсных диодах, входы которых подключаются к датчикам тока, а выходы соединены вместе,

Фильтр 41 представляет собой RC-цепочку для фильтрации импульсных помех, возникающих при работе силовых транзисторов 12-17, предотвращая ложное срабатывание блока токовой защиты (узды 4, 11, 40, 41).

Пороговое устройство 11 представляет собой компаратор напряжения, который сравнивает входной сигнал, поступающий от фильтра 41 помех, с опорным напряжением (на схеме не показано).

Бланкировщик 4 представляет собой одновибратор, формирующий сигнал запрета работы силовых транзисторов 12-17, который подается на двухвходовые схемы 1-3.

Источник опорного напряжения, пороговое устройство 11 и бланкировщик 4 могут быть реализованы на базе микросхемы ШИМ-контроллера.

Повышение надежности работы обеспечивается реализацией в ФИТ резонансного режима работы силовых транзисторов за счет введения демпферов тока, т.е он работает с полной «мягкой» коммутацией как при включении (режим нулевого тока), так и при выключении силовых транзисторов (режим нулевого напряжения). Условия резонансного режима работы силовых транзисторов обеспечивается путем выбора нужного соотношения между величинами емкостей демпферов напряжений (30-35) и

индуктивностей демпферов тока (18-23), которые в цепях силовых транзисторов (12-17) образуют последовательные и параллельные колебательные контуры, между которыми соблюдается баланс обмена реактивной энергией. Эта энергия обмена воплощается в синусоидальную форму токов и напряжений пол\проводниковых элементов ФИТ.

Увеличение коэффициента полезного действия устройства обеспечивается за счет уменьшения динамических потерь мощности в моменты включения и выключения силовых транзисторов, что обеспечивается реализацией полного режима их «мягкой» коммутации.

Улучшение электромагнитной совместимости ФИТ обеспечивается за счет коммутации в момент нулевого значения тока, что снижает значение производной нарастания тока и, следовательно, уровень помех, создаваемых дифференциальными токами в момент включения силовых транзисторов.

Работает ФИТ следующим образом.

От внешнего модуля слаботочные импульсные сигналы управления поступают на выходные каскады 5-10. Эти внешние импульсные сигналы поступают на узлы 5, 7, 9 непосредственно, а на узлы 6, 8, 10 - через первые входы двухвходовых схем 1, 2, 3. С выходов узлов 1, 2, 3 эти внешние импульсные сигналы передаются на выходные каскады 6, 8, 10 только в том случае, если с блока токовой защиты (узлы 4, 11,40, 41) поступает сигнал разрешения на вторые входы узлов 1, 2, 3.

Усиленные узлами 5-10 импульсные сигналы затем умощняютcя силовыми транзисторами 12-17 путем коммутирования ими электропитания положительного «+» и отрицательного «-» полюса источника, формируя на выходах ФИТ сильноточные двухполярные импульсные сигналы (U, V, W). В процессах коммутации (моменты включения и выключения) силовых транзисторов 12-17 совместно участвуют демпферы тока 18-23 и демпферы напряжения 30-35, создавая резонансный режим работы силовых транзисторов.

Подключенный к источнику питания узел 36 обеспечивает ограничение напряжение на установленном уровне.

Выходные импульсные токи сигналов U, V, W. протекая в первых обмотках трансформаторов тока 37-39, индуцируют во вторых обмотках токи, пропорциональные сигналам U, V, W. Трансформаторы тока 37-39 обеспечивают гальваническую развязку входов трехфазного моста 40 от выходных импульсных сигналов U. V, W, и преобразуют протекающий через них ток в напряжение, пропорциональное току. Выходы (вторые обмотки) трансформаторов нагружаются резисторами (на схеме не показаны) для предотвращения насыщения сердечников трансформаторов тока. Изменением номиналов нагрузочных резисторов трансформаторов тока можно изменять порог срабатывания защитного блока.

Сигналы с выходов датчиков тока 37-39 поступают на входы трехфазного моста 40. Сигналы на выходах датчиков тока могут быть двухполярными, а диодные мосты преобразуют двухполярные сигналы в однополярные, т.е. выделяют модули значений сигналов на своих входах. Объединенные выходы трех диодных мостов обеспечивают выделение максимального сигнала, поступающего с датчиков тока. Сигнал на выходе трехфазного моста 40 меньше сигналов с датчиков тока 37-39 на величину напряжения падения на двух диодах моста, причем это напряжение имеет отрицательную температурную зависимость, что обеспечивает «автоматическую» корректировку порога срабатывания защитного блока от изменения температуры, т.е. обеспечивается независимость работы защитного блока от изменения температуры.

Сигнал с выхода трехфазного моста 40, проходя через фильтр 41, очищается от наведенных помех, и поступает на вход порогового устройства - компаратора 11. Пороговое устройство 11 сравнивает сигнал на своем входе с опорным напряжением. При превышении входным сигналом порогового значения (опорного) напряжения, компаратор «срабатывает» и выдает сигнал в бланкировщик 4, который формирует сигнал, поступающий на двухвходовые схемы 1, 2, 3 и запрещающий их работу, тем самым ограничивая выходные токи силовых транзисторов 12-17 и предотвращая выходы их из строя.

Был изготовлен опытный образец ФИТ, подтвердивший его работоспособность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНВЕРТОР НАПРЯЖЕНИЯ | 2001 |

|

RU2210152C2 |

| АВТОНОМНЫЙ ИНВЕРТОР НАПРЯЖЕНИЯ | 2009 |

|

RU2403667C1 |

| Преобразователь переменного напряжения в постоянное | 1985 |

|

SU1270849A1 |

| СПОСОБ УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЕМ ЧАСТОТЫ | 2011 |

|

RU2454782C1 |

| Преобразователь переменного напряжения в постоянное | 1988 |

|

SU1577020A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2475922C1 |

| Передатчик СВЧ миллиметрового диапазона волн повышенной выходной мощности | 2019 |

|

RU2722422C1 |

| Преобразователь переменного напряжения в постоянное | 1985 |

|

SU1325640A1 |

| Датчик состояния вентилей реверсивного тиристорного преобразователя | 1991 |

|

SU1787303A3 |

| УПРАВЛЯЕМЫЙ ВЫПРЯМИТЕЛЬ | 2017 |

|

RU2634348C1 |

Изобретение относится к области силовой преобразовательной электроники, в частности к автономным инверторам напряжения, и может быть использовано в качестве источника питания для трехфазных нагрузок с индуктивностью, например для асинхронных и синхронных электродвигателей. Техническим результатом заявленного изобретения является обеспечение ограничения уровней коммутационных экстратоков при переключении силовых транзисторов, улучшения электромагнитной совместимости, увеличение КПД, работоспособности с заданными электрическими характеристиками в условиях воздействия ВФ (внешние факторы) с высокими значениями характеристик воздействия. Формирователь импульсов тока содержит двухвходовые логические элементы «И», выход каждого из которых соединен со входом соответствующего первого выходного каскада, выход каждого из которых соединен с затвором соответствующего нижнего транзистора, вторые выходные каскады, выход каждого из которых соединен с затвором верхнего транзистора соответственно, ограничитель напряжения, датчики тока, встречные диоды, анод каждого из которых соединен с истоком верхнего или нижнего транзистора соответственно, пороговое устройство. Введены шесть демпферов тока, шесть демпферов напряжения, бланкировщик, последовательно соединенные трехфазный мост и фильтр помех. Первый вывод каждого из демпферов тока соединен со стоком верхнего или нижнего транзисторов соответственно. Второй вывод первого, третьего и пятого демпферов тока соединен с катодом первого, третьего и пятого встречных диодов, а второй вывод второго, четвертого и шестого демпферов тока соединен с катодом второго, четвертого и шестого встречных диодов. Шесть демпферов напряжения соединены между собой последовательно. Первый вывод первого, третьего и пятого демпферов напряжения соединен с катодом первого, третьего и пятого встречных диодов и объединены между собой и подключены к первому входу ограничителя напряжения и к плюсовой шине источника питания. Вторые выводы второго, четвертого и шестого демпферов напряжения соединены с анодами второго, четвертого и шестого встречных диодов, объединены между собой и подключены к минусовой шине источника питания и ко второму входу ограничителя напряжения. Выход фильтра помех соединен со входом порогового устройства, выход которого соединен со входом бланкировщика, выход которого соединен с первыми входами двухвходовых логических элементов «И», вторые входы которых и входы вторых выходных каскадов являются входами формирователя импульсов тока. Первичная цепь каждого датчика тока соединена с первым выводом второго, четвертого и шестого демпферов напряжения и является одним из выходов формирователя импульсов тока, а вторичная цепь каждого датчика тока соединена с входом трехфазного моста соответственно. 1 ил.

Формирователь импульсов тока, содержащий двухвходовые логические элементы «И», выход каждого из которых соединен со входом соответствующего первого выходного каскада, выход каждого из которых соединен с затвором соответствующего нижнего транзистора, вторые выходные каскады, выход каждого из которых соединен с затвором верхнего транзистора соответственно, ограничитель напряжения, датчики тока, встречные диоды, анод каждого из которых соединен с истоком верхнего или нижнего транзистора соответственно, пороговое устройство, отличающийся тем, что дополнительно введены первый, второй, третий, четвертый, пятый, шестой демпферы тока, первый вывод каждого из которых соединен со стоком верхнего или нижнего транзисторов соответственно, второй вывод первого, третьего и пятого демпферов тока соединен с катодом первого, третьего и пятого встречных диодов, а второй вывод второго, четвертого и шестого демпферов тока соединен с катодом второго, четвертого и шестого встречных диодов, первый, второй, третий, четвертый, пятый, шестой демпферы напряжения, первый и второй, третий и четвертый, пятый и шестой из которых соединены между собой последовательно, первый вывод первого, третьего и пятого демпферов напряжения соединен с катодом первого, третьего и пятого встречных диодов и объединены между собой и подключены к первому входу ограничителя напряжения и к плюсовой шине источника питания, вторые выводы второго, четвертого и шестого демпферов напряжения соединены с анодами второго, четвертого и шестого встречных диодов, объединены между собой и подключены к минусовой шине источника питания и ко второму входу ограничителя напряжения, бланкировщик, последовательно соединенные трехфазный мост и фильтр помех, выход которого соединен со входом порогового устройства, выход которого соединен со входом бланкировщика, выход которого соединен с первыми входами двухвходовых логических элементов «И», вторые входы которых и входы вторых выходных каскадов являются входами формирователя импульсов тока, первичная цепь каждого датчика тока соединена с первым выводом второго, четвертого и шестого демпферов напряжения и является одним из выходов формирователя импульсов тока, а вторичная цепь каждого датчика тока соединена с входом трехфазного моста соответственно.

| АВТОНОМНЫЙ ИНВЕРТОР НАПРЯЖЕНИЯ | 2009 |

|

RU2403667C1 |

| ИНВЕРТОР НАПРЯЖЕНИЯ | 2001 |

|

RU2210152C2 |

| Транзисторный инвертор | 1991 |

|

SU1786623A1 |

| US 8384298 B2, 26.02.2013 | |||

| JP S6359774 A, 15.03.1988 | |||

| Транзисторный инвертор | 1990 |

|

SU1757069A1 |

Авторы

Даты

2023-05-18—Публикация

2022-11-01—Подача