Изобретение относится к области технологии производства полупроводниковых приборов, в частности к технологии изготовления тонкопленочного транзистора с пониженным значением дефектности.

Известен способ изготовления тонкопленочного транзистора [Пат. 5384271 США, МКИ H01L 21/24] с пониженным током выключения транзисторов. Для снижения тока при выключенном состоянии тонкопленочного транзистора на аморфном кремнии проводятся последовательно следующие этапы: пассивация области канала, жидкостное травление в HF, сухое реактивное ионное травление, повторное жидкостное травление в HF, обработка в очищающем растворе, отжиг. В таких приборах из-за нетехнологичности процесса формирования аморфного кремния образуется большое количество дефектов, которые ухудшают электрические параметры приборов.

Известен способ изготовления тонкопленочного транзистора [Пат. 5326989 США, МКИ H01L 21/78] используемая в качестве нагрузочного транзистора в составе элемента статического ЗУПВ. Полевые транзисторы изготавливаются на изолирующем слое, покрывающим Si подложку. С целью увеличения воспроизводимости толщины активного канального Si-слоя последний предохраняется от окисления защитным слоем поликремния, аморфном кремнии или Si3H4. Поверх защитного слоя наносится промежуточный слой стекла, растекающийся с увеличением температуры.

Недостатками этого способа являются:

- высокая дефектность;

- высокие значения токов утечек;

- низкая технологичность.

Задача, решаемая изобретением: снижение дефектности, обеспечение технологичности, улучшение параметров приборов, повышение качества и увеличение процента выхода годных.

Задача решается формированием слоя аморфного кремния, после предварительной обработки Si подложки пучком нейтрализованных ионов Аг в сверхвысоком вакууме с последующим отжигом при температуре 600°С в течение 60 мин в камере, нанесением электронно-лучевым методом со скоростью 0,5 нм/с на Si подложки, нагретые до 100°С при давлении 2*10-7Па, с последующим уплотнением слоя аморфного кремния при температуре 450°С.

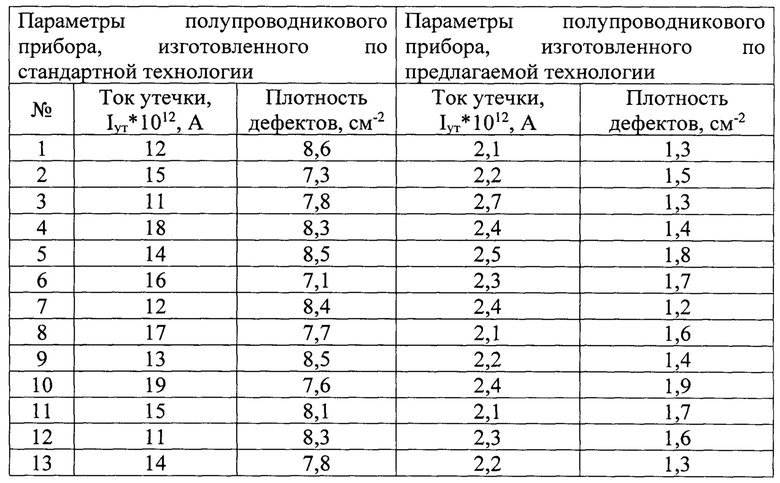

По предлагаемому способу были изготовлены и исследованы полупроводниковые приборы. Результаты обработки представлены в таблице.

Технический результат: снижение дефектности, обеспечение технологичности, улучшение параметров приборов, повышение качества и увеличение процента выхода годных.

Экспериментальные исследования показали, что выход годных структур на партии пластин, сформированных в оптимальном режиме, увеличился на 20,3%.

Стабильность параметров во всем эксплуатационном интервале температур была нормальной и соответствовала требованиям.

Предложенный способ изготовления тонкопленочного транзистора формированием слоя аморфного кремния, после предварительной обработки Si подложки пучком нейтрализованных ионов Аг в сверхвысоком вакууме с последующим отжигом при температуре 600°С в течение 60 мин в камере, нанесением электронно-лучевым методом со скоростью 0,5 нм/с на Si подложки, нагретые до 100°С при давлении 2*10-7Па, с последующим уплотнением слоя аморфного кремния при температуре 450°С, позволяет повысить процент выхода годных приборов и улучшить их надежность.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОГО ТРАНЗИСТОРА | 2014 |

|

RU2571456C1 |

| Способ изготовления тонкопленочного транзистора | 2023 |

|

RU2819702C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОГО ТРАНЗИСТОРА | 2012 |

|

RU2522930C2 |

| Способ изготовления полупроводниковой структуры | 2022 |

|

RU2796455C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА | 2014 |

|

RU2581418C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА | 2011 |

|

RU2466476C1 |

| Способ изготовления тонкопленочного транзистора | 2020 |

|

RU2754995C1 |

| Способ изготовления тонкопленочного транзистора | 2018 |

|

RU2696356C1 |

| СПОСОБ ОТЖИГА ПОЛУПРОВОДНИКОВЫХ СТРУКТУР | 2014 |

|

RU2567117C1 |

| Способ изготовления силицида титана | 2020 |

|

RU2751983C1 |

Изобретение относится к области технологии производства полупроводниковых приборов, в частности к технологии изготовления тонкопленочного транзистора с пониженным значением дефектности. Способ изготовления тонкопленочных транзисторов согласно изобретению включает предварительную обработку Si-подложек пучком нейтрализованных ионов Аr в сверхвысоком вакууме с последующим отжигом при температуре 600°С в течение 60 мин в камере и формирование слоя аморфного кремния электронно-лучевым методом со скоростью 0,5 нм/с на Si-подложках, нагретых до 100°С при давлении 2⋅10-7 Па, с последующим уплотнением слоя аморфного кремния при температуре 450°С. Изобретение обеспечивает снижение дефектности, повышение технологичности, улучшение параметров приборов, повышение качества и увеличение процента выхода годных. 1 табл.

Способ изготовления тонкопленочных транзисторов, включающий процессы формирования контактных окон, активных областей полупроводниковых приборов и электродов к ним, отличающийся тем, что после предварительной обработки Si-подложек пучком нейтрализованных ионов Аr в сверхвысоком вакууме с последующим отжигом при температуре 600°С в течение 60 мин в камере формируют слой аморфного кремния электронно-лучевым методом со скоростью 0,5 нм/с на Si-подложках, нагретых до 100°С при давлении 2⋅10-7 Па, с последующим уплотнением слоя аморфного кремния при температуре 450°С.

| US 5326989 A, 05.07.1994 | |||

| US 5384271 A, 24.01.1995 | |||

| Способ изготовления тонкопленочного транзистора | 2020 |

|

RU2754995C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОГО ТРАНЗИСТОРА | 2012 |

|

RU2522930C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНЫХ ТРАНЗИСТОРОВ | 1992 |

|

RU2035800C1 |

Авторы

Даты

2023-06-23—Публикация

2022-06-10—Подача