(54) УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и передачи информации | 1983 |

|

SU1140144A1 |

| Устройство для приема и передачи информации | 1984 |

|

SU1251149A2 |

| Устройство для приема информации | 1983 |

|

SU1104572A1 |

| Устройство для приема информации | 1979 |

|

SU830488A2 |

| Устройство для приема и дешифрации команд | 1987 |

|

SU1476510A1 |

| Устройство для приема и передачи информации | 1986 |

|

SU1372347A1 |

| Устройство для передачи и приема сигналов | 1981 |

|

SU1068051A3 |

| Устройство для приема и передачи информации | 1988 |

|

SU1536422A1 |

| Устройство для приема и передачи информации | 1986 |

|

SU1325545A1 |

| Устройство для передачи и приема информации | 1985 |

|

SU1257688A2 |

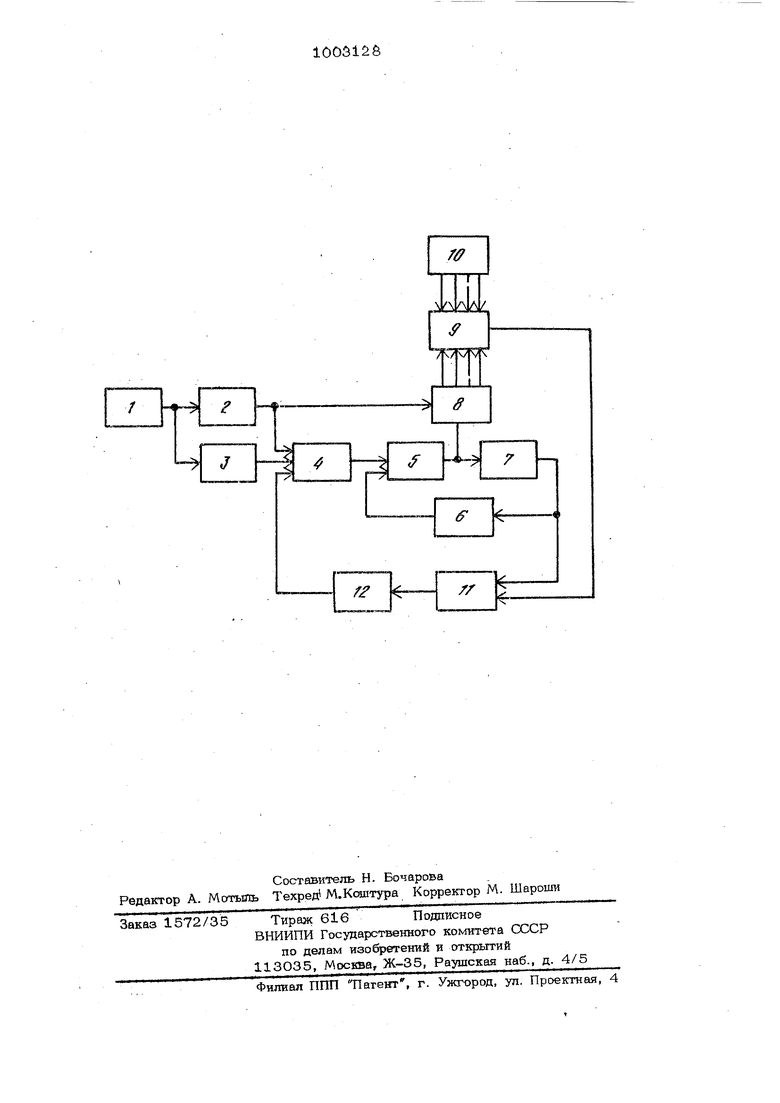

Изобретение относится к приему и передаче информации и может быть использовано для приема информации, переде вае- мой в двоичном коде, в системах с большим количеством приемников и передатчиков, рабатакших в обшем канале связи. Известны устройства для записи инфор мации, содержащие приемник, вход которо го соединен с входной клеммой устройства, выход приемника подключен к входам селектора кодового признака единицы и селектора кодового признака нуля 11 . Надоотвггки устройства - невозможность обеспечить запись сигналов кода в условиях помеж и конструктивная сложность устройства в -целом, что снижает надежность его функционирования. f Наиболее близким техническим решением к предлагаемому является устройство для приема информации, которое содержит приемник, выход которого подкшочен к входам селекторов кодового признака едвнкць и нуля, а уск. выходы - к первому и второму входам элемента ИЛИ, выход последнего соединен с первым входом элемента И и тактовым входом регистра сдвига, чей информационный вход подключен к вькоду селектора кодового признака едишшы, а группа его выходов - к первой группе входов блока сравнения, вторая группа входов которого соединена с выходами блока памяти, а выход сравнения подключен к D -входу триггера, С-вход которого подсоединен через элемент задержки к входу счетчика, а выход - к третьему входу элемента ИЛИ, второй вход элемейта И подключен к выходу счетчика, а его выход соеjjHHeH с-входом упомянутого счетчика 2. Недостатком известного устройства является низкая помехоустойчивость, обу/словленная возможностью прохождения сигнала помеки на тактовый вход регистра сдвига в промежутке времени, равном времени запаздывания сигнала Запрет на третий нсод элемента ИЛИ по цепи: элемент И - счетчик - элемент задерж ки - триггер - третий вход элемента ИЛИ, и как следствие этого искад ение информации D -входе триггера. Цепь изобрете1гая - повьшюние помехоустой щвости устройства. Постав-ленная пель цостигается тем, что в устройство для приема информации, содержащее приемник, выход которого соединен с входсами селектора единицы и селектора нуля, выход которого соединен с первым входом элемента ИЛИ, выход элемента ИЛИ соединен с первым входом первого элемента И, выход которого соед1инен с аходом счетч 1к выход селектора едишплы соединен с вт рым входом эле 11еита ИЛИ и информациош1ьг.1 входом регистра, сдвига, выходы которого соедпнепы с первы1 /п: Входа ми блока сравнеш-ш, вторые входы кото рого соеданены с вькодакт блока памя-Г15, введены формирователь и:уЛ1ул:ьсов, второй элемент И и элемент НЕ. выход счетчика соединен непосредственно с перным входом второго элемента И и через элемент- НЕ: с вторым входом первого элемента И, выход которого со динен с тактирующим В7содом регис гра сдвига, выход блока сравнения соешпюн с вторым входом второго элемента И, выход которого через фор,«трователь импугп ов соеШ1Т1ен с Tpei-bHM входом элемента ИЛИ. На чертеже изобрал ена блок-схема устройства для приема информации. Устройство содержит приемник 1, селектор 2 единШ-Ш, селектор 3 нуля, э.т семент ИЛИ 4, первый элемент И 5, элемент НЕ б, счетчик 7, регистр 8 сдвига, блок 9 сравнения, блок 10 памя ти, второй элемент И 11, формирова-тель 12 и /шулъсоЕ. Устройство работает следующим образом. Перед приемом очередной кодовой комбиншгл- регистр 8 сдвига, счетчик 7 и форм1фователь 12 импульсов устанавливаются в исходное состояние, т.е. на ИХ выходах устанавливаются уро ни логического нуля. При этом, на втор входе первого элемента И 5 устанавливается уровень логической единицы, т.е разрешакяций для этого элемента. Число (h) выходных сигналов регисТ- ргЭ 8, а также число выходных, сигналов с вгжода блока 10 памяти и появление на выходе счетчика 7 уровня логическо едищщы равно пюлу регистров, необход ых для записи в двоичной форме числа риемников, подключенных к общему аналу связи (не по1шзан). Выходные сигналы селекторов 2 и 3 меют значение логического нуля. Переаваемые сигйалы принимаются приемниом 1 и поступают на входы селекторш и 3. При появлении в каком-либо разряде кода единицы на выходе селектора 2 диницы устанавливается уровень логиеской единицы, а на выходе селектора 3нуля сохраняется значение логического нуля. Аналогично, при появлении кода НУЛЯ, на выходе селектора 3 устанавливается уровень логической единицы, а па выходе селектора 2 едиьги.ды сохраняется значение логического лупя. Сигналы с выходов селекторов 2 л 3 далее на входы элемента ИоТИ 4, причем сигналы с выхода селек тора 2 единтзды подаются также на информационный вход регистра 8 сдвига па тактовый вход которого, Q тахсн е на вход счетчика 7 и шульсов постзпают сигна/ш с выкода элемента ИЛИ 4 через первый элемент И 5. -Еисло такто-вых И1утульсов, проходящих с выхода эл-з мента ИЛИ 5 на тактовый вход регисг-ра 8 сдвига, ограничено. Действительно, уровещ, логического HJTIH на выходе счетчика 7 сохрат-юется до прихода п-го числа икшульсов. При достиже1-ти --исла П на выходе счетчика 7 устанявливает-ся уровень логической единицы, который nocTjTiaeT iia вход элемента НЕ 6. 13 результаге на его вьткоце появляется уфовень логического : -jin, блокирузощий логический .ет)г М о для прохождентгя через него тавггорзыл гП-лпутесов. Такнг-л обр&зом, достигается повьпление помехоустойчивости устро йства. Сигналы, пост5Т1ившие на тактовый вход регистра 8 , продвигают сигналы, постутгаюшие па информапгионный вход, с выхода селектора 2 единицы. При этом, информашш, записанная- на предыд тцем шаге в регистр 8 сдвига, переписывается в следующий по порядку старший разряд рогютра 8 при приходе на его тактовый вход нового икшуттьса, а информация на группе выходов регистра 8 сдвига в процессе приема кодовой комбинации поэтому непрерывно меняется. Блок 9 сравнет1я ос ацествляет непрерывное сравнение информации, записа|шой в блоке 10 памяти, с вновь

поступающей с выходов регистра 8 сдвига. После окончания приема при совпадении -информации, записанной на выходе регистра , 8 сдвига с информацией, записанной в блоке 1О памяти, на выхо де блока 9 сравнения появлявтся сигнал с Уровнем логической едишпхы, поступающий на первый вход -второго элемента И 11. После завершения приема кодовой группы на выходе счетчика 7 появляется скгнал с уровнем логической единицы, который,как указывалось выще, после инвертирова1гая элементом НЕ 6 поступает на второй вход первого элемента И 5 и запрещает прохождение икш лхлов с выхода элемента ИЛИ 4 на тактовый вход регистра 8 сдвига.

Кроме того, сигнал с уровнем логической с выхода счетчика 7 подается на ваюрой нкод второго элемента И 11, разрешая, тем, самым, прохождение сигнала с выхода блока 9 сравнения на вход формирователя 12, который, формируя сигнал с уровнем логической ед 1нины, запрещает прием новой кодовой группы до заданного мамента времени, воздействия на третий вход элемента ИЛИ 4.

Г1редла. устройство ггс-зноляет noBMQtfTb пом8 :о;5стойчивость уг:т1;ойствз для np Tpv-a 11 Ь-;;рмащш И, спедо ;:;Гб;1Ь ю jc ib его функционирования. Фор .-; у л а изобретения

Усгройсгво для приема информэлии, содержащее прИ9- ниК; выход которого

соединен с входами селектора единицы и селектора нупя выход которого соединен с первым входом элемента ИЛИ, выход элемента ИЛИ соедтгаен с первым входом первого элемента И, выход котснрого соединен с входом счетчика, выход ceneiCTOpa единицы соединен с вторым входом элемента ИЛИ и информационньпу ш:одом регистра сдвига, выходы которого соединены с первыми входа га блока сравнения,- вторые входы которого соединены с выходами блока памяти, о -т л и ч в ю щ е е с я .тем, что, с целью пoBJ шeния помех о устойчивое TII устройства, в него введены формирователь импульсов, второй элеме1гт И и Элемент НЕ, выход счетчика соединен непосредственно с первым входом второго элемента И и через элемент НЕ с вторым входом первого элемента И, выход которого соед11нен с -тахсгирующим аходом регистра сдвига, выход блока сравнетш соединен с вторым входом второго элемента И, выход которого через фop ПIpoвaтeль ик-туяьсов соединен с третьим входом элемента ИЛИ.

Источники ин41ормащга, прин-ятые во внимаш1е при экспертизе

.. Авторское свидетельство СССР № S3O488, кл, С, 08 С 19/28, 1979.

(лу-- члчш)

Авторы

Даты

1983-03-07—Публикация

1981-11-25—Подача