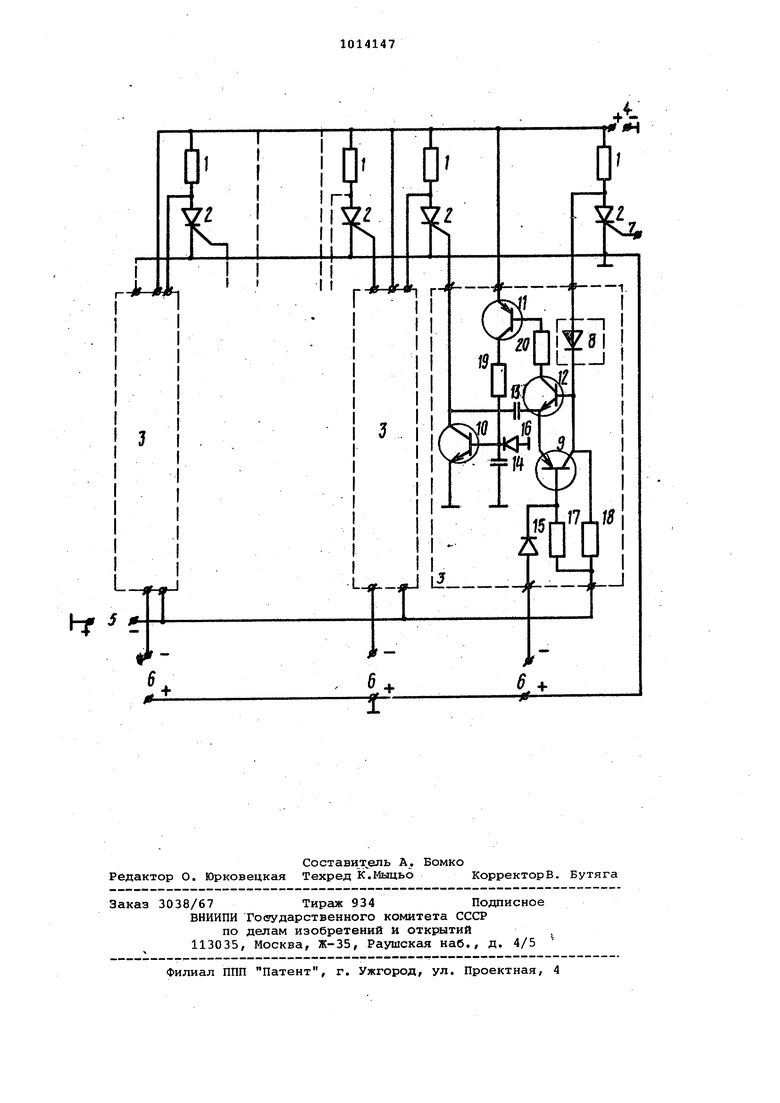

4 Изобретение относится к сильноточной импульсной техике, а точнее: к устройствам бесконтактной коммута ции . . Известен коммутатор, содержащий последовательно соединенные элемен временной задержки, каждый из котор выполнен на транзисторе с времязада щей RC -цепочкой 1. Недостатком устройства является узкий диапазон регулирования задерже обусловленный ограниченной скорость во сстановления время за дающего конде сатора. Известен также коммутатор, содер щий тиристоры по числу Нагрузок и времязадающие ячейки, каждая из которы содержит прибор eg-образной характеристикой, анод .которого соединен с нагрузкой времязадающей ячейки, тран.зистор база и коллектор которого через соответствующие первьой и второй резисторы соединены с шиной источника питания времязадающих ячеек, диод, включенный между базой тран зистора и источником напряжения управления, и конденсатор, у которого одна обкладка соединена с выходом данной времязадающей ячейки, а, вторая - с эмиттером транзисто- ра 2. Недостатком известного устройства является также узкий диапазон временйых задержек из-за ограниченной скорости восстановления элементов схемы. Целью изобретения является расширение диапазона временных задержек между коммутируемыми нагрузками I .Поставленная цель достигается тем, что в коммутатор, содержащий тиристоры по числу нагрузок и времязадающие ячейки, каждая из которы содержит прибор cS -образной характеристикой , анод которого .соединен с нагрузкой времязадающей ячейки, первый транзистор, база и коллектор которого череэ соответствующие первый и второй резисторы соединены с щиной источника питания времязадающих ячеек, диод, включенный между базой первого транзистора и источНИКОМ напряжения управления, и первый конденсатор, у которого одна обкладка соединена с выходом данной .времязадающей ячейки, а вторая - с эмиттером первого транзистора, введены второй, третий и четвертый транзисторы, второй конденсатор, ко торый шунтирован ограничительным диодом, третий и четвертый резисторь1, при этом эмиттер второго транзистора соединен с общей шиной неточника питания коммутатора и источника питания времязадающих ячеек коллектор ,- с выходом времязаданнцей ячейки, а база - с обкладкой второго конденсатора и выводом третьего резистора, другая обкладка второго конденсатора соединена с общей шиной источника питания времязадающих ячеек, другой вывод третье ю резистора соединен с коллектором третьего транзистора, змиттер третьего транзистора соединен с шиной источника питания коммутатора, а база - через четвертый резистор с коллектором четвертого транзистора, эмиттер которого соединен с эмиттером первого транзистора, а база - с точкой соединения катода элемента с S -образной характеристикой с коллектором первого транзистора. На чертеже приведена принципиальная электрическая схема предлагаемого устройства. Устройство содерижт нагрузки 1 и тиристоры 2 по числу коммутируемых цепей, времязадающие ячейки 3 на различные времена переключения, источник 4 напряжения для питания нагрузок 1,ИСТОЧНИК 5 напряжения для питания времязадающих ячеек, источники 6 напряжения управления и входную шину 7. Времязадающая ячейка 3 остоит из динистора ( элемента с S-образной характеристикой) 8, первого транзистора 9, второго транзистора 10, третьего транзистора 11, четвертого транзистора 12, первого конденсатора 13, .второго конденсатора 14, диода 15, ограничительного диода 16, первого резистора 17, второго резистора 18, третьего резистора 19 и четвертого резистора 20. Устройство работает следующим образом. В исходном состоянии тиристоры 2 выключены, динистор 8 включен и удерживается в этом состоянии током, протекающим от источни-ка 4 напряжения через нагрузку 1, второй резистор 18 и источник 5 напряжения. Первый транзистор 9 насглщен током, проходящим через первый резистор ; 17. Первый конденсатор 13 заряжен до напряжения источника 4 напряжения, так как сопротивление второго резистора 18 значительно больше сопротивления нагрузки 1. Транзисторы 10-12 находятся в закрытом состоянии. I При подаче импульса на входную шину 7 включается тиристор 2. При это. напряжение на аноде динистора 8 времязадающей ячейки 3 становится равным нулю и он запирается, так как к его катоду приложено запирающее напряжение первого конденсатора 13 через эмиттерный переход четвертого транзистора 12. С этого момента начинается отсчет времени включения первой нагрузки 1. Величина задержки определяется временем перезаряда первого конденсатоpa 13 током эмиттера первого транзистора 9, равным сумме токов, текущих через первый и второй резисторы 17 и 18. При этом ток перезаряда первого конденсатора замыкается через открытый переход коллектор - база второго транзистора 10 и второй конденсатор 14, шунтированный ограничительным диодом 16.

Первый конденсатор 13 стремится перезарядиться на напряжение источника 5 напряжения. Однако когда напряжение на нем, а следовательно, и на базе первого транзистора 9 достигнет величины напряжения управления,откроется диод 15. При этом первый транзистор 9 начнет закрываться, что вызовет резкое увеличение напряжения на его коллекторе. Это напряжение прикладывается к катоду динистора 8, вследствие чего он включается.При включении динистора 8 напряжение на базе четвертого транзистора 12 снижается до величины напряжения заряда первого конденсатора 13, которое определяется напряжением источника 6 напряжения управления. Далее происходит открывание четвертого транзистора 12 и перезаряд первого конденсатора 13 по цепи исто1ника 4 напряжения, нагрузки 1, динистора 8 и цепи управления следующего тиристора 2. При этом второй транзистор 10 будет заперт.

В результате протекания тока через следующий тиристор 2 происходит его включение и выключение первого тиристора 2. С этого момента заканчивается время включения одной нагрузки 1 и начинается время включения другой нагрузки 1.

Второй, третий и четвертый транзисторы . служат для ограничени по длительности импульса управления на последукяцем тиристоре 2.

Для получения большого времени включения предыдущей нагрузки 1 необходимо обеспечить необходимую постоянную времени заряда первого конденсатора 13. Когда напряжение на этом конденсаторе станет положительным и достигнет такой величины при которой откроется второй транзистор 10, ток перезаряда первого конденсатора 13 начнет протекать через переход коллектор - эмиттер второго транзистора 10 на общую Шину, минуя цепь управляющего электрода тиристора 2 следующей ячейки.

В предложенном устройстве время перезаряда первого конденсатора 13 не влияет на длительность импульса запуска тиристора 2, так как эта длительность определяется временем перезаряда второго конденсатора 14.

Работа остальных ячеек коммутато ра на разщле времена переключения осуществляется аналогичным образом.

Преимуществом предложенного коммутатора является возможность пода.чи на входную шину импульса управления до окончания полного цикла ег работы. Это расширяет его функциональные возможности, так как позволяет включать несколько назтрузок одновременно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реле времени | 1982 |

|

SU1018166A1 |

| Ячейка временной задержки импульсов | 1980 |

|

SU945967A1 |

| Коммутатор | 1984 |

|

SU1233273A1 |

| Устройство задержки | 1980 |

|

SU917232A1 |

| Генератор импульсов | 1983 |

|

SU1102024A1 |

| Трехпозиционное устройство | 1971 |

|

SU449334A1 |

| Устройство последовательной коммутации нагрузок | 1981 |

|

SU1003340A1 |

| Многофазный мультивибратор | 1978 |

|

SU744925A1 |

| Однотактный распределитель | 1976 |

|

SU598250A1 |

| Генератор импульсов | 1980 |

|

SU868983A1 |

КОММУТАТОР, содержащий тири с торы по числу нагрузок и времязадающие ячейки,каждая из которых содержит с S-образиой характеристикой, анод которого соединен с нагрузкой времязадающей ячейки, первый транзистор, база и коллектор которого через соответствующие первый и второй резисторы соединены с шиной источника питания времязадакяцих ячеек, диод включенный между базой первого транзистора,и источником напряжения управления, и первый конденсатор, в котором одна обкладка соединена с выходом данной времязадающей ячейки, а другая - с ;эмиттером первого транзистора, о т и ч а ю щ и и с я тем, что, с це-;лью расигарения диапазона временных задержек между коммутируемыми нагрузками, в нетчэ введены второй, третий и четвертый транзисторы, второй конденсатор, который шунтирован ограничительным диодом, третий и четвертый резисторы, при этом эмиттер второго транзистора соединен с общей шиной : источника питания коммутатора к ис-; точника питания времязадающих ячеек коллектор - с ш:1ходом премязадаю щей ячейки, а база - с обкладкой второго конденсатора и выводом третьего резистора, другая обкладка второго конденсатора соединена о общей; шиной источника питания времязадающих ячеек, другой вывод третьего резисто-, ра соединен с коллектором третьего | транзистора, эмиттер третьего транл; (Л зистора соединен с шиной источника 1 питания кок№1утатора, а база через четвертый резистор - с коллектором четвертого транзистора, эьтаттер ко8 С .торого соединен с эмиттером первого .транзистора, а база - с точкой сб-единения катода элемента с Sгобразной характеристикой с коллектором : первого тра нзистора. .

ii

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 225327, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| 0 |

|

SU359757A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-04-23—Публикация

1981-02-06—Подача