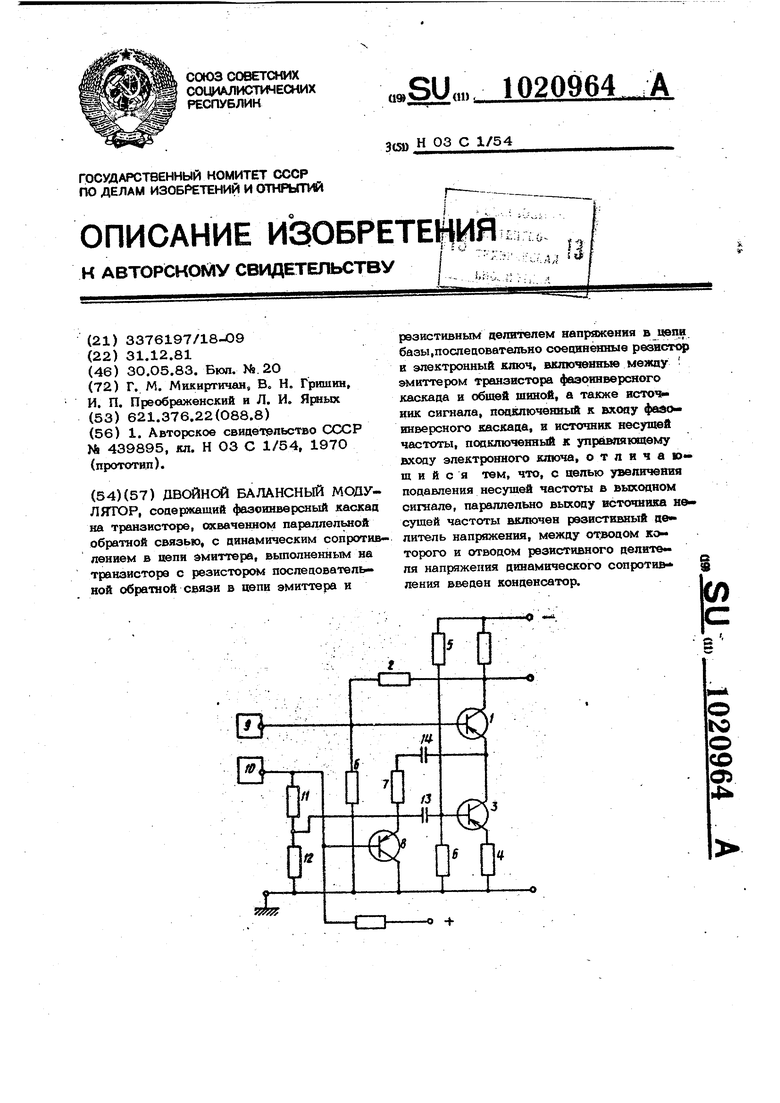

Изобретение относится к радиотехник ке и может исполЕззоваться цпя формирования амппитуано-моцупированных сигналов в различных рааиотехнических уст ройствах. Известен аврйной балансный моауля- тор, содержащий фазоииверсный каскад н транзисторе, охваченном параллельной об ратной связью, с динамическим сопроти& лением в цепи эмиттера, вьшолнениым на транзисторе с резистором послеаова тельной обратной связи в цепи эмиттера и резистивным делителем напряжения в цепи базы, последовательно соединенные резистор и электронный ключ, включенные между эмиттером транзистора фазоинверсного каскада и общей шиной, а также источник сигнала, подключенный к входу фазоинверсного каскада, и источ ник несущей частоты, подключенный к управляющему входу электронного клю- ча ly. Однако в выходном сигнале известног двойного модулятора несущая частота подавляется недостаточно и ее остаток присутствует на выходе в виде узких импульсов, возникающих в моменты переключения ключа в такт с несущей частотой. Цель изобретения - увеличение igoдавления несущей частоты в выходном; сигна те. Указанная цель достигается тем, что в двойном балансном модуляторе, содержашэм фазоинверсный каскад на транзис- торе, охваченном параллельной обратной связью, с динамическим сопротивлением в цепи эмиттера, выполненым на трав зисторе с резистором последовательной обратной связи в цепи эмиттера и разно- тивным делителем напряжения в цепи базы, последовательно соединенные резистор и электронный ключ, включенные меж ду эмиттером транзистора фазоинверсного каскада и общей щиной, атакже источник сигнала, подключенный к входу фазоин- версного .каскада, и источник несущей частоты, подключенный к управляющему входу электронного ключа, параллельно выхоау источника несущей частоты вклют чен резистивный делитель напряжения, между отводом которого и отводом резистивного делителя напряжения дина-, мического сопротивления введен ксшцен- сатор. На чертеже представлена п{шниип « альная электрическая схема двойного балансного модулятора. Двойной балансный модулятор содержит фазоииверсный каскад на транзисторе 1, скваченном параллельной обратной связью, образованной резистором 2, с динамическим сопротивлением в цепи эмиттера, вьъполненным на транзисторе 3 с резистором 4 последовательной обратной связи в цепи эмиттера, и резистивным делите-, лем на резисторах 5 и 6 в цепи базы, резжгтор 7, алектронный ключ 8, источи ник 9 сигнала, источник Ю несущей частоты, резистивный делитель на резисторах 11 и 12, конденсатор 13. Устройство работает следующим образом.. Ti H3HCTOp электронного ключа 8 для получения лучщих ключевых свойств ио- пользуется в инверсном включении. На базу транзистора с выхода источника 1О несущей частоты поступает несущая частота, представляющая собой импульсную последовательность прямоугольной формы. На выходе электронного ключа 8 (эмиттере транзистора 1) постоянное напряжение питания отсутствует наличия конденсатора 14, Под действием прямоуголь ньсх импульсов, поступающих на базу транзкстора электрсяшого ключа 8, на его эмиттере (выходе) имеет место такая же далпульсная последовательность, но с очень маленькой амплитудой (несколько десятков микровольт). Наряду с этим на эмиттере транзистора электронного ключа 8 во время переключения его имеют место узкие (продифференцированные) импульсы с амплитудой несколько десятков милливольт (т.е. в 1ООО раз больше). Эти импульсы возникают из-за паразитных емкостей транзистора электронного ключа 8, поступают далее на выход двойного балансного модулятора через резистор 7, ксжденсатор 14 и цепь эмиттер-коллектор транзистора 1 и являются причиной того, что несущая частота подавляется на выходе двойного баланса модулятора не полностью, а только на 4О дБ, т.е. в 100 раз. Для дополнительного подавления несущей частоты параллельно вькоду ис- точника 10 несущей частоты включен резистивный делитель напряжения на резисторах 11 и 12, уменьшающий напряжение импульсов несущей частоты. Последние через дифференди отйщую цепь - конденсатор 13 - резисторяы 5 и 6 поотупают на базу транзистора 3, создаюшегр динамическое сопротивление в цепи эмиттера транзистора 1. Продифференцирован- нью импульсы инвертируются транаистором 3 и на эмиттере транзистора 1 склааываются в противофаэе с узкими вмпульсами, поступающими от транзисто ра электронного ключа 8 по цепи - ре- зистор 7 - конденсатор 14. Параметры анфференцируюшей цэпи выбираются так, что&д в результате вь1читания остаток сигнала бьш по возможности близким к нулю. В результате, leta выхоое ОБОЙНОГО балансного модулятора обеспечивается цопопнитвльное подавление несущей частоты еще на дБ, т.е. ао 60-QO цБ. Таким образе л, в прецпагаел ом авойном бешансном модуляторе выполненное s |На транзисторе 3 динамическое сопротнв{пение используется еще и в новом качест ве как фазоинвертируюшее и фаэнруюшее устройство для компенсации очень узких импульсов, длительность которых прибл 0 зителыю в 10О раз короче длительности периода импульсов нес -дей частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двойной балансный модулятор | 1970 |

|

SU439895A1 |

| Импульсный стабилизатор напряжения постоянного тока | 1978 |

|

SU752286A1 |

| Ключевой стабилизатор напряжения постоян-НОгО TOKA | 1978 |

|

SU845146A1 |

| Функциональный генератор | 1979 |

|

SU788348A1 |

| Двойной балансный модулятор | 1979 |

|

SU843160A1 |

| Квадратор | 1978 |

|

SU736126A1 |

| БАЛАНСНЫЙ МОДУЛЯТОР | 1973 |

|

SU362405A1 |

| Трансформаторный широтно-импульсный модулятор | 1985 |

|

SU1383475A1 |

| ПАРАЛЛЕЛЬНЫЕ АПЕРИОДИЧЕСКИЕ УПЧ | 1993 |

|

RU2118063C1 |

| БАЛАНСНЫЙ СМЕСИТЕЛЬ | 1989 |

|

RU2017321C1 |

двойней БАЛАНСНЫЙ МОДУnffTOP, содержащий фазоинверсный каскад на транзисторе, окваченном параллельной обратной связью, с аинамическим сопротиа лением в цепи дмиттера, выполненным на транзисторе с резистором послецоватепь ной обратной связи в цепи эмиттера и peзиcтивньnvi делителем напр$1жения в кепи базы,послеаовательно соецкненные резвскф в электронный ключ, вклю юнные между эмиттером транзистора фазоинверсяого каскада и обшей шиной, а также источ ник сигнала, подключенный к входу фаао инверсного каскада, и источник несушей частоты, подключенный к управляющему виоиу электронного ключа, о т л и ч а ю ш и и с я тем, что, с целью увеличения подавления несушей частоты в вьссодном сигнале, параллелысо выходу источника не сушей частоты включен резистивный де литель напряжения, между отводом кс торого и отводсж разистивного делите- ля напряжения динамического сопротив лення введен конденсатор. (Л О со 05 4iak

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Двойной балансный модулятор | 1970 |

|

SU439895A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-05-30—Публикация

1981-12-31—Подача