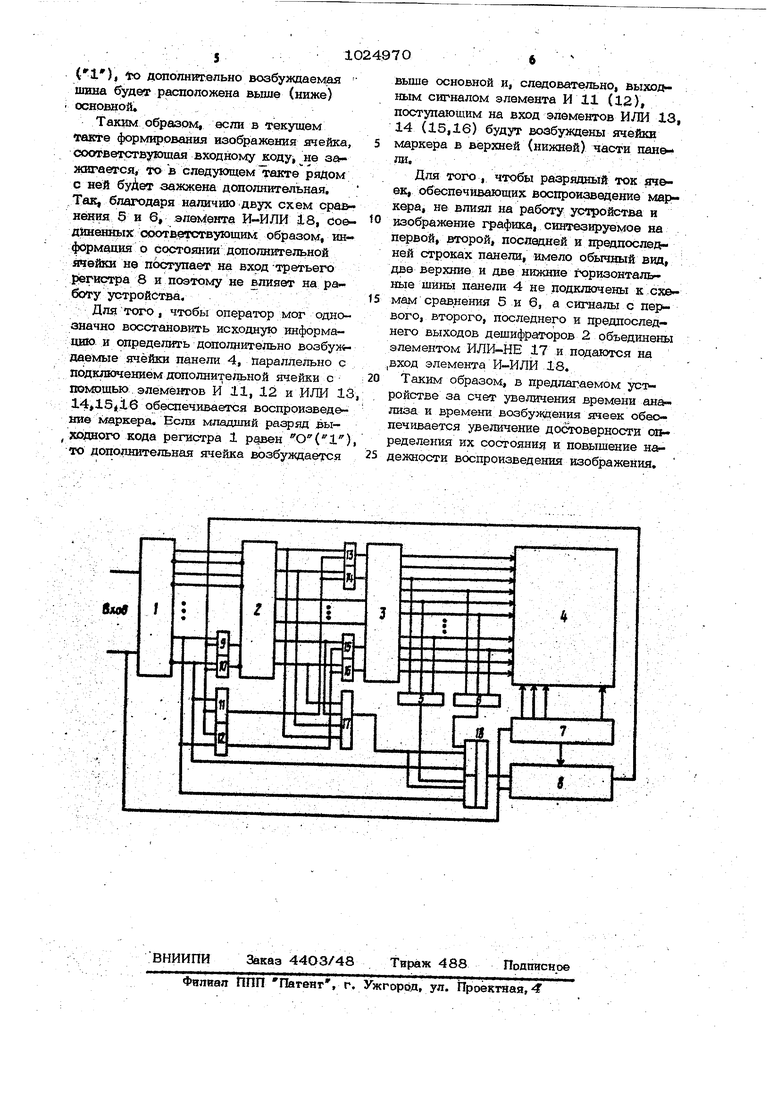

Изобретение относится к устройст вам отображения информации и предназначено для воспроизведения графичео кой информации на газоразрядной ЩЗД1Н каторной панели. Известно устройство для индикадан, содержащее газоразрядную щщикатрркую панель, блоки коммутации, .пороговый элемент, схему сравнения |lj , Амплитуда управляющих имщ льсов для индикаторной панели в этрм устройстве выбирается в зависимости Ьт среднего по множеству времени аапаадывания зажигания ячеек. Если в ajXJOepсе воспроизведения графической инфор мааии с помощью этогр устройства одна или несколько ячеек участвующих в cmirese изображения, не зажигаются;, то ячейки, подключаемые неиосре|1етвенн после них, оказываются в худших условиях и поэтому также зажигаются шна деншо. Тогда схема сравнения выр. ботает сигнал, который обес1|ечйт увеш чение амплитуды управляющих иьлйудьсов на всех электродах панели. Йэ- аеа- чительных разбросов нахфяжения бозник- новения разряда увеличение ампли уды управляющих импульсов выгащает JjOJ нов зажигание ячеек, имеющих низкое напряжение зажигания. Таким образом, недостатком устройства является нады-. сокая надежность формирования изображен11яНаиболее близким к изобретению явд ется устройство для индикации, содержащее схему сравнения, газоразрядную индикаторную панель, шины которой додклв чены к блоку коммутации к второму регистру, связанному с входом устройства и первым регистром. Прямой и инверсный выходы младшего этого регистра подключены через первый и второй элементы ИЛИ, остальные выходы непосредственно к .входам дешифратфа. Первый, второй, предпоследний и послед ний выходы дешифратора подсоединены через третий , четвертый, nsiivtu и шеотой элементы ИЛИ, а остальные непосредственно к входам блока коммутации. Другие входы третьего, четвертого и пятого, шестого элементов ИЛИ подклххчены соответственно к выходам первого и второго элемешчж И, одни входы которых подключены к пряьвому в инверк ному входам младшего разряда, а вторые - к выходу схемы сравнения j2j . В этом устройстве Щ)И поакпюче шш очередной ячейки схемой яравненвя осуществляется анализ состошшя боэ10 буяодаемой ячейки и при невозникнов&нни в течение заданного интервала времени разрядного тока производится возбужи&Ше дополнительной ячейки, расположенной выше или ниже её. Так как шреде - деление состояния ячейки прои;зводится в процессе ее подключения, то формирование сигнала для возбуждения дойолн тельной ячейки производится с задержкой о(гносительно йодключения столбяа. Для увеличения достоверное полученных; ресзу/шгатов время очрводимое на анализ х стояш1я ячейка, далнющееся частью времени подключений , необход о выбирать возможно большим. длительность подключении каждого столбца ограничивается крт еской частотой мельканий и поэтому обеспечить достоверное определите состояния ячейки весьма трудно. Кроме того, дополнетельно возбуждаемые ячейки в уст рОйстве имеют более низкую надежность зажигания, чем схл-альные, так как Hai ряженне возбужде1шя на нее подается лзшиь в течааие части времени подключения столбца, причем с задержкой относ тельно момента гашения ячейий в предыдушем стол&1е.. Таким образом, недостатком устройстjsa является невысокая надежность воо1фОизведения информашга. Цель изобретения - повышение надежности воспроизведения информации. Для этого в устройство для индикации, содержащее матричную индикаторную панель, вертикальные шины которой соедянёны с выходами первого регистра, а горизонтальные шины - с выходами блока коммутации, первую схему сравнения, второй регистр, прямой и инверсный вьь зоодь младшего разряда которого соед нень с первыми входами первого и второго элементов ИЛИ и элементов И, а остальные выходь второго регистра соединены с входами дешифратора, выход первого Э1юмента И роединен с первыми входами третьего и четвертого элеменн тов ИЛИ, а выход второго элемента И соединен с первыми входами пятого и шестого элементов ИЛИ, вторые входы . элементов ИЛИ соединены с управляюшими выходами деши4фатсфа, а выходы элементов ИЛИ соединены с одними из входов блока коммутации, другие входыкоторого соединены с информационными выходами дешифратора вход нового рёгис гра соединен с первым входом вто рого регистра и является тактовым входом устройства а второй вход второго регистра является информацисжным входом устройства, введены вторая схема . сравнения, ттретий регистр, элемент ИЛИ-Н и элемент , первый и четвертый . входы элемегага И-ИЛИ соединены с выходами схем сравнения, второй и пятый входы в с выходами элёмекга ИЛИ-НЕ, а третий и шестой входы соедйнень соответственно с .ицверо ным и прямым выходами младшего разр:яда второго регистра, входы лервой и второй схем сравнения соединены соответственно с нечетными и чет ными горизонтальными шинами матричной индиасаторной панели, выход элеме 1 та И-ИЛИ соединен с первым входом третьего регистра, второй вход которого является тактовым входом устройства а выход соединен с вторыми входами пер вого и второго элементов ИЛИ и элементов И, входы элемента ИЛИ-НЕ соедине ны с управляющими выходами дешифратора. На чертеже представлена структурная схема предлагаемого устройства, Устройство содержит второй регистр выходы которого подключены к дешифр тору 2. Блок коммутации 3 обеспеч вает возбуждение необходимых горизо тальных шин (газоразрядной) матричной индикаторной панели 4, связанных с пер вой 5 и второй 6 схемами сравнения, Первый регистр 7 обеспечивает последовательное переключение вертикальных шин панели 4, Выход третьего регист ра 8 подключен к входам первого 9 и /BTopoixj 10 элементов ИЛИ и первого 11 и второго 12 элементов И, Третий 13, четвертый 14, пятый 15 и шестой 16 элементы ИЛИ обеспечивают воспроизвелдение на панели 4 маркера. Первый, второй, последний и предпоследний вь ходы дешифратора 2 подкгаочены к входам элемента ИЛИ-НЕ 17, Вход третьего регистра 8 подключен к выходу элемента И-ИЛИ 18,. Усугройство работает следующим образом. При поступлении на вход устройства очередного синхронизирующего импульса во второй регистр 1 записывается код очередной ординаты графика отображавмого процесса, который подается на вход дешифратора 2, Его выходной , поступая через блок коммутации 3 на шздикаторную панель 4, обеспечивает возбуждение горизонтальной шины, соответствуюшей коду, храшшому во втором регистре 1, Синхронно с восзбуждением горизонтальной шины с помошью первого регистру 7 подключается очередная вертикальная шина, В момент поступления на вход устройства следующего синхрон зирующ©гр импульса первый регистр 7 обеспечит подключение соседней . кальной шины, а выходным сигналом дешифратора 2 ю помошью блока коммутации 3 будет возбуждена строка, соответствующая текушему входному коду, записанному во второй регистр 1 и т.д. . В каждом такте формирования изображения первой 5 и второй 6 схемами сравнения осушествляется анализ COCTOSJния ячеек панели 4. При отсутствии во всех горизонтальных шинах панели 4, к которым подключены входы первой 5 и второй. 6 схем сравнения в течение заданного интервала разрядного тока на их выходах будут сформированы сигналы логической 1, которые поступают на первый и четвертый входы элемешга И-ИЛИ 18, На его второй и пятый входы подаются сигналы с прямого и инверсного выходов младшего разряда, второго регистра 1, которые обеспечат дередачу на вход третьего регистра 8 сигнала, характеризующего состояние ячеек, отно« сящихся к нечетным (четным) горизонтальным шинам панели, если в младшем разряде входного кода содержится (О ) т.е, сигнала, хара1 геризу10шего состояние ячейки, соответствующей входному кеду, Если при возбуждении ячейки в i -м столбце в течение заданного интервала через гюризонтальную шину соответствуюшего текущему значению входного кода не протекал разрядный ток, т.е. ячейка не загорелась, то на выхода элемента И-ИЛИ 18 сигнал равен 1 и перед подключением ( i -l-D-ro столбца он будет записан в - -ю ячейку треть.его регистра 8, а при подключении 1 -го столбца b следующем кадре фЬ|рмирования 213ображения ,от поступит на вход элементов ИЛИ 9,10 и И 11,12, Тогда на прямой и инверсный входы младшего раэряда дешифратора 2 поступят логические сигналы, равнь:е 1, которые обесп&чат возбуждение двух рядом располо ш ных (четной и нечетной) горизонтальных шин панели 4, Очевидно, расположение дополнительно возбуждаемой шины, опр&депяется значением выходного кода младшего разряда регистра 1, причем, если в младшем разряде содержится О

(1), to дополнкгвльно возбуждаемая шина будет расположена вьняе (ниже) основной.

Таким образом, если в текущем Такте формирования изображения ячейка, соответствующая входному jKoay, не зажигается. То в следующем такте рядом с ней буАет зажжена дополнительная. Так благодаря наличию двух схем сравнения 5 и 6, элемента И-ИЛИ 18, со&дйненнык соответствующим образом, информадвя о состоянии дополнительной ейки не пбстгупает на вход -третьего регистра 8 и поэтому не влияет на работу устройства.

Для того, чтобы оператор мог однозначно восстановить исходную информа1ШЮ. и шределить дополнительно возбу мдаемые ячейки панели 4, Параллельно с подключением дополнительной ячейки с покязшью элементов И 11, 12 и ИЛИ 13 14 lS4ie обеспечивается воспроизвед нив маркера. Если младший разряд вы/Хйдного кода регистра 1 то дополнительная ячейка возбуждается

выше основной и, следовательно, выходным сигналом элемента И 11 (12), поступающим на вход элементов ИЛИ 13, 14 (15,16) будут возбуждены ячейки

маркера в верхней (нижней) части пан&1ш, . /. , , ;

Для того , чтобы разрядный ток яч&ек, обеспечивающих воспроизведение маркера, не влиял на работу устройства и

изображение графика, синтезируемое на первой, второй, последней и хфедпоследней строках панели, имело обычный вид, : две верхние и две нижние горизонтальные шины панели 4 не подключены к схемам сравнения 5 и 6, а сигналы с Первого, второго, последнего и предпоследнего выходов дешифраторов 2 объединены элементом ИЛИ-НЕ 17 и подаются на |ВХод элемента И-ИЛИ 18., ,

Таким образом, в предлагаемом устройстве за счет увеличения времени анализа и времени возбуждения ячеек обеспечивается увеличение достоверности определения их состояния и повышение надежности воспроизведения изображения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1976 |

|

SU590783A1 |

| Устройство для отображения информации | 1986 |

|

SU1387040A1 |

| Устройство для отображения информации | 1982 |

|

SU1064293A1 |

| Устройство для индикации | 1982 |

|

SU1022213A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 2014 |

|

RU2541109C1 |

| Устройство для отображения информации | 1988 |

|

SU1501135A1 |

| Устройство для отображения информации | 1982 |

|

SU1045251A1 |

| Устройство для индикации | 1979 |

|

SU830513A1 |

| Устройство для отображения информации | 1983 |

|

SU1092557A1 |

| Устройство для отображения информации | 1981 |

|

SU960920A1 |

УСТРОЙСТВО ДЛЯ ИНДИКАШИ, срдёржатаее матричную индикаторную панель, вертикальные шины которой соединены с выходами первого регистра, а горизонтальные шишз - с вызсодами блока коммутации, первую схему cpaвнeНИИ, второй periKJTp, прямой и инверсный выходы младшего разряда которого сое динешэ с первыми входами первого к второго элементов ИЛИ и элементов И, а ос тапьные выходы второго регистра соединены с входами дешифратора, выход пер вого элемента И соединен с первыми входами третьего и четвертого элемеотов ИЛИ, а выход второго элемента И боедннен с перЕяыми входами nsftaro и щёстого элементов И ЛИ, вторые входа элементов ИЛИ соединены с управпгоопшмв выходами дешифратора, а выходы элемейгов ИЛИ соединены с одними иэ входов блока коммутации, другие входы которого соединены с информационными выходами дешифратора, вход первого регистра соединен с первым входом второго регистра и является тактовым входом устройства, а второй вход второго регистра является информационным входом устройства, о т л и ч а к щ е е с я тем, что, с целью повышения надежности, в него введены вторая схема сравнения, третий регистр, элемент ИЛИ-НЕ и элемещр И-Или, первый и четвертый входы которозто соединены с выходами схем сравнения, второй и ПЯРГЫЙ входы - с вьнходами элемента ИЛИ-НЕ, а третий и шестой входы соединены соответстве (О но с инверсдаым и прямым выходами младшего разряда второ1ч регистра, вхоС да первой и 1эторой схем сравнения соединены соответственно с нечетными и четными горизонтальными ранами матричной индикаторной панели, выход элемента И-ИЛИ соединен с первым входом tsD третьего регистра, второй вход которо4 СО го является тактовым входом устройства, а выход соединен с вторыми входами первого н второго элементов ИЛИ и элементов И, входы элемента ИЛИ-НЕ соединены с управл50опшми выходами дешифратора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для индикации | 1976 |

|

SU577549A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для индикации | 1976 |

|

SU590783A1 |

Авторы

Даты

1983-06-23—Публикация

1982-01-20—Подача