а на каждой яромежуточной станиии введевы тганейный анапизатор нарушений бипопярности и обнаружитель нарушений, бшютшрносги, входы которого соединены с выходами регенератора прямого напра&пенкя и с первым и вторым входами . линейного анализатора нарушений бипотшрности, третий вход и выходы которого соединены соответственно с хронирующим выходом регенератора прямого направления и с входами элемента памяти, а чет вергый вход пинейногчз анализатора нарушений биполярности соединен с выходом обнаружитепя нарушений биполяраости, причем регенераторы прямого и обратного направления соединены с лийейным трактом., ,

2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что анализатор нарушений биполярности состоит Из дешифратора, блока совпадения и двух решающих бпоков, первый и второй входы которых обьединвны и соединены соответственно :; с №1 ходами дешифратора и блока совпадения, при этом выход дешифратора оо&диаен с первым входом блока совпадения, на тактирующий вход дешифратора поданы тактовые импульсы, причем рой вход блока совпадения, первый и второй входы дешифратора являются со- j

ответственно первым, вторым и третьим входами анализатора нарушений бшюпярности, соответствующие входы обоих решаюших блоков являются установочными входами анализатора нарушений биполярностИ| а соответствующие выходы решающих блоков являются первым, вторым, третьим и четвертым выходами анализатора нарушений биполярности, пятым выходом которого является третий выход первого решающего блока.

3. Устройство по п. 2, о т л и ч а ю щ е ее я тем, что решающий блок состоит из стетчика, блока совпадения, блока неравнозначности и накопителя, причем первые и вторые входы блока совпадения и блока неравнозначности объединены и соединены соответственно с выходом и nepBbiM входом счетчика, а выходы блока совпадения и блока неравнозначности соединены с соотвегствук шимй входами накопителя, первый и вгорой И установочные входы счетчика являются первым и вторым и установочными входами- решающего блока, а выходы накопителя, блока неравнозначности и блока совпадения Являются соответственж) первым, вторым и третьим выходами решающего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство телеконтроля линейных трактов цифровых систем передачи | 1986 |

|

SU1374436A1 |

| Устройство телеконтроля линейных трактов цифровых систем передачи | 1985 |

|

SU1241494A1 |

| Устройство телеконтроля линейных трактов цифровых систем передачи | 1986 |

|

SU1385303A1 |

| Устройство для телеконтроля линейных трактов цифровых систем передачи | 1986 |

|

SU1345358A2 |

| Устройство телеконтроля линейных трактов цифровых систем передачи | 1988 |

|

SU1555875A1 |

| УСТРОЙСТВО ТЕЛЕКОНТРОЛЯ ДЛЯ ЛИНИЙ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ | 1996 |

|

RU2119251C1 |

| Устройство телеконтроля для обнаружения неисправного участка регенерации линий передачи цифровой информации | 1981 |

|

SU1022318A1 |

| Устройство контроля сбоев линейных регенераторов | 1981 |

|

SU1021002A1 |

| Устройство дистанционного контроля линейных регенераторов | 1975 |

|

SU562054A1 |

| Устройство для дистанционного контроля линейных регенераторов | 1983 |

|

SU1117845A1 |

1. УСТРОЙСТВО ТЕПЕКОН- ТРОЛЯ ЛИНЕЙНЫХ ТРАКТОВ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ, содержащее на каждой оконечной станции первый и второй эпементы памяти, источник информационного сигнала и генератор псевдослучайной, поспедоватепьности, выходы которых подкпючень к информационным входам первого коммутатора, выход которого подключен к первому входу управттяемого преобразователя кода, выход которого- соединен с линейным трактом, обнаружитель нарушений бипопярности и анализатор псевдослучайной последовательности, входы которых объединены и соединены с линейдам трактом, при этом выход анализатора псевдослучайной последовательности подключен к первому входу, второго коммутатора, второй вход и выход которого соединены соответственно с ВЫХОДОМобнаружителя нарушений бипо- лярности и со счетным входом счетчика, выходы которого соединены с первым и вторым входами блока управления, служеб-. ньш входы первого и второго коммутатор ров подключены к соответствующим выходам блока управления, причем на тактовый вход счетчика и анализатора псевдослучайной последовательности поданы тактовые импульсы, на каждой промежуточной .станции - регенератор прямого направления, выходы которого через искусственную пинию подключены к входам регенератора обратного направления, элемент памяти, выход котосюго чесез ключ подключен к коммутирующему вхоцу искусственной линии и к другому входу регенератора обратного направления, о т п .и ч а ю щ е е с я тем,что, с целью повышения достоверности контроля путем обеспечения контроля исходящего направления без перерыва связи, на каждой оконечной станции введены дешифратор фиксированной комбинации, делитель с переменным коэффициентом деления и анализатор нарушений би(Л полярности, при этом вы ход первого коммутатора через последовательно соединенС ные дешифратор фиксированной комбина ции и делитель с перемен 1ым коэффициентом деления, установочные входы которого соединены с соответствующими выходаi I ми блока управления, подключен к второму входу управляемого преобразователя кода, установочный вход которого соединен с соответствующим входом блока 0) управления, причем первый, второй и тре-/ тий входы анализатора нарушений биполярности подключены соответственно к выходу и входам обнаружителя нарушений биполярности, а первь й, второй, третий .г четвертый и пятый выходы аналкзйтора нарушений биполярности соединены соответственно через первый и второй элементы памяти с третьим и четвертым входами блока управления и с пятым входом блока управления непосредственно, соответствующие выходы которого соедигнень с установочными входами анапюатора нарушений биполярности и счетчика.

Изобретение относится к технике связи и может использоваться при построении цифровых систем передачи информаци Известно устройство телеконтроля, содержащее линейное и станционное обору дование, соединенные через линейный

ГЛ.

тракт

Недостатком известного устройства является большой объем оборудования пиней ной части, необходимый для обеспечения высокой помехозащищенности.

Наиболее близким к предлагаемому техническ.им решением является устройство телеконтроля линейных трактов цифровых систем передачи, содержащее на каждой оконечюй станции источник и формационного сигнала и генератор псевдослучайной последовательности, выходы которых подключены к информационным входам первого к 4мутатора, выход которого подключен к первому входу управ

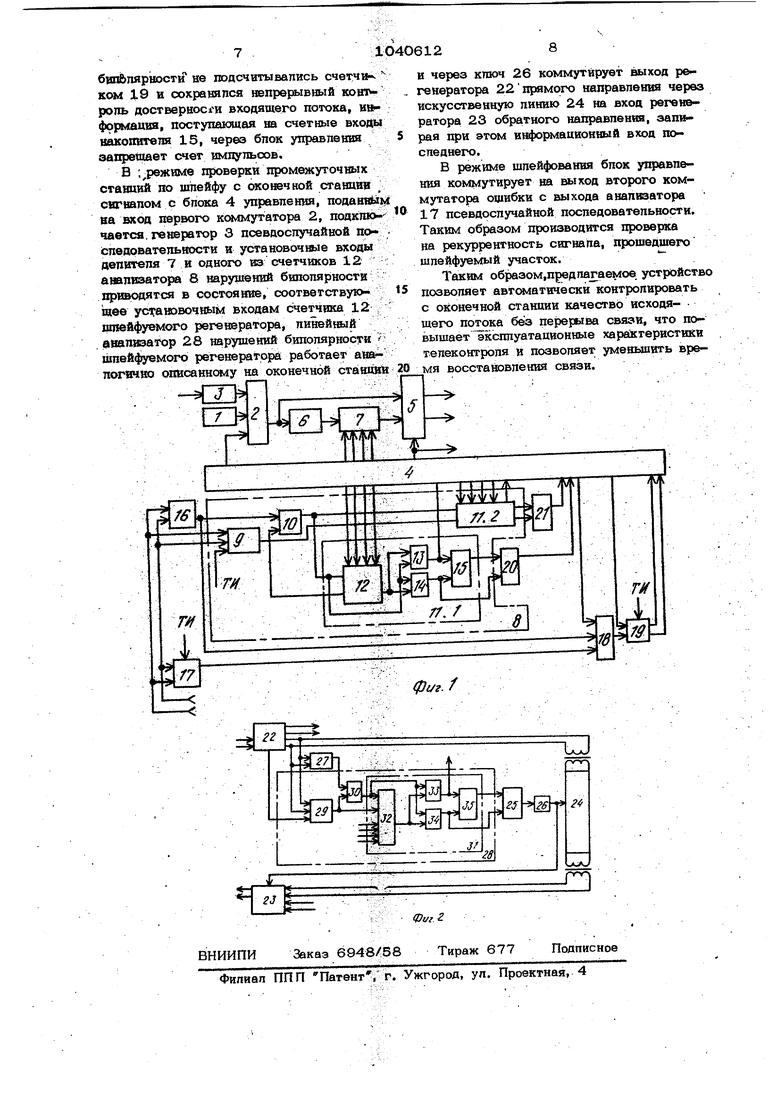

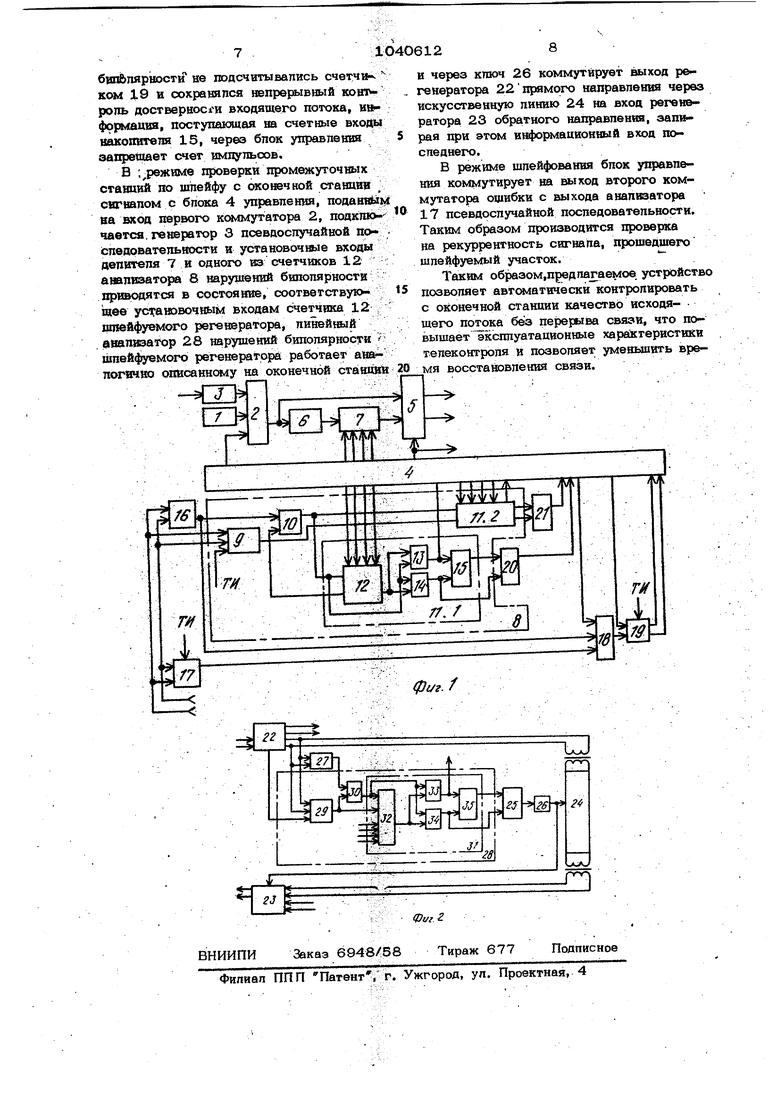

ляемрго Преобразователя кода, выход которого соединен с линейнь М трактом, обнаружитель нарушений биполярности и анализатор псевдослучайной последовательности, входы которых объединены и соединены с линейным трактом, а выход анализатора псевдослучайной последовательгноети подключей к первому входу второго KOMMyriaTopa, второй вход и выход которого соединены соответственно с выходом обнаружителя нарушений биполярнрсти и со счетным в,ходом счетчика, выходы которого соединены с первым и вторым входами блока управления, а служебные входы первого и второго коммутаторов подключены к соответствующим выходам блока управлени, причем на тактовый вход счетчика и анализатора псевдослучайной последовательности поданы тактовые импульсы, а на каждой промежуточной - регенератор прямого направления. выходы которого через искусственную пинию подключены к входам регенератора обратного направления, элемент памяти, выход которого через ключ Подключен к коммутирующему входу искусственной пиНИИ и к другому входу регенератора обратного направления 2 , Однако это устройство имеет низкую достоверность контроля. Цепь изобретения - повышение достоверности контроля путем обеспечения конт роля исходящего направпения без перерыв связи. Поставленная- цель достигается тем, что в устройстве телеконтроля линейных трактов цифровых систем передачи, содер жащим на каждой оконечной станции первый и второй элементы памяти, источник инфэрмационного сигнала и ге-нератор псевдослучайной последовательности, вы- ходы которых подключень к информаиионн ным входам первого коммутатора,выход которого подключен к первому входу управляемого преобразователя кода,выход которого соединен с линейным трактом, обнаружитель нарушений биполярности и анализатор псевдослучайной последовательности, рходы которых-объединены и соединены с линейным трактом, при этом выход анализатора псевдослучайной последоватеиьности подключен к первому входу второ-. го коммутатора, второй вход и выход коToporxD соединены соответственно с выходом обнаружителя нарушений биполчрн носги и со счетным входом счетчика, ходы которого соединены с первым и вторым входами блока управления, а слу жебные входы первого и второго коммутаторов подключены к соответствующим выходам блока управления, причем, на тактовый вход счетчика и канализатора псевдослучайной последовательности поданы тактовые импульсы, на каждой промежуточной станции - регенератор прямого направления,, выходы которого через искусственную пинию подключены к входам регенератора обратного направления, элемент памяти, выход которого через кпюч подключен к коммутирующему входу искусственной линии и к другому.входу регенератора обратного направления, на каждой оконечной станции введены дешифратор фиксированной комбинации, делитель с переменным коэффициентом деления и анализатор нарушений бипопя хности, при этом выход первого коммутатора через последовательно соединенные дешифратор фиксированной комбинации и делитель с переменным коэффициентом яе пения, установочные входы которого соединены с соответствующими выходамибпока управпения, подключен к второму входу управпяемого преобразователя кода, установочный вход которого соединен с соответствующим входом блока управления, причем первый, второй и третий входы анализатора нарушений биполярнооти подключены соответственно к выходу и входам обнаружителя нарушений бипопярности, а первый, второй, третий, четвертый и пятый выходы анализатора нарушений биполярности соединены соответственно через первый и второй элементы памяти с третьим и четвертым входами блока управления и с пятым вхо- о дом блока управления непосредственно, соответствующие выходы которого соединены с установочными входами анализатора нарушений биполярности и счетчкн ка, а на каждой промежуточной станции введены линейный анализатор нарушений биполярности и обнаружитель нарушений биполярности, входы которого соединены с выходами регенератора прямого направления и с первым и вторым входами линейного анализатора нарушений бицопярности, третий вход и йыходь которого соединеш 1 соответственно с хронирующим выходом регенератора прямого направления и с входами элемента памяти, а четвертый вход линейного анализатора нарушений биполярности соединен с выходом обнаружителя нарушений биполярности, причем регенерато{я 1 прямого и обратного направления соединены с линейным трактом. При этом анализатор нарушений биполярности СОС-1-ОИТ из деши4ратора, блока . совпадения и двух решающих блоков, первый и второй входы которых объединены и соединены соответственно с выходами дешифратора и блока совпадения, при этом дешифратора соединен с первым входом, блока совпадения, на тактирующий вход дешифратора поданы тактовые импульол, причем второй вход блока совпадения, первый и второй входы дешифратор являются соответственно первым, вторлм и третьим входами анализатора нарушений бипопярности, соответствующие . входы обоих решающих блоков являются устатовочными входами анализатора нарушений биполярности, а соответствующие выходы решающих блоков являются , вторым, третьим и четвертым выходами анализатора нарушений бипотгярнооти, пятым выходом которого является третий выход первого решающего бпока.. Причем решающий бпок состоит из счетчика, бпока совпадения, бпока неравкозвачности и какопктетм, причем первые в BTOpbie входы бпока совпадения и бпок веравнозшчности объединены и соедийюны cootBeTCTBeHBo с выходом .i первым входом счетчика, а выходы бпока совпадени и блока неравнозначности соединены с со ответстэукпцими входами накопителя, пер вый в второй и установочные входы счет чика являются первым и вторым и устан вочными входами рехиакзщего блока, а выходы накопителя, блока неравнозначное ти и блока совшщенйя являются соответственно первым, вторым и третьим выходами решающего блока. На фиг.1 представлена структурная электрическая схема оконечной станции, предлагаемого устройства; на фиг. 2 то же, промежуточной станции. Устройство телеконтроля линейных трактов цифровых систем передачи содержит на оконечной станции (фиг.ДУиоточнйк 1 инфортлаиионного сигнала, первый коммутатор 2, генератор 3 псевдослучайной последовательности, бпок 4 управления, управляемый преобразователь кода, дешифратор 6 фиксированной ком 1инации, делитель 7 с переменным коэфг ;зш1иентом деления, анализатор 8 нарушений биполярности, состоящий из дешифратора 9, блока 10 совпадения и дву решающих блоков 11Д и 11.2, каждый из которых состоит да счетчика 12, блока 13 совпадения, блока 14 неравнозначности н накопителя 15, обнаружитель 16 нарушений бипопярности, анализатор 17 псевдослучайной последовательности, второй к шутатор 18j счетчик 19, первь1й и-второй элементы 20 И 21 памяти соответственно, а на каждой промежуточной станции (фиг. 2) регенератор 22 прямого ваправлентщ, регенератор 2:3 обратного направления, искусственную линию 24, элемент 25 памяти, ключ 26, обнаружитель 27 нарушё{Шй биполярности, линейный а на 28 нарушений биполярности, состоящий из дешифратора 29, блока ЗО совпадения и решающего блока: 31, который состоит 153 счетчика 32, блока 33 совпа денпя блока 34 неравнозначности и накопителя 35. Устройство работает следующим образом. В условиях прохождения рабочего сигнала оборудование телеконтропя на каждой оконечной станции (фиг. 1) анап зирует качество принимаемого цифрового потока по нарушениям бипопярности и с обнаружителя 16 нарушения биполярности через второй коммутатор 18/ скоммутированный блоком 4 управления дпя прохождения, на счетчик 19 выходного сигнала обнаружителя 16 нарушений биполярности. При ухудшении достоверности передачи, оцениваемой на промежуточной станции (фиг. 2) до аварийного или предупредительного состояния, на соответствующем выходе счетчика 19 появля ется сигнал. В блоке 4 управления имеется коммутация, позволяющая пропускать выходной сигнал счетчика 19 на соот-. ветствующий вход первого коммутатора, в результате чего с источника 1 информационного сигнала (рабочий сигнал) поступает через дешифратор 6 фиксированной комбинации, делитель 7 и управляегльШ преобразователь кода 5 в линейный тракт. Дешифратор 6 фиксированной комбинации выделяет символ рабочего сигнала, которому предшествует н-битная комбинация заданного вида, встречающаяся в .случайном сигнале с большой вероятностью. Делитель 7 выделяет каждый е-й символ из поступающих на его вход, где определяется состоянием установочных входов, которые в режиме не-. обслуживаемой станции управляются вы -ходными сигналами счетчика 19 через блок управления. Сигнал с выхода делителя 7, воздействуя на вкод управляемого преобразователя 5 кОда, нарушает биполярность символов по соответсгвующему закону.Рабочий сигнал с нарушенной биполярностью линейных символов поступает на вход станции, где нарушения биполярности выделяются обнаружителем 16 нарушений бипопярности, позиции.символа, которому предшествует фиксированная комбинация выделяются дешифратором фиксированной комбинаций, а на вы коде блока 1О совпадения ан1апизатора 8 выдепяют- ся пЬзиции симвопов, которым предшествует фиксированная комбинация, и бипопярность KOTopbix нарушена. В решающих блоках 11.1 и 11.2 происходит проверка закона нарушения биполярности в передаваемом сигнале на соответствие закону, определяемому структурой счетчика 12 и состоянием их установочных входов. Для того, чтобы запланированные нарушения

Авторы

Даты

1983-09-07—Публикация

1982-02-19—Подача