третьего коммутатора соединен с чет- i является вторым вжздом устройства вертым входом второго коммутатора и для отображения информации.

1042069

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1981 |

|

SU960920A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| Устройство для отображения информации | 1985 |

|

SU1259333A2 |

| Устройство для отображения информации | 1985 |

|

SU1269181A2 |

| Устройство для отображения совмещенной обстановки | 1981 |

|

SU978091A1 |

| Устройство для формирования знаков на экране телевизионного приемника | 1982 |

|

SU1073793A2 |

| Устройство для отображения информации | 1986 |

|

SU1310888A1 |

| Устройство для индикации | 1983 |

|

SU1092558A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1339628A1 |

| Устройство для формирования знаков на экране телевизионного индикатора | 1989 |

|

SU1679536A1 |

УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ, содержащее последовательно соединенные генератор импульсов, делитель частоты, первый счетчик, первый дешифратор и первый ключей, соединенный с вертикальными шинами матричной индикаторной панели, последовательно соединённые первый коммутатор, первый регистр и второй блок ключей, соединенный с горизонтальными шинами панели, последовательно соединенные второй, третий и четвертый счетчики, второй выход л делителя частоты соединен с входом второго счетчика, второй выход которого соединен с входом второго дешифратора, выход которого соединен с.вторым входом первого регистра, третий выход второго счетчика соединен с первым входом второго коммутатора, второй вход которого соединен с выходом четвертого счетчика, а третий вход - с выходом второго регистра, выход второго KOMMyTatopa соединен с первым входом первого блока памяти, и знакогенератор, первый вход которого соединен с выходом третьего счетчика , первый вход второго регистра является первый входом устройства для отображения информации, отличающееся тем, .что, с целью повышения достоверности отображения информации при ее воспроизведении в случае выхода из строя блока памяти и знакогенератора, в него введен второй и третий блоки . памяти., две схемы сравнения, третий коммутатор , элемент И, блок элементов И и блок инверторов, выход которого соединён с первым входом первого коммутатора, второй вход которого соединен с первыми входами третьего коммутатора и первой схемы сравнения, второй вход которой соединен с выходом второго блока памяти и вторВ1м входом третьего коммутатора, первый вход второго блока памяти соединен S с выходом второго коммутатора, а второй вход - с первым выходом треть(Л его коммутатора, выход первого блока памяти соединен с первым входом блока элементов И , второй вход которого соединен с выходом элемента И, первый вход которого соединен с третьим выходом делителя частоты, второй вход - с выходом третьего блока памяти, первый вход которого ND соединен с выходом второго коммутатоо ра, а второй вход - с выходом второй 9д схемы сравнения , первый вход которой соединен с первым выходом знакогенератора , второй выход которого соединен с вторым входом второй схемы сравнения и первым входом блока инверторов, второй вход которого соединен с выходом первой схемы сравнения, третий вход первого коммутатора соединен с вторым выходом третьего коммутатора, третий выход которого соединен с вторыми входами второго регистра и первого блока памяти, выход блока элементов И соединен с вторым входом знакогенератора, третий вход

1

Изобретение относится к автоматике и вычислительной технике, в частности к индикаторным устройствам, и может быть использовано в устройствах вывода информации из ЭВМ.

Известны устройства для отображени информации, содержащие последовательно соединенные блок памяти . знакогенератор, коммутатор, регистр и первый блок ключей, соединенный с горизонтальными шинами матричной панели, последовательно соединенные генератор импульсов, делитель частоты, второй счетчик, дешифратор и второй блок ключей , соединенный с вертикальными шинами панели последовательно соединенные второй, третий и четвертый счетчики, второй дешифратор и второй коммутатор ij .

Недостаток данного устройства заключается в низкой достовер |}ости отображения информации за счет отсутствия контроля работы блока памяти и знакогенератора.

Целью изобретения является повышеIние достоверности отображения информации при ее воспроизведении в случае выхода из строя блока памяти и знакогенератора.

Указанная цель достигается тем, что в устройство для отображения инфо мации, содержащее последовательно соединенные генератор импульсов, делитель частоты, первый счетчик, первый дешифратор и первый блок ключей, соединенный с вертикальными шинами матричной индикаторной панели, последовательно соединенные первый коммутатор, первый регистр и второй блок ключей, соединенный с горизонтальными шинами панели, последовательно соединенные второй, третий и четвертый счетчики, второй выход делителя частоты соединен с входом второго счетчика, второй выход которого соеди нен с входом второго дешифратора, выход которого соединен с вторым вхо. дом первого регистра . третий выход второго счетчика соединен с первым

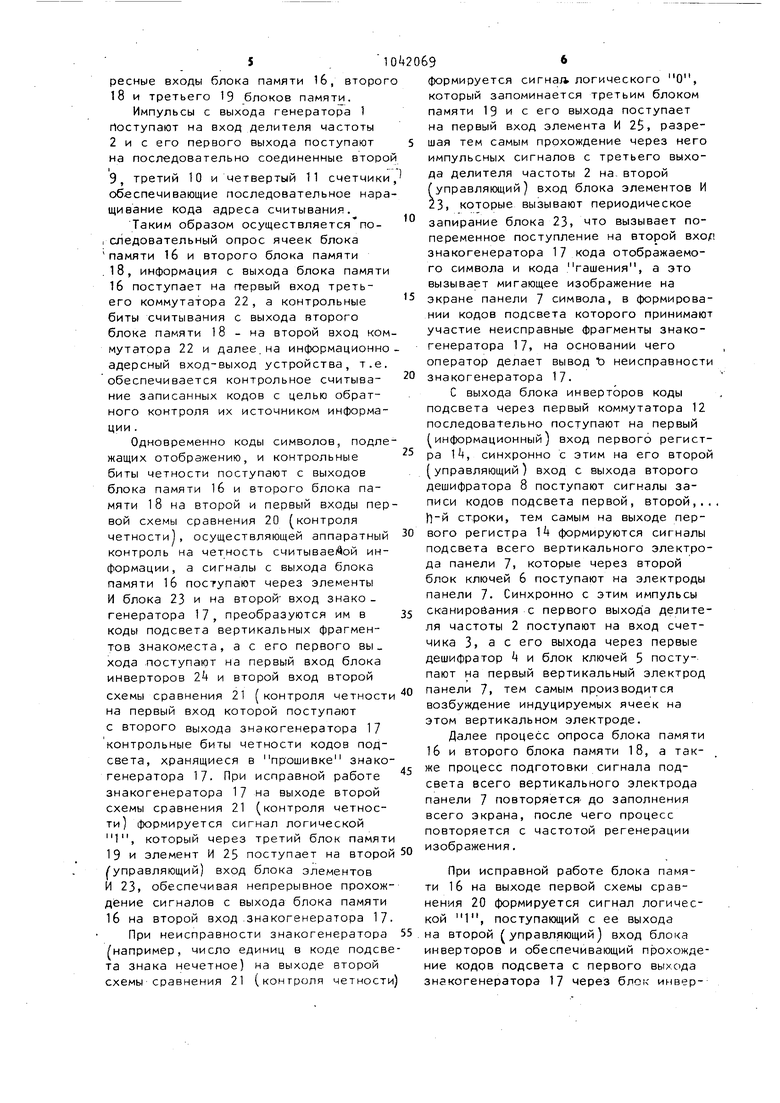

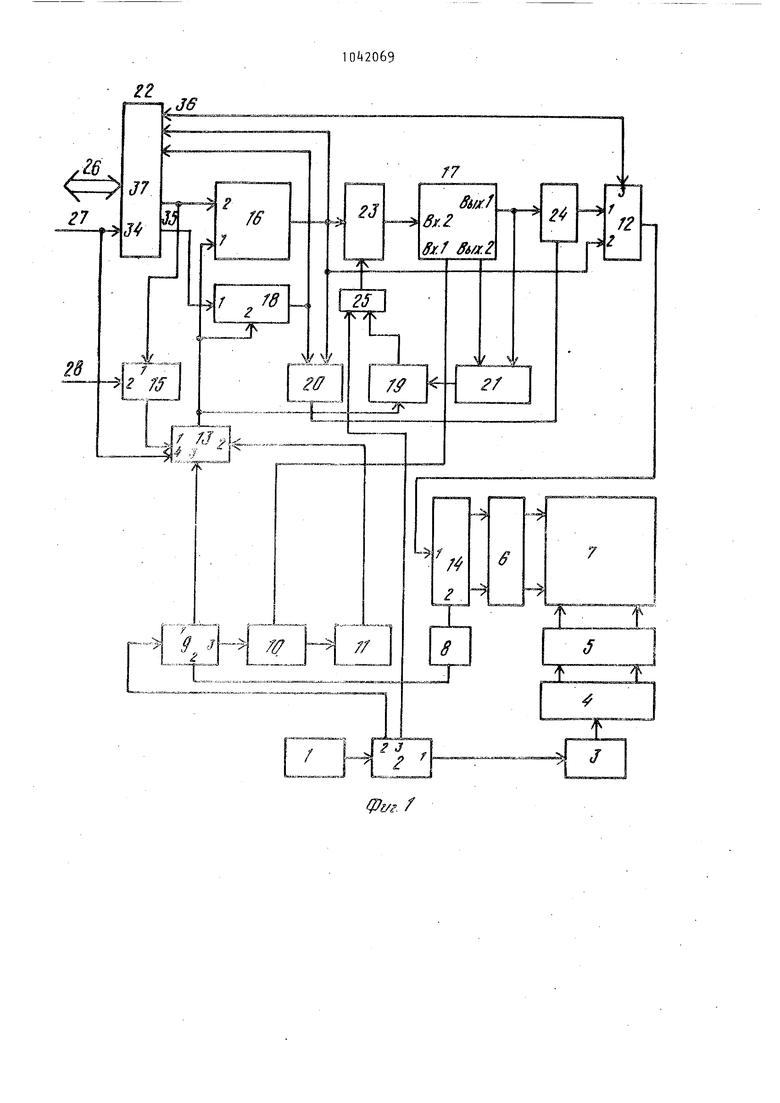

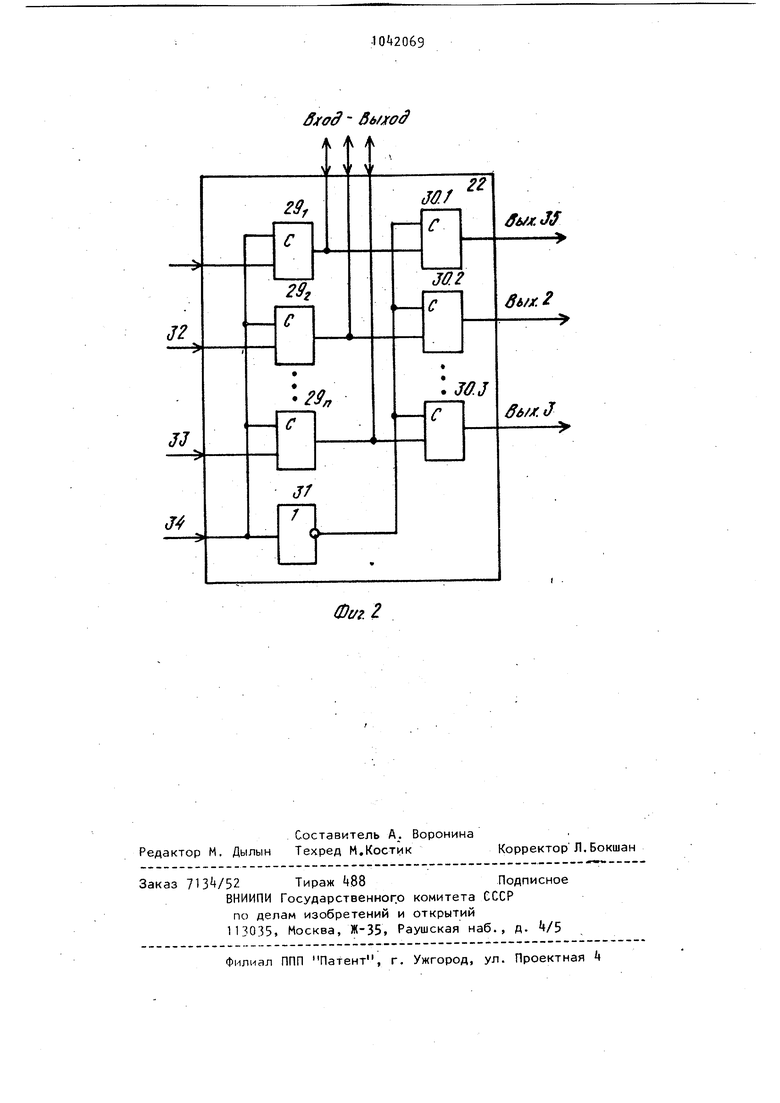

входом второго коммутатора второй |Вход которого соединен с выходом {четвертого счетчика а третий вход с выходом второго регистра, выход второго коммутатора соединен с первым входом первого блока памяти, и знакогенератор, первый вход которого соединен с выходом третьего счетчика, первый вход второго регистра является первым входом устройства для отображения информации, введены второй и третий блоки памяти , две схемы сравнения , третий коммутатор, элемент И, блок элементов И и блок инверторов, выход которого соединен с первым входом первого коммутатора, второй вход которого соединен с первыми входами третьего коммутатора и первой схемы сравнения, второй вход которой соединен с выходом второго блока памяти и вторым входом третьего .коммутатора , первый вход второго блока памяти соединен с выходом второго коммутатора, а второй вход с первым выходом третьего коммутатора, выход первого блока памяти соединен с первым входом блока элементов И, второй вход которого соединен с выходом элемента И первый вход которого соединен с третьим выходом делителя частоты, второй вход с выходом третьего блока памяти первый вход которого соединен с выходом второго коммутатора ,. а второй вход -с выходом второй схемы сравнения, первый вход которой соединен с первым выходом знакогенератора, второй выход которого соединен с вторым входом второй схемы сравнения и первым входом блока инверторов, второй вход которого соединен с выходом nepBofi схемы сравнения, третий вход первого коммутатора соединен с вторым выходом коммутатора, третий выход которого соединен с вторыми входами второго регистар и первого блока памяти, выход блока элементов И соединен с вторым входом знакогенератора, третий вход третьего коммуtлтора соединен с четвертым входом второго коммутатора и является вторы входом устройства , для отображения информации. На фиг. 1 представлена структурна схема устройства, на фиг. 2 - пример выполнения третьего коммутатора Схема включает генератор 1 импуль сов, делитель 2 частоты, первый 3 счетчик, первый дешифратор k, первый блок 5 ключей, второй блок 6 ключей, матричную индикаторную панель 7, вто рой дешифратор 8, второй счетчик 9, третий счетчик 10, четвертый счетчик 11, первый коммутатор 12, второй коммутатор 13, первый регистр 1, второй регистр 15, первый блок памяти 16, знакогенератор 17, второй бло памяти 18, третий блок памяти 19, первую 20 и второй 21 схемы сравнения, третий- коммутатор 22, блок элементов И 23, блок инверторов 2 , элемент И 25, вход-выход третьего коммутатора 26, второй вход устройст ва 27, первый вход устройства 28, элементы И первой группы Z9i - .29п элементы И второй группы 30, инверор 31, первый, второй и третий входы третьего коммутатора 32 , 33 и 3, первый, второй и третий выходы третьего коммутатора 35, 36 и 37. Устройство работает следующим образом. Режим записи информации. На второй вход устройства (выбора режима работы) и далее на первый вхо З- третьего коммутатора 22 и четвер тый вход второго коммутатора 13пост пает сигнал Запись. При этом коммутатор 22 подгота.вливается для прохождения сигнала с информационноадресного входа-выхода устройства на второй вход второго регистра 15 и В:торой вход блока памяти 16 путем подачи на управляющие входы первой группы элементов И (29 - 29. фиг. 2 запрещающего уровня сигнала с второго входа устройства 27 , а на управляющие входы второй группы элементов И (,30.1,,- ЗОп, фиг. 2) разрешающего уровня сигнала .с выхода эле мента НЕ , что вызывает закрывание элементов И первой группы (29 29ц и открывание элементов И второй груп пы 30.1 - 30nV, а также обеспечивае ся прохождение сигналов с второго входа второго коммутатора 13 на его выход. Синхронно с этим с первого входа 28 (сигнала стробирования адреса) на первый вход второго регистра 15поступают импульсы стробирования адреса , в результате на выходе .второго регистра 15 формируется код адреса записи который поступает на третий вход второго коммутатора 13 и далее с его выхода - на первый адресный вход блока памяти 16 и первый (ад- ресный вход второго блока памяти 18 (накопителя четности), на второй вход которого с первого выхода 35 коммутатора 22 поступают биты контроля четности информационного слова, поступающие от источника информации с входа-выхода 2б. Таким образом , в блоке памяти 16 осуществляется последовательная запись,кодов символов, в случае записи цифро-буквенной информации или точек, в случае записи графической информации, подлежащих отображению на матричной газоразрядной панели 7 , а во втором блоке памя ти 18 записываются контрольные биты четности, соответствующие этим кодам причем каждому знакоместу или точке на экране панели 7 соответствует ячейка или бит памяти в блоке памяти 16и первом накопителе четности 18. Остальные узлы устройства в этом режиме участия не принимают. I Режим контрольного считывания и отображения информации, На второй вход выбора устройства 27 режима работы и далее на.третий вход коммутатора 22 и четвертый вход второго коммутатора 13 поступает сигнал Отображение. Коммутатор 22 подготавливается для прохождения сигналов с его первого и второго входов на выход и далее на информа ционно-адресный вход-выход устройст.. ва 26 путем подачи на управляющие входы первой группы элементов И (29 29ц, фиг. 2) разрешающего уровня сигнала с второго входа уст . ройства 27, а на управляющие входы второй группы элементов И (30.1 30м, фиг..2) запрещающего уровня сигнала с выхода элемента НЕ, чтовызывает закрывание элементов И первой группы ( 29 /( - 29ц) , а также запрещается прохождение сигналов адреса с третьего входа второго коммутатора 13 и разрешается прохождение сигналов адреса считывания с третье, го выхода второго счетчика 9 и выхода четвертого счетчика 11 на выход второго коммутатора 13 и далее на ад5 , 1 ресные входы блока памяти 16, второг 18 и третьего 19 блоков памяти. Импульсы с выхода генератора 1 Поступают на вход делителя частоты 2 и с его первого выхода поступают на последовательно соединенные второ 9, третий 10 и четвертый 11 счетчики обеспечивающие последовательное нара щивание кода адреса считывания. Таким образом осуществляется по,следовательный опрос ячеек блока памяти 16 и второго блока памяти .18, информация с выхода блока памяти 16 поступает на ггервый вход третьего коммутатора 22, а контрольные биты считывания с выхода второго блока памяти 18 - на второй вход ком мутатора 22 и далее.на информационно адерсный вход-выход устройства, т.е. обеспечивается контрольное считывание записанных кодов с целью обратного контроля их источником информации . Одновременно коды символов, подле жащих отображению, и контрольные биты четности поступают с выходов блока памяти 1б и второго блока памяти 18 на второй и первый входы пер вой схемы сравнения 20 (контроля четности, осуществляющей аппаратный контроль на четность считывае ой информации, а сигналы с выхода блока памяти 16 поступают через элементы И блока 23 и на второй вход знако генератора 17, преобразуются им в коды подсвета вертикальных фрагментов знакоместа, а с его первого выхода .поступают на первый вход блока инверторов 2k и второй вход второй схемы сравнения 21 (контроля четности на первый вход которой поступают с второго выхода знакогенератора 17 контрольные бить четности кодов подсвета, хранящиеся в прошивке знако генератора 17- При исправной работе знакогенератора 17 на выходе второй схемы сравнения 21 (контроля четности) формируется сигнал логической 1, который через третий блок памяти 19 и элемент И 25 поступает на второй /управляющий) вход блока элементов И 23, обеспечивая непрерывное прохождение сигналов с выхода блока памяти 16 на второй вход .знакогенератора 17 При неисправности знакогенератора /например, число единиц в коде подсве та знака нечетное) на выходе второй схемы сравнения 21 (контроля четности 9 формируется сигнал логического О, который запоминается третьим блоком памяти 19 и с его выхода поступает на первый вход элемента И 25, разрешая тем самым прохождение через него импульсных сигналов с третьего выхода делителя частоты 2 на, второй (управляющий) вход блока элементов И 23, которые вызывают периодическое запирание блока 23, -ITO вызывает попеременное поступление на второй вхол знакогенератора 17 кода отображаемого символа и кода гашения, а это вызывает мигающее изображение на экране панели 7 символа, в формировании кодов подсвета которого принимают участие неисправные фрагменты знакогенератора 17, на основании чего оператор делает вывод Ъ неисправности знакогенератора 17. С выхода блока инверторов коды подсвета через первый коммутатора 12 последовательно поступают на первый (информационный) вход первого регистра , синхронно с этим на его второй (управляющий) вход с выхода второго дешифратора 8 поступают сигналы записи кодов подсвета первой, второй,... h-й строки, тем самым на выходе первого регистра 14 формируются сигналы подсвета всего вертикального электрода панели 7, которые через второй блок ключей 6 поступают на электроды панели 7. Синхронно с этим импульсы сканиробания с первого выхода делителя частоты 2 поступают на вход счетчика 3, а с его выхода через первые дешифратор и блок ключей 5 поступают на первый вертикальный электрод панели 7 тем самым производится возбуждение индуцируемых ячеек на этом вертикальном электроде. Далее процесс опроса блока памяти 16 и второго блока памяти 18, а также процесс подготовки сигнала подсвета всего вертикального электрода панели 7 повторяется- до заполнения всего экрана, после чего процесс повторяется с частотой регенерации изображения. При исправной работе блока памяти 16 на выходе первой схемы сравнения 20 формируется сигнал логичеспоступающий с ее выхода на второй (управляющий) вход блока инверторов и обеспечивающий прохождение кодов подсвета с первого выхода знакогенератора 17 через блок инверторов без инверсии. При неисправности блока памяти 16 либо считывани ложной информации (например, число единиц в коде нечетное) на выходе первой схемы-сравнения 20 контроля четности) формируется сигнал логичес кого О, который вызывает инвертирование блоком инверторов кодов подсвета символов, что вызывает на экране панели 7 негативное изображение соответствующего символа, код которого считан из блока памяти 16. с ошибкой. В случае отображения графической информации на третий (управляющий) вход первого коммутатора 12 с второг выхода 36 коммутатора 22, подготовленного для прохождения сигналов 69 с входа-выхода устройства 26, поступает сигнал графика, запрещающий, прохождение на вход первого регистра И сигналов подсвета с выхода знакогенератора 17 и разрешающий прохождение сигналов с выхода блока памяти 16, представляющих собой непосредственно коды подсвета точек на экране матричной газоразрядной панели 7. Таким образом, предлагаемое устройство позволяет осуществлять как запись, так и обратное (контрольноеУ считывание кодов отображаемой информации, а также обеспечивает контроль исправности блока памяти и знаког енератора что резко повышает достоверность отображаемой информации.

77

Si/jff

2

/

ff;fo - Sb/jfO

Фи.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для отображения информации | 1981 |

|

SU960920A1 |

Авторы

Даты

1983-09-15—Публикация

1982-01-08—Подача