Изобретение относится к преобразвательной технике и может быть использовано при разработке источнико вторичного электропитания индикатор, ных устройств, выполненных на электроннолучевых трубках с барьерным люминофором.

По основному авт. св. № 920984 известен управляемый ступенчатый преобразователь, содержащий зарядный источник питания с П последовательно включенньми конденсаторами на выходе с Х выводами, п - 1 управляемый конвертор с выходными выпрямителями, п - 1 трехобмоточный дроссе.ль, зарядный и разрядный узлы, которые выполнены в виде п- 1 последовательно включенных ключевых элементов, с m входами и выходами, где п- число ступеней выходного напряжения, k - вывод конденсаторно цепочки, соответствующей ступени, гпвходы зарядного и выходы разрядного ключевых элементов соответствующей ступени, при этом управляющие входы управляемых конверторов связаны с блоком управления, а их выходные выпрямители включены последовательно через первичные обмотки трехобмоточных дросселей, зашунтированы через эти обмотки диодами и резисторами и эта последовательная цепочка включена между выводом конденсаторной цепочки нижней ступени и выходным выводом .для подключения нагрузки, вторичные обмотки указанных дросселей одним из своих выводов через разделительные диоды подключены к соответствующему входу ключевы элементов узла заряда, адругие выводы связаны с соответствующими своей ступени выводами конденсатор ной цепочки через развязывающие диоды и с выходным выводом через обратные диоды, причем третьи обмотки дросселей соединены последовательно с разрядными диодами и эти цепочки зашунтированы дополнительными шунтирующими диодами и включены между соответствующим выходом узла разряд и выводом конденсаторной цепочки низшей ступени.

В известном устройстве при переключении уровней напряжения с низкого на,высокий включение всех управляемых конверторов происходит одновременно, что снижает КПД устройства особенно при повышенных частотах переключения, так как заряд емкости нагрузки происходит сразу до верхнего уровня, т.е. потребляется значительный ток от зарядного источника. Выделение значительных мощностей в -моменты переключения приводит к возникновению импульсных помех, воздействующих на разрядный и зарядный ключевые элементы и к сбою их работы. Кроме того, при сбое управляющйх импульсов может возникнуть ава рийная ситуация, когда будут включены одновременно зарядные и разрядные ключевые элементы, что снижает функциональную надежность устройства. Отсутствие автономного функционального контроля значительно усложняет поиск неисправностей и приводит к усложнению настройки устройства.

Цель изобретения - повышение надежности и упрощение настройки.

Поставленная достигается тем, что в управляемом ступенчатом преобразователе блок управления выполнен на (п- 1) RS-триггерах, прямые выходы которых образуют выходные выводы блока управления,R - и S-входы триггеров подключены к соответствующим выходам узла логической обработки импульсов управления, состоящего из двух логических элементов 2И, выход первого из которых подключен к S-входу триггера высшей, а выход второго - к R-входу триггера низшей переключаемой ступени, из 2 (п - 2) логических элементов 2И-ИЛИ выходы которых подключены к соответствующим R - и S-входам триггеров, причем количество узлов 2И в этих элементах, подключенных к R-входам триггеров, равно порядковому номеру переключаемой ступени, начиная с низшего уровня, а к 5-входам - порядковому номеру переключаемой ступени, начиная с верхнего уровня, при этом первые входы всех логических элементов 2И объединены и подключены к выходу ждущего мультивибратора, входом соединенного с выходом логического элемента ИЛИ-НЕ с п входами, причем каждый из входных выводов узла логической обработки импульсов управления подключен к вторым входам логических узлов 2И, связанных с R-входами триггеров своей и высшей ступеней непосредственно, с вторыми входами узлов 2И, связанных с S-входами низшей ступени непосредственно, а высших ступеней - через узлы задержки,, при этом один из входов логического элемента ИЛИ-НЕ подключен к входному выводу узла логической обработки низшей ступени, а другие подключены к вторьом входам логических узлов 2И, связанных с 5-входами триггеров переключаемых ступеней, причем входные выводы узла логической обработки импульсов управления подключены к соответствующим выходам пультиплексора, информационные входы которого подключены к вводам импульсов внешнего управления, а вторые информационные входы - .к соответствующим выходам распределителя импульсов, а вход управления через инвертор - к входу команды режима работы и первому входу третьего логического элемента

2И, второй вход которого подключен к выходу задающего генератора такто рых импульсов, а выход - к входному выводу распределителя импульсов.

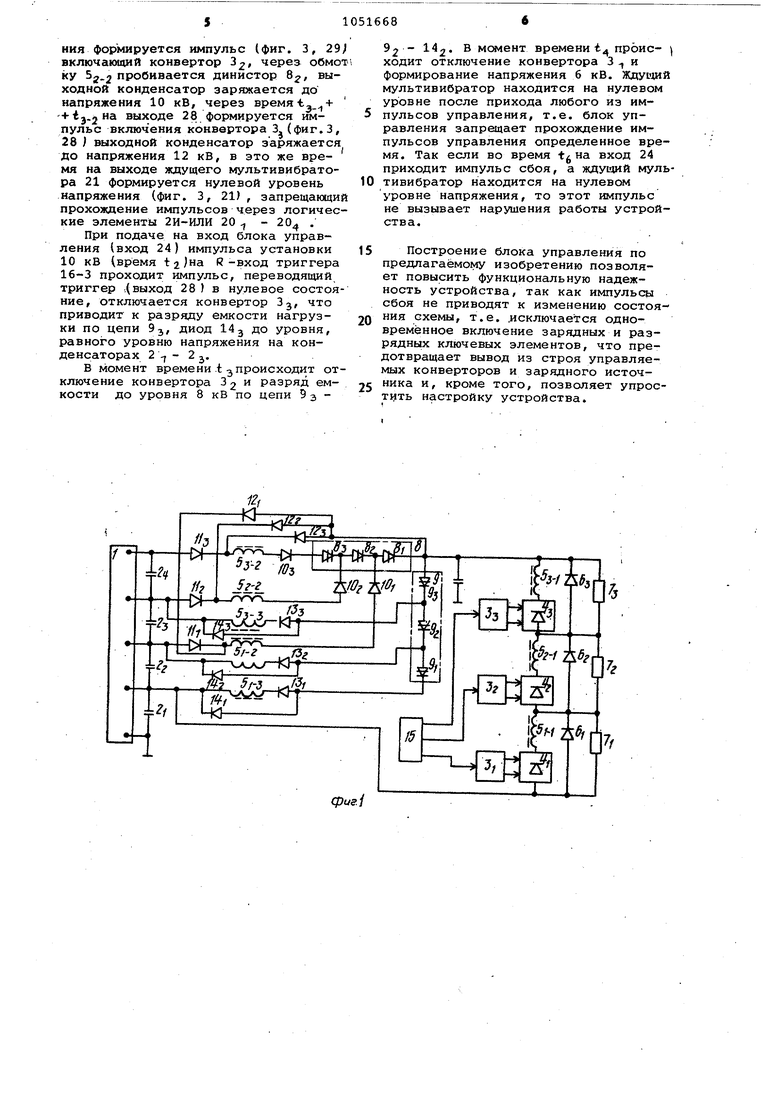

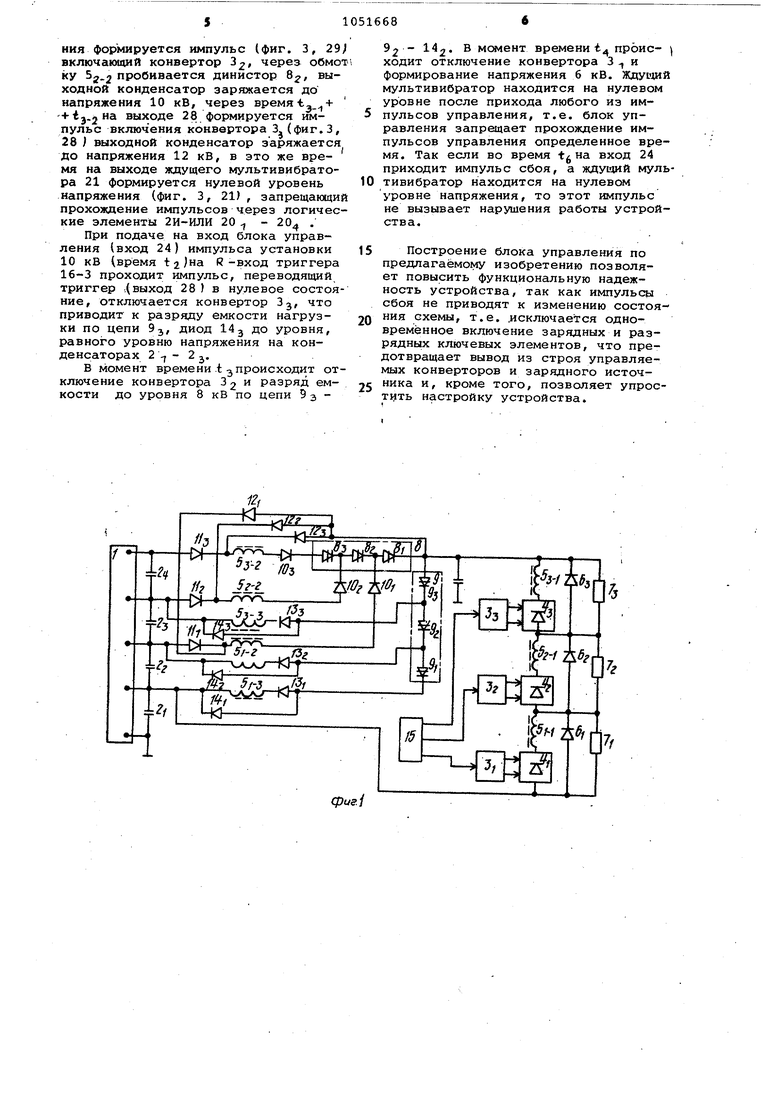

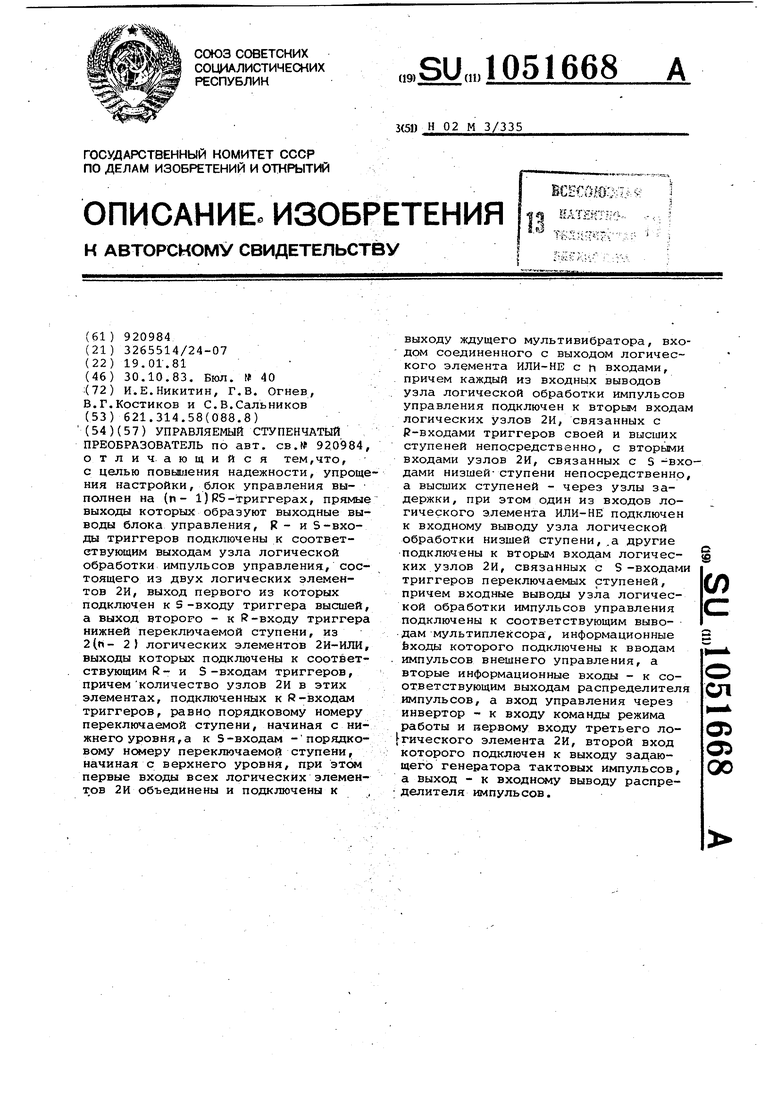

На фиг. 1 показана функциональная схема устройства; на фиг. 2 - функциональная схема узла логической обработки импульсов управления; на фиг. 3 - принципиальная схема блока АФК и мультиплексора; на фиг. 4 диаграммы напряжений в отдельных точках схемы, поясняющие принцип работь( устройства, выполненных на четыре ступени выходного напряжения.

Устройство содержит зарядный источник 1 с последовательно включенными конденсаторами 2 - 2 на выходе, управляемые конверторы 3 с выходными выпрямителями 4 - 4, которые включены последователе.но через первичные обмотки 5 , 25 j трехобмоточных дросселей и зашунтированы через эти обмотки диодами 6 - 6 2 и резисторы 7 ;, - 7, зарядный 8 и разрядный 9 узлы, которые выполнены в виде последовательно включенных зарядных ключевых элементов 8 - 8 и разрядных 9/ 9. Вторичные обмотки дросселей

5-т-2 г 2-2 -3-2 ОД своих выводов через разделительные диоды 10 - Юз подключены к соответствующему входу ключевых элементов узла заряда, а другие выводы с соответствующими своей ступени выводами конденсаторной цепочки через развязывающие диоды 11 - Из выходным выводом через обратные диоды

121 - 12з.. / :

Третьи обмотки дросселей S. , 5 2-3 5 3-3 соединены последовательно с разрядными диодами - 13 и эти цепочки зашунтироваными дополнительньп«1И шунтирующ.ими диодами .

Блок 15 управления, принципиальная схема КоторогоПоказанана фиг.2 и 3 содержит: RS-триггеры 16 - 16 узла.17 логической обработки импульсов управления, который содержит два логических элемента 2И (18 и 19-J, выход первого кз которых подключен к 5-входу триггера высшей ступени, а выход второго к R-входу тригггера низшей ступени, логические

элементы 2И-ИЛИ 20- - 20,

выходы

которых подключены к соответствую- щим входам RS-триггеров, при этом одни из входов И всех логических элементов 2И объединены и подключены к выходу ждущего мультивибратора 21, а его вход подключен к выхо- ду логического элемента ИЛИ-НЕ 22, входы которого подключены к вводам 23-26 импульсов управления, которые: подключены к соответствующим входам; логических элементов 2Й и 2И-ИЛИ непосредственно или через элементы

27 - 27 задержки, прямые входы ;RS-триггеров образуют выходные выВоды 28-30 блока управления, а вхо ды импульсов управления подключены к выходам мультиплексора 31 (фиг.З) выполненного на логических элементах 2И-2И-ИЛИ 31 -314 Узел 32 автономного функционального контроля содержит автогенератор 33, соединенный с одним из входовхлогического элемента 2И 34, выход которого подключен к входу распределителя 35 импульсов, состоящего из счетчика

36и дешифратора 37 на логических элементах ЗИ, выходы которого подклюл чены к вторым информационным входам мультиплексора, первые информационные входы которого соединены с выводами ввода импульсов внешнего управления, вход 38 команды режима работы через инвертор 39 подключен

к входу управления мультиплексора.

Управляемый ступенчатый преобразователь работает следующим образом.

Автогенератор 23 вырабатывает последовательность тактовых импульсов заданной частоты. При подаче на вход 38 положительного потенциала напряжения .разрешается прохождение тактовых импульсов на счетчик 36, с выхода которого на вход дешифратора

37подаются перепады напряжения

по заданной программе, а на объединенные входы логических схем И дешифратора подается тактовый импульс, который в определенной последовательности по заданной программе выделяется на выходах дешифратора и поступает на входы мультиплексора 31. На выходе инвертора 39 образуется нулевой потенциал, запрещающий прохождение импульсов внешнего управления. На выходах мультиплексора 24 27 импульсы управления появляются по заданной блоком АФК команде.

При подаче на вход38 нулевого потенциала блокируется прохождение импульсов генератора 33 на вход дешифратора и разрешается м льтиплексором 31 прохождение на выходы 24-27 импульсов внешнего управления.

При включении устройства на его выходе формируется выходное напряжение +6 кВ, которое выделяется на конденсаторе 2 и через, диоды 6 -62 подается на выход. При подаче на вход 23 импульсов управления (время t, фиг. 3) триггер 16-1 формирует на выходе 28 (диаграмма 30, фиг. 3) импульс напряжения, который включает управляемый конвертор 3, на первичной обмотке 5 дросселя формируется импульс напряжения, наводяцдай в обмотке -.2 импульс высокого напряжения, пробивающий динисторы 8 , выходной конденсатор заряжается до напрям ения В кВ, через время t. на выходе 29 узла управления формируется импульс (фиг. 3, 29) включающий конвертор 32 через обмот ку 52-2 пробивается динистор выходной конденсатор заряжается до напряжения Ю кВ, через время t3. + -+i-.5Ha выходе 28 формируется импульс включения конвертора 3j (фиг. 3, 28; выходной конденсатор заряжается до напряжения 12 кВ, в это же время на выходе ждущего мультивибратора 21 формируется нулевой уровень напряжения (фиг. 3, 21), запрещающий прохождение импульсов через логические элементы 2И-ИЛИ 20 - 20 ,

При подаче на вход блока управления (вход 24) импульса установки 10 кВ (время f -вход триггера 16-3 проходит импульс, переводящий. триггер .(выход 28 ) в нулевое состояние, отключается конвертор 3, что приводит к разряду емкости нагрузки по цепи 9з, диод 14з до уровня, равного уровню напряжения на конденсаторах 2 -, - 2 J.

В момент времени i э Р° ° -- ° ключение конвертора 3 2 и разряд емкости до уровня 8 кВ по цепи 9 э

В момент времени i проис9, - 142с

ходит отключение конвертора 3 -, и формирование напряжения 6 кВ. Ждуидий мультивибратор находится на нулевом уровне после прихода любого из импульсов управления, т.е. блок управления запрещает прохождение импульсов управления определенное время. Так если во время вход 24 приходит импульс сбоя, а ждущий мультивибратор находится на нулевом уровне напряжения, то этот импульс не вызывает нарушения работы устройства.

Построение блока управления по предлагаемому изобретению позволяет повысить функциональную надежность устройства, так как импульсы сбоя не приводят к изменению состояния схемы, т.е. .исключается одновременное включение зарядных и разрядных ключевых элементов, что предотвращает вывод из строя управляемых конверторов и зарядного источника и, кроме того, позволяет упростить настройку устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый ступенчатый преобразователь | 1978 |

|

SU790084A1 |

| Управляемый ступенчатый преобразователь | 1980 |

|

SU920984A2 |

| Управляемый двухступенчатый преобразователь | 1977 |

|

SU694955A1 |

| Коммутатор уровней высокого напряжения | 1980 |

|

SU907724A1 |

| Коммутатор уровней постоянного напряжения | 1984 |

|

SU1224922A1 |

| Преобразователь постоянного напряжения | 1987 |

|

SU1415368A1 |

| Стабилизирующий конвертор | 1980 |

|

SU902010A1 |

| Управляемый ступенчатый преобразователь постоянного тока в постоянный для питания емкостной нагрузки | 1976 |

|

SU705614A1 |

| Мостовой преобразователь напряжения | 1984 |

|

SU1182609A1 |

| Инвертирующий бестрансформаторный понижающий преобразователь постоянного напряжения | 1980 |

|

SU1086520A1 |

УПРАВЛЯЕМЫЙ СТУПЕНЧАТЫЙ ПРЕОБРАЗОВАТЕЛЬ по авт. св. 920984, отличающийся тем,что, с целью повыидения надежности, упрощения настройки, блок управления вы- полнен на (п - 1)RS-триггерах, прямые выходы которых образуют выходные выводы блока управления, R - и S-входы триггеров подключены к соответствующим выходам узла логической обработки импульсов управления, состоящего из двух логических элементов 2И, выход первого из которых подключен к S-входу триггера высшей, а выход второго - к (-входу триггера нижней переключаемой ступени, из 2(h- 2) логических элементов 2И-ИЛИ, выходы которых подключены к соответствующим R- и S-входам триггеров, причем количество узлов 2И в этих элементах, подключенных к R-входам триггеров, равно порядковому номеру переключаемой ступени, начиная с нижнего уровня, а к S-входам -порядковому номеру переключаемой ступени, начиная с верхнего уровня, при этом первые входы всех логических элемент ов 2и объединены и подключены к выходу ждущего мультивибратора, входом соединенного с выходом логического элемента ИЛИ-НЕ с п входами, причем каждый из входных выводов . узла логической обработки импульсов управления подключен к вторым входам логических узлов 2И, связанных с Р-входами триггеров своей и высших ступеней непо.средственно, с вторьоми входами узлов 2И, связанных с S -входами низшей-ступени непосредственно, а высших ступеней - через узлы задержки, при этом один из входов логического элемента ИЛИ-НЕ подключен к входному выводу узла логической обработки низшей ступени,.а другие подключены к вторым входам логичес- i ких узлов 2И, связанных с S -входами (Л триггеров переключаемых ступеней, причем входные выводы узла логической обработки импульсов управления подключены к соответствующим выводам мультиплексора, информационные бходы которого подключены к вводам . импульсов внешнего управления, а вторые информационные входы - к сосд ответствующим выходам распределителя импульсов, а вход управления через инвертор - к входу команды режима да о: работы и первому входу третьего ло гического элемента 2И, второй вход которого подключен к выходу задаю00 щего генератора тактовых импульсов, а выход - к входному выводу распре; делителя импульсов.

Авторы

Даты

1983-10-30—Публикация

1981-01-19—Подача