блока умножения, третий и четвертый входы которого подключены соответственно к выходам элементов ИЛИ первой и.второй групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования сетевых графов | 1981 |

|

SU1013965A1 |

| Устройство для моделирования сетевых графов | 1984 |

|

SU1251099A1 |

| Устройство для исследования путей в графе | 1982 |

|

SU1076909A1 |

| Устройство для моделирования сетевых графов | 1983 |

|

SU1151979A1 |

| Устройство для определения характеристик графа | 1981 |

|

SU991434A1 |

| Устройство для исследования путей в графах | 1981 |

|

SU1005066A2 |

| Устройство для моделирования графов | 1984 |

|

SU1218392A1 |

| Устройство для определения характеристик связности ориентированного графа | 1983 |

|

SU1133596A1 |

| Устройство для исследования графов | 1985 |

|

SU1252791A1 |

| Устройство для вычисления характеристик графов | 1984 |

|

SU1244673A1 |

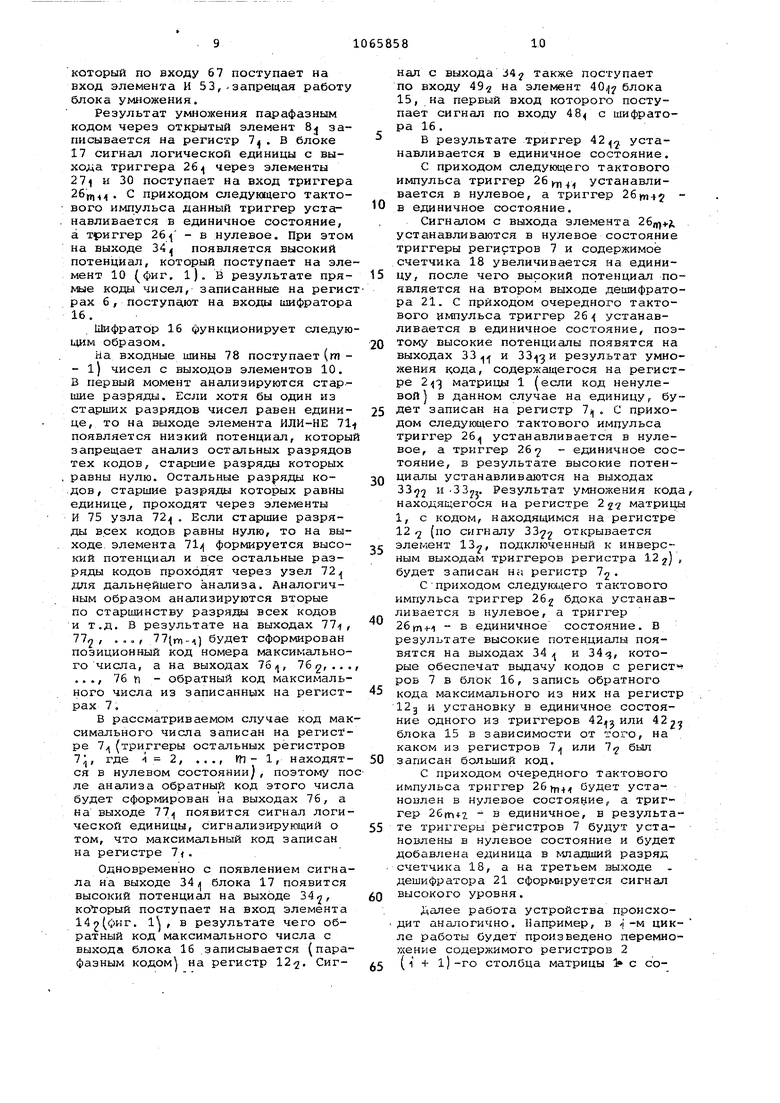

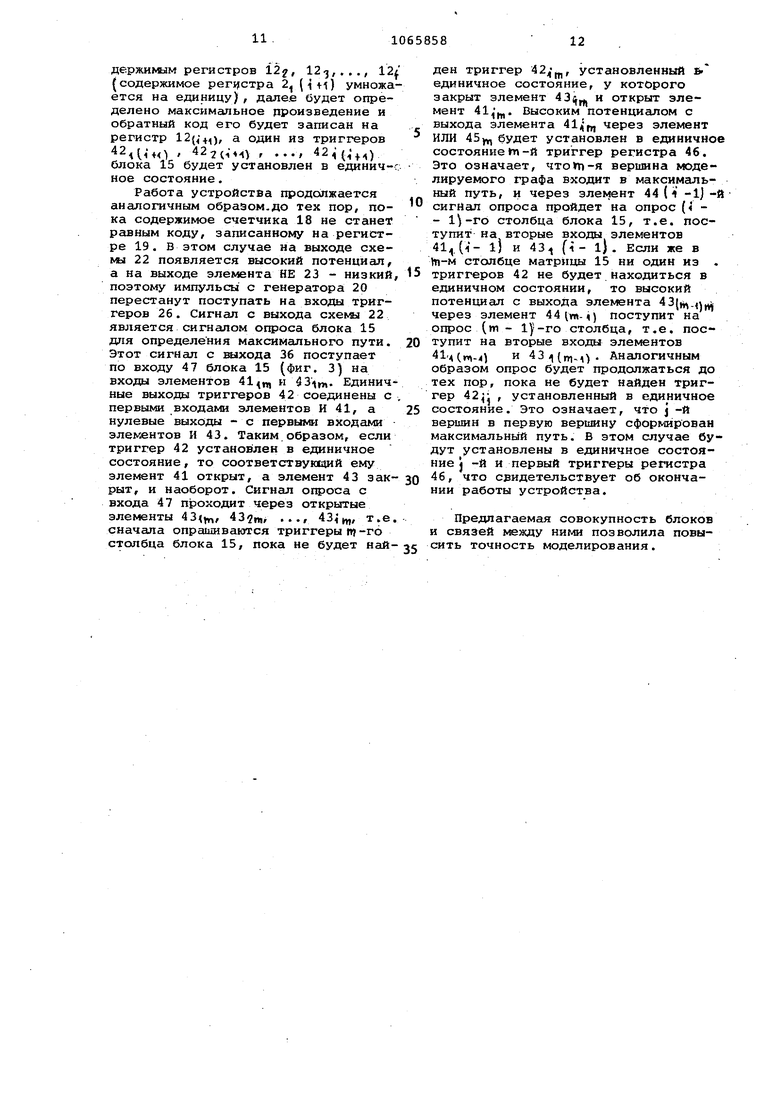

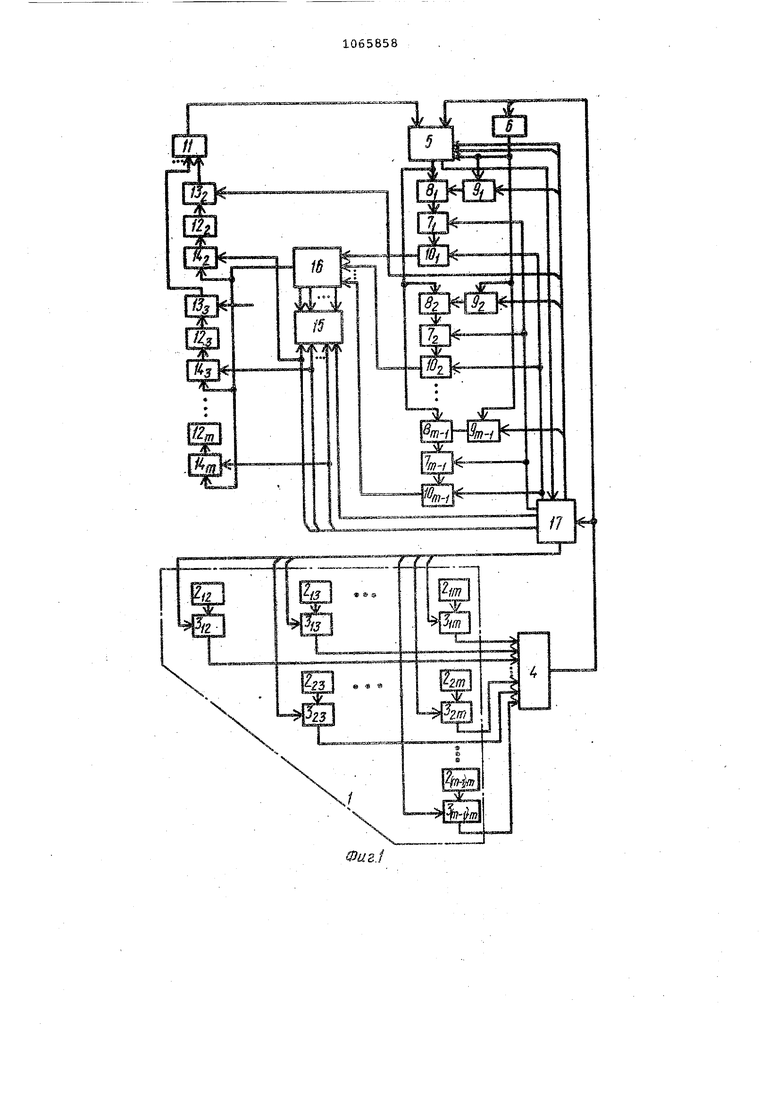

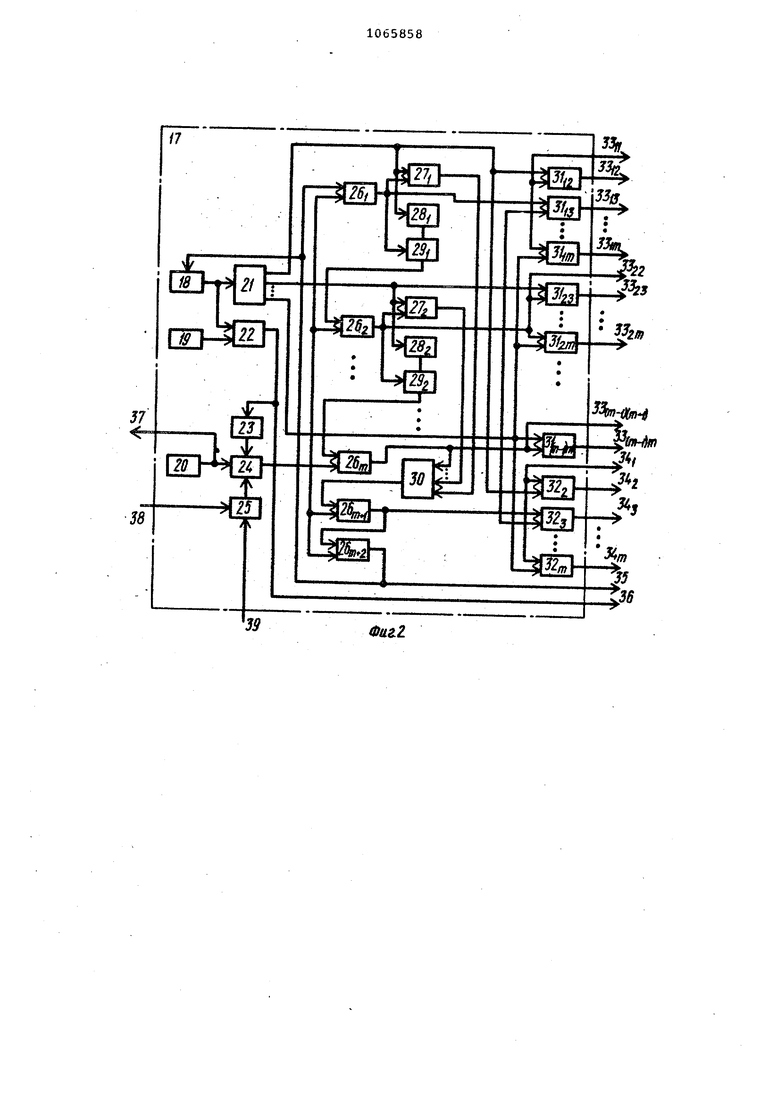

УСТРОЙСТВО ДЛЯ МОДЕЛИРОВА- . НИЯ СЕТЕВЫХ ГРАФОВ, содержащее треугольную матричную модель графа, ij-fi Узел которой включает регистр, выходы которого соединены с первым входом блока элементов И (где 4 1, m - 1, ) у + 1,т , m максимальное количество вершин в графе) , первую группу элементов ИЛИ, блок управления, первую группу регистров, блок формирователей пути , блок выбора максимального кода, вторую группу элементов ИЛИ, первую, вторую, третью, четвертую, пятую группы элементов И и .элемент ИЛИ, выход J-го peг ;cтpa первой, группы подключен к первому входу j-го элемента И первой группы, второй вход которого соединен с соответствующим разрядом первой выходной ыины блока управления, j -и разряд второй выходной шины которого подключен к первому входу j -го элемента И второй группы, выход которого соединен с входом J-го регистра первой группы, выход элемента ИЛИ подключен к первым входам элементов И пятой группы, вторые входы элементов И пятой группы соединены с соответствующими разрядами первой выходной шины блока управления, выход -4 -го элемента И пятой группы подключен к первому входу ( -го элемента И третьей группы, выход которого соединен с входом i-го регистра второй группы, выход которого подключен к первому входу i -го элемента И четвертой -группы, выход которого соединен с i -м входом группы блока выбора максимального кода, первая группа выходов которого подключена к вторым входам соответствующих элементов И второй группы, вторая группа выходов блока выбора максимального кода соединена с первой группой входов блока формирователей пути, вторая группа входов которого подключена к соответствуьацим разря-. дам второй выходной шины блока управления, первый Быход которого соеi динен с входом блока формирователей пути, .установочные входы регист ров второй группы подключены к втоpojvty выходу блока управления, третий выход которого соединен с вторыми входаил элементов И четвертой группы, выход ij -го блока элементов И треугольной катричной модели графа соединен с ni -м входом соответствуицего элемента ИЛИ первой группы, выходы элементов ИЛИ первой группы х :л эо :л эо подключены к входам элемента ИЛИ, j-ft разряд третьей выходной шины блока управления подключен к второму входу ij -го блока элементов И треугольной матричной модели графа, выход j-го элемента И первой группы i соединен с j -м входом соответствующего элемента ИЛИ второй группы, отличающееся тем, что, с целью повышения быстродействия, в него введен блок умножения, первый выход которого подключен к вторым входам элементов И третьей группы, второй выход блока умножения соединен с первым входом блока управления, j -и разряд первой выходной шины которого подключен к первому входу блока умножения, выход элемента ИЛИ соединен с вторым входом

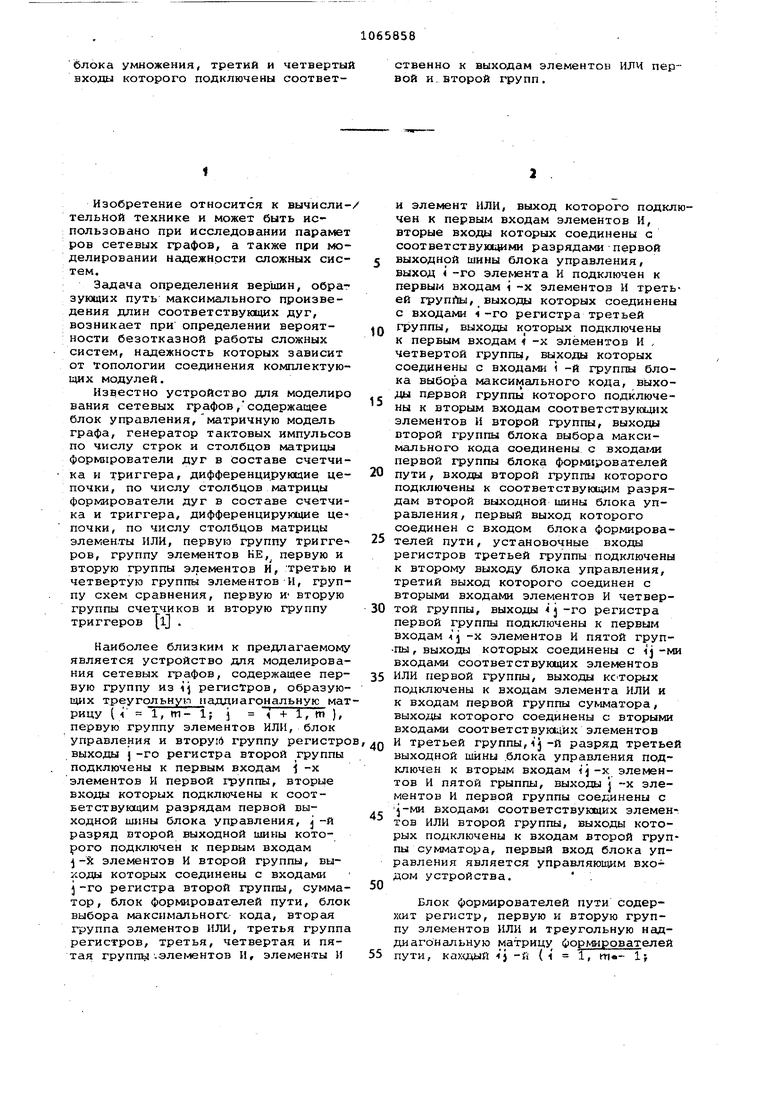

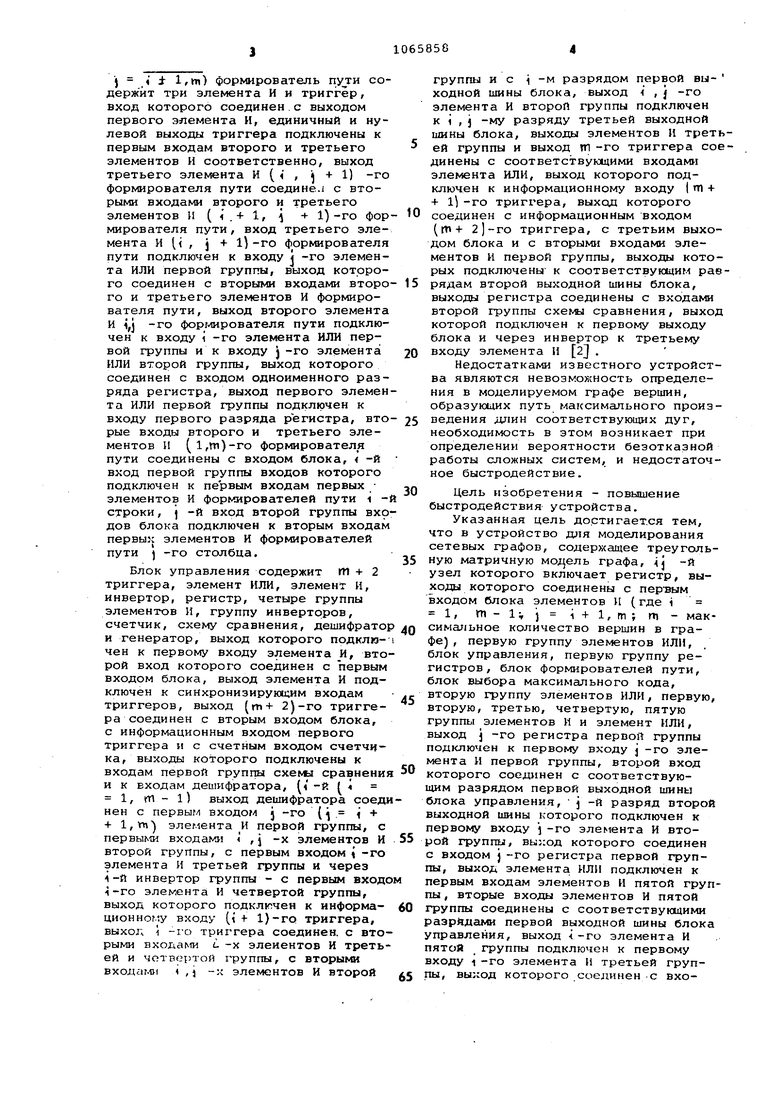

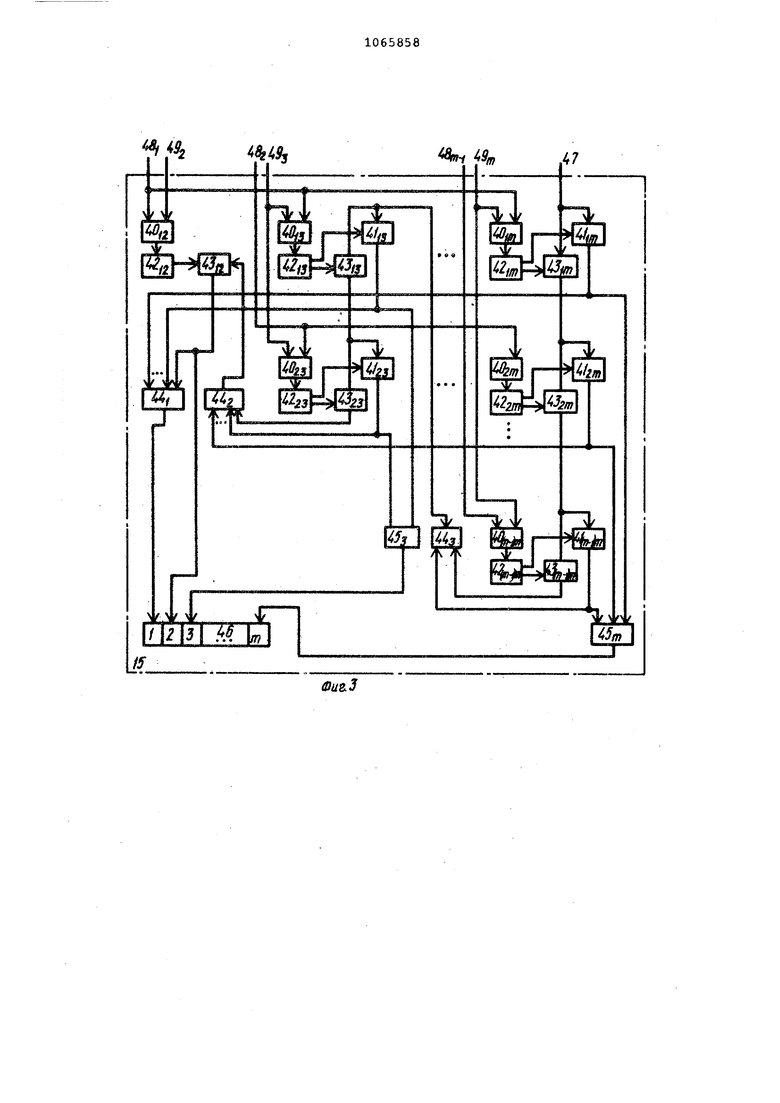

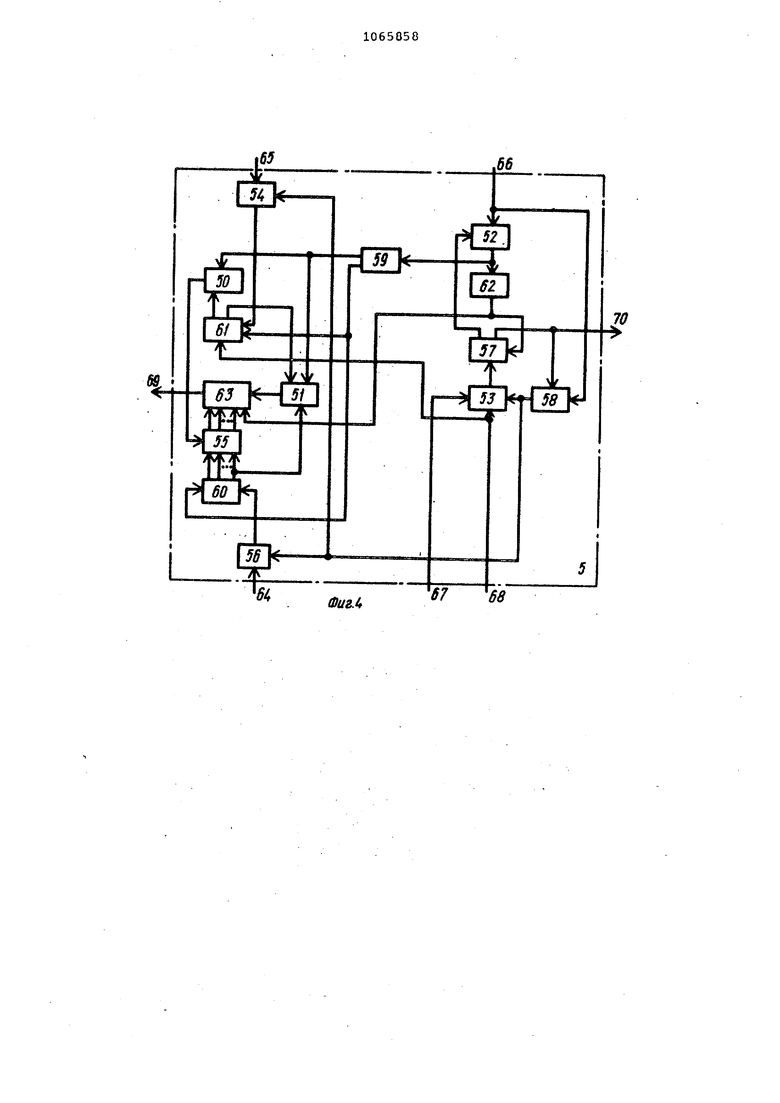

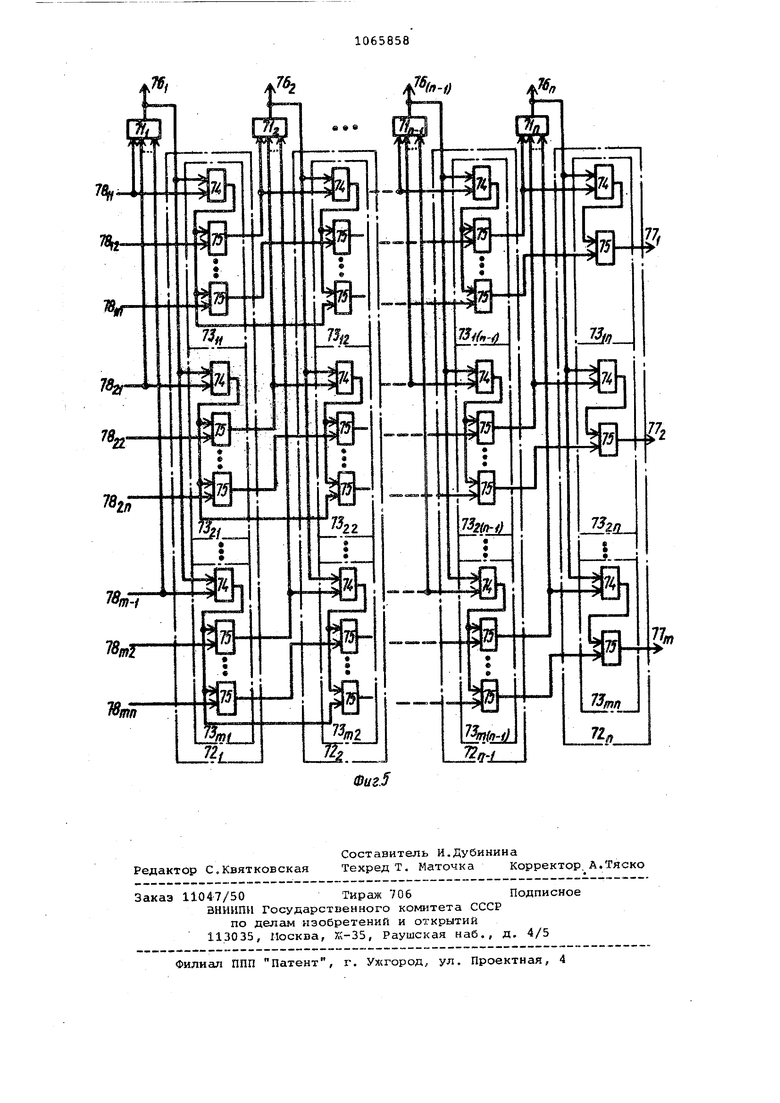

Изобретение относится к вычислительной технике и может быть использовано при исследовании парамет ров сетевых графов, а также при моделировании надажирсти сложных сиетем. Задача определения вершин, образующих путь максимального произведения длин соответствующих дуг, возникает при определении вероятности безотказной работы сложных систем, надежность которых зависит от топологии соединения комплектующих модулей. Известно устройство для моделиро вания сетевых графов,содержащее блок управления,матричную модель графа, генератор тактовых импульсов по числу строк и столбцов матрицы формирователи дуг в составе счетчика и триггера, дифференцирующие цепочки, по числу столбцов матрицы формирователи дуг в составе счетчика и триггера, дифференцирующие цепочки, по числу столбцов матрицы элементы ИЛИ, первую группу триггеров, группу элементов НЕ, первую и вторую группы элементов И, третью и четвертую группы элементов И, группу схем сравнения, первую и вторую группы счетчиков и вторую группу триггеров l . Наиболее близким к предлагаемому является устройство для моделирова ния сетевых графов, содержащее первую группу из ij регистров, образую щих треугольную паддиагональнук ма рицу (( 1, т- 1; i ч + 1, m ), первую группу элементов ИЛИ, блок управления и BTopyiii группу регистр выходы j-го регистра второй группы подключены к первым входс1М -х элементов И первой группы, вторые входы которых подключены к соответствующим разрядам первой выходной шины блока управления, j-и разряд второй выходной шины которого подключен к первым входам -Sc элементов И второй группы, выходы которых соединены с входами j-го регистра второй группы, сумма тор, блок формирователей пути, бло выбора максимального кода, вторая группа элементов ИЛИ, третья групп регистров, третья, четвертая и пятая группу-элег- нтов И, элементы И и элемент ИЛИ, выход которого подключен к первым входам элементов И, вторые входы которых соединены с соответствуюс ми разрядами первой выходной шины блока управления, выход i -го элемента И подключен к первым входам i-х элементов И третьей групЛы, выходы которых соединены с входами 4-го регистра третьей группы, выходы которых подключены к первым входам ч -х элементов И , четвертой группы, исходы которых соединены с входами i -и группы блока выбора максимального кода, выходы первой группы которого подключены к вторым входам соответствую14их элементов И второй группы, выходы второй группы блока выбора максимального кода соединены с входами первой группы блока формирователей пути, входы второй группы которого подключены к соответствую1цим разрядам второй выходной шины блока управления , первый выход которого соединен с входом блока форг-шрователей пути, установочные входы регистров третьей группы подключены к второму выходу блока управления, третий выход которого соединен с вторыми входами элементов И четвертой группы, выходы j-го регистра первой группы подключены к первым входам Ii -X элементов И пятой группы, выходы которых соединены с i j -ми входами соответствую1дих элементов ИЛИ первой группы, выходы ксторых подключены к входам элемента ИЛИ и к входам первой группы сумматора, выходы которого соединены с вторыми входами соответствующих элементов И третьей группы, Ij-и разряд третьей выходной щины .блока управления подключен к вторым входам ij-х элементов И пятой грыппы, выходы } -X элементов И первой группы соединены с j-ми входами соответствующих элемен-; тов ИЛИ второй группы, выходы которых подключены к входам второй группы сумматора, первый вход блока управления является управляющим входом устройства, Блок формирователей пути содер :шт регистр, первую и вторую группу элементов ИЛИ и треугольную наддиагональную матрицу формирователей пути, каходый V} -и ( 1 Т, n-ie- 1} ) i 1,№) формирователь пхти содержит три элемента И и триггер, вход которого соединен.с выходом первого элемента И, единичный и нулевой выходы триггера подключены к первым входам второго и третьего элементов И соответственно, выход третьего элемента И (i , + 1) -го формирователя пути соедине.1 с вторыми входами второго и третьего элементов И ( i .4- 1, -f 1)-го фор мирователя пути, вход третьего элемента И ( , j + формирователя пути подключен к входу 1 -го элемента ИЛИ первой группы, выход которого соединен с вторыми входами второ го и третьего элементов И формирователя пути, выход второго элемента И 1, -го фор1 1ирователя пути подключен к входу i -го элемента ИЛИ первой группы и к входу ) -го элемента ИЛИ второй группы, выход которого соединен с входом одноименного разряда регистра, выход первого элемен та ИЛИ первой группы подключен к входу первого разряда регистра, вто рые входы второго и третьего элементов И (l,ni)-ro формирователя пути соединены с входом блока, -и вход первой группы входов которого подключен к первым входам первых элементов И формирователей пути i строки, j -и вход второй группы вхо дов блока подключен к вторым входам первых элементов И формирователей пути -го столбца. Блок управления содержит т + 2 триггера, элемент ИЛИ, элемент И, инвертор, регистр, четыре группы элементов И, группу инверторов, счетчик, схему сравнения, дешифрато к генератор, выход которого подключен к первому входу элемента И, вто рой вход которого соединен с первым входом блока, выход элемента И подключен к СИНХРОНИЗИРУЮ1ДИМ входам триггеров, выход (т+ 2)-го триггера соединен с вторым входом блока, с информационным входом первого триггера и с счетным входом счетчика, выходы которого подключены к входам первой группы cxeNU сравнени и к входам дешифратора, (i -и 1, m - l) выход дешифратора соед нен с первым входом j -го ( . i + + l,) элемента И первой групгы, с nepBUNiH входами , j -х элементов И второй группы, с первым входом { -го элемента И третьей группы и через i-и инвертор группы - с первым вход 1-го элемента И четвертой группы, выход которого подключен к информационному входу (i + 1)-го триггера, выход i -го триггера соединен, с вто рыми входами L -X элеиентов И треть ей и четвертой группы, с вторыми входаг-in ,j -X элементов И второй группы и с i -м разрядом первой выходной шины блока, выход i , -го элемента И второй группы подключен к i ,j -му разряду третьей выходной шины блока, выходы элементов И третьей группы и выход m -го триггера соединены с соответствующими входами элемента ИЛИ, выход которого подключен к информационному входу I П1 + + триггера, выход которого соединен с информационным входом (tn + 2)-го триггера, с третьим выходом блока и с вторыми входами элементов И первой группы, выходы которых подключены к соответствующим раерядам второй выходной шины блока, выходы регистра соединены с входами второй группы схекы сравнения, выход которой подключен к первому выходу блока и через инвертор к третьему входу элемента И 2 , Недостатками известного устройства являются невозможность определения в моделируемом графе вершин, образующих путь максимального произведения длин соответствующих дуг, необходимость в этом возникает при определении вероятности безотказной работы сложных систем, и недостаточное быстродействие. Цель изобретения - повышение быстродействия устройства. Указанная цель достигается тем, что в устройство для моделирования сетевых графов, содержащее треугольную матричную моцель графа, ц| -и узел которого включает регистр, выходы которого соединены с первым входом блока элементов И (где i 1, m-lv ) i+l,m; m - максимальное количество вершин в графе) , первую группу элементов ИЛИ, блок управления, первую группу регистров, блок формирователей пути, блок выбора максимального кода, вторую группу элементов ИЛИ, первую, вторую, третью, четвертую, пятую группы элементов И и элемент ИЛИ, выход j -го регистра первой группы подключен к первому входу j -го элемента И первой группы, второй вход которого соединен с соответствующим разрядом первой выходной шинь блока управления, j -и разряд второй выходной шины которого подключен к первому входу j-го элемента И второй группы, вы5:од которого соединен с входом j-го регистра первой группы, выход элемента ИЛИ подключен к первым входам элементов И пятой группы , вторые входы элементов И пятой группы соединены с соответствующими разрядами первой выходной шины блока управления, выход i-го элемента И пятой группы подключен к первому входу 1 -го элемента И третьей группы, выход которого соединен-с входом f-го регистра второй группы, вы ход которого подключен к первому входу i-го элемента Н четвертой гру пы, выход которого соединен с li -м входом группы блока выбора максимал ного кода, первая группа выходов ко торого подключена к вторым входам соответствуквдих элементов И второй груцпы, вторая группа выходов блока выбора максимального кода соединена с первой группой входов блока формирователей пути, вторая группа,входов которого подключена к соответствующим разрядам второй выходной шины блока управления, первый выход которого соединен с входом блока формирователей пути, установочные входы регистров второй групп подключены к второму выходу блока управления, третий выход которого соединен с вторыки входами элементов И четвертой группы, выход if,-го блока элементов И треугольной матричной модели графа соединен CIJ-M входом соответствующего элемента ИЛИ первой группы, выходы эдементов ИЛИ первой группы подключены к входам элемента ИЛИ, j -и разряд треть ей выходной шины блока управления подключен к второму входу j-го блока элементов И треугсрльной матрично модели графа, выход j -го элемента И первой группы соединен с j-м входом соответствующего эпемеата ИЛИ второй группы, введен блок умножения, первый выход которого подключе к вторым входам элементов И третьей группы, второй выход блока умноже НИН соединен с первым входом блока управления, j -и разряд первой выходной шины которого подключен к первому входу блока умножения, выхо элемента ИЛИ соединен с вторым вхо дом блока умножения, третий и четвертый входы которого подключены соответственно к выходам элементов ИЛИ первой и второй групп. На фиг. 1 представлена структурная схема устройства для моделирова .ния сетевых графов; на фиг. 2 - то хсе, блока управления; на фиг. 3 то же, блока формирователей пути; на фиг. 4 - то же, блока yмнoжeния на фиг. 5 - то же, шифратора. Устройство для моделирования сетевых графов содержит (фиг. 1| треугольную матричную модель 1 графа, состоящую из регистров 2 / , 2/,.,уп и блоков элементов И - W .., 3(у,-1) т , где m максимальное количество вершин в графе, первую группу элементов ИЛИ блок 5 умножения, элемент ИЛИ б, вторую группу регистров,, 7, ..., 1т. , третью группу элементов И 8, В, ...г 8п1м пятую группу элементов И 9 , 9, ..., т- , чел вертуюгруппу элементов И 10, 10.,., / вторую группу элементов ИЛИ 11, первую группу регистров 12, 12з, .../ 12frt первую и вторую группы элементов И 13, 13 13„1., и 14, 14, блок 15 фор1-шрователей пути, шифратор 16, блок 17 управления. Блок 17 управления (фиг. 2) включает счетчик 18, регистр 19, генератор 20 тактовых импульсов, дешифратор 21, схему 22 сравнения, элемент КБ 23, элементы И 24 и 25, триггеры 26 , 2б2, .., элементы И 27lf , 272, f 21tn- элементы НЕ 28, 28, ft 2В ff). f элементы И 29, 29, ..., 29, , элемент ИЛИ 30, элементь И 31 , 31,, ..,, 31(п,.). и 32-;., 32, ..., 32, выходы 33, 33;52. . 33(ti,, 34, 34 2, ..., ,,., 34(jj, 35, 36 и 37, входы 38 и 39. Блок 15 форкшрователей пути (фиг. . включает элементы И , 40i3 , - 40(n..Jiv m 41, , 41 ,... ..,, 41 .),. , триггеры , .. 42(„,-,)m элементы И 43 43)4, ..., 43.д5 элементы . .; ИЛИ 44 , 44,, ..., 44,.1 , 45ч , . . . , .,., 45fn, регицтр 46, входам 47, 48, 48,., .,., 48,.4 и 49, 49э,... ... 49. Блок 5 умножения (фиг. 4) вклйчает элементы И 50 - 53, группы элементов И 54 - 56, триггеры 57 - 59, сдвигающие регистры 60 и 61, счетчик 62, сум.5атор 63 накапливающего типа, входы 64 - 68, выходы 69 и 70. Шифратор (фиг. 5J включает элементы ИЛИ-НЕ 71i , 71,j, ..., 71f, , где n - число разрядов в кодах, узлы 72, 722, , . . , 72j , анализа разрядов , состоящие из схем поразрядного переноса 73 i , 73;j.j , .,., 73(„,.« в состав которых входят элементы ИЛИ 74 и элементы И 75, выхо,цы 76, 76„ и 77, 77, входы 78ц , , ..., 70rt,h. Устройство для моделирования сетевых графов работает еледукядим образом.. jb исходном состоянии триггер 26 у,, 2 блока 17 установлен в единичное состояние, остальные триггеры 26 (i 1, ..., m+1) -в нулевое состояние. Сигналом с выхода триггера 26 уг s младший разряд счетчика 18 записывается единица, в результате только на первой выходной шине дешифратора 21 устанавливаатся высокий потенциал, который поступает на первые входы элементов И 27/1, 31;j2 и 32 и на вход элемента НЕ 2bf. Одновременно сигналом с выхода триггера 26,m-f2 по выходу 35 устанавливаются в нулевое состоя|Ние триггеры регистров 7, 7, ..,,

«/ 7дт1-ч . На регистр 19 блока 17 записывается код числа вершин в моделируемом графе, на регистры 2 г 2f , ..,, 2(,„.;, матрицы 1 записываются коды весов соответствующих дуг графа. Если дуги между какими-либо вершинами графа отсутствуют, то на соответствующих регистрах записаны коды нуля. Триггеры регистра 46 блока 15 установлены в нулевое состояние.

Устройство начинает работу после подачи входного сигнала по шине 39 блока 17. Этот сигналчерез элемент И 25 поступает навторой вход элемента И 24, и тактовые импульсы с выхода генератора 20 поступают на входы триггеров 26. С приходом первого импульса триггер 26- устанавливается в единичное состояние, при этом на выходе 33 «i появляется высокий потенциал, который поступает на вход элемента И 9, ас выхода высокий потенциал поступает на входы группы . В результате код с регистра через открытую группу {2 г группу элементов ИЛИ 4 поступает на вход блока 5 и подается . также на вход элемента 6. В зависимости от содержимого регистра 2 2 на выходе элемента 6 форг ируется высокий или низкий потенциал, запрещающий или разрешающий работу блока умножения и запись на регистры 7 результатов умножения. Если код на регистре 2 ненулевой, то на выходе элемента 6 формируется высокий потенциал, и наоборот.

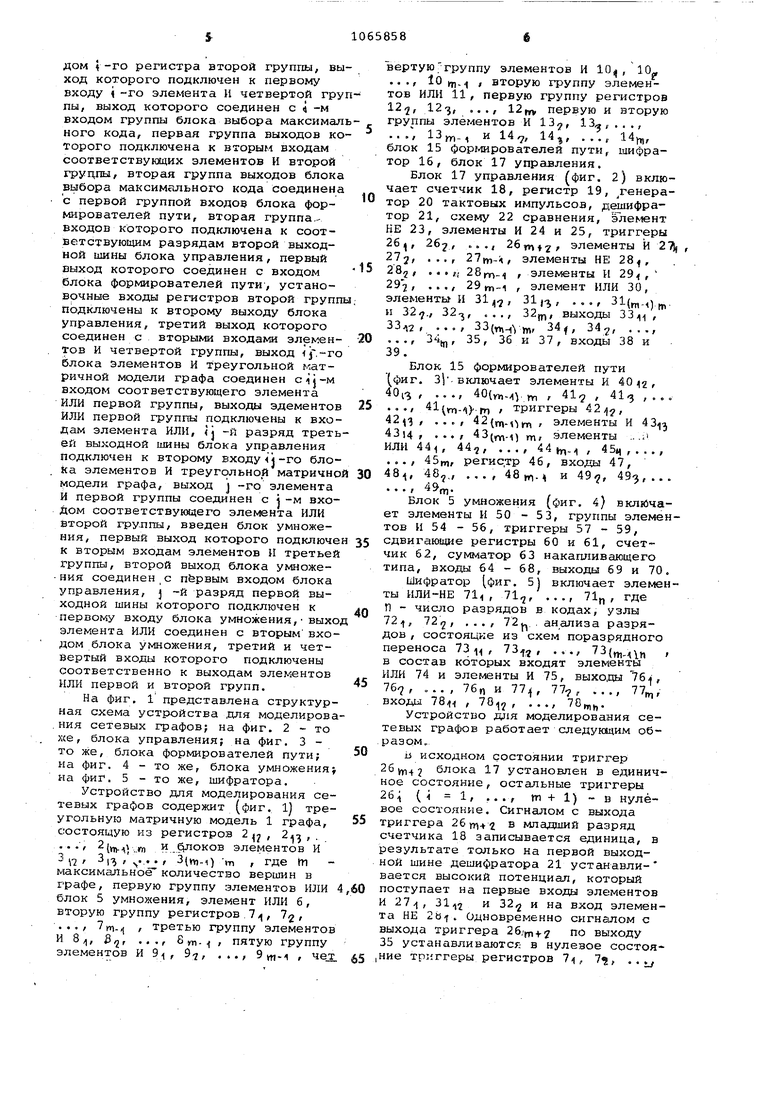

Блок 5 умножения функционирует следующим образом.

В исходном состоянии триггер 57 находится в нулевом состоянии. С прямого выхода этого триггера низкий потенциал подается на второй вход элемента И 52. С инверсного выхода триггера 57 высокий потенциал по выходу 70 подается на вход 38 блока 17 фиг. 2 и на вход триггера 58, который находится в единичном состоянии. С выхода триггера 58 высокий потенцисш подается на трег тий вход элемента 53 и на группы элементов И 54 и 56.

Высокий потенциал с выхода 33 блока 17 поступает по входу 68, в результате чего записывается единица в старший разряд регистра 61 и . I высокий потенциал поступает также на второй вход элемента И 53. По синалу с выхода 33||2 код, записанный на регистре (если он нулевой), поступает по входу 64 и через откры тый элемент И 56 записывается на регистр 60. С выхода элемента 6 высокий потенциал поступает навход 67 и через элемент И 53 устанавлнвается в единичное состояние триггер

На второй вход элемента И 50 подается высокий потенциал с триггера старшего разряда регистра множителя 61. На выходе элемента И 50 появляется, высокий потенциал, поступающий на элемент И 55. Множимое, находящееся на регистре 60, через открытый элемент И 55 поступает на вход сумматора 63, где происходит сложение кодов, lia первый и второй входы элемента И 51 поступают сигналы с второго по старшинству триггера регистра 61 и нулевого триггера регистра 60. Если эти триггеры будут Находиться в единичном состоянии, то с. выхода элемента И 51 в дополнительный разряд сумматора записывается единица. С приходом следующего тактового импульса к со.держимому счетчика 62 приставляется едщница и триггер 59 устанавливается в нулевое состояние. С инверсного выхода этого триггера высокий потенциал поступает в цепи сдвига геристров 60 и 61, причем содержимое регистра 60 сдвигается на один разряд в сторону младших разрядов, а содержимое регистра 61 - в сторону старших разрядов. Умножение продолжается до прихода ( п+ 1)-го тактового импульса, при этом на выходе счетчика 62 появляется единица переполнения. Данный сигнал усТсШавливается в нулевое состояние триггер 57 и подается в дополнительный разряд сумматора 63 для округления результата умножения. С прямого выхода триггера 57 низкий потенциал подается на второй вход элемента И 52, ас инверсного выхода этого элемента высокий потенциал подается на вход триггера 58 и по выходу 70 поступает на вход 38 блока 17, тем сакым разрешая тактовым импульсгш через элемент 24 проходить в блок 17 управления.

Если код, считываемый с регистра нулевой, то на выходе элемента 6 формируется сигнал низкого уровня,

который по входу 67 поступает на вход элемента И 53,-запрещая работу блока ушюжения.

Результат умножения парафазным кодом через открытый элемент 8 записывается на регистр 7. В блоке 17 сигнал логической единицы с выхода триггера 26 через элементы 27f и 30 поступает на вход триггера 26. С приходом следуквдего тактового импульса данный триггер устанавливается в единичное состояние, а триггер - в нулевое. При этом на выходе 34 появляется высокий потенциал, который поступает на элемент 10 (фиг. 1). В результате прямые коды чисел, записанные на регис рах 6, поступают на входы шифратора 16,

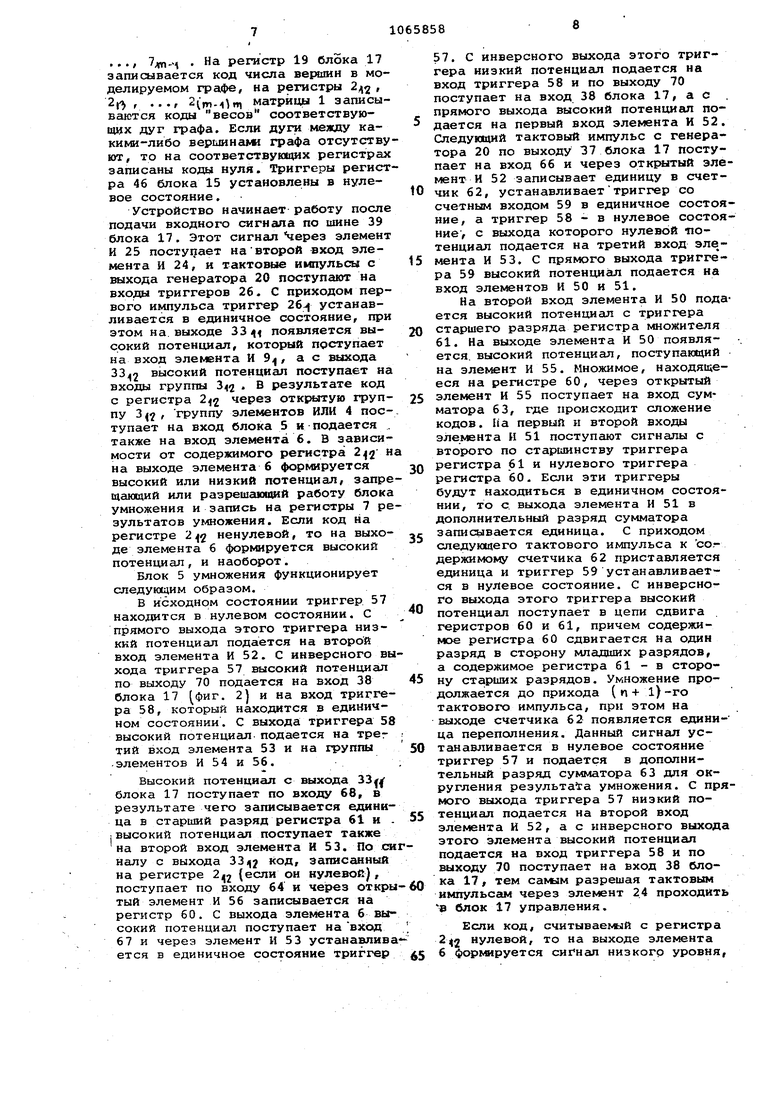

Шифратор 16 функционирует следующим образом.

На входные шины 78 поступает (т - l) чисел с выходов элементов 10. В первый момент анализируются стар.шие разряды. Если хотя бы один из старших разрядов чисел равен единице, то на выходе элемента ИЛИ-НЕ 71 появляется низкий потенциал, которы запрещает анализ остальных разрядов тех кодов, старшие разряды которых равны нулю. Остальные разряды кодов, старшие разряды которых равны единице, проходят через элементы И 75 узла 72 . Если старшие разряды всех кодов равны нулю, то на выходе элемента 71;( формируется высокий потенциал и все остальные разряды кодов проходят через узел 72 j для дальнейшего анализа. Аналогичным образом анализируются вторые по старшинству разряды всех кодов и т.д. В результате на выходах 77, 77 , . . о , Т}.т- будет сформирован позиционный код номера максимального числа, а на выходах 7б,(, 1( t ..., 76 я - Обратный код максимального числа из записанных на регистрах 7, .

В рассматриваемом случае код максимального числа записан на регистре 7( (триггеры остальных регистров 1, где 2, ..., 1Г7 - 1, находятся в нулевом состоянии), поэтому поле анализа обратный код этого числа будет сформирован на выходах 76, а на выходе 77 появится сигнал логической единицы, сигнализирующий о том, что максимальный код записан на регистре 7i.

Одновременно с появлением сигнала на выходе 34 блока 17 появится высокий потенциал на выходе 345, коТорый поступает на вход элемента 14о(фиг. 1, в результате чего обратный код максимального числа с выхода блока 16 записывается (парафазным кодом на регистр 12. Сигнал с выхода J4 также поступает по входу 49-2 на элемент 40,|у блока 15, на первый вход которого поступает сигнал по входу 48 с шифратора 16.

В результате триггер 42 устанавливается в единичное состояние.

С приходом следующего тактового импульса триггер 26 устанавливается в нулевое, а триггер в единичное состояние.

Сигналом с выхода элемента 26. устанавливаются в нулевое состояние триггеры регистров 7 и содержимое счетчика 18 увеличивается на единицу, после чего высокий потенциал появляется на втором выходе дешифратора 21. С приходом очередного тактового импульса триггер 26 /( устанавливается в единичное состояние, поэтому высокие потенциалы появятся на выходах 33 и результат умножения кода, содержащегося на регистре 2,(3 матрицы 1 (если код ненулевой) в данном случае на единицу, будет записан на регистр 7ij . С приходом следукнцего тактового импульса триггер 26; устанавливается в нулевое, а триггер 26 - единичное состояние, в результате высокие потенциалы устанавливаются на выходах н-ЗЗ. Результат углножения кода находя1цегося на регистре 22-z матрицы 1, с кодом, находящимся на регистре 12 -2 (по сигналу ЗЗ. открывается элемент 13, подключенный к инверсным выходам триггеров регистра , будет записан на регистр 1 .

С-приходом следующего тактового импульса триггер 26 бдока устанавливается в нулевое, а триггер 26(Т1-н1 в единичное состояние. В результате высокие потенциалы появятся на выходах 34 ; и 34, которые обеспечат выдачу кодов с регист ров 7 в блок 16, запись обратного кода максимального из них на регистр 123 и установку в единичное состояние одного из триггеров 42;(j или 422 блока 15 в зависимости от того, на каком из регистров 7 или 7, был записан больший код.

С приходом очередного тактового импульса триггер 26 fp будет установлен в Нулевое состояние,, а триггер в единичное, в результате трипперы регистров 7 будут установлены в нулевое состояние и будет добавлена единица в младший разряд счетчика 18, а на третьем выходе дешифратора 21 сформируется сигнал высокого уровня.

Далее работа устройства происходит аналогично. Например, в -j -м цикле работы будет произведено перемножение содержимого регистров 2 (i + 1)-го столбца матрицы с содержимым регистров 12, 12з,..., 12 {содержимое perijCTpa 2 (itl) умножа ется на единицу), далее будет определено максимальное произведение и обратный код его будет записан на регистр 12(4+,), а один из триггеров 22(;мУ , .../ 42,(4) блока 15 будет установлен в единичное состояние. Работа устройства продолжается аналогичным обраэом.до тех пор, пока содержимое счетчика 18 не станет равным коду, записанному на регистре 19. В этом случае на выходе схеълл 22 появляется высокий потенциал, а на выходе элемента НЕ 23 - низкий поэтому импульсы с генератора 20 перестанут поступать на входа триггеров 26. Сигнал с выхода схеьвл 22 является сигналом опроса блока 15 для определения максимального пути. Этот сигнал с выхода 36 поступает по входу 47 блока 15 (фиг. 3) на входы элементов 41 j Единич ные выходы триггеров 42 соединены с первыми входами элементов И 41, а нулевые выходы - с первыми входами элементов И 43. Таким образом, если триггер 42 установлен в единичное состояние, то соответствуидий ему элемент 41 открыт, а элемент 43 зак рыт, и наоборот. Сигнал опроса с входа 4 7 проходит через открытые элементы 43, 435ni, ..., , т.е сначала опрашиваются триггеры -го столбца блока 15, пока не будет най ден триггер 42,-, установленный в- единичное состояние, у которого закрыт элемент 43ij и открыт элемент . Высоким потенциалом с выхода 41;( через элемент ИЛИ 45у будет установлен в единичное состояние Hi -и триггер регистра 46. Это означает, вершина моделируемого графа входит в максимальный путь, и через элемент 44(4 -1J-и сигнал опроса пройдет на опрос ( - столбца блока 15, т.е. поступит на вторые входы элементов 41 (i- ij и 43 l). Если же в hi-M столбце матрицы 15 ни один из . триггеров 42 не будет находиться в единичном состоянии, то высокий потенциал с выхода элемента 43(й. через элемент 44iv«-) поступит на опрос (т - 1|-го столбца, т.е. поступит на вторые входы элементов 41Um- l и 43 („,,,). Аналогичным образом опрос будет продолжаться до тех пор, пока не будет найден триггер 42 , установленный в единичное состояние. Это означает, что j -и вершин в первую вершину сформирован максимальный путь. В этом случае будут установлены в единичное состояние j -и и первый триггеры регистра 46, что свидетельствует об окончании работы устройства. Предлагаемся совокупность блоков и связей между ними позволила повысить точность моделирования.

Фаг.2. ППЗ 4 Ul , 49

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения крат-чАйшЕгО пуТи B гРАфЕ | 1979 |

|

SU842842A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3341571/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-07—Публикация

1982-03-24—Подача