а

о

Иг обретение относится к технике связи и может испольковгггься для ре reHejpauHH цифровых сигналов по волноводу, световоду, коаксиальному кабелю, радиорелейным линиям и с помощью различных кодов„

По основному авТо св. 856032 известен видеорегеьератор цифровых сигналов с автоматической регулировкой усиления ЧАРУ), содержащий последовательно соединенные блок вычитания, регулируемой усилитель и решающий блок, два .детектора, выходы которых подключены к соответствующим входам блока вычитания, формирователь, вход которого соединен с выходом регулируемого усилителя, а выход - с тактовым-, входами решающего блока и двух детекторов, сигнальные входы которых соединены с выходом решающего блока, а их управляющие входы с выходом регулируемого усилителя, причем каждый детектор выполнен в виде последовательно соединенных порогового блока, сумматора по модулю два и интеграторгг, при этом выход интегратора, входы с у -.« тор а и порогового блока .являются выходом и входамз-1 детектора 1,

Недостатком известного видеорегенератора является точносаь регенерации . влиянтля изменений моментов схробирования в решающем к пороговых блоках, обусловленных дрейфом фазы импульсов на выходе формирователя по отно уению к фазе импульсов ia выхода регулируемого усилителя (температурный и временной дрейф)„ При изменении моментов стробировггния и,зменяеугся амплитуда регулируюш.его напряжег-п я- снстеглы ЛРУ, что приводит к несоответствию порога в решающем блоке амплитуде регенерируемых импульсов и ухудшению помехоустойчивости регенератора,

Цель 1-::зоб.рете1-:ия - повы1::ение точиости ре1енерадии сигналов ,. .-:

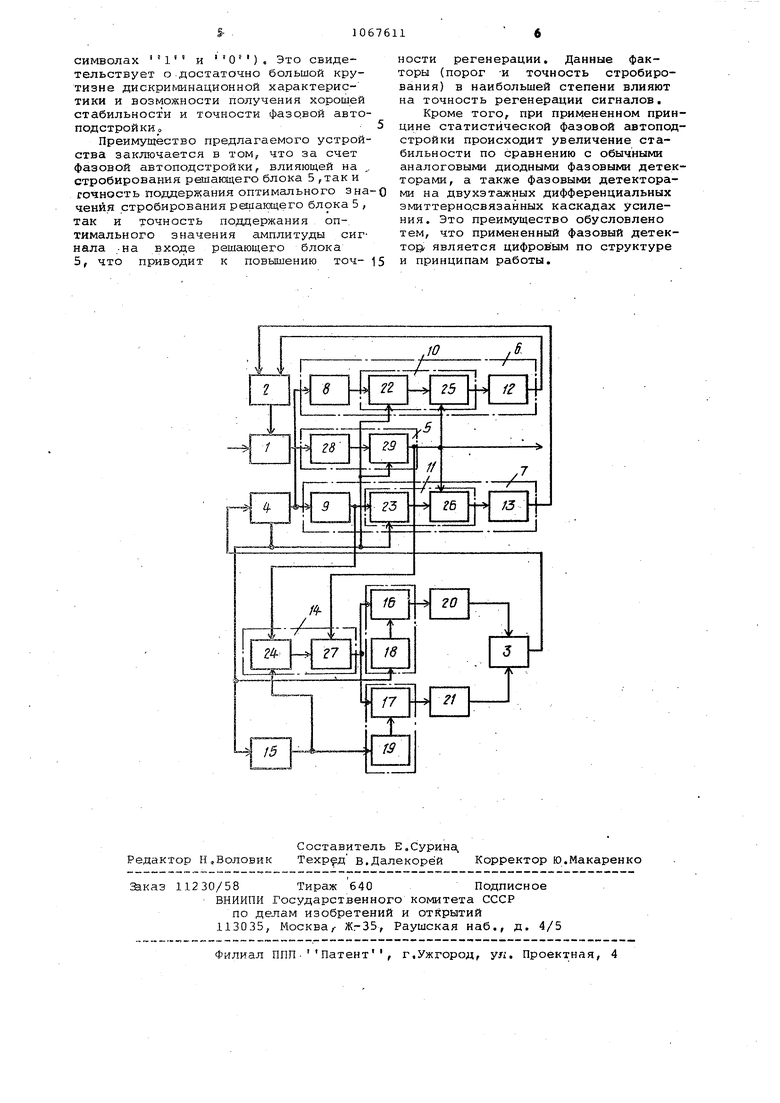

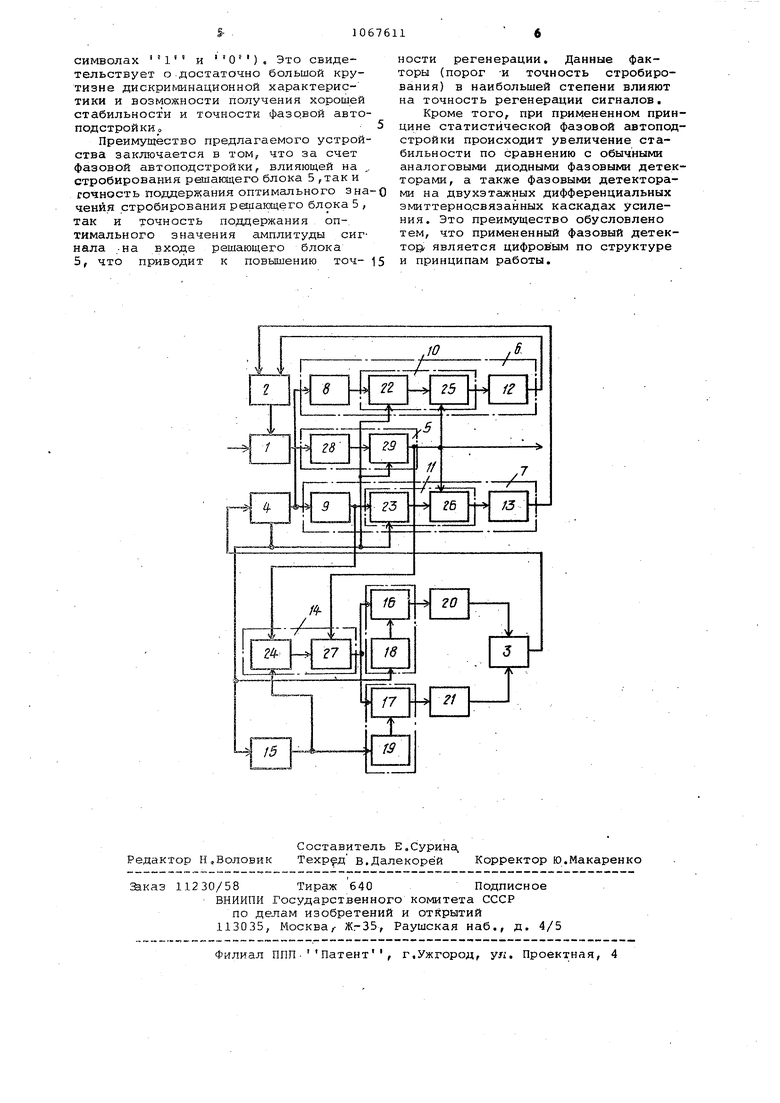

Поставленная najib достигается тем что в видеорегенератор цифровых сиг-налов с автоматической регулировкой усиления (АРУ) введены суг &1атор по модулю два. два В-триг /ера, два интеграторе. второй бдок вычитания, фазовращатель и два блока задерл ки, причем выход фррмователя через послеовательно соединенные еразовраш,атель И сумматор по модулю два подключен к входам первого и второго D-тригге-ов, выходы которых через соответствующие интеграторы подключены к вхо-. ам второго вычиталощего блока., которого подключен к управляющеу входу формирователя, вход и выод фазовращателя соответсственно чеез первый и второй блоки зг держки оединены с другнм : входггми О-тригерон f выход решггющего блока и .вы™ од порогового блока второго детек-тора подключены соответственно к второму и третьему входу сумматрра по модулю два.

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит регулируемый усилитель 1, блоки 2 и 3 вычитания, формирователь 4, решающий блок 5, детекторы 6 и 7, состоягдие из пороговых блоков 8 и 9, сумматоров 10 и 11 по модулю два и,интеграторов 12 и 13, сумматор 14 по модулю два, фазовращатель 15, D-триггера 16 и 17, блоки 18 и 19 задержки, интеграторы 20 и 21, сумматоры 10, 11 и 14 по модулю два состоят из D-триггеров 22 - 24 и полусумматоров 25 - 27, а решающий блок 5 состоит из пороговог блока 28 D-триггера 29.

Регенератор работает следующим образом

Бинарные сигналы, подлежащие регенерации, поступают на вход устройства, а затем после усиления в регулируемом усилителе 1 - на вход решающего блока 5, в котором происходит восстановление передаваемого сигнала по форме и временному положению. Тактовая застота вьщеляется из сигнала с помощью формирователя 4, на выходе которого вырабатываются прямоугольные импульсы (меандр) тактовой частоты.Если в момент полохсительного фронта напряжения тактовой частоты напряжение на входе решающего блока 5 превышает порог,то на выходе D-триггера 29 формируется импульс с задержкой на один такт. Этот импульс имеет длительность, равную одному такту, и соответствуЕсли такого превы1

ет символу

шения порога нет, то на выходе D-триггера 29 появляется пробел, соответствующий символу О. Действие помех приводит к трансформации передаваемых символов в противоположные посвоему значению, т.е. возникают сбои э передаваемом сообщении. При отклонении амплитуды сигнала от оптимального значения, соответствующего определенному порогу в решающем блоке 5, вероятности ошибок увеличиваются. Восстановление амплитуды сигнала до ее оптимального значения производится системой автоматической регулировки усиления, содержащей деTeKTopF:. 6 и 7, а также первый блок вычитания 2« .

Работа системы АРУ основана на измерении вероятностей попадания сигнала и шума в область напряжений больше и меньше порога решающего блока 5, причем максимальная и минимальная амплитуды напряжений смеси сигнала и шума ограничены по- рогами пороговых блоков 8 и 9..Оценка указанных вероятностей производится сумматорами и интеграторами. 12 и 1.3 в момент стробирования детек торов 6 и 7 тактовыми импульсами. Параметры детекторов 6 и 7 подбираются таким образом, что в установившемся режиме указанные вышевероятности равны. При отклонении значеНИИ напряжений сигнала в моменты стробирования детекторов 6 и 7 по их тактовым входам от оптимальной величины порога нарушается равенство указанных вероятностей, что приводит к появлению регулирующего напряжения на выходе блока 2 вычитания. В результате действия этого напряжения система АРУ восстанавливает значение напряжения сигнала на входе решающего блока 5 в момент действия стробирующих импульсов на тактовых входах детекторов 6 и 7, т.е. делает его равным оптимальному порогу. Использование D-триггеров в детекторах 6 и. 7, а также в решающем блоке 5 позволяет оказаться от форми рования узких стробирующих импульсо в формирователе 8. Это обусловлено тем, что. D-триггер (например типа MS тактируется фронтом прямоугольного напряжения, поступающего на его вход синхронизации. При этом запись инфор мации в D-триггер 24 с выхода порог вого блока 9 производится со сдвиго /на +180 (т.е. на + /2) , где Т -так товый интервал) по отношению к моме ту опроса решающего блока 5 не инве тированным напряжением тактовой час тоты. В эти моменты времени величин напряжения сигнального импульса сос тавляет приблизительно половину от максимального значения и находится в области максимальной крутизны изменения фронта импульсного сигнала передаваемой информации. Действие п |Мех приводит к тому, что прог сходит превышение или непревышение порога порогового блока 9 суммарным напряжением сигнала и помех в указанные моменты времени ± Т/2. Если сигнал сдвинут по фазе по .отношениюк тактовому напряжению, то .вероятность превышения (и соответственно непревышения) порога блока 9 в моменты :стробирования - Т/2 по отношению К моментам стробирования решающего . блока 5 не равна вероятности превы. шения порога (и соответственно его непревышёния) в моменты ±/2. Это обстоятельство и определяет принцип работы предлагаемого устройства. . Сумматор 14 оценивает неравно. значность решений, принятых решающим блоком 5 и пороговым блоком 9 соответственно в различные моменты времени, сдвинутые на половину пери да тактовой частоты, причем в перво половине напряжения сумматора 14 содержится информация о неравнознач ности по отношению к решению в пороговом блоке 9 в момент времени, предшествующий решению в решающем.блоке 5, а во второй половине - о неравнозначности по отношению к решению в пороговом блоке 9 в момент времени, запаздывающий по отношению к решению в решающем блоке 5. При сдвиге по фазе сигнала по отнош нию к вырабатываемому тактовому напряжению вероятности двух указанных выше сигналов неравнозначности не равны, что может быть использовано для корректировки фазы напряжения тактовой частоты. D-триггеры 16 и 17 фиксируют .указанные неравнозначности, а затем интеграторы 20 и 21 усредняют соответствующие напряжения неравнозначности. Регулирующее напряжение в соответствии с указанным принципом работы появляется на выходе второго блока 3 вычитания при неравенстве вероятностей неравнозначных решений. Благодаря обратной связи с выхода второго блока 3 вычитания на управляющий вход формирователя 4 прои ходит корректировка фазы напряжения тактовой частоты, и момент стробирования порогового блока 28 приближа- ; ется к оптимальному значению соответствующему максимуму входного сигнала. При этом система АРУ обеспечивает соответствие амплитуды сигнала опти..мальному значению порога. При отклонениях формы сигнала от симметричной требуется корректировка величины фазового сдвига в фазовращателе 15 относительно значений t/2, что может быть достигнуто либо путем включения последовательно с инвертором в фазовращателе 15 линии задержки небольшой величины (напри мер, одного-двух корпусов интегральных схем) либо вычитанием напряжений интеграторов 20 и 21 с неравными весами . Блоки задержки 18 и 19 предназначены для компенсации задержки импульсов в цепях сумматора 14. В качестве этих блоков задержки могут быть также использованы интегральные схемы (например, один-два корпуса повторителя напряжений). Анализ показывает, что на форму дискриминационной характеристики, фазового детектора, незначительно влияет коэффициент корреляций шумов, а также различие порогов пороговых блоков 9 и 28. Это обусловлено тем, что на характеристику фазового детектора в большей степени влияют межсимвольные помехи, а не шумы входного усилителя видеорегёнератора. Максимальное значение дискриминационной характеристики соответствует вероятности появлений импульсов равной 1/2 (при равновероятных

О ) . Это свидеЧ.

символах

тельствует о достаточно большой крутизне дискриминационной характеристики и возможности получения хорошей стабильности и точности фазовой автоподстройки,,

Преимущество предлагаемого устройства заключается в том, что за счет фазовой автоподстройки, влияющей на ., стробирования решающего блока 5 ,так и сочность поддержания оптимального зна ченйя стробирования решающего блока 5 , так и точность поддержания оп-. тимального значения амплитуды сигнала -на входе решающего блока 5, что приводит к повышению точности регенерации. Данные факторы (порог -и точность стробирования) в наибольшей степени влияют на точность регенерации сигналов.

Кроме того, при примененном принцине статистической фазовой автоподстройки происходит увеличение стабильности по сравнению с обычными аналоговыми диодными фазовыми детекторами, а также фазовыми детекторами на двухэтажных дифференциальных эмиттерносвязанных каскадах усиления. Это преимущество обусловлено тем, что примененный фазовый детектор, является цифровым по структуре и принципам работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Видеорегенератор цифровых сигналов с автоматической регулировкой усиления | 1979 |

|

SU856032A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460225C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| Устройство контроля работоспособности видеорегенератора цифровой системы связи | 1981 |

|

SU1054912A2 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2003 |

|

RU2271071C2 |

| Устройство контроля работоспособности видеорегенератора цифровой системы связи | 1979 |

|

SU951727A2 |

| Устройство для контроля работоспособности видеорегенератора цифровой системы связи | 1979 |

|

SU879789A1 |

| Устройство для подавления помех | 1983 |

|

SU1095419A1 |

| ДИСКРЕТНЫЙ СОГЛАСОВАННЫЙ ФИЛЬТР | 2005 |

|

RU2310978C2 |

ВИДЕОРЕГЕНЕРАТОР ЦИФРОВЫХ СИГНАЛОВ С АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКОЙ УСИЛЕНИЯ . по авт. св. № 856032, отличающийся тем, что, с целью повышения точности регенерации сигналов, введены сумматор по модулю два, два D-триггера, два интегратора, второй блок вычитания, фазовращатель и два блока задержки, при.чем выход формирователя через последовательно соединенные фазовращатель и сумматор по модулю два подключен к входам первого и второго D-триггеров, выходы которых через соответствующие интеграторы подключены к входам второго вычитающего, блока, выход которого подключен к управляющему входу формирователя, вход и выход фазовращателя соответственно , через первый и второй блоки задержки соединены с.другими входами D-трйггеров, выход решающего блока и выход порогового блока второго детектора подключены соответственно к второму и третьему входу сумматора (Л по модулю два.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Видеорегенератор цифровых сигналов с автоматической регулировкой усиления | 1979 |

|

SU856032A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-01-15—Публикация

1980-07-16—Подача