а ;о

изобретение относится к вычислительной и измерительной технике.

Известны реверсивные кольцевые счетчики, содержащие триггеры на транзисторах с различным типом проводимости, объединенные в кольцевые декады с помощью междукаскадных конденсаторов и общих эмиттерных резисторов транзисторов одного типа проводимости , каждый резистор подключен к входам прямого и обратного счета, выходы первой кольцевой декады соединены с входами триггера реверса. .

. Однако известные счетчики сложны как в конструктивном, так и в схемном выполнении и недостаточно надежны в работе.

Целью изобретения является упрощение устройства и повьаиение надежности в работе.

Поставленная цель достигается тем, что счетчик содержит разделительные диоды, причем триггер реверса выполнен на транзисторах с различным типом проводимости, к одному из входов которого подключен инвертор на транзисторе, коллектор которого соединен через разделительный диод в каждой декаде с общим эмиттерным резистором транзисторов одного типа проводимости, другой выход триггера соединен через разделительный диод в каждой декаде с общим эмиттерным резистором тран.зисторов противоположного THrta Проводимости.

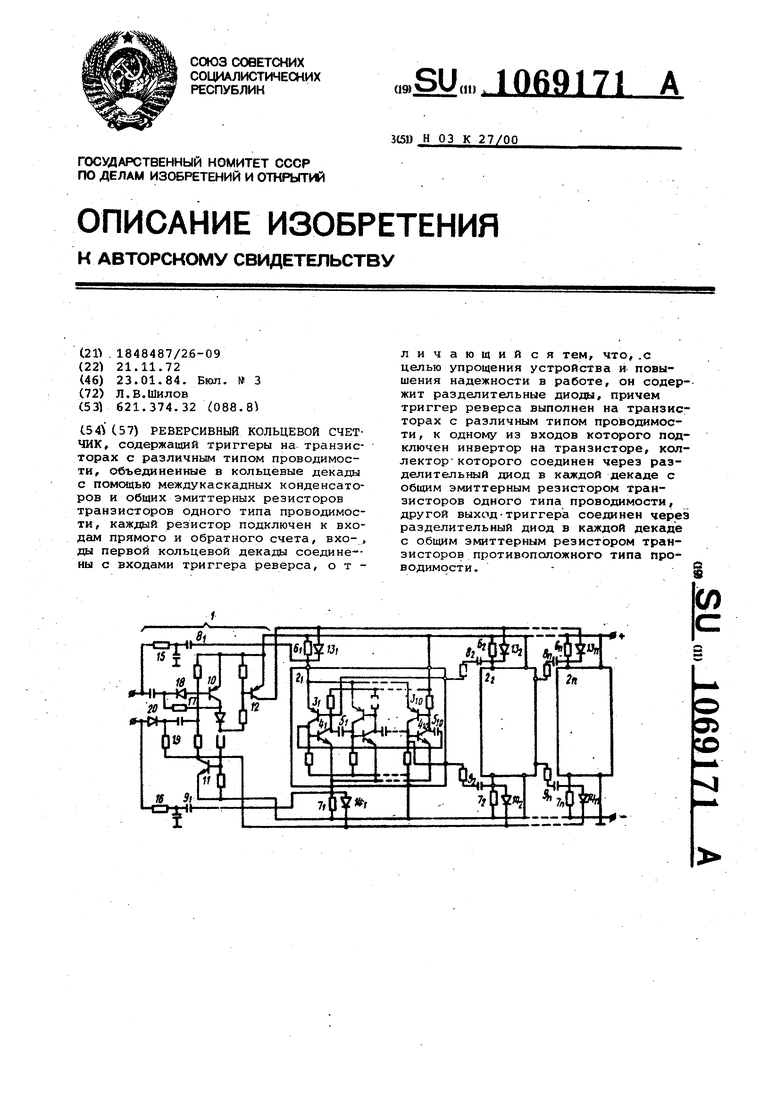

На чертеже представлена функциональная схема предлагаемого реверсивного кольцевого счетчика.

Реверсивный счетчик, состоит из схемы реверса 1 и счетных декад 2,2а .

Каждая декада 2 выполнена на десяти триггерах, каждый из которых содержит по два транзистора 3 - Зд,и 4i соответственно имеющих различный тип проводимости. Триггеры счетных декад 2 объединены в кольцевую схему с десятью устойчивыми состояниями с помощью междукаскадных емкостных связей - конденсаторов 5л. - 5до и общих эмиттерных резисторов б - 6h и 7д - 7п соответственно для группы транзисторов 3 - 3« и 4;( - 4x0 всех счетных декад 2л - 2 . Каждая группа транзисторов 34 - 3|(о и 4;( - 4 имеет одноименную проводимость. Резисторы бд - 6rt каждой декады 2 - 2h подключены через конденсаторы 8, 8о к входу прямого счета, а резисторы 7д - 7rt через конденсаторы - к входу обратного счета.

Схема реверса 1 содержит триггер реверса, выполненный на транзисторах 10 и 11 с различным типом проводимости, и инвертор на транзисторе, подключенный к одному из выходов триггера реверса. Входы младшей декады 2, объединены соответственно с входами триггера реверса. &аход 5 инвертора 12 соединен с общими

эмиттерными резисторами 6, - бр каждой счетной декады 2 - 2 через разделительные диоды 13л - 13п . Другой выход триггера реверса (кол0 лектор транзистора 11J подключен к общим эмиттерным резисторам 1ц Тщ через разделительные диоды каждой счетной декады 2 - 2ц . Для разнесения во времени подго5 товки, схеи«л 1 реверса в нужном направлении и счета импульсов на входах младшей декады 2/ ставятся цепи 15 и.16 задержки соответственно. Кроме того, в схему 1 реверса

п входят резисторы 17 и 18 и диоды 19 и 20.

Счетчик работает следующим образом.

Величина сопротивлений резистос ров 6 - и 7 - 7 выбирается так, что в проводящем (единичном) состоянии в каждой декаде 2 - 2п находится только одна триггерная ячейка. Все остальные транзисторы декад заперты падением напряжения

на общих эмиттерных резисторах , б и 7 - 7(д . В исходное (нулевое; состояние каждаядекада 2 - 2{л приводится .положительным ::.утульсом сброса, подаваемым непосредст5 венно на базу первого h-p-n транзистора 4х (на чертеже цепь сброса не показана) . Отпирание этого транзистора приводит к отпиранию соответствующего фиксирующего, транзистора

0 3/ - 3x0 благодаря коллекторно-базовой продолжительной обратной связи между ними,Такое состояние является устойчивым.

5 Импульсы, подлежащие счету в прямом и обратном направлениях, поступают на соответствующие входы первой декады 2 и схемы 1 реверса. При поступлении отрицательного импульса прямого счета отпирается транзистор 10 триггера реверса,что приводит к отпиранию транзистора 11, который своим переходом коллектор эмиттер через разделительные диоды 14 - 14) шунтирует общие эмиттерные резисторы 7 - 7 каждой декады 2 - 2г,-. Открытый транзистор 10 шунтирует базовый делитель напряжения инвертора, выполненного на транзисторе 12, что приводит к его запи0 ранию. Это подготавливает общие

эмиттерные резисторы б - бр, к. сче- ту импульсов в прямом направлении. При поступлении отрицательных счетных импульсов движение открытой

5 ячейки сединицы) происходит слева

направо, так Kak основное воздействие оказывают транзисторы 4 - 4 .

Последующие отрицательные импульсы прямого счета (кроме первого не воздействуют на триггер реверса благодаря запиранию соответствующего его входа положительным напряжением, снимаекым с коллектора транзистора 10 через резистор 17 и диод 19.

Если схема подготовлена к счету импульсов в нужном направлении, то триггер реверса не срабатывает,

При срабатывании последнего каскада и опирания нулевой (на чертеже первой) ячейки на вторую декаду поступает первый отрицательный счетны импульс и фиксируется единица высшего разряда.

При поступлении первого положительного импульса обратного счета запираются транзисторы 10 и 11 и отпирается транзистор 12, что приводит к шунтированию через диоды 13/1/ - 13г, резисторов бд - бп Шунтирование резисторов - 7(1 прекращаетЬя благодаря запиранию диодов 144 . л положительным напряжением с коллектора запертого транзистора 11. Это подготавливает декады. 2/1 - 2п к счету в обратном направлении. Первый положительный импульс обратного счета, задержанный на время срабатывания 1 реверса цепью 16 задержки, поступает на соответствующий вход младшей декады, осуществляя сдвиг единицы на один шаг справа нашево, так Как теперь основное воздействие оказывают тран0зисторы 3; - 3jM .

В дальнейшем поступающие положительные импульсы не и-зменяют состояние схемы 1 реверса благодаря запиранию входа обратного счета через резистор 18 и диод 20 положительным

5 напряжением с коллектора закрытого транзистора 11.

Икшульс переноса на вторую декаду при обратном счете снимается с выхода девятой ячейки первой декады.

0Разделение разнополярных импульсов на входе схемы 1 реверса позволяет осуществить движение единицы в Одном направлении при появлении

5 отрицательного импульса и в противоположном, - при появлении положительного импульса.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОЛЬЦЕВОЙ СЧЕТЧИКр-'--г | 1971 |

|

SU308524A1 |

| Кольцевой счетчик | 1973 |

|

SU511702A2 |

| СЧЕТНАЯ ДЕКАДА С ЦИФРОВОЙ ИНДИКАЦИЕЙ | 1973 |

|

SU373889A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК НА НАСЫЩАЮЩИХСЯ ТРАНЗИСТОРАХ | 1970 |

|

SU270355A1 |

| РАСПРЕДЕЛИТЕЛЬ—СЧЕТЧИК | 1972 |

|

SU332577A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК С ИНДИКАЦИЕЙ | 1973 |

|

SU404075A1 |

| РЕВЕРСИВНЫЙ КОЛЬЦЕВОЙ СЧЕТЧИК | 1973 |

|

SU363216A1 |

| РЕЛЕ ВРЕМЕНИ (С ВЫХОДОМ НА СИМИСТОРЕ) | 1992 |

|

RU2130213C1 |

| ДЕСЯТИЧНЫЙ ТРАНЗИСТОРНЫЙ СЧЕТЧИК С ЦИФРОВОЙИНДИКАЦИЕЙ | 1972 |

|

SU341026A1 |

| Счетчик с неразрушающейся информацией | 1989 |

|

SU1651380A1 |

РЕВЕРСИВНЫЙ КОЛЬЦЕВОЙ СЧЕТЧИК, содержащий триггеры на транзисторах с различным типом проводимости, объедииенные в кольцевые декады с помощью междукаскадных конденсаторов и общих эмиттерных резисторов транзисторов одного типа проводимости, каждый резистор подключен к входам прямого и обратного счета, вхо- , ды первой кольцевой декады соедине-ны с входами триггера реверса, отличающийся тем, что,.с целью упрощения устройства и повышения надежности в работе, он содер-. жит разделительные диоды, причем триггер реверса выполнен на транзисторах с различным типом проводимости, к одному из входов которого подключен инвертор на транзисторе, коллектор- которого соединен через разделительный диод в кёикдой декаде с общим эмиттерным резистором транзисторов одного типа проводимости, другой выход-триггера соединен череэ разделительный диод в каждой декаде с общим эмиттерным резистором транзисторов противоположного типа проводимости. -I

Авторы

Даты

1984-01-23—Публикация

1972-11-21—Подача